# SONY

# **CXD1217Q**

# **Synchronizing Signal Generator for Video Camera**

#### **Description**

The CXD1217Q is a synchronizing signal generator for color video cameras.

#### **Features**

- Compatible with the respective systems, NTSC, PALM, PAL and SECAM

- Output is synchronized with the clock of 910fH or 908fH

- 25Hz offset processing by PAL system

- Color framing by the respective systems, NTSC, PALM and PAL

- Possible external synchronization by H reset, V reset and line alternate reset pins

Synchronizing signal generator for color video cameras

#### **Structure**

Silicon gate CMOS IC

#### **Absolute Maximum Ratings** (Ta = 25°C)

| <ul> <li>Supply voltage</li> </ul> | Vdd  | Vss - 0.5 to +7.0          | V  |

|------------------------------------|------|----------------------------|----|

| <ul> <li>Input voltage</li> </ul>  | Vı   | $Vss-0.5 \ to \ Vdd + 0.5$ | V  |

| <ul> <li>Output voltage</li> </ul> | Vo   | $Vss-0.5 \ to \ VdD + 0.5$ | V  |

| Operating temperature              | Topr | -20 to +75                 | °C |

| Storage temperature                | Tstg | -55 to +150                | °C |

#### **Recommended Operating Conditions**

| <ul> <li>Supply voltage</li> </ul> | VDD  | 4.5 to 5.5   | V  |

|------------------------------------|------|--------------|----|

| Operating temperature              | Topr | -20  to  +75 | °C |

Sony reserves the right to change products and specifications without prior notice. This information does not convey any license by any implication or otherwise under any patents or other right. Application circuits shown, if any, are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits.

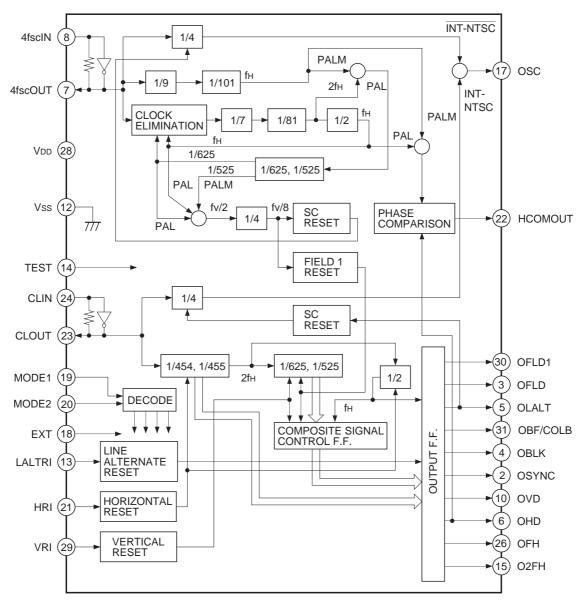

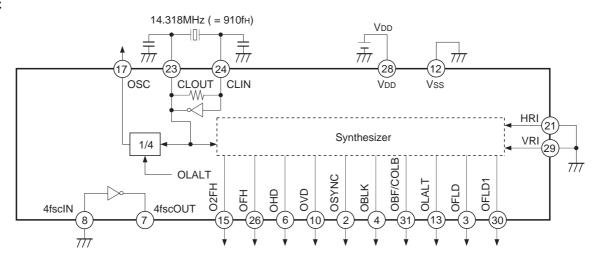

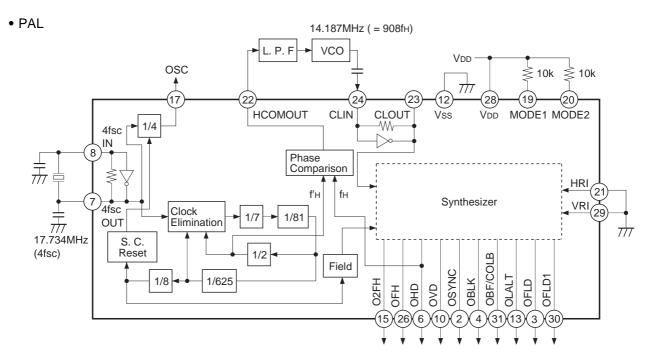

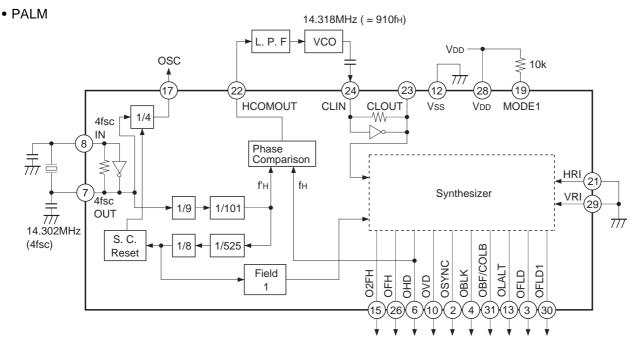

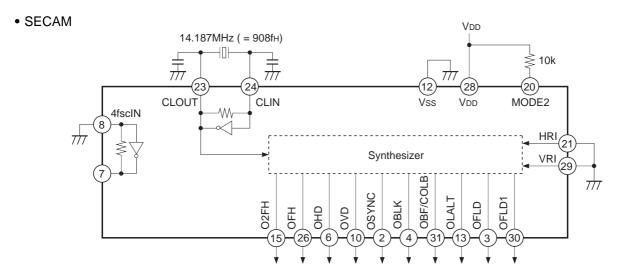

## **Block Diagram and Pin Configuration**

Note) Pin 17 output is (a) a signal based on Pin 24 in INT mode at NTSC. (b) each signal is based on Pin 8 in other modes.

# **Pin Description**

| Pin No. | Symbol   | I/O | Description                                                                                                  |

|---------|----------|-----|--------------------------------------------------------------------------------------------------------------|

| 1       | NC       | _   |                                                                                                              |

| 2       | OSYNC    | 0   | Composite sync output                                                                                        |

| 3       | OFLD     | 0   | Even and Odd output                                                                                          |

| 4       | OBLK     | 0   | Composite blanking output                                                                                    |

| 5       | OLALT    | 0   | Line alternate output                                                                                        |

| 6       | OHD      | 0   | Horizontal drive output                                                                                      |

| 7       | 4fscOUT  | 0   | 4fsc output                                                                                                  |

| 8       | 4fscIN   | I   | 4fsc input                                                                                                   |

| 9       | NC       | _   |                                                                                                              |

| 10      | OVD      | 0   | Vertical drive output                                                                                        |

| 11      | NC       | _   |                                                                                                              |

| 12      | Vss      | _   | GND pin                                                                                                      |

| 13      | LALTRI   | I   | Line alternate reset input                                                                                   |

| 14      | TEST     | I   | Test input                                                                                                   |

| 15      | O2FH     | 0   | 2fн output (Double the frequency of Pin 27)                                                                  |

| 16      | NC       | _   |                                                                                                              |

| 17      | osc      | 0   | Sub carrier output                                                                                           |

| 18      | EXT      | 1   | Internal and external synchronizing modes switchover L: Internal synchronization H: External synchronization |

| 19      | MODE1    | 1   | System selecting input 1                                                                                     |

| 20      | MODE2    | 1   | System selecting input 2                                                                                     |

| 21      | HRI      | I   | Horizontal reset input                                                                                       |

| 22      | HCOMOUT  | 0   | Phase comparator output                                                                                      |

| 23      | CLOUT    | 0   | Clock output                                                                                                 |

| 24      | CLIN     | I   | Clock input                                                                                                  |

| 25      | NC       | _   |                                                                                                              |

| 26      | OFH      | 0   | Horizontal frequency output                                                                                  |

| 27      | NC       | _   |                                                                                                              |

| 28      | Vdd      | _   | Power supply pin                                                                                             |

| 29      | VRI      | I   | Vertical reset signal                                                                                        |

| 30      | OFLD1    | 0   | First field output                                                                                           |

| 31      | OBF/COLB | 0   | Burst flag/color blanking output                                                                             |

| 32      | NC       | _   |                                                                                                              |

#### **Electrical Characteristics**

#### **DC** characteristics

$(VDD = 5V \pm 10\%, Vss = 0V, Topr = -20 \text{ to } +75^{\circ}C)$

| Item                               | Symbol | Conditions               | Min.               | Тур. | Max.               | Unit |

|------------------------------------|--------|--------------------------|--------------------|------|--------------------|------|

| Output voltage 1                   | Vон    | lон = −2mA               | VDD - 0.5          |      | VDD                | V    |

| Output voltage 1                   | Vol    | IoL = 4mA                | Vss                |      | 0.4                | V    |

| Output voltage 2*1                 | Vон    | Iон = -4mA               | VDD - 0.5          |      | VDD                | V    |

| Output voltage 2                   | Vol    | IoL = 4mA                | Vss                |      | 0.4                | V    |

| Output voltage 3*2                 | Vон    | Iон = -4mA               | V <sub>DD</sub> /2 |      |                    | V    |

| Output voltage 3                   | VoL    | IoL = 8mA                |                    |      | V <sub>DD</sub> /2 | V    |

| Input voltage                      | ViH    |                          | 0.7Vdd             |      |                    | V    |

| input voitage                      | VIL    |                          |                    |      | 0.3Vpd             | V    |

| Input current*3<br>(Pull-down pin) | Іін    | VIH = VDD                | 20                 | 50   | 120                | μA   |

| Output leak current*1              | lız    | At high impedance        |                    | ±30  |                    | nA   |

| Power current supply               | IDD    | At output pin in no-load |                    | 8    |                    | mA   |

| Feedback<br>resistance*4           | RfB    | VDD = 5V                 | 250k               |      | 2.5M               | Ω    |

<sup>\*1</sup> HCOMOUT pin

# I/O capacitance

(VDD = VI = 0V, fM = 1MHz)

| Item       | Symbol | Conditions | Min. | Тур. | Max. | Unit |

|------------|--------|------------|------|------|------|------|

| Input pin  | Cin    |            | _    | _    | 9    | pF   |

| Output pin | Соит   |            | _    | _    | 11   | pF   |

<sup>\*2 4</sup>fscOUT and CLOUT pins

<sup>\*3</sup> LALTRI, TEST, EXT, MODE1 and MODE2 pins

<sup>\*4 4</sup>fscOUT, 4fscIN, CLOUT and CLIN pins

SONY CXD1217Q

#### **Description of Operation** (See Block Diagram.)

The CXD1217 is applicable to four systems; namely, NTSC, PAL, PALM and SECAM. In order to realize them, the following relative equations of Sub-carrier (4fsclN) and Clock (CLIN) are adopted.

|       | Sub carrier         | Clock |

|-------|---------------------|-------|

| NTSC  | 4fsc = 910fн        | 910fн |

| PAL   | 4fsc = 1135fн + 2fv | 908fн |

| PALM  | 4fsc = 909fн        | 910fн |

| SECAM | _                   | 908fн |

As it is obvious from the above equations, the 4fsc and clock frequency do not coincide with each other in the PAL and PALM. Therefore matching of the clock frequency is carried out by providing PLL.

#### 1. MODE specified input

The CXD1217 provides four inputs to specify the respective modes.

\* EXT input: Set this pin to VDD side, and it becomes into external synchronizing mode. At this time, the counters in connection with the PLL loop as shown in the upper part of the block diagram become into stand still state.

<sup>\*</sup> MODE1 and MODE2 inputs: These are inputs for the system selection.

| MODE1 | MODE2 | System |

|-------|-------|--------|

| 0     | 0     | NTSC   |

| 0     | 1     | SECAM  |

| 1     | 0     | PALM   |

| 1     | 1     | PAL    |

$$"0" \rightarrow Vss$$

$"1" \rightarrow Vpp$

(Because it is dropped internally to Vss with MOS resistance.)

#### 2. Reset operation

The CXD1217 has three reset inputs; namely, HRI, VRI, LALTRI, and it works to perform reset operation when it detects falling edge. These three inputs are so designed as to take in synchronization with the IC internal clock. Therefore, it is a prerequisite that both systems should have clock frequencies that are matched as a reset operation to each other (GEN locked).

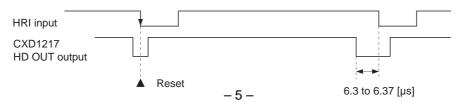

#### • H reset (HRI input)

When the HRI input is continuous with H synchronization, resetting is activated with the initial falling edge, and for the subsequent edges they do not have to be reset unless they are deviated more than 2-bit (140ns) against the initial edge in the internal clock. That is, if the jitter of HRI input is less than 140ns, it is absorbed. The minimum resetting pulse width is over 0.3µs.

The phase to be reset is the advanced point of 6.3 to 6.37 $\mu$ s (= 90 to 91-bit  $\times$  70ns) than the HRI input as shown in the diagram below.

<sup>\*</sup> TEST input: An input to be used to measure IC. This input is normally kept opened.

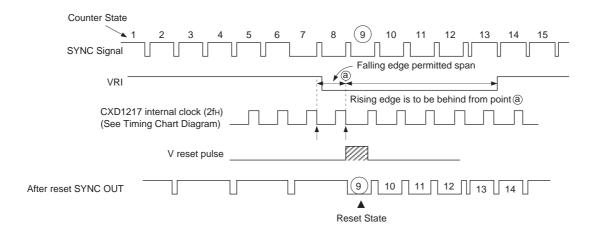

#### V reset (VRI input)

When the VRI is input as shown in figure below, OSYNC can be reset at the same phase with the SYNC signal.

Since the falling edge point in the diagram above (marked with  $\uparrow$ ) is the boundary of reset, if the falling edge of the VRI input traverses that point, it causes 1/2H deviation to the reset state.

Accordingly, if resetting is applied between two similar systems whose frequency are different, the V to which resetting is applied generates jitter of 1/2H. (When the resetting is applied continuously.)

#### • LALT reset (LALTRI input)

Phase relation between LALTRI pulse polarity and 2fH is the same as in the case of V resetting.

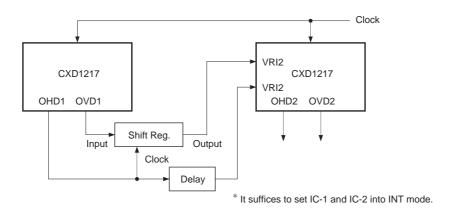

Resetting operation is basically required only in the external synchronizing mode (GEN LOCK mode). However, even in the internal synchronizing mode, it sometimes requires H and V outputs whose phases are deviated against a certain output. In that case, it suffices to use two CXD1217s and conduct the operation as follows:

By varying the Delay and Shift Reg. of the above diagram, any phases of OHD2 and OVD2 can be provided against the respective OHD1 and OVD1.

#### 3. Color framing

In the case of internal synchronization in the individual NTSC, PAL and PALM systems, the phase relationships between SYNC of the 1st field and sub-carrier are kept stable regardless of the power supply being ON or OFF. However, as the PAL and PALM systems are comprised of PLL, the absolute values concerning the phase according to variation of the ambient temperature drifts.

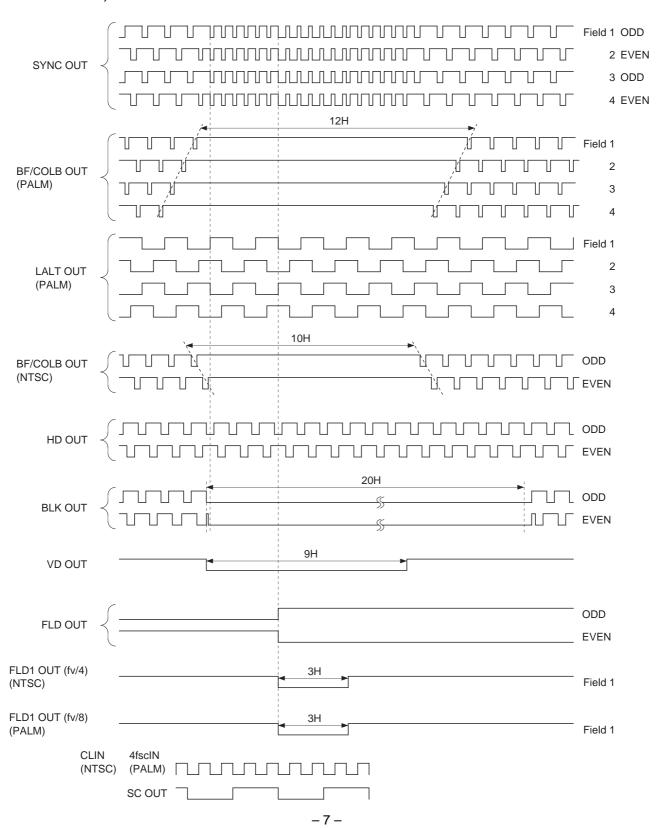

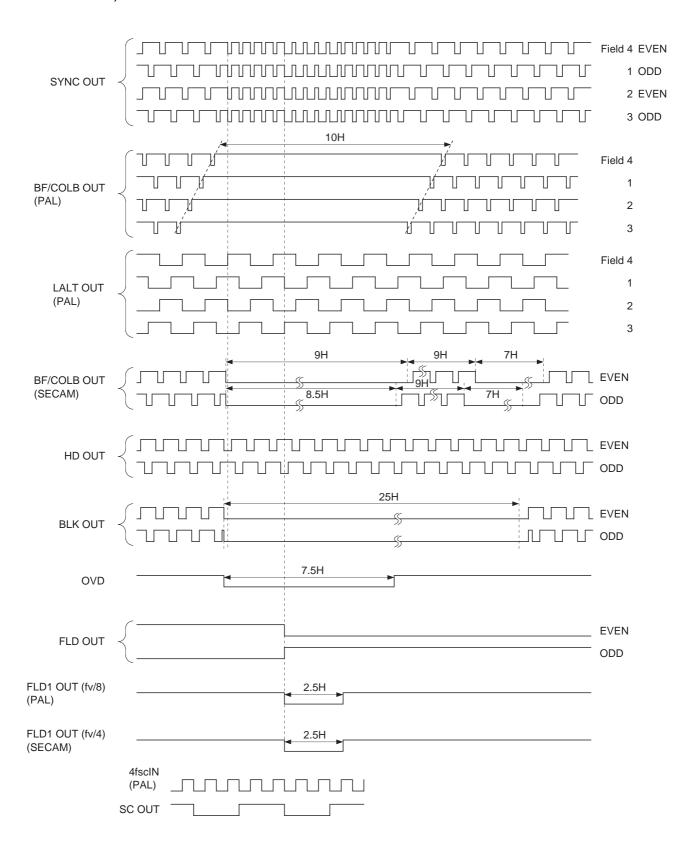

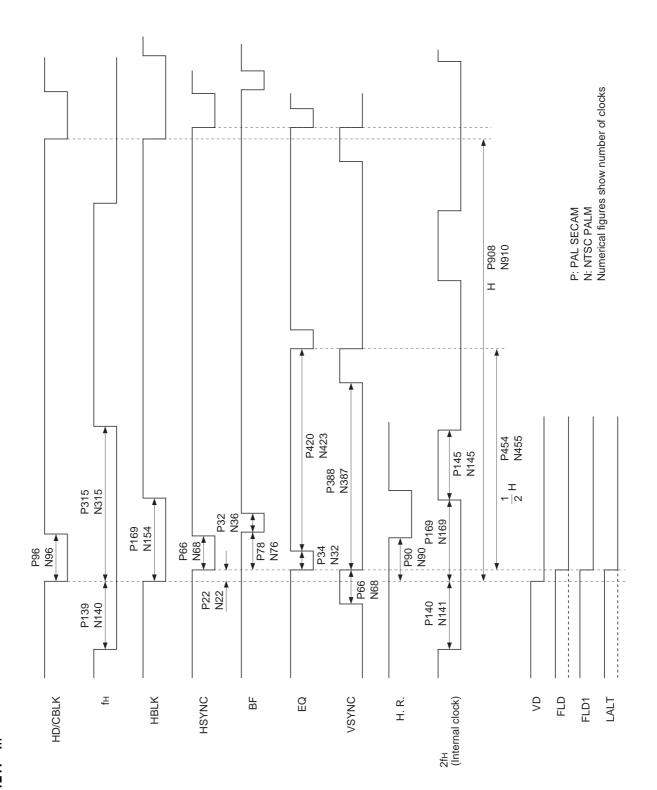

#### **Timing Chart**

#### **Output Timing Chart Diagram**

### CXD1217 NTSC, PALM

#### CXD1217 PAL, SECAM

#### **Application Circuit**

#### Basic connection in individual systems

Basic connection in individual systems at internal synchronization mode (EXT input = "0") is as follows. See waveform diagram for each output.

#### NTSC

<sup>\*</sup> H/2 is output for LALT OUT even in NTSC mode.

<sup>\*</sup> MODE1, MODE2, EXT, TEST and LALTRI pins can be kept open. (If noise annoys, connect to Vss by low impedance.)

<sup>\*</sup> Inverter of CLIN or CLOUT pins are usable as VCO.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

<sup>\*</sup> Internal inverter is usable as VCO.

<sup>\*</sup> COLB is output to BF/COLB OUT pin.

Application circuits shown are typical examples illustrating the operation of the devices. Sony cannot assume responsibility for any problems arising out of the use of these circuits or for any infringement of third party patent and other right due to same.

<sup>\*</sup> SDR and SDB are formed in PLL using 908fH.

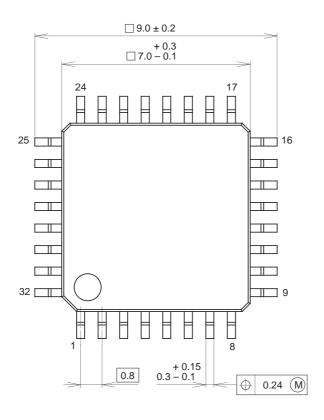

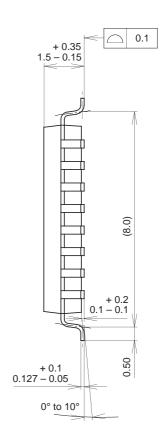

## Package Outline Unit: mm

# 32PIN QFP (PLASTIC)

| SONY CODE  | QFP-32P-L01   |

|------------|---------------|

| EIAJ CODE  | QFP032-P-0707 |

| JEDEC CODE |               |

| PACKAGE MATERIAL | EPOXY RESIN    |

|------------------|----------------|

| LEAD TREATMENT   | SOLDER PLATING |

| LEAD MATERIAL    | 42 ALLOY       |

| PACKAGE MASS     | 0.2g           |