#### **Features**

- Makes volatile memories nonvolatile

- Precision Voltage Monitor disables memory access when supply voltage out of tolerance specification. No incorrect data can be written to the memory.

- Supply voltage selectable with TOL pin (5% or 10%).

- Automatic battery back-up during power failure for nonvolatile data storage in memory.

- Independent dual battery switches for redundancy.

- Battery check at Power-up.

- Memory access disabled for 20 ms after power-up or after power glitches for extra data integrity.

- Low Power CMOS

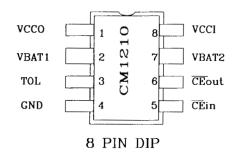

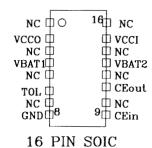

- Space saving 8-pin DIP or 16-pin SOIC surface mount package.

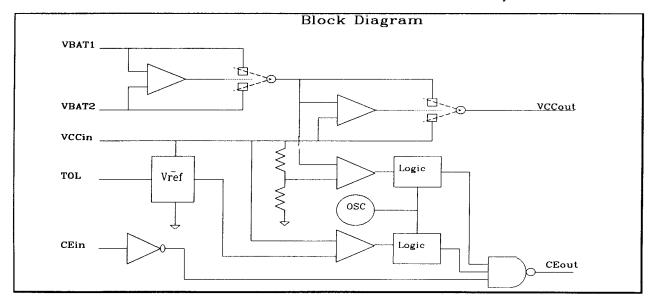

## **Operation**

The CM1210 nonvolatile controller performs all essential functions for retaining valid data in volatile memory during power failure by a battery backup. With one CM1210 and one or two 3V batteries a bank of SRAM's can be made nonvolatile.

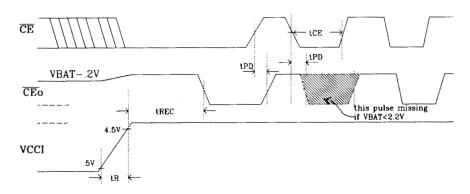

At power-up both batteries are tested under loaded conditions. If only one battery is being used the second battery input needs to be grounded. A battery failure will be only indicated if both battery inputs are below 2.2V. A battery failure is signaled by disabling the 2nd CEO pulse after power-up.

At power-up and for a period of maximum 125 ms thereafter the CEO output is held high, disabling all memory cycles.

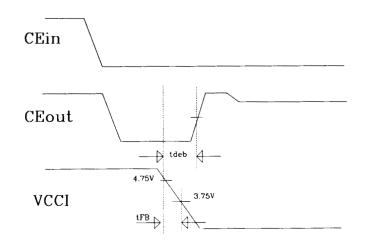

During normal operation with VCCI within the programmable tolerance limits, 5% or 10%, the VCCO output is connected to the VCCI input by an internal switch with less than 200 mV voltage drop at 80 mA of output current. CEO will follow CE with a maximum 20 ns delay. Power fail detection occurs in the VCCI range of 4.74V to 4.5V with the tolerance pin grounded (5% tolerance) or in the range of 4.49 V to 4.25 V with the tolerance pin connected to VCCO (10 % tolerance). Power fail must occur during three subsequent 25 ms intervals before it is validated and CEO then will be disabled: If CE is high CEO will stay high at VCCO during a validated power fail condition. If CE is low it will be forced high 75 ms after the validated power fail occurs. A recovery from power fail is equivalent to a power-up.

As long as VCCI is above the higher of the two battery voltages VCCO will be connected to VCCI. As soon as VCCI falls below the higher of the two battery voltages VCCO will be disconnected from VCCI and connected to the higher battery voltage (at a lower current rating of the switch). Once VCCO is connected to a VBAT, this battery voltage must drop .5 V below the other battery voltage before VCCO will be connected to the other battery.

C0720300

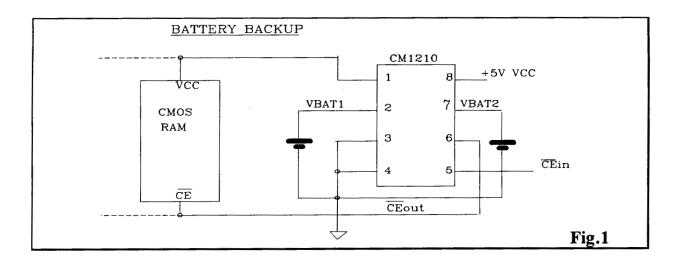

<u>Fig. 1</u> shows a typical application to make CMOS RAMs nonvolatile with all the necessary connections to write protect the RAMs when VCC is less than 4.75 Volts.

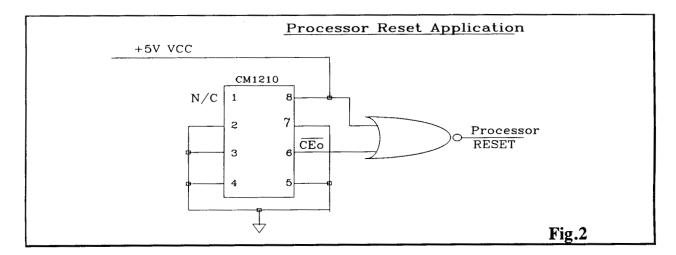

Fig. 2 shows the use of the CM1210 to halt the processor when VCC is less than 4.75 Volts and to delay its restart on power-up to prevent erroneous writes.

#### ABSOLUTE MAXIMUM RATINGS\*

# **RECOMMENDED DC OPERATING CONDITIONS** ( $0^{\circ}$ C < $T_A$ < $70^{\circ}$ C)

| PARAMETER                     | SYMBOL        | MIN  | TYP | MAX      | UNIT |

|-------------------------------|---------------|------|-----|----------|------|

| Supply Voltage<br>PIN3 = GND  | VCCI<br>(5%)  | 4.75 | 5.0 | 5.5      | V    |

| Supply Voltage<br>PIN3 = VCCO | VCCI<br>(10%) | 4.5  | 5.0 | 5.5      | V    |

| CE input low                  | VIL           | 3    |     | 0.8      | V    |

| CE input high                 | VIH           | 2.2  |     | VCCO+0.3 | V    |

| Battery voltage               | VBAT1,2       | 2.0  |     | 4.0      | V    |

# **D.C. ELECTRICAL CHARACTERISTICS** ( $0^{\circ}$ C < $T_A$ < $70^{\circ}$ C)

| PARAMETER                    | SYMBOL           | MIN         | TYP  | MAX  | UNIT | CONDITION                          |

|------------------------------|------------------|-------------|------|------|------|------------------------------------|

| Standby Current              | ICCI             |             |      | 5    | mA   | VCCI=5.5V,no load                  |

| Battery Current              | IBAT             |             |      | 100  | nA   | V <sub>BAT</sub> =4V,no load       |

| Output Voltage               | VCC01            | VCCI2       |      |      | V    | VCCI=VTOL=4.5V<br>ICCO1=80 mA      |

| Output Voltage               | VCCO2            | VBAT-<br>.3 |      |      | V    | VCCI=0,VBAT=2V<br>ICCO2=50 mA      |

| CE output low                | V <sub>OL</sub>  |             |      | 0.4  | V    | I <sub>L</sub> =4 mA,<br>VCCI=4.5V |

| CE output high               | V <sub>OH</sub>  | 2.4         |      | -    | V    | $I_L=-1$ mA,VCCI=4.5V              |

| CE output high               | V <sub>OHL</sub> | VBAT-       |      |      | V    | VCCI=0, VBAT=2V                    |

| VCC Trip Point (TOL=GND)     | VCCTP<br>5%      | 4.50        | 4.62 | 4.74 | V    |                                    |

| VCC Trip Point (TOL=VCCO)    | VCCTP<br>10%     | 4.25        | 4.37 | 4.49 | V    |                                    |

| VBAT Fail Warning  @Power-up | $V_{BATF}$       |             | 2.2  |      | V    | VCCI=5V                            |

| VBAT Hysteresis              | dVBAT            |             | .45  |      | V    | VBAT=3V                            |

<sup>\*</sup> This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods of time may affect reliability.

# A.C. ELECTRICAL CHARACTERISTICS ( $0^{\circ}$ C < $T_{A}$ < $70^{\circ}$ C)

| PARAMETER                     | SYMBOL           | MIN | TYP | MAX | UNIT | CONDITION                          |

|-------------------------------|------------------|-----|-----|-----|------|------------------------------------|

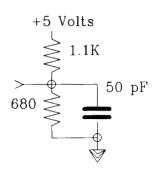

| CE Propagation Delay          | <sup>t</sup> PD  | 5   | 12  | 20  | ns   | TTL load (fig.3)<br>VCCI=VTOL=4.5V |

| CE Pulse Width                | t <sub>CE</sub>  |     |     | 1.5 | ms   |                                    |

| VCCI slew rate  @ power down  | t <sub>FB</sub>  | 2   |     |     | V/ms |                                    |

| VCCI rise time  @ power up    | <sup>t</sup> R   | 0   |     |     | ms   |                                    |

| Power-up Recovery             | tREC             | 2   | 20  | 125 | ms   | VCCI=5V                            |

| VCCI debounce time            | t <sub>deb</sub> | 6   | 60  | 375 | ms   |                                    |

| CE <sub>in</sub> capacitance  | C <sub>in</sub>  |     | 5   |     | pF   |                                    |

| CE <sub>out</sub> capacitance | C <sub>out</sub> |     | 7   |     | pF   |                                    |

# Powerup Timing Diagram

# Powerdown Timing Diagram

# CE output load

4

#### PIN CONFIGURATION

#### **ORDERING INFORMATION**

<u>CM1210</u> P

I

Product Identification Number

Package Types

Temperature Range

P - Plastic

S - SOIC, JEDEC

F - SOIC, EIJA

C - Ceramic

X - Die

None  $0^{\circ}\text{C}$  to  $+70^{\circ}\text{C}$ I  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$

6/5/2000