February 1998

# **Address Sequencer**

#### Features

- This Circuit is Processed in Accordance to MIL-STD-883 and is Fully Conformant Under the Provisions of Paragraph 1.2.1.

- Block Oriented 24-Bit Sequencer

- Configurable as Two Independent 12-Bit Sequencers

- 24 x 24 Crosspoint Switch

- Programmable Delay on 12 Outputs 9-

- Multi-Chip Synchronization Signals

- Standard μP Interface

- 100pF Drive on Outputs

- DC to 40MHz Clock Rate

# **Applications**

- 1-D, 2-D Filtering

- · Pan/Zoom Addressing

- FFT Processing

- · Matrix Math Operations

# Ordering Information

| PART NUMBER       | TEMP.<br>RANGE ( <sup>O</sup> C) | PACKAGE   | PKG.<br>NO. |

|-------------------|----------------------------------|-----------|-------------|

| HSP45240GM-25/883 | -55 to 125                       | 68 Ld PGA |             |

| HSP45240GM-33/883 | -55 to 125                       | 68 Ld PGA |             |

| HSP45240GM-40/883 | -55 to 125                       | 68 Ld PGA |             |

# Description

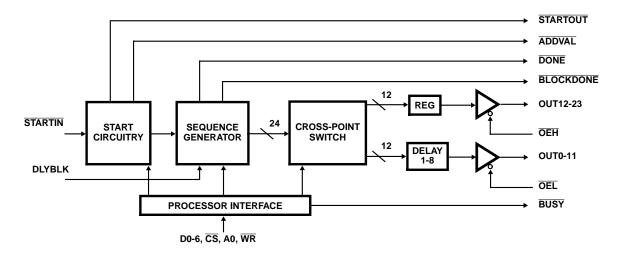

The Intersil HSP45240/883 is a high speed Address Sequencer which provides specialized addressing for functions like FFTs, 1-D and 2-D filtering, matrix operations, and image manipulation. The sequencer supports block oriented addressing of large data sets up to 24 bits at clock speeds up to 40MHz.

Specialized addressing requirements are met by using the onboard 24 x 24 crosspoint switch. This feature allows the mapping of the 24 address bits at the output of the address generator to the 24 address outputs of the chip. As a result, bit reverse addressing, such as that used in FFTs, is made possible.

A single chip solution to read/write addressing is also made possible by configuring the HSP45240 as two 12-bit sequencers. To compensate for system pipeline delay, a programmable delay is provided on 12 of the address outputs.

The HSP45240 is manufactured using an advanced CMOS process, and is a low power fully static design. The configuration of the device is controlled through a standard microprocessor interface and all inputs/outputs, with the exception of clock, are TTL compatible.

# **Block Diagram**

#### **Absolute Maximum Ratings**

#

## **Operating Conditions**

| Temperature Range | 55°C to 125°C |

|-------------------|---------------|

| Voltage Range     |               |

#### **Thermal Information**

| Thermal Resistance (Typical, Note 1)   | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (oC/W) |

|----------------------------------------|----------------------|----------------------|

| PGA Package                            | 37.1                 | 10.1                 |

| Maximum Package Power Dissipation at 1 | 25°C                 |                      |

| PGA Package                            |                      | 1.35W                |

| Maximum Junction Temperature           |                      | 175 <sup>0</sup> C   |

| Maximum Storage Temperature Range      | 65                   | oC to 150°C          |

| Maximum Lead Temperature (Soldering 1  |                      |                      |

|                                        |                      |                      |

#### **Die Characteristics**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTE:

1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

#### **TABLE 1. DC ELECTRICAL SPECIFICATIONS**

Device Guaranteed and 100% Tested

|                                   |                                                                                |                                                             | GROUP A        |                            | LIN |     |       |

|-----------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------|----------------|----------------------------|-----|-----|-------|

| PARAMETER                         | SYMBOL                                                                         | TEST CONDITIONS                                             | SUB-<br>GROUPS | TEMPERATURE (°C)           | MIN | MAX | UNITS |

| Logical One Input<br>Voltage      | V <sub>IH</sub>                                                                | V <sub>DD</sub> = 5.5V                                      | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | 2.2 | -   | V     |

| Logical Zero Input<br>Voltage     | V <sub>IL</sub>                                                                | V <sub>DD</sub> = 4.5V                                      | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 0.8 | V     |

| Output HIGH Voltage               | V <sub>OH</sub>                                                                | I <sub>OH</sub> = -400μA<br>V <sub>DD</sub> = 4.5V (Note 2) | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | 2.6 | -   | V     |

| Output LOW Voltage                | V <sub>OL</sub>                                                                | OL = +2.0mA<br>V <sub>CC</sub> = 4.5V (Note 2)              | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 0.4 | V     |

| Input Leakage Current             | I <sub>I</sub>                                                                 | $V_{IN} = V_{CC}$ or GND<br>$V_{CC} = 5.5V$                 | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | -10 | +10 | μА    |

| Output Leakage Current            | lo                                                                             | $V_{OUT} = V_{CC}$ or GND $V_{CC} = 5.5V$                   | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | -10 | +10 | μА    |

| Clock Input High                  | V <sub>IHC</sub>                                                               | V <sub>CC</sub> = 5.5V                                      | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | 3.0 | -   | ٧     |

| Clock Input Low                   | V <sub>ILC</sub>                                                               | V <sub>CC</sub> = 4.5V                                      | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 0.8 | V     |

| Standby Power Supply<br>Current   | by Power Supply   I <sub>CCSB</sub>   V <sub>IN</sub> = V <sub>CC</sub> or GND |                                                             | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 500 | μΑ    |

| Operating Power<br>Supply Current | ICCOP                                                                          | f = 33MHz<br>V <sub>CC</sub> = 5.5V (Note 3)                | 1, 2, 3        | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 99  | mA    |

| Functional Test                   | FT                                                                             | (Note 4)                                                    | 7, 8           | -55 ≤ T <sub>A</sub> ≤ 125 | -   | -   |       |

#### NOTES:

- 2. Interchanging of force and sense conditions is permitted.

- 3. Operating Supply Current is proportional to frequency, typical rating is 3mA/MHz.

- 4. Tested as follows: t = 1MHz,  $V_{IH} = 2.6$ ,  $V_{IL} = 0.4$ ,  $V_{OH} \ge 1.5V$ ,  $V_{OL} \le 1.5V$ ,  $V_{IHC} = 3.4V$ , and  $V_{ILC} = 0.4V$ .

#### **TABLE 2. AC ELECTRICAL SPECIFICATIONS**

Device Guaranteed and 100% Tested

|                                                                       |                  | GROUP A   | TEMPERATURE                | -25 (2 | 5MHz) | -33 (33MHz) |        | -40 (40MHz) |     |       |

|-----------------------------------------------------------------------|------------------|-----------|----------------------------|--------|-------|-------------|--------|-------------|-----|-------|

| PARAMETER                                                             | SYMBOL           | SUBGROUP  | (°C)                       | MIN    | MAX   | MIN         | MAX    | MIN         | MAX | UNITS |

| Clock Period                                                          | t <sub>CP</sub>  | 9, 10, 11 | $-55 \le T_A \le 125$      | 39     | -     | 30          | -      | 25          | -   | ns    |

| Clock Pulse Width High                                                | <sup>t</sup> CH  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 15     | -     | 12          | -      | 10          | -   | ns    |

| Clock Pulse Width Low                                                 | t <sub>CL</sub>  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 15     | -     | 12          | -      | 10          | -   | ns    |

| Setup Time D0-6 to WR High                                            | t <sub>DS</sub>  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 17     | -     | 16          | -      | 14          | -   | ns    |

| Hold Time D0-6 from WR<br>Low                                         | t <sub>DH</sub>  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 0      | -     | 0           | -      | 0           | -   | ns    |

| Setup Time A, $\overline{\text{CS}}$ to $\overline{\text{WR}}$<br>Low | t <sub>AS</sub>  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 5      | -     | 5           | -      | 5           | -   | ns    |

| Hold Time A, $\overline{\text{CS}}$ from $\overline{\text{WR}}$ High  | t <sub>AH</sub>  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 0      | -     | 0           | -      | 0           | -   | ns    |

| Pulse Width for WR Low                                                | t <sub>WRL</sub> | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 18     | -     | 14          | -      | 12          | -   | ns    |

| Pulse Width for WR High                                               | t <sub>WRH</sub> | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 18     | -     | 14          | -      | 12          | -   | ns    |

| WR Cycle Time                                                         | t <sub>WP</sub>  | 9,10,11   | -55 ≤ T <sub>A</sub> ≤ 125 | 39     | -     | 30          | -      | 25          | -   | ns    |

| Set-up Time STARTIN, DLYBLK, to Clock High                            | t <sub>IS</sub>  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 15     | -     | 12          | -      | 10          | -   | ns    |

| Hold Time STARTIN,<br>DLYBLK, to Clock High                           | t <sub>IH</sub>  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | 0      | -     | 0           | -      | 0           | -   | ns    |

| Clock to Output Prop.<br>Delay on OUT0-23                             | t <sub>PDO</sub> | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | -      | 18    | -           | 16     | -           | 14  | ns    |

| Clock to Prop. Delay, on STARTOUT, BLKDONE, DONE, ADVAL, and BUSY     | <sup>t</sup> PDS | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | -      | 18    | -           | 16     | -           | 14  | ns    |

| Output Enable Time (Note 6)                                           | t <sub>EN</sub>  | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 | -      | 22    | -           | 20     | -           | 15  | ns    |

| RST Low Time                                                          | t <sub>RST</sub> | 9, 10, 11 | -55 ≤ T <sub>A</sub> ≤ 125 |        |       | 2 Clock     | Cycles |             |     | ns    |

#### NOTES:

- 5. AC Testing: V<sub>CC</sub> = 4.5V and 5.5V, inputs are driven at 3.0V for Logic "1" and 0.0V for a Logic "0". Input and output timing measurements are made at 1.5V for both a logic "1" and "0". CLK is driven at 4.0V and 0V and measured at 2.0V.

- 6. Transition is measured at  $\pm 200$ mV from steady state voltage with loading as specified by test load circuit and  $C_L = 40$ pF.

#### **TABLE 3. ELECTRICAL PERFORMANCE SPECIFICATIONS**

|                       | TEST             |                                                                                                  |       |                            |     | -25<br>(25MHz) |     | -33<br>(33MHz) |     | -40 (40MHz) |       |

|-----------------------|------------------|--------------------------------------------------------------------------------------------------|-------|----------------------------|-----|----------------|-----|----------------|-----|-------------|-------|

| PARAMETERS            | SYMBOL           | CONDITIONS                                                                                       | NOTES | TEMPERATURE                | MIN | MAX            | MIN | MAX            | MIN | MAX         | UNITS |

| Input<br>Capacitance  | C <sub>IN</sub>  | V <sub>CC</sub> = Open,<br>f = 1MHz, All mea-<br>surements are<br>referenced to de-<br>vice GND. | 7     | T <sub>A</sub> = 25        | -   | 10             | -   | 10             | 1   | 10          | pF    |

| Output<br>Capacitance | C <sub>OUT</sub> | V <sub>CC</sub> = Open,<br>f = 1MHz, All mea-<br>surements are<br>referenced to de-<br>vice GND. | 7     | T <sub>A</sub> = 25        | -   | 10             | -   | 10             | -   | 10          | pF    |

| Output Disable        | t <sub>OEZ</sub> |                                                                                                  | 7, 8  | -55 ≤ T <sub>A</sub> ≤ 125 | -   | 22             | -   | 20             | -   | 15          | ns    |

# TABLE 3. ELECTRICAL PERFORMANCE SPECIFICATIONS (Continued)

|                     | TEST            |            | -25<br>(25MHz) |                            | -33<br>(33MHz) |     | -40 (40MHz) |     |     |     |       |

|---------------------|-----------------|------------|----------------|----------------------------|----------------|-----|-------------|-----|-----|-----|-------|

| PARAMETERS          | SYMBOL          | CONDITIONS | NOTES          | TEMPERATURE                | MIN            | MAX | MIN         | MAX | MIN | MAX | UNITS |

| Output Rise<br>Time | tOR             |            | 7, 8           | -55 ≤ T <sub>A</sub> ≤ 125 | -              | 5   | -           | 5   | 1   | 3   | ns    |

| Output Fall<br>Time | t <sub>OF</sub> |            | 7, 8           | -55 ≤ T <sub>A</sub> ≤ 125 | -              | 5   | -           | 5   | -   | 3   | ns    |

#### NOTES:

- 7. Parameters listed in Table 3 are controlled via design or process parameters and are not directly tested. These parameters are characterized upon initial design and after major process and/or design changes.

- 8. Loading is as specified in the test load circuit with  $C_L$  = 40pF.

#### **TABLE 4. ELECTRICAL TEST REQUIREMENTS**

| CONFORMANCE GROUPS | METHOD       | SUBGROUPS                     |  |  |

|--------------------|--------------|-------------------------------|--|--|

| Initial Test       | 100%/5004    | -                             |  |  |

| Interim Test       | 100%/5004    | -                             |  |  |

| PDA                | 100%         | 1                             |  |  |

| Final Test         | 100%         | 2, 3, 8A, 8B, 10, 11          |  |  |

| Group A            | -            | 1, 2, 3, 7, 8A, 8B, 9, 10, 11 |  |  |

| Groups C and D     | Samples/5005 | 1, 7, 9                       |  |  |

# **Burn-In Circuit**

| L |     | ŌĒĦ             | DLY<br>BLK | START<br>OUT    | v <sub>cc</sub> | BLOCK<br>DONE | GND             | OUT1  | OUT2            | NC    |                 |

|---|-----|-----------------|------------|-----------------|-----------------|---------------|-----------------|-------|-----------------|-------|-----------------|

|   |     |                 | BLK        |                 |                 | DONE          |                 |       |                 |       |                 |

| K | NC  | NC              | OEL        | START<br>IN     | ADD<br>VAL      | BUSY          | DONE            | оито  | V <sub>CC</sub> | NC    | OUT3            |

| J | RST | v <sub>cc</sub> |            |                 |                 |               |                 |       |                 | GND   | OUT4            |

| н | CLK | GND             |            |                 |                 |               |                 |       |                 | OUT5  | v <sub>cc</sub> |

| G | cs  | A0              |            |                 |                 |               |                 |       |                 | OUT6  | оит7            |

| F | WR  | GND             |            |                 |                 |               |                 |       |                 | GND   | OUT8            |

| E | D6  | D5              |            |                 |                 |               |                 |       |                 | OUT9  | v <sub>cc</sub> |

| D | D4  | D3              |            |                 |                 |               |                 |       |                 | OUT10 | OUT11           |

| С | D2  | D1              |            |                 |                 |               |                 |       |                 | GND   | OUT12           |

| В | D0  | NC              | OUT22      | OUT21           | GND             | OUT18         | OUT17           | GND   | OUT14           | NC    | NC              |

| Α |     | GND             | OUT23      | v <sub>cc</sub> | OUT20           | OUT19         | v <sub>cc</sub> | OUT16 | OUT15           | OUT13 |                 |

| ļ | 1   | 2               | 3          | 4               | 5               | 6             | 7               | 8     | 9               | 10    | 11              |

| PGA<br>PIN | PIN<br>NAME | BURN-<br>IN<br>SIGNAL | PGA<br>PIN | PIN<br>NAME     | BURN-<br>IN<br>SIGNAL | PGA<br>PIN | PIN<br>NAME     | BURN-<br>IN<br>SIGNAL | PGA<br>PIN | PIN NAME        | BURN-<br>IN<br>SIGNAL |

|------------|-------------|-----------------------|------------|-----------------|-----------------------|------------|-----------------|-----------------------|------------|-----------------|-----------------------|

| A2         | GND         | GND                   | В9         | OUT14           | V <sub>CC</sub> /2    | F11        | OUT8            | V <sub>CC</sub> /2    | K6         | BUSYB           | V <sub>CC</sub> /2    |

| A3         | OUT23       | V <sub>CC</sub> /2    | C1         | D2              | F10                   | G1         | CSB             | F5                    | K7         | DONEB           | V <sub>CC</sub> /2    |

| A4         | Vcc         | Vcc                   | C2         | D1              | F9                    | G2         | A0              | F6                    | K8         | OUT0            | V <sub>CC</sub> /2    |

| A5         | OUT20       | V <sub>CC</sub> /2    | C10        | GND             | GND                   | G10        | OUT6            | V <sub>CC</sub> /2    | K9         | V <sub>CC</sub> | V <sub>CC</sub>       |

| A6         | OUT19       | V <sub>CC</sub> /2    | C11        | OUT12           | V <sub>CC</sub> /2    | G11        | OUT7            | V <sub>CC</sub> /2    | K11        | OUT3            | V <sub>CC</sub> /2    |

| A7         | Vcc         | Vcc                   | D1         | D4              | F12                   | H1         | CLK             | F0                    | L2         | ОЕНВ            | F13                   |

| A8         | OUT16       | V <sub>CC</sub> /2    | D2         | D3              | F11                   | H2         | GND             | GND                   | L3         | DLYBLK          | F11                   |

| A9         | OUT15       | V <sub>CC</sub> /2    | D10        | OUT10           | V <sub>CC</sub> /2    | H10        | OUTS            | V <sub>CC</sub> /2    | L4         | STARTOUTB       | V <sub>CC</sub> /2    |

| A10        | OUT13       | V <sub>CC</sub> /2    | D11        | OUT11           | V <sub>CC</sub> /2    | H11        | V <sub>CC</sub> | V <sub>CC</sub>       | LS         | V <sub>CC</sub> | V <sub>CC</sub>       |

| B1         | D0          | F8                    | E1         | D6              | F7                    | J1         | RSTB            | F14                   | L6         | BLOCKDONEB      | V <sub>CC</sub> /2    |

| В3         | OUT22       | V <sub>CC</sub> /2    | E2         | D5              | F13                   | J2         | V <sub>CC</sub> | V <sub>CC</sub>       | L7         | GND             | GND                   |

| B4         | OUT21       | V <sub>CC</sub> /2    | E10        | OUT9            | V <sub>CC</sub> /2    | J10        | GND             | GND                   | L8         | OUT1            | V <sub>CC</sub> /2    |

| B5         | GND         | GND                   | E11        | V <sub>CC</sub> | V <sub>CC</sub>       | J1 1       | OUT4            | V <sub>CC</sub> /2    | L9         | OUT2            | V <sub>CC</sub> /2    |

| B6         | OUT18       | V <sub>CC</sub> /2    | F1         | WRB             | F4                    | K3         | OELB            | F12                   |            |                 |                       |

| В7         | OUT17       | V <sub>CC</sub> /2    | F2         | GND             | GND                   | K4         | START1NB        | F6                    |            |                 |                       |

| В8         | GND         | GND                   | F10        | GND             | GND                   | K5         | ADVALB          | V <sub>CC</sub> /2    |            |                 |                       |

#### NOTES:

- 9.  $V_{CC}/2$  (2.7V  $\pm 10\%$ ) used for outputs only.

- 10. 47 $\Omega$  (±20%) resistor connected to all pins except VCC and GND.

- 11.  $V_{CC} = 5.5 \pm 0.5 V$ .

- 12.  $0.1 \mu F$  (min) capacitor between  $V_{\mbox{\footnotesize{CC}}}$  and GND per position.

- 13.  $F0 = 100 \text{kHz} \pm 10\%$ , F1 = F0/2, F2 = F1/2...., F11 = F10/2, 40% -60% Duty Cycle.

- 14. Input voltage limits:  $V_{IL}$  = 0.8V max.,  $V_{IH}$  = 4.5V  $\pm 10\%.$

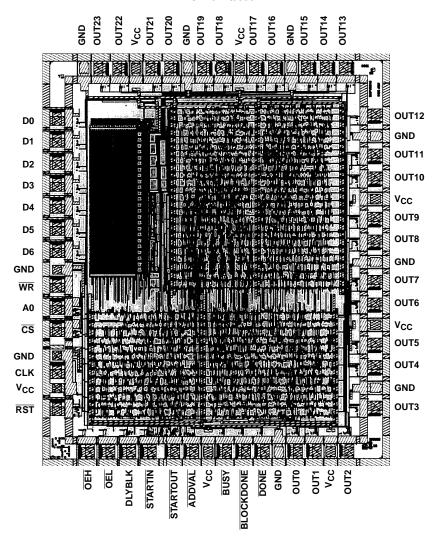

## Die Characteristics

**DIE DIMENSIONS:**

186 mils x 222 mils x 19 ±1mils

**METALLIZATION:**

Type: Si - Al or Si-Al-Cu

Thickness: 8kÅ

#### **GLASSIVATION:**

Type: Nitrox Thickness: 10kÅ

#### **WORST CASE CURRENT DENSITY:**

$1.8 \times 10^5 \text{A/cm}^2$

# Metallization Mask Layout

#### HSP45240/883

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com