#### **Features**

- Implements Bluetooth<sup>™</sup> Specification on Short Distance Wireless Communication in 2.4 GHz ISM Band

- Provides 1 Mbps Aggregate Bit Rate

- Supports Frequency Hopping Spread Spectrum Physical-layer Interface to Dedicated Transceiver with Frequency Hopping Algorithm Implemented in Hardware

- Provides Baseband Functions in Hardware which Implement Bluetooth Low-level Bit Processing Such as Forward Error Correction (FEC), Header Error Check (HEC) and CRC Generation/Checking and Encryption/Decryption

- Integrated ARM7TDMI® RISC Processor

- Glueless SRAM Interface, Supporting Up to 256K Bytes of Memory

- Glueless Flash Memory Interface, Supporting Up to 256K Bytes of Nonvolatile Memory

- Glueless PCMCIA Bus Interface Conforming to PC Card Standard Feb. 1995

- USB Interface Conforming to Universal Serial Bus Standard Version 1.1

- 16550 UART Core Offering 32-byte Receive FIFO and Programmable Baud Rate

- Programmable 8/16-bit Wide External Memory Interface

- Supports Multiple Reference Clock Frequencies (13.000, 14.400, 16.800, 19.440 MHz)

- 176-lead LQFP

- 3.3V Supply

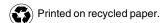

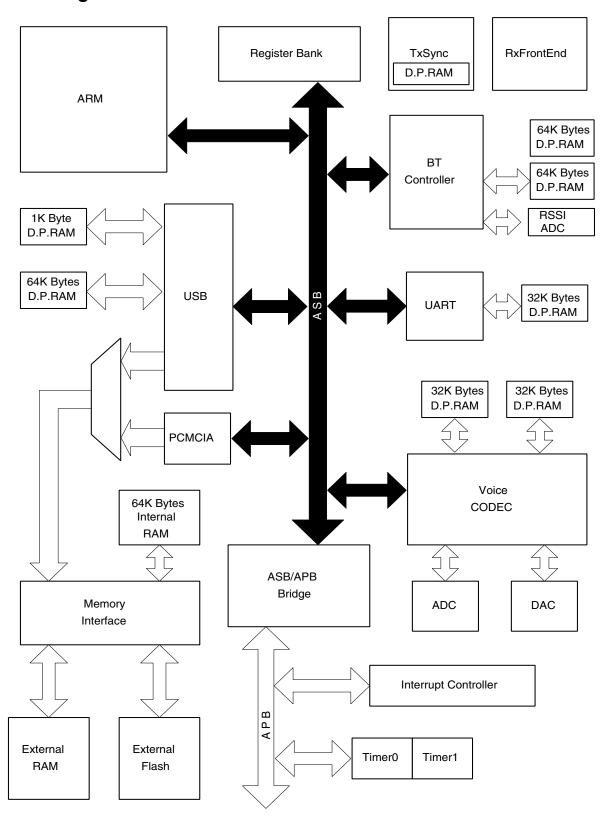

## **System Level Block Diagram**

# Single Chip Bluetooth<sup>™</sup> Controller

AT76C551

#### Overview

The AT76C551 is a single chip controller providing the functionality for high data rate, short distance wireless communications in the free ISM band. In conjunction with a 2.4 GHz transceiver, it provides a cost effective networking solution for a wide range of digital communication devices and computer peripherals. Integration is simplified due to the incorporation of three different interfaces: USB and 16550 UART compatible interfaces and a PCMCIA interface conforming to the PC Card 95 specification. Additionally, a voice coding/decoding module is provided.

The AT76C551 is comprised of a baseband processor. This processor carries out all bit-level processing after modulation/demodulation of the Bluetooth bitstream. It controls the transceiver and dedicated voice coding/decoding. The AT76C551 has an ARM7TDMI processor core with support for internal and external memory, as well as the interface core logic.

The powerful RISC processor in the ARM7TDMI carries out all but the low level baseband functions.

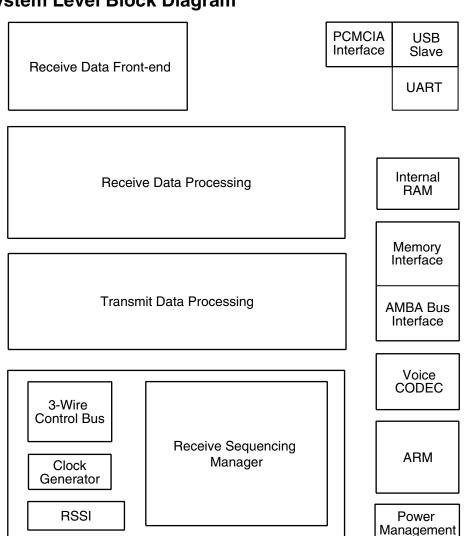

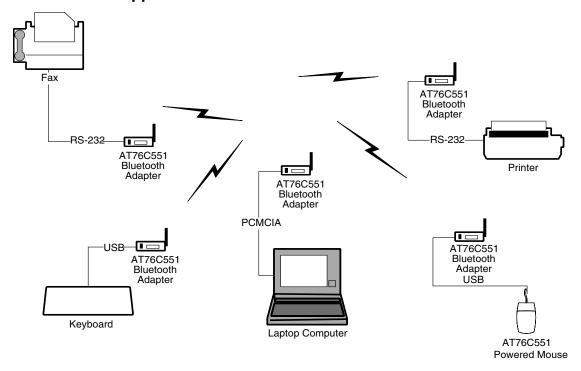

# **Applications**

AT76C551 can be used in applications where fast short range communication is required between portable devices such as mobile phones and digital peripherals.

Typical usages would include:

- Wireless network cards

- Mobile phones

- Laptop and desktop computers

- Pagers

- Digital cameras

- PDAs

- Wireless computer peripherals (printers, etc.)

# **Typical AT76C551 Home Application**

## **Typical AT76C551 Mobile Application**

# **Functional Diagram**

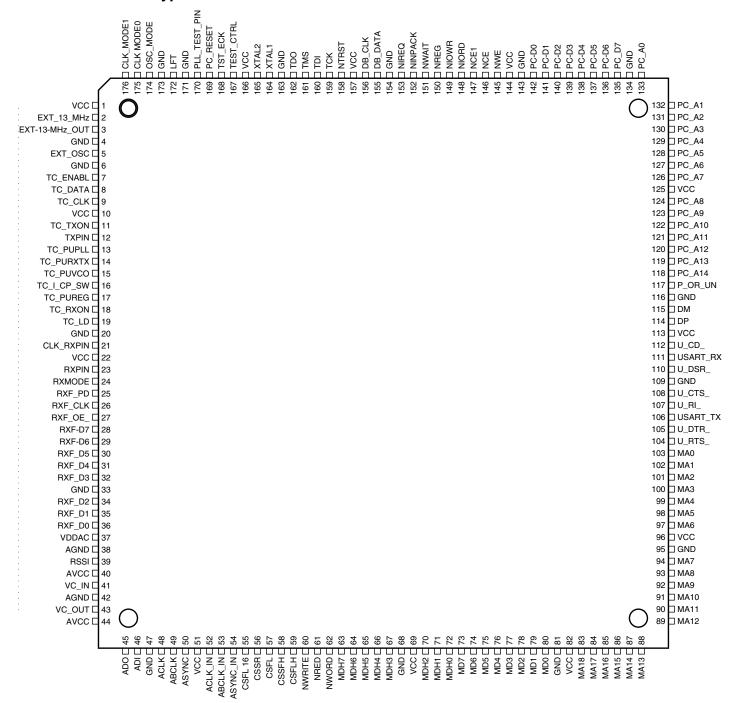

## **Pinout and Package Options**

The AT76C551 controller will be available in three different packages, each will have the same basic functionality but with a different system interface (PCMCIA 8-bit, full-speed USB, extended speed RS-232). The prototype version comes in a LQFP-176 package and supports the three different interfaces simultaneously.

#### **Pinout of the Prototype Version**

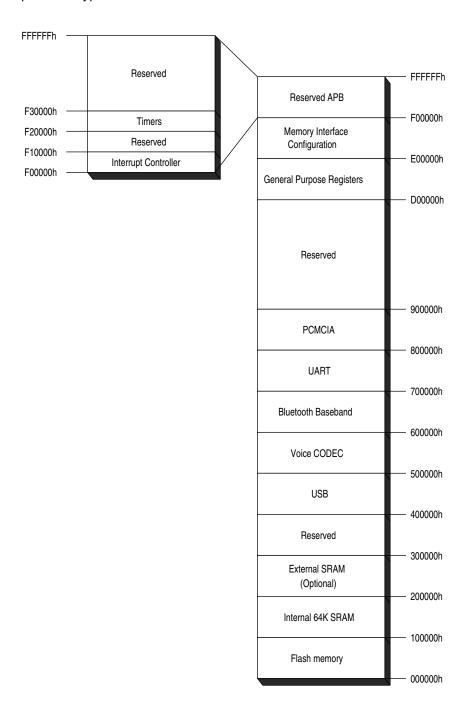

# Pin Summary – Pin Assignment in Numerical Order

| Pin # | Pin Name       | Туре           |

|-------|----------------|----------------|

| 1     | VCC            | Digital Supply |

| 2     | EXT_13_MHz     | 1              |

| 3     | EXT_13_MHz_OUT | 0              |

| 4     | GND            | Digital Ground |

| 5     | EXT_OSC        | 1              |

| 6     | GND            | Digital Ground |

| 7     | TC_ENABL       | 0              |

| 8     | TC_DATA        | 0              |

| 9     | TC_CLK         | 0              |

| 10    | VCC            | Digital Supply |

| 11    | TC_TXON        | 0              |

| 12    | TXPIN          | 0              |

| 13    | TC_PUPLL       | 0              |

| 14    | TC_PURXTX      | 0              |

| 15    | TC_PUVCO       | 0              |

| 16    | TC_I_CP_SW     | 0              |

| 17    | TC_PUREG       | 0              |

| 18    | TC_RXON        | 0              |

| 19    | TC_LD          | 1              |

| 20    | GND            | Digital Ground |

| 21    | CLK_PXPIN      | 1              |

| 22    | VCC            | Digital Supply |

| 23    | RXPIN          | 1              |

| 24    | RXMODE         | 1              |

| 25    | RXF_PD         | 0              |

| 26    | RXF_CLK        | 0              |

| 27    | RXF_OE_        | 0              |

| 28    | RXF_D7         | 1              |

| 29    | RXF_D6         | 1              |

| 30    | RXF_D5         | I              |

| 31    | RXF_D4         | 1              |

| 32    | RXF_D3         | 1              |

| 33    | GND            | Digital Ground |

| 34    | RXF_D2         | 1              |

| 35    | RXF_D1         | 1              |

| 36    | RXF_D0         | 1              |

| 37    | VDDAC          |                |

| 1 | ent ii | n Numerica | l Order        |

|---|--------|------------|----------------|

|   | Pin #  | Pin Name   | Туре           |

| Ī | 38     | AGND       | Analog Ground  |

| Ī | 39     | RSSI       | I              |

| Ī | 40     | AVCC       |                |

| Ī | 41     | VC_IN      | LOG 1          |

| Ī | 42     | AGND       | Analog Ground  |

| ĺ | 43     | VC_OUT     | LOG O          |

| Ī | 44     | AVCC       |                |

| Ī | 45     | ADO        | 0              |

| ĺ | 46     | ADI        | I              |

| Ī | 47     | GND        | Digital Ground |

| ĺ | 48     | ACLK       | 0              |

| ĺ | 49     | ABCLK      | 0              |

| ĺ | 50     | ASYNC      | 0              |

| ĺ | 51     | VCC        | Digital Supply |

| ĺ | 52     | ACLK_IN    | ı              |

| Ī | 53     | ABCLK_IN   | I              |

| Ì | 54     | ASYNC_IN   | 1              |

| Ī | 55     | CSFL16     | 0              |

| Ī | 56     | CSSR       | 0              |

| Ī | 57     | CSFL       | 0              |

| Ī | 58     | CSSFH      |                |

| Ī | 59     | CSFLH      | 0              |

| Ī | 60     | NWRITE     | 0              |

| Ī | 61     | NRED       |                |

| Ī | 62     | NWORD      | I              |

| Ī | 63     | MEM_DATAH7 | В              |

| Ī | 64     | MEM_DATAH6 | В              |

| Ī | 65     | MEM_DATAH5 | В              |

| Ī | 66     | MEM_DATAH4 | В              |

| Ī | 67     | MEM_DATAH3 | В              |

| Ī | 68     | GND        | Digital Ground |

| İ | 69     | VCC        | Digital Supply |

| İ | 70     | MEM_DATAH2 | В              |

| İ | 71     | MEM_DATAH1 | В              |

| Ī | 72     | MEM_DATAH0 | В              |

| Ī | 73     | MEM_DATA7  | В              |

| Ī | 74     | MEM_DATA6  | В              |

| - |        |            |                |

| Pin # | Pin Name   | Туре           |

|-------|------------|----------------|

| 75    | MEM_DATA5  | В              |

| 76    | MEM_DATA4  | В              |

| 77    | MEM_DATA3  | В              |

| 78    | MEM_DATA2  | В              |

| 79    | MEM_DATA1  | В              |

| 80    | MEM_DATA0  | В              |

| 81    | GND        | Digital Ground |

| 82    | VCC        | Digital Supply |

| 83    | MEM_ADDR18 | 0              |

| 84    | MEM_ADDR17 | 0              |

| 85    | MEM_ADDR16 | 0              |

| 86    | MEM_ADDR15 | 0              |

| 87    | MEM_ADDR14 | 0              |

| 88    | MEM_ADDR13 | 0              |

| 89    | MEM_ADDR12 | 0              |

| 90    | MEM_ADDR11 | 0              |

| 91    | MEM_ADDR10 | 0              |

| 92    | MEM_ADDR9  | 0              |

| 93    | MEM_ADDR8  | 0              |

| 94    | MEM_ADDR7  | 0              |

| 95    | GND        | Digital Ground |

| 96    | vcc        | Digital Supply |

| 97    | MEM_ADDR6  | 0              |

| 98    | MEM_ADDR5  | 0              |

| 99    | MEM_ADDR4  | 0              |

| 100   | MEM_ADDR3  | 0              |

| 101   | MEM_ADDR2  | 0              |

| 102   | MEM_ADDR1  | 0              |

| 103   | MEM_ADDR0  | 0              |

| 104   | U_RTS_     | 0              |

| 105   | U_DTR_     | 0              |

| 106   | USART_TX   | 0              |

| 107   | U_RI_      | 1              |

| 108   | U_CTS_     | 1              |

| 109   | GND        | Digital Ground |

| 110   | U_DSR_     | 1              |

|       | 1          | 1              |

USART\_RX

# Pin Summary – Pin Assignment in Numerical Order (Continued)

|       | =        | _              |

|-------|----------|----------------|

| Pin # | Pin Name | Туре           |

| 112   | U_CD_    | I              |

| 113   | VCC      | Digital Supply |

| 114   | DP       | В              |

| 115   | DM       | В              |

| 116   | GND      | Digital Ground |

| 117   | P_OR_UN  | 1              |

| 118   | PC_A14   | I              |

| 119   | PC_A13   | I              |

| 120   | PC_A12   | I              |

| 121   | PC_A11   | I              |

| 122   | PC_A10   | I              |

| 123   | PC_A9    | I              |

| 124   | PC_A8    | I              |

| 125   | VCC      | Digital Supply |

| 126   | PC_A7    | I              |

| 127   | PC_A6    | I              |

| 128   | PC_A5    | I              |

| 129   | PC_A4    | I              |

| 130   | PC_A3    | I              |

| 131   | PC_A2    | I              |

| 132   | PC_A1    | I              |

| 133   | PC_A0    | 1              |

| Pin # | Pin Name | Туре           |

|-------|----------|----------------|

| 134   | GND      | Digital Ground |

| 135   | PC_D7    | В              |

| 136   | PC_D6    | В              |

| 137   | PC_D5    | В              |

| 138   | PC_D4    | В              |

| 139   | PC_D3    | В              |

| 140   | PC_D2    | В              |

| 141   | PC_D1    | В              |

| 142   | PC_D0    | В              |

| 143   | GND      | Digital Ground |

| 144   | vcc      | Digital Supply |

| 145   | NWE      | 1              |

| 146   | NCE      |                |

| 147   | NCE1     | 1              |

| 148   | NIORD    | 1              |

| 149   | NIOWR    | I              |

| 150   | NREG     | I              |

| 151   | NWAIT    | 0              |

| 152   | NINPACK  | 0              |

| 153   | NIREQ    |                |

| 154   | GND      | Digital Ground |

| 155   | DB_DATA  | 0              |

| Pin # | Pin Name     | Туре           |

|-------|--------------|----------------|

| 156   | DB_CLK       | 0              |

| 157   | vcc          | Digital Supply |

| 158   | NTRST        | I              |

| 159   | TCK          | 1              |

| 160   | TDI          | I              |

| 161   | TMS          | I              |

| 162   | TDO          | I              |

| 163   | GND          | Digital Ground |

| 164   | XTAL1        | I              |

| 165   | XTAL2        | I              |

| 166   | vcc          | Digital Supply |

| 167   | TEST_CTRL    | I              |

| 168   | TST_ECK      | I              |

| 169   | PC_RESET     | I              |

| 170   | PLL_TEST_PIN | I              |

| 171   | GND          | Digital Ground |

| 172   | LFT          |                |

| 173   | GND          | Digital Ground |

| 174   | OSC_MODE     |                |

| 175   | CLK_MODE0    |                |

| 176   | CLK_MODE1    |                |

|       |              |                |

# Pin Summary – Pin Assignment in Alphabetical Order

| Pin # | Pin Name       | Туре           |

|-------|----------------|----------------|

| 49    | ABCLK          | 0              |

| 53    | ABCLK_IN       | I              |

| 48    | ACLK           | 0              |

| 52    | ACLK_IN        | I              |

| 46    | ADI            | I              |

| 45    | ADO            | 0              |

| 38    | AGND           | Analog Ground  |

| 42    | AGND           | Analog Ground  |

| 50    | ASYNC          | 0              |

| 54    | ASYNC_IN       | 1              |

| 40    | AVCC           |                |

| 44    | AVCC           |                |

| 175   | CLK_MODE0      |                |

| 176   | CLK_MODE1      |                |

| 21    | CLK_PXPIN      | I              |

| 57    | CSFL           | 0              |

| 55    | CSFL16         | 0              |

| 59    | CSFLH          | 0              |

| 58    | CSSFH          |                |

| 56    | CSSR           | 0              |

| 156   | DB_CLK         | 0              |

| 155   | DB_DATA        | 0              |

| 115   | DM             | В              |

| 114   | DP             | В              |

| 2     | EXT_13_MHz     | I              |

| 3     | EXT_13_MHz_OUT | 0              |

| 5     | EXT_OSC        | 1              |

| 4     | GND            | Digital Ground |

| 6     | GND            | Digital Ground |

| 20    | GND            | Digital Ground |

| 33    | GND            | Digital Ground |

| 116   | GND            | Digital Ground |

| 47    | GND            | Digital Ground |

| 68    | GND            | Digital Ground |

| 134   | GND            | Digital Ground |

| 143   | GND            | Digital Ground |

| 154   | GND            | Digital Ground |

| 7 | 111 1111 | Aiphabelic | ai Order       |

|---|----------|------------|----------------|

|   | Pin #    | Pin Name   | Туре           |

|   | 81       | GND        | Digital Ground |

|   | 95       | GND        | Digital Ground |

|   | 109      | GND        | Digital Ground |

|   | 163      | GND        | Digital Ground |

|   | 171      | GND        | Digital Ground |

|   | 173      | GND        | Digital Ground |

|   | 172      | LFT        |                |

|   | 103      | MEM_ADDR0  | 0              |

|   | 102      | MEM_ADDR1  | 0              |

|   | 91       | MEM_ADDR10 | 0              |

|   | 90       | MEM_ADDR11 | 0              |

|   | 89       | MEM_ADDR12 | 0              |

|   | 88       | MEM_ADDR13 | 0              |

|   | 87       | MEM_ADDR14 | 0              |

|   | 86       | MEM_ADDR15 | 0              |

|   | 85       | MEM_ADDR16 | 0              |

|   | 84       | MEM_ADDR17 | 0              |

|   | 83       | MEM_ADDR18 | 0              |

|   | 101      | MEM_ADDR2  | 0              |

|   | 100      | MEM_ADDR3  | 0              |

|   | 99       | MEM_ADDR4  | 0              |

|   | 98       | MEM_ADDR5  | 0              |

|   | 97       | MEM_ADDR6  | 0              |

|   | 94       | MEM_ADDR7  | 0              |

|   | 93       | MEM_ADDR8  | 0              |

|   | 92       | MEM_ADDR9  | 0              |

|   | 80       | MEM_DATA0  | В              |

|   | 79       | MEM_DATA1  | В              |

|   | 78       | MEM_DATA2  | В              |

|   | 77       | MEM_DATA3  | В              |

|   | 76       | MEM_DATA4  | В              |

|   | 75       | MEM_DATA5  | В              |

|   | 74       | MEM_DATA6  | В              |

|   | 73       | MEM_DATA7  | В              |

|   | 72       | MEM_DATAH0 | В              |

|   | 71       | MEM_DATAH1 | В              |

|   | 70       | MEM_DATAH2 | В              |

|   |          | ·          |                |

| Pin Name   | Туре                                                                                                                                                                                                                                                  |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MEM_DATAH3 | В                                                                                                                                                                                                                                                     |

| MEM_DATAH4 | В                                                                                                                                                                                                                                                     |

| MEM_DATAH5 | В                                                                                                                                                                                                                                                     |

| MEM_DATAH6 | В                                                                                                                                                                                                                                                     |

| MEM_DATAH7 | В                                                                                                                                                                                                                                                     |

| NCE        |                                                                                                                                                                                                                                                       |

| NCE1       | 1                                                                                                                                                                                                                                                     |

| NINPACK    | 0                                                                                                                                                                                                                                                     |

| NIORD      | 1                                                                                                                                                                                                                                                     |

| NIOWR      | 1                                                                                                                                                                                                                                                     |

| NIREQ      |                                                                                                                                                                                                                                                       |

| NRED       |                                                                                                                                                                                                                                                       |

| NREQ       | I                                                                                                                                                                                                                                                     |

| NTRST      | 1                                                                                                                                                                                                                                                     |

| NWAIT      | 0                                                                                                                                                                                                                                                     |

| NWE        | I                                                                                                                                                                                                                                                     |

| NWORD      | 1                                                                                                                                                                                                                                                     |

| NWRITE     | 0                                                                                                                                                                                                                                                     |

| OSC_MODE   |                                                                                                                                                                                                                                                       |

| P_OR_UN    | ı                                                                                                                                                                                                                                                     |

| PC_A0      | I                                                                                                                                                                                                                                                     |

| PC_A1      | I                                                                                                                                                                                                                                                     |

| PC_A10     | 1                                                                                                                                                                                                                                                     |

| PC_A11     | 1                                                                                                                                                                                                                                                     |

| PC_A12     | 1                                                                                                                                                                                                                                                     |

| PC_A13     | ı                                                                                                                                                                                                                                                     |

| PC_A14     | I                                                                                                                                                                                                                                                     |

| PC_A2      | I                                                                                                                                                                                                                                                     |

| PC_A3      | ı                                                                                                                                                                                                                                                     |

| PC_A4      | I                                                                                                                                                                                                                                                     |

| PC_A5      | 1                                                                                                                                                                                                                                                     |

| PC_A6      | I                                                                                                                                                                                                                                                     |

| PC_A7      | I                                                                                                                                                                                                                                                     |

| PC_A8      | I                                                                                                                                                                                                                                                     |

| PC_A9      | 1                                                                                                                                                                                                                                                     |

| PC_D0      | В                                                                                                                                                                                                                                                     |

|            | MEM_DATAH3 MEM_DATAH4 MEM_DATAH5 MEM_DATAH6 MEM_DATAH7 NCE NCE1 NINPACK NIORD NIOWR NIREQ NRED NRED NRED NWAIT NWE NWORD NWRITE OSC_MODE P_OR_UN PC_A0 PC_A1 PC_A10 PC_A11 PC_A12 PC_A13 PC_A14 PC_A2 PC_A3 PC_A4 PC_A5 PC_A6 PC_A7 PC_A8 PC_A8 PC_A8 |

PC\_D1

В

# Pin Summary – Pin Assignment in Alphabetical Order (Continued)

| Pin # | Pin Name     | Туре |

|-------|--------------|------|

| 140   | PC_D2        | В    |

| 139   | PC_D3        | В    |

| 138   | PC_D4        | В    |

| 137   | PC_D5        | В    |

| 136   | PC_D6        | В    |

| 135   | PC_D7        | В    |

| 169   | PC_RESET     | 1    |

| 170   | PLL_TEST_PIN | 1    |

| 39    | RSSI         | I    |

| 26    | RXF_CLK      | 0    |

| 36    | RXF_D0       | 1    |

| 35    | RXF_D1       | 1    |

| 34    | RXF_D2       | 1    |

| 32    | RXF_D3       | 1    |

| 31    | RXF_D4       | I    |

| 30    | RXF_D5       | 1    |

| 29    | RXF_D6       | 1    |

| 28    | RXF_D7       | I    |

| 27    | RXF_OE_      | 0    |

| 25    | RXF_PD       | 0    |

| 24    | RXMODE       | I    |

| 23    | RXPIN        | I    |

| Pin # | Pin Name   | Туре |

|-------|------------|------|

| 9     | TC_CLK     | 0    |

| 8     | TC_DATA    | 0    |

| 7     | TC_ENABL   | 0    |

| 16    | TC_I_CP_SW | 0    |

| 19    | TC_LD      | 1    |

| 13    | TC_PUPLL   | 0    |

| 17    | TC_PUREG   | 0    |

| 14    | TC_PURXTX  | 0    |

| 15    | TC_PUVCO   | 0    |

| 18    | TC_RXON    | 0    |

| 11    | TC_TXON    | 0    |

| 159   | TCK        | 1    |

| 160   | TDI        | 1    |

| 162   | TDO        | 1    |

| 167   | TEST_CTRL  | 1    |

| 161   | TMS        | 1    |

| 168   | TST_ECK    | 1    |

| 12    | TXPIN      | 0    |

| 112   | U_CD_      | 1    |

| 108   | U_CTS_     | 1    |

| 110   | U_DSR_     | 1    |

| 105   | U_DTR_     | 0    |

| Pin # | Pin Name | Туре           |

|-------|----------|----------------|

| 107   | U_RI_    | 1              |

| 104   | U_RTS_   | 0              |

| 111   | USART_RX | I              |

| 106   | USART_TX | 0              |

| 41    | VC_IN    | LOG 1          |

| 43    | VC_OUT   | LOG O          |

| 1     | VCC      | Digital Supply |

| 10    | VCC      | Digital Supply |

| 22    | VCC      | Digital Supply |

| 113   | VCC      | Digital Supply |

| 125   | VCC      | Digital Supply |

| 51    | VCC      | Digital Supply |

| 69    | VCC      | Digital Supply |

| 144   | VCC      | Digital Supply |

| 82    | VCC      | Digital Supply |

| 96    | VCC      | Digital Supply |

| 157   | VCC      | Digital Supply |

| 166   | VCC      | Digital Supply |

| 37    | VDDAC    |                |

| 164   | XTAL1    | I              |

| 165   | XTAL2    | I              |

|       |          |                |

# **Signal Description – Pin Name Order**

| Pin Name                | Туре       | Description                                                                                                                                                             |  |

|-------------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Supply Pins             | !          |                                                                                                                                                                         |  |

| AGND                    | Power      | Analog Ground                                                                                                                                                           |  |

| AVCC                    | Power      | Analog Supply                                                                                                                                                           |  |

| GND                     | Power      | Digital Ground                                                                                                                                                          |  |

| VCC                     | Power      | Digital Supply                                                                                                                                                          |  |

| Global Pin              |            |                                                                                                                                                                         |  |

| PC_RESET                | I          | Global Reset pin                                                                                                                                                        |  |

| Oscillator Pins         |            |                                                                                                                                                                         |  |

| XTAL1                   | I          | Crystal oscillator input                                                                                                                                                |  |

| XATL2                   | 0          | Crystal oscillator output                                                                                                                                               |  |

| EXT_13_MHZ              | I          | 13 MHz input clock                                                                                                                                                      |  |

| EXT_13_MHZ_OUT          | 0          | 13 MHz output clock                                                                                                                                                     |  |

| EXT_OSC                 | I          | External oscillator input                                                                                                                                               |  |

| CLK_MODE1,<br>CLK_MODE0 | I          | Clock Frequency Configuration                                                                                                                                           |  |

| OSC_MODE                | I          | Internal/Extenal Clock Selector                                                                                                                                         |  |

| LFT                     | PLL Filter | PLL loop filter pin                                                                                                                                                     |  |

| Memory Interface Pins   |            |                                                                                                                                                                         |  |

| CSFL16                  | 0          | Chip select when 16-bit Flash is used                                                                                                                                   |  |

| CSSR                    | 0          | Chip select for low byte 8-bit SRAM                                                                                                                                     |  |

| CSFL                    | 0          | Chip select for low byte Flash                                                                                                                                          |  |

| CSSRH                   | 0          | Chip select for high byte SRAM                                                                                                                                          |  |

| CSFLH                   | 0          | Chip select for high byte Flash                                                                                                                                         |  |

| NWRITE                  | 0          | Memory write                                                                                                                                                            |  |

| NREAD                   | 0          | Memory read                                                                                                                                                             |  |

| NWORD                   | I          | Selects between 8 and 16 memory access                                                                                                                                  |  |

| MEM_ADDR [18:0]         | 0          | Memory Address Bus – Signals MEM_ADDR [18:0] are address-bus output lines of Flash and SRAM.                                                                            |  |

| MEM_DATA [7:0]          | В          | Memory Data Bus – Signals MEM_DATA [7:0] are the bi-directional data bus lines for the SRAM and Flash memory.                                                           |  |

| MEM_DATAH [7:0]         | В          | Memory Data Bus – Signals MEM_DATAH [7:0] are the bi-directional data bus lines for the SRAM and Flash memory. These lines are used during 16-bit memory configuration. |  |

| P_OR_UN                 | I          | Selects whether PCMCIA or USB will have direct access to the memories. When "1" PCMCIA has direct access while when "0" USB has access                                  |  |

# **Signal Description – Pin Name Order (Continued)**

| Pin Name                | Туре | Description                                                                                                                                                                                             |  |

|-------------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Baseband Interface Pins | s    |                                                                                                                                                                                                         |  |

| TC_CLK                  | 0    | Clock output for transceiver control bus                                                                                                                                                                |  |

| TC_DATA                 | 0    | Data output for transceiver control bus                                                                                                                                                                 |  |

| TC_ENBL                 | 0    | Enable output for transceiver control bus                                                                                                                                                               |  |

| TC_LD                   | I    | Lock detect input                                                                                                                                                                                       |  |

| TC_PU_REG               | 0    | Transceiver voltage regulator power up                                                                                                                                                                  |  |

| TC_PU_PLL               | 0    | Power up output for transceiver PLL                                                                                                                                                                     |  |

| TC_PU_VCO               | 0    | VCO power up output                                                                                                                                                                                     |  |

| TC_PU_RXTX              | 0    | Power up output for Transmit/Receive sections of transceiver                                                                                                                                            |  |

| TC_RX_ON                | 0    | RX section power up control output                                                                                                                                                                      |  |

| TC_TX_ON                | 0    | TX section power up control output                                                                                                                                                                      |  |

| TC_I_CP_SW              | 0    | Transceiver Current Pump external switch signal                                                                                                                                                         |  |

| RSSI                    | I    | Receive signal strength indicator input from transceiver                                                                                                                                                |  |

| TXPIN                   | 0    | Transmit data output to transceiver                                                                                                                                                                     |  |

| RXPIN                   | I    | Receive data input from transceiver                                                                                                                                                                     |  |

| CLK_RXPIN               | I    | Clock driven to internal RxFront module                                                                                                                                                                 |  |

| RX_MODE                 | I    | If "0", internal clock recovery enabled and data extracted from external A/D. If "1" only E packet processing carried out. Clock generation and recovery must be carried out externally                 |  |

| RXF_PD                  | 0    | Power Down signal for external A/D                                                                                                                                                                      |  |

| RXF_CLK                 | 0    | Clock driven to external A/D                                                                                                                                                                            |  |

| RXF_OE_                 | 0    | Output enable signal for external A/D                                                                                                                                                                   |  |

| RXF_D[7:0]              | I    | A/D RXF_D[7:0] output bus                                                                                                                                                                               |  |

| PCMCIA Interface Pins   |      |                                                                                                                                                                                                         |  |

| PC_A[14:0]              | I    | Address Bus – Signals A0 through A14 are address-bus input lines. Signal A0 is always used since the data interface is 8 bits wide.                                                                     |  |

| PC_D[7:0]               | В    | Data Bus – Signals D7 through D0 are the bi-directional data bus for PCMCIA. The most significant bit is D7.                                                                                            |  |

| NWE                     | I    | Write Enable – Used to strobe memory write data into the chip from the PCMCIA data bus Should be deasserted during memory read cycles. It is used for both Common memory and Attribute memory accesses. |  |

| NOE                     | I    | Output Enable – Active low output enable signal. It is used to gate memory read data from the BT device onto PCMCIA data bus. It is used for Common memory accesses and Attribute memory Accesses.      |  |

| NCE1                    | I    | Card Enable – Used to enable even-numbered word address bytes. A0 is used to select between the even and odd number bytes within the addressed word                                                     |  |

# **Signal Description – Pin Name Order (Continued)**

| Pin Name                   | Туре  | Description                                                                                                                                                                                                                                                                                               |  |

|----------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NIORD                      | I     | I/O Read – Asserted by the host system to indicate to BT that a read from the I/O address space is required. The chip will not respond until it has been configured for I/O operation by the system.                                                                                                      |  |

| NIOWR                      | I     | I/O Write – Asserted by the host system to indicate to the chip that a write to its I/O address space is required. The device will not respond until it has been configured for I/O operation by the system.                                                                                              |  |

| NREG                       | I     | Attribute Memory Select – Driven by the host to select between Attribute memory or I/O space (REG asserted) and Common memory (REG deasserted) in the device and the PCMCIA card.                                                                                                                         |  |

| NWAIT                      | 0     | Extend Bus Cycle – This signal is asserted by the device to delay completion of the access cycle currently in progress.                                                                                                                                                                                   |  |

| NINPACK                    | 0     | Input Acknowledge – It is asserted when the BT device is selected and can respond to an I/O read cycle at the address currently applied on the address bus. It is used by the host to control the enable of any input buffer between the card and the CPU. It will be inactive during card configuration. |  |

| NIREQ                      | 0     | Interrupt Request – Asserted by the chip to indicate to the host that software service should take place.                                                                                                                                                                                                 |  |

| <b>UART Interface Pins</b> |       |                                                                                                                                                                                                                                                                                                           |  |

| U_CTS_                     | I     | Clear To Send                                                                                                                                                                                                                                                                                             |  |

| U_DSR_                     | I     | Data Set Ready                                                                                                                                                                                                                                                                                            |  |

| U_DTR_                     | 0     | Data Terminal Ready                                                                                                                                                                                                                                                                                       |  |

| U_RI_                      | I     | Ring Indicator                                                                                                                                                                                                                                                                                            |  |

| U_RTS_                     | 0     | Request To Send                                                                                                                                                                                                                                                                                           |  |

| USART_RX                   | I     | Serial Input Port                                                                                                                                                                                                                                                                                         |  |

| USART_TX                   | 0     | Serial Output Port                                                                                                                                                                                                                                                                                        |  |

| U_CD_                      | 1     | Carrier Detect                                                                                                                                                                                                                                                                                            |  |

| USB Interface Pins         |       |                                                                                                                                                                                                                                                                                                           |  |

| DP                         | В     | Upstream Plus USB I/O. This pin should be connected to CEXT through an external $1.5 \text{ k}\Omega$ pull-up resistor. DPLUS and DMINUS form the differential signal pin pairs connected to the Host Controller or an upstream Hub.                                                                      |  |

| DM                         | В     | Upstream Minus USB I/O                                                                                                                                                                                                                                                                                    |  |

| Analog Voice CODEC Pi      | ns    |                                                                                                                                                                                                                                                                                                           |  |

| VC_IN                      | LOG I | Voice Input                                                                                                                                                                                                                                                                                               |  |

| VC_OUT                     | LOG O | Voice Output                                                                                                                                                                                                                                                                                              |  |

| Digital Voice CODEC Pin    | ıs    |                                                                                                                                                                                                                                                                                                           |  |

| ADO                        | 0     | Data Transmit                                                                                                                                                                                                                                                                                             |  |

| ADI                        | I     | Data Receive                                                                                                                                                                                                                                                                                              |  |

| ACLK                       | 0     | Master Clock - Out                                                                                                                                                                                                                                                                                        |  |

| ABCLK                      | 0     | Bit Clock - Out                                                                                                                                                                                                                                                                                           |  |

# **Signal Description – Pin Name Order (Continued)**

| Pin Name     | Туре | Description              |  |

|--------------|------|--------------------------|--|

| ASYNC        | 0    | Frame Sync – Out         |  |

| ACLK_IN      | I    | Master Clock – In        |  |

| ABCLK_IN     | I    | Bit Clock – In           |  |

| ASYNC_IN     | I    | Frame Sync – In          |  |

| JTAG Pins    |      |                          |  |

| DB_DATA      | 0    | Debug data port          |  |

| DB_CLK       | 0    | Debug clock port         |  |

| NTRST        | I    | JTAG reset input         |  |

| TCK          | I    | JATG clock               |  |

| TDI          | 1    | JTAG data input          |  |

| TDO          | I    | JTAG data output         |  |

| TMS          | 1    | JTAG master select input |  |

| TEST Pins    |      |                          |  |

| TEST_CTRL    | I    | For production test      |  |

| TEST_ECK     | I    | For production test      |  |

| PLL_TEST_PIN | I    | For production test.     |  |

# **Functional Description – Pin Name Order**

| Name                  | Туре       | Description                                                                                                                                                            |  |  |

|-----------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Supply Pins           | •          |                                                                                                                                                                        |  |  |

| AGND                  | Power      | Analog Ground – used by the RSSI ADC, the Voice CODEC ADC and DAC                                                                                                      |  |  |

| AVCC                  | Power      | Analog Supply – used by the RSSI ADC, the Voice CODEC ADC and DAC                                                                                                      |  |  |

| GND                   | Power      | Digital Ground                                                                                                                                                         |  |  |

| VCC                   | Power      | Digital Supply                                                                                                                                                         |  |  |

| Global Pin            |            |                                                                                                                                                                        |  |  |

| PC_RESET              | I          | Global Reset Pin                                                                                                                                                       |  |  |

| Oscillator Pins       |            |                                                                                                                                                                        |  |  |

| XTAL1                 | I          | Crystal oscillator input                                                                                                                                               |  |  |

| XATL2                 | 0          | Crystal oscillator output                                                                                                                                              |  |  |

| EXT_13_MHZ            | I          | 13 MHz input clock                                                                                                                                                     |  |  |

| EXT_13_MHZ_OUT        | 0          | 13 MHz output clock                                                                                                                                                    |  |  |

| EXT_OSC               | I          | External oscillator input                                                                                                                                              |  |  |

| CLK_MODE1             |            | Clock Frequency Configuration (see "Support for Different Operating Frequencies")                                                                                      |  |  |

| CLK_MODE0             | I          | Clock Frequency Configuration (see "Support for Different Operating Frequencies")                                                                                      |  |  |

| OSC_MODE              | I          | Selects if the PLL will use the internal clock oscillator connected to the XTAL1, XTAL2 pin or an external clock oscillator connected to the EXT_OSC pin.              |  |  |

| LFT                   | PLL Filter | PLL loop filter pin                                                                                                                                                    |  |  |

| Memory Interface Pins |            |                                                                                                                                                                        |  |  |

| CSFL16                | 0          | Chip Select when 16-bit Flash is used                                                                                                                                  |  |  |

| CSSR                  | 0          | Chip select for low byte 8-bit SRAM                                                                                                                                    |  |  |

| CSFL                  | 0          | Chip select for low byte Flash                                                                                                                                         |  |  |

| CSSRH                 | 0          | Chip select for high byte SRAM                                                                                                                                         |  |  |

| CSFLH                 | 0          | Chip select for high byte Flash                                                                                                                                        |  |  |

| NWRITE                | 0          | Memory write                                                                                                                                                           |  |  |

| NREAD                 | 0          | Memory read                                                                                                                                                            |  |  |

| NWORD                 | I          | Selects between 8 and 16 memory access                                                                                                                                 |  |  |

| MEM_ADDR [18:0]       | 0          | Memory Address Bus – Signals MEM_ADDR [18:0] are address-bus output lines of Flash and SRAM.                                                                           |  |  |

| MEM_DATA [7:0]        | В          | Memory Data Bus – Signals MEM_DATA [7:0] are the bi-directional data bus lines for the SRAM and Flash memory.                                                          |  |  |

| MEM_DATAH [7:0]       | В          | Memory Data Bus – Signals MEM_DATAH [7:0] are the bi-directional data bus lines for the SRAM and Flash memory. These lines are used during 16-bit memory configuration |  |  |

| P_OR_UN               | I          | Selects whether PCMCIA or USB will have direct access to the memories When "1" PCMCIA has direct access while when "0" USB has access                                  |  |  |

# **Functional Description – Pin Name Order (Continued)**

| Name                    | Туре | Description                                                                                                                                                                                            |  |

|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Baseband Interface Pins |      | 1                                                                                                                                                                                                      |  |

| TC_CLK                  | 0    | Clock output for transceiver control bus                                                                                                                                                               |  |

| TC_DATA                 | 0    | Data output for transceiver control bus                                                                                                                                                                |  |

| TC_ENBL                 | 0    | Enable output for transceiver control bus                                                                                                                                                              |  |

| TC_LD                   | I    | Lock detect input                                                                                                                                                                                      |  |

| TC_PUREG                | 0    | Transceiver voltage regulator power up                                                                                                                                                                 |  |

| TC_PUPLL                | 0    | Power up output for transceiver PLL                                                                                                                                                                    |  |

| TC_PUVCO                | 0    | VCO power up output                                                                                                                                                                                    |  |

| TC_PURXTX               | 0    | Power up output for Transmit/Receive sections of transceiver                                                                                                                                           |  |

| TC_RXON                 | 0    | RX section power up control output                                                                                                                                                                     |  |

| TC_TXON                 | 0    | TX section power up control output                                                                                                                                                                     |  |

| TC_I_CP_SW              | 0    | Transceiver Current Pump external switch signal                                                                                                                                                        |  |

| RSSI                    | I    | Receive signal strength indicator input from transceiver                                                                                                                                               |  |

| TXPIN                   | 0    | Transmit data output to transceiver                                                                                                                                                                    |  |

| RXPIN                   | I    | Receive data input from transceiver                                                                                                                                                                    |  |

| CLK_RXPIN               | I    | Clock driven to internal RxFront module                                                                                                                                                                |  |

| RXMODE                  | I    | If "0", internal clock recovery enabled and data extracted from external A/D. If "1" only packet processing carried out. Clock generation and recovery must be carried out externally.                 |  |

| RXF_PD                  | 0    | Power Down signal for external A/D                                                                                                                                                                     |  |

| RXF_CLK                 | 0    | Clock driven to external A/D                                                                                                                                                                           |  |

| RXF_OE_                 | 0    | Output enable signal for external A/D                                                                                                                                                                  |  |

| RXF_D[7:0]              | I    | A/D RXF_D[7:0] output bus                                                                                                                                                                              |  |

| PCMCIA Interface Pins   |      |                                                                                                                                                                                                        |  |

| PC_A[14:0]              | I    | Address Bus – Signals A0 through A14 are address-bus input lines. Signal A0 is always used since the data interface is 8-bits wide.                                                                    |  |

| PC_D[7:0]               | В    | Data Bus – Signals D7 through D0 are the bi-directional data bus for PCMCIA. The most significant bit is D7.                                                                                           |  |

| NWE                     | I    | Write Enable – Used to strobe memory write data into the chip from the PCMCIA data bus Should be deasserted during memory read cycles. It is used for both Common memory an Attribute memory accesses. |  |

| NOE                     | 1    | Output Enable – Active low output enable signal. It is used to gate memory read data from the BT device onto PCMCIA data bus. It is used for Common memory accesses and Attribute memory Accesses.     |  |

| NCE1                    | I    | Card Enable – Used to enable even-numbered word address bytes. A0 is used to select between the even and odd number bytes within the addressed word                                                    |  |

| NIORD                   | 1    | I/O Read – Asserted by the host system to indicate to BT that a read from the I/O address space is required. The chip will not respond until it has been configured for I/O operation by the system.   |  |

# **Functional Description – Pin Name Order (Continued)**

| Name                    | Туре  | Description                                                                                                                                                                                                                                                                                               |  |

|-------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NIOWR                   | I     | I/O Write – Asserted by the host system to indicate to the chip that a write to its I/O address space is required. The device will not respond until it has been configured for I/O operation by the system.                                                                                              |  |

| NREG                    | 1     | Attribute Memory Select – Driven by the host to select between Attribute memory or I/O space (REG asserted) and Common memory (REG deasserted) in the device and the PCMCIA card.                                                                                                                         |  |

| NWAIT                   | 0     | Extend Bus Cycle – This signal is asserted by the device to delay completion of the access cycle currently in progress.                                                                                                                                                                                   |  |

| NINPACK                 | 0     | Input Acknowledge – It is asserted when the BT device is selected and can respond to an I/O read cycle at the address currently applied on the address bus. It is used by the host to control the enable of any input buffer between the card and the CPU. It will be inactive during card configuration. |  |

| NIREQ                   | 0     | Interrupt Request – Asserted by the chip to indicate to the host that software service should take place.                                                                                                                                                                                                 |  |

| UART Interface Pins     |       |                                                                                                                                                                                                                                                                                                           |  |

| U_CTS_                  | I     | Clear to Send                                                                                                                                                                                                                                                                                             |  |

| U_DSR_                  | I     | Data Set Ready                                                                                                                                                                                                                                                                                            |  |

| U_DTR_                  | 0     | Data Terminal Ready                                                                                                                                                                                                                                                                                       |  |

| U_RI_                   | I     | Ring Indicator                                                                                                                                                                                                                                                                                            |  |

| U_RTS_                  | 0     | Request to Send                                                                                                                                                                                                                                                                                           |  |

| USART_RX                | I     | Serial input port                                                                                                                                                                                                                                                                                         |  |

| USART_TX                | 0     | Serial output port                                                                                                                                                                                                                                                                                        |  |

| U_CD_                   | I     | Carrier Detect                                                                                                                                                                                                                                                                                            |  |

| USB Interface Pins      |       |                                                                                                                                                                                                                                                                                                           |  |

| DP                      | В     | Upstream Plus USB I/O. This pin should be connected to CEXT through an external 1.5 k $\Omega$ pull-up resistor. DPLUS and DMINUS form the differential signal pin pairs connected to the Host Controller or an upstream Hub.                                                                             |  |

| DM                      | В     | Upstream Minus USB I/O                                                                                                                                                                                                                                                                                    |  |

| Analog Voice CODEC Pin  | S     |                                                                                                                                                                                                                                                                                                           |  |

| VC_IN                   | LOG I | Voice input                                                                                                                                                                                                                                                                                               |  |

| VC_OUT                  | LOG O | Voice output                                                                                                                                                                                                                                                                                              |  |

| Digital Voice CODEC Pir | ns    |                                                                                                                                                                                                                                                                                                           |  |

| ADO                     | 0     | Data Transmit                                                                                                                                                                                                                                                                                             |  |

| ADI                     | I     | Data Receive                                                                                                                                                                                                                                                                                              |  |

| ACLK                    | 0     | Master Clock – Out                                                                                                                                                                                                                                                                                        |  |

| ABCLK                   | 0     | Bit clock - Out                                                                                                                                                                                                                                                                                           |  |

| ASYNC                   | 0     | Frame Sync – Out                                                                                                                                                                                                                                                                                          |  |

| ACLK_IN                 | I     | Master Clock – In                                                                                                                                                                                                                                                                                         |  |