#### DDR 24-Bit to 48-Bit Registered Buffer

#### **Features**

- Differential clock signals.

- Supports SSTL\_2 class II specifications on inputs and outputs.

- Low voltage operation.

- $V_{DD} = 2.3V$  to 2.7V.

- Available in 114 ball BGA package.

Industrial temperature range also available.

#### **Product Description**

The 24-Bit to 48-Bit ASM4SSTVF32852 is a universal bus driver designed for 2.3V to 2.7V  $V_{\text{DD}}$  operation and SSTL\_2 I/O levels except for the LVCMOS RESETB input.

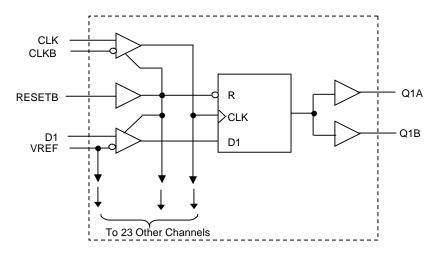

Data flow from D to Q is controlled by the differential clock (CLK/CLKB) and a control signal (RESETB). The positive edge of CLK is used to trigger the data flow, and CLKB is used to maintain sufficient noise margins, whereas the RESETB, an LVCMOS asynchronous signal is intended for use at the time of power-up only.

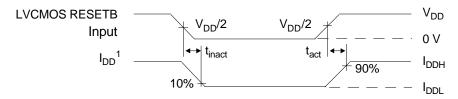

The ASM4SSTVF32852 supports a low power standby mode of operation. A logic "Low" level at RESETB, assures that all internal registers and outputs (Q) are reset to a logic "Low" state, and that all input receivers, data (D) buffers, and clock (CLK/CLKB) are switched off. Please note that RESETB must always be supported with a LVCMOS levels at a valid logic state since VREF may not be stable during power-up.

To ensure that outputs are at a defined logic state before a stable clock has been supplied, RESETB must be held at a logic "Low" level during power-up.

In the DDR DIMM application, RESETB is specified to be asynchronous with respect to CLK/CLKB. Therefore, no timing relationship can be guaranteed between the two signals. When entering a low-power standby state, the register will be cleared and the outputs will be driven to a logic "Low" level quickly relative to the time to disable the differential input receivers. This ensures there are no "glitches" on any output. However, when coming out of low power standby state, the register will become active quickly relative to the time taken to enable the differential input receivers. When the data inputs are at a logic level "Low" and the clock is stable during the "Low-to-High" transition of RESETB until the input receivers are fully enabled, the design ensures that the outputs will remain at a logic "Low" level.

#### **Applications**

- DDR Memory Modules.

- Provides complete DDR DIMM logic solution with ASM5CVF857, ASM4SSTVF16857 and ASM4SSTVF16859.

- SSTL\_2 compatible data registers.

### **Block Diagram**

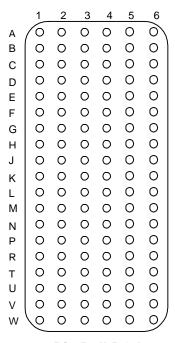

# **Pin Configurations**

114-Pin Ball BGA

# **Pin Description**

| Pin #                                                                                          | Pin Name  | Туре | Description                          |

|------------------------------------------------------------------------------------------------|-----------|------|--------------------------------------|

| R1, P1, N1, N2, M1, L2, L1, K1, K2, J2, J1, H1, G1, G2, F1, F2, E1, D1, D2, C1, C2, B1, A1, A2 | Q (24:1)A | 0    | Data output.                         |

| R6, P6, N6,N5,M6, L5, L6, K6, K5, J5, J6, H6, G6, G5, F6, F5, E6, D6, D5, C6, C5, B6, A6, A5   | Q (24:1)B | 0    | Data output.                         |

| E2, B3, D3, G3, J3, L3, M3, P3, B4, D4, G4, J4, L4, M4, P4, E5                                 | GND       | Р    | Ground.                              |

| B2, M2, P2, C3, E3, F3, H3, K3, N3, C4, E4, F4, H4, K4, N4, B5, M5, P5                         | VDDQ      | Р    | Output supply voltage, 2,5V nominal. |

| W4, V4, U4, W5, W6, V5, T4, V6, U6, U5, T6, T5, W3, V3, U3, W2, W1, V2, T3, V1, U1, U2, T1, T2 | D(24:1)   | I    | Data input.                          |

| А3                                                                                             | CLK       | I    | Positive master clock input.         |

| A4                                                                                             | CLKB      | ı    | Negative master clock input.         |

| H2, H5, R2, R5                                                                                 | VDD       | Р    | Core supply voltage, 2.5V nominal.   |

| R3                                                                                             | RESETB    | I    | Reset (Active Low).                  |

| R4                                                                                             | VREF      | I    | Input reference, 1.25V nominal.      |

rev 2.0

# **Pin Configuration Assignments**

|   | 1    | 2    | 3      | 4    | 5    | 6    |

|---|------|------|--------|------|------|------|

| А | Q2A  | Q1A  | CLK    | CLKB | Q1B  | Q2B  |

| В | Q3A  | VDDQ | GND    | GND  | VDDQ | Q3B  |

| С | Q5A  | Q4A  | VDDQ   | VDDQ | Q4B  | Q5B  |

| D | Q7A  | Q6A  | GND    | GND  | Q6B  | Q7B  |

| Е | Q8A  | GND  | VDDQ   | VDDQ | GND  | Q8B  |

| F | Q10A | Q9A  | VDDQ   | VDDQ | Q9B  | Q10B |

| G | Q12A | Q11A | GND    | GND  | Q11B | Q12B |

| Н | Q13A | VDD  | VDDQ   | VDDQ | VDD  | Q13B |

| J | Q14A | Q15A | GND    | GND  | Q15B | Q14B |

| К | Q17A | Q16A | VDDQ   | VDDQ | Q16B | Q17B |

| L | Q18A | Q19A | GND    | GND  | Q19B | Q18B |

| М | Q20A | VDDQ | GND    | GND  | VDDQ | Q20B |

| N | Q22A | Q21A | VDDQ   | VDDQ | Q21B | Q22B |

| Р | Q23A | VDDQ | GND    | GND  | VDDQ | Q23B |

| R | Q24A | VDD  | RESETB | VREF | VDD  | Q24B |

| Т | D2   | D1   | D6     | D18  | D13  | D14  |

| U | D4   | D3   | D10    | D22  | D15  | D16  |

| V | D5   | D7   | D11    | D23  | D19  | D17  |

| W | D8   | D9   | D12    | D24  | D21  | D20  |

#### Truth Table<sup>1</sup>

|        | Q Outputs     |               |               |                             |

|--------|---------------|---------------|---------------|-----------------------------|

| RESET# | CLK           | CLK#          | D             | Q                           |

| L      | X or floating | X or floating | X or floating | L                           |

| Н      | 1             | <b>\</b>      | Н             | Н                           |

| Н      | 1             | <u> </u>      | L             | L                           |

| Н      | L or H        | L or H        | Х             | Q <sub>0</sub> <sup>2</sup> |

Note: 1. H=High signal level, L=Low signal level, ↑= transition from low to high, ↓= transition from high to low, X = don't care 2. Output level before the indicated steady state input conditions were established.

## **Absolute Maximum Ratings**

| Parameter                              | Min  | Max                   | Unit |

|----------------------------------------|------|-----------------------|------|

| Storage Temperature                    | -65  | +150                  | °C   |

| Supply Voltage                         | -0.5 | 3.6                   | V    |

| Input Voltage <sup>1</sup>             | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Output Voltage <sup>1,2</sup>          | -0.5 | V <sub>DD</sub> + 0.5 | V    |

| Input Clamp Current                    | ±    | 50                    | mA   |

| Output Clamp Current                   | ±    | mA                    |      |

| Continuous Output Current              | ±:   | mA                    |      |

| VDD, VDDQ or GND current/pin           | 10   | mA                    |      |

| Package Thermal Impedance <sup>3</sup> | 5    | 5                     | °C/W |

#### Note

- 1. The input and output negative voltage ratings may be excluded if the input and output clamp ratings are observed.

- 2. This current will flow only when the output is in the high state level  $V_0 > V_{DDQ}$ .

- 3. The package thermal impedance is calculated in accordance with JESD 51.

These are stress ratings only and functional operation is not implied. Exposure to absolute maximum ratings for prolonged periods can affect device reliability.

# **Recommended Operating Conditions**

Guaranteed by design. Not 100% tested in production.

| Parameter           | Description                                    |        | Min                         | Тур       | Max                        | Unit |

|---------------------|------------------------------------------------|--------|-----------------------------|-----------|----------------------------|------|

| $V_{DD}$            | Supply voltage                                 |        | 2.3                         | 2.5       | 2.7                        | V    |

| $V_{DDQ}$           | Output supply voltage                          |        | 2.3                         | 2.5       | 2.7                        | V    |

| $V_{REF}$           | Reference voltage                              |        | 1.15                        | 1.25      | 1.35                       | V    |

| $V_{TT}$            | Termination voltage                            |        | V <sub>REF</sub> - 0.04     | $V_{REF}$ | V <sub>REF</sub> + 0.04    | V    |

| Vı                  | Input voltage                                  |        | 0                           |           | $V_{DDQ}$                  | V    |

| $V_{\text{IH(DC)}}$ | DC input high voltage                          |        | V <sub>REF</sub> + 0.15     |           |                            | V    |

| V <sub>IH(AC)</sub> | AC input high voltage                          | Data   | V <sub>REF</sub> + 0.31     |           |                            | V    |

| $V_{\text{IL}(DC)}$ | DC input low voltage                           | Inputs |                             |           | V <sub>REF</sub> - 0.15    | V    |

| $V_{\text{IL(AC)}}$ | AC input low voltage                           |        |                             |           | V <sub>REF</sub> - 0.31    | V    |

| V <sub>IH</sub>     | Input high voltage level                       | RESETB | 1.7                         |           |                            | V    |

| $V_{IL}$            | Input low voltage level                        | KLOLIB |                             |           | 0.7                        | V    |

| V <sub>ICR</sub>    | Common mode input range                        | CLK    | 0.97                        |           | 1.53                       | V    |

| $V_{\text{ID}}$     | Differential input voltage                     | CLKB   | 0.36                        |           |                            | V    |

| $V_{IX}$            | Cross-point voltage of differential clock pair |        | (V <sub>DDQ</sub> /2) - 0.2 |           | (V <sub>DDQ</sub> /2) +0.2 | V    |

| I <sub>OH</sub>     | High-level output current                      |        |                             |           | -19                        | mA   |

| I <sub>OI</sub>     | Low-level output current                       |        |                             |           | 19                         | mA   |

| T <sub>A</sub>      | Operating free-air temperature                 |        | 0                           |           | 70                         | °C   |

### **DC Electrical Characteristics**

$T_{\text{A}}$  = 0°C to 70°C,  $V_{\text{DD}}$  = 2.5  $\pm$  0.2V, and  $V_{\text{DDQ}}$  = 2.5  $\pm$  0.2V (unless otherwise stated)

Guaranteed by design. Not 100% production tested.

| Symbol            | Parameter                                                   | Test conditions                                                                                                                                                                                    |                    | V <sub>DDQ</sub> | Min                   | Тур | Max  | Units                         |

|-------------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------|-----------------------|-----|------|-------------------------------|

| V <sub>IK</sub>   |                                                             | I <sub>1</sub> = -18 mA                                                                                                                                                                            |                    | 2.3 V            |                       |     | -1.2 | V                             |

| V <sub>OH</sub>   |                                                             | I <sub>OH</sub> = -100 μA                                                                                                                                                                          |                    | 2.3 V to 2.7 V   | V <sub>DD</sub> - 0.2 |     |      | ٧                             |

| VOH               |                                                             | I <sub>OH</sub> = -16 mA                                                                                                                                                                           |                    | 2.3 V            | 2.05                  |     |      | V                             |

| $V_{OL}$          |                                                             | I <sub>OL</sub> = 100 μA                                                                                                                                                                           |                    | 2.3 V to 2.7 V   |                       |     | 0.2  | V                             |

| V OL              |                                                             | I <sub>OL</sub> = 16 mA                                                                                                                                                                            |                    | 2.3 V            |                       |     | 0.20 | ٧                             |

| I <sub>I</sub>    | All inputs                                                  | $V_{I} = V_{DD}$ or GND                                                                                                                                                                            |                    | 2.7 V            |                       |     | ± 5  | μΑ                            |

| I <sub>DD</sub>   | Standby<br>(static)                                         | RESETB = GND                                                                                                                                                                                       |                    |                  |                       |     | 0.01 | μΑ                            |

| סטי               | Operating (static)                                          | $V_{I} = V_{IH(AC)}$ or $V_{IL(AC)}$ ,<br>RESETB = $V_{DD}$                                                                                                                                        |                    |                  |                       | 40  |      | mA                            |

|                   | Dynamic<br>operating<br>(clock only)                        | RESETB = $V_{DD}$ ,<br>$V_{I} = V_{IH(AC)}$ or $V_{IL(AC)}$ ,<br>CLK and CLKB switching<br>50% duty cycle                                                                                          | I <sub>O</sub> = 0 | 2.5V             |                       | 35  |      | μΑ/clock<br>MHz               |

| I <sub>DDD</sub>  | Dynamic<br>operating<br>(per each<br>data input)            | RESETB = V <sub>DD</sub> , V <sub>I</sub> = V <sub>IH(AC)</sub> or V <sub>IL(AC)</sub> , CLK and CLKB = switching 50% duty cycle; One data input switching at half clock frequency, 50% duty cycle |                    |                  |                       | 7   |      | μΑ/clock<br>MHz/data<br>input |

| r <sub>OH</sub>   | Output high                                                 | I <sub>OH</sub> = -20 mA                                                                                                                                                                           |                    | 2.3 V to 2.7 V   |                       | 12  |      | Ω                             |

| r <sub>OL</sub>   | Output low                                                  | I <sub>OL</sub> = 20 mA                                                                                                                                                                            |                    | 2.3 V to 2.7 V   |                       | 10  |      | Ω                             |

| r <sub>O(D)</sub> | r <sub>OH</sub> - r <sub>OL</sub>  <br>each<br>separate bit | I <sub>O</sub> = 20 mA, T <sub>A</sub> = 25° C                                                                                                                                                     |                    | 2.5 V            |                       |     | 4    | Ω                             |

| C <sub>i</sub>    | Data inputs                                                 | $V_{I} = V_{REF} \pm 350 \text{ mV}, \ V_{ICR} = 1.25 \text{ V}$                                                                                                                                   | <i>'</i> ,         | 2.5 V            | 2.5                   |     | 3.5  | pF                            |

| O <sub>i</sub>    | CLK & CLKB                                                  | $V_{I(PP)} = 360 \text{ mV}$                                                                                                                                                                       |                    | 2.5 V            | 2.5                   |     | 3.5  | pF                            |

## rev 2.0 **Timing Requirements**

(Over recommended operating free-air temperature range, unless otherwise noted).

| Symbol             | Parar                                     | <b>V</b> <sub>DD</sub> = 2 | Unit |      |     |

|--------------------|-------------------------------------------|----------------------------|------|------|-----|

|                    |                                           | Min                        | Max  |      |     |

| f <sub>CLOCK</sub> | Clock frequency                           |                            |      | 200  | MHz |

| $T_{PD}$           | Clock to output time                      |                            |      | 2.7  | ns  |

| T <sub>RST</sub>   | Reset to output time                      |                            |      | 4.5  | ns  |

| ts                 | Setup time, fast slew rate <sup>2,4</sup> | Data before CLK↑, CLKB↓    | 0.5  |      | ns  |

| 15                 | Setup time, slow slew rate 3,4            | Data before CERT, CERD     | 0.7  |      | ns  |

| t <sub>h</sub>     | Hold time, fast slew rate <sup>2,4</sup>  | Data after CLK↑, CLKB↓     | 0.3  |      | ns  |

| rn<br>             | Hold time, slow slew rate 3,4             | Bata and GERT, GERBY       | 0.5  |      | ns  |

| t <sub>SL</sub>    | Output slew rate                          | 1                          | 4    | V/ns |     |

- Note: 1. Guaranteed by design, not 100% tested in production.

- 2. For data signal input slew rate >= 1V/ns

- 3. For data signal input slew rate >= 0.5 V/ns and < 1V/ns

- 4. CLK,CLKB signals input slew rates are >=1V/ns

# **Switching Characteristics**

(Over recommended operating free-air temperature range unless otherwise noted.)

| Symbol           | From (input) | To (output) | $V_{DD} = 2.5 \text{ V} \pm 0.2 \text{ V}$ |     | .2 V | Units |

|------------------|--------------|-------------|--------------------------------------------|-----|------|-------|

|                  |              |             | Min                                        | Тур | Max  |       |

| f <sub>max</sub> |              |             | 200                                        | _   | _    | MHz   |

| t <sub>PD</sub>  | CLK, CLKB    | Q           | 1.9                                        |     | 2.7  | ns    |

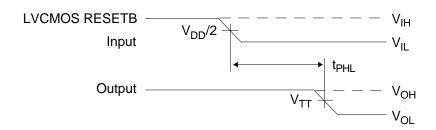

| t <sub>phl</sub> | RESETB       | Q           | _                                          | _   | 4.5  | ns    |

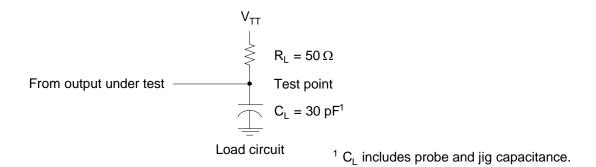

# Parameter Measurement Information (V<sub>DD</sub> = 2.5 V ± 0.2V)

#### **Voltage and Current Waveforms**

In the following waveforms, note that all input pulses are supplied by generators having the following characteristics:

- PRR  $\leq$  10 MHz,  $Z_0 = 50 \Omega$ , input slew rate = 1 V/ns  $\pm$  20% (unless otherwise specified).

- The outputs are measured one at a time with one transition per measurement.

- $V_{TT} = V_{REF} = V_{DDQ}/2$ .

- $V_{IH} = V_{REF} + 310 \text{ mV}$  (AC voltage levels) for differential inputs.  $V_{IH} = V_{DD}$  for LVCMOS input.

- V<sub>IL</sub> = V<sub>REF</sub> 310 mV (AC voltage levels) for differential inputs. V<sub>IL</sub> = GND for LVCMOS input.

- t<sub>PLH</sub> and t<sub>PHL</sub> are the same as t<sub>pd</sub>.

#### Input active and inactive times

$<sup>^{1}</sup>$  I<sub>DD</sub> tested with clock and data inputs held at V <sub>DD</sub> or GND, and I  $_{\rm O}$  = 0 mA.

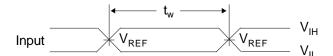

#### **Pulse duration**

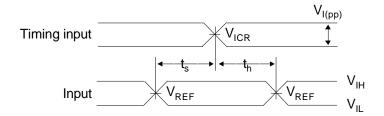

#### Setup and hold times

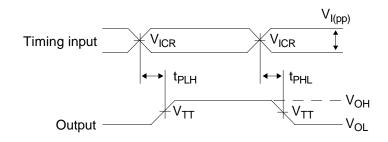

rev 2.0 Propagation delay times

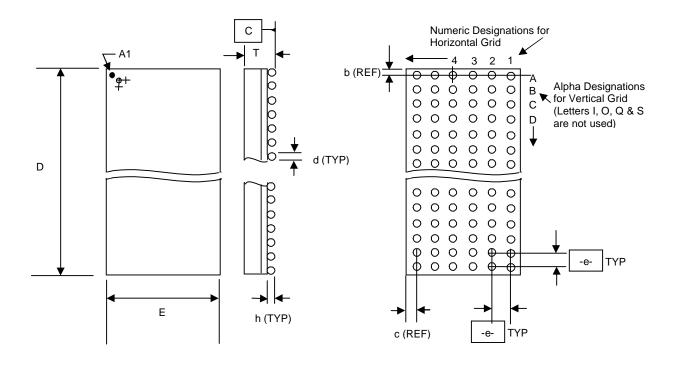

### **Package Dimensions**

#### 114-Pin Ball BGA

|       | _    | T Min/May |      | Е     | BALL GRI | D     |      | la Min/Mass | REF. DIMENSION |      |

|-------|------|-----------|------|-------|----------|-------|------|-------------|----------------|------|

| D     |      | T Min/Max | е    | HORIZ | VERT     | TOTAL | a    | h Min/Max   | b              | С    |

| 16.00 | 5.50 | 4 20/4 50 | 0.80 |       | 40       | 444   | 0.40 | 0.04/0.44   | 0.00           | 0.75 |

| BSC   | BSC  | 1.30/1.50 | BSC  | 6     | 19       | 114   | 0.46 | 0.31/0.41   | 0.80           | 0.75 |

# **Ordering Codes**

| Ordering Number       | Marking         | Package Type                     | Quantity<br>per reel | Temperature    |

|-----------------------|-----------------|----------------------------------|----------------------|----------------|

| ASM4SSTVF32852-114BT  | AS4SSTVF32852B  | 114-pin Ball, BGA, tray/tube     |                      | 0°C to 70°C    |

| ASM4SSTVF32852-114BR  | AS4SSTVF32852B  | 114-pin Ball, BGA, tape and reel | 2500                 | 0°C to 70°C    |

| ASM4ISSTVF32852-114BT | AS4ISSTVF32852B | 114-pin Ball, BGA, tray/tube     |                      | -40°C to +85°C |

| ASM4ISSTVF32852-114BR | AS4ISSTVF32852B | 114-pin Ball, BGA, tape and reel | 2500                 | -40°C to +85°C |

Alliance Semiconductor Corporation 2595, Augustine Drive, Santa Clara, CA 95054

Tel# 408-855-4900

Fax: 408-855-4999 www.alsc.com Copyright © Alliance Semiconductor All Rights Reserved Advance Information Part Number: ASM4SSTVF32852 Document Version: v1.1

© Copyright 2003 Alliance Semiconductor Corporation, All rights reserved. Our three-point logo, our name and Intelliwatt are trademarks or registered trademarks of Alliance. All other brand and product names may be the trademarks of their respective companies. Alliance reserves the right to make changes to this document and its products at any time without notice. Alliance assumes no responsibility for any errors that may appear in this document. The data contained herein represents Alliance's best data and/or estimates at the time of issuance. Alliance reserves the right to change or correct this data at any time, without notice. If the product described herein is under development, significant changes to these specifications are possible. The information in this product data sheet is intended to be general descriptive information for potential customers and users, and is not intended to operate as, or provide, any guarantee or warrantee to any user or customer. Alliance does not assume any responsibility or liability arising out of the application or use of any product described herein, and disclaims any express or implied warranties related to the sale and/or use of Alliance products including liability or warranties related to fitness for a particular purpose, merchantability, or infringement of any intellectual property rights, except as express agreed to in Alliance's Terms and Conditions of Sale (which are available from Alliance). All sales of Alliance products are made exclusively according to Alliance's Terms and Conditions of Sale. The purchase of products from Alliance does not convey a license under any patent rights, copyrights; mask works rights, trademarks, or any other intellectual property rights of Alliance or third parties. Alliance does not authorize its products for use as critical components in life-supporting systems where a malfunction or failure may reasonably be expected to result in significant injury to the user, and the inclusion of Alliance products in such life-supporting systems implies that the manufacturer assumes all risk of such use and agrees to indemnify Alliance against all claims arising from such use.