# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

#### **AUGUST 1992**

DS3535 - 1.0

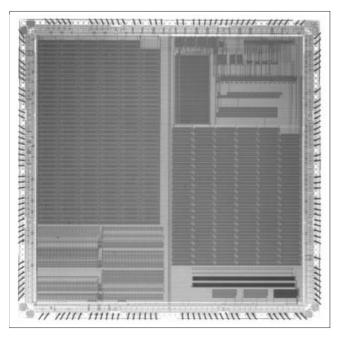

# CLA70000V LOW VOLTAGE SPECIFICATION 1.0µ CMOS GATE ARRAYS

#### **GENERAL DESCRIPTION**

Advances in processing technology have led to the development of an array family which can operate at 3 volts. This series of arrays may be used with the lower voltage power supply rails which are becoming increasingly common. Applications include battery portable such as laptop computers where low power consumption is essential as well as pagers and consumer applications like hand held language translators and games. This summary datasheet gives information on the CLA70000 series AC and DC characteristics at low voltage.

#### CLA70000 FAMILY

| ARRAY    | RAW GATES | PADS |

|----------|-----------|------|

| CLA70000 | 5000      | 44   |

| CLA71000 | 12000     | 68   |

| CLA72000 | 19000     | 84   |

| CLA73000 | 27000     | 100  |

| CLA74000 | 39000     | 120  |

| CLA75000 | 70000     | 160  |

| CLA76000 | 110000    | 200  |

| CLA77000 | 182000    | 256  |

| CLA78000 | 256000    | 304  |

|          |           |      |

#### **FEATURES**

- Operates at 3.3V

- 1.0μ (0.8μ Leff) twin well, epitaxial CMOS process

- 5,000 to 250,000 available gates on a chanelless array architecture

- Low current and power (<1µA/gate/MHz)

- Slew controlled outputs with drivers up to 12mA for bus driving and other applications.

- ESD protection in excess of 2kV

- Comprehensive cell library including DSP and compiled memory cells (ROM blocks to 64K bits and RAM blocks to 16K bits)

- Supports JTAG/BIST test philosophies (IEEE 1149-1 Test Procedures)

- Fully supported on Industry Standard workstations and in-house software

#### Description Page **Process Technology** 2 Core Design 2 I/O Design 2 **AC Characteristics** 3 **DC** Characteristics 4 **Design Tools** 5 Packaging 6

#### CONTENTS

#### **CMOS PROCESS TECHNOLOGY**

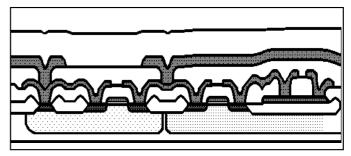

The CLA70000 arrays are based on GEC Plessey Semiconductors well proven 1 $\mu$  CMOS process, manufactured at GPS's advanced, Class 10, six-inch wafer fabrication facility. The process (fig.1) is a twin well, self aligned oxide-isolated technology, with an effective channel length of 0.8 $\mu$ m (1.0 $\mu$ m drawn), giving a low defect density, high reliability, and inherently low power dissipation. The process has excellent immunity to latch-up, and ESD, and exhibits stable performance characteristics.

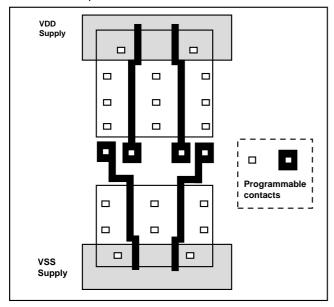

Figure 2 : Diagrammatic representation of Array Core Cell

#### **INPUT/OUTPUT BUFFER DESIGN**

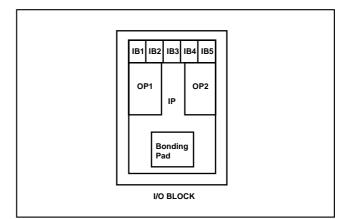

The peripheral cells (fig.3) are fully programmable as Input, Output, VDD or GND, and they are designed to offer several interfacing options, TTL and CMOS for example. The cells already contain input 'pull-up' and 'pull-down' resistors and Electro Static Discharge protection elements. Components for implementing Schmitt Triggers, TTL threshold detectors, tristate control, and flip-flops for signal re-timing are also included. A range of output buffers is available with various output drive currents to match system requirements.

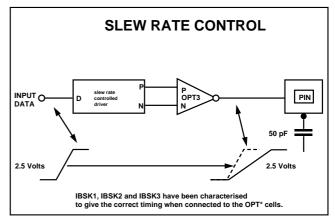

Noise transients due to a large number of simultaneously switching outputs are an increasing problem as bus widths widen (The supply pad location, and the inductance of the bond wires and package leads are also factors). CLA70000 Arrays offer several I/O buffers with the capability to control the output slew (di/dt) (fig.4) which are invaluable in controlling these transients when driving large capacitive loads such as busses.

Figure 1 : Process 'VQ' Process Cross Section

#### **CORE CELL DESIGN**

A four transistor group (2 NMOS and 2PMOS) (fig 2.) forms the basic cell of the core array. This array element is repeated in a regular fashion over the complete core area to give a homogeneous 'Full Field' (sea of gates) array. This lends itself to hierarchical design, allowing pre-routed user defined subcircuits to be repeated anywhere on the array. The core cell structure has been carefully designed to maximise the number of nets which may be routed through the cell. This enables optimal routing for both data flow and control signal distribution schemes thus giving very high overall utilisation figures. This feature is of particular benefit in designs using highly structured blocks such as memory or arithmetic functions.

Figure 3

Figure 4

#### AC CHARACTERISTICS The performance of the CLA70000V device depends on numerous factors including:

Supply voltage Ambient temperature, and temperature of the devices active junctions Gate front, i.e. the logic loading on the gate outputs Interconnection loading on the gates Processing tolerance, i.e. the manufacturing spreads

The CLA70000 technology library contains all the performance information for each cell in the design libraries. The PDS design software suite accesses this data, and the simulation program automatically calculates the design's performance under the selected operating conditions. Prior to layout, estimates of the interconnection loadings are used in the simulations. After layout, track loadings are extracted from the physical design to allow re-simulation with actual values to confirm device performance.

The effect of those factors on the propagation delays of arange of selected cells is illustrated in the tables below.

#### Fanout is in gate load units

| INTERNAL | CORE  | CELLS                            |        | Typical<br>propagation<br>Delay Ns<br>5 volts 25°C | Prop<br>Dela<br>3 vol | st case<br>agation<br>ay (ns)<br>ts 70°C<br>nout |

|----------|-------|----------------------------------|--------|----------------------------------------------------|-----------------------|--------------------------------------------------|

| Name     | Cells | Description                      | Symbol | Fanout = 2                                         | 2                     | 4                                                |

| INV2     | 1     | INVERTER DUAL DRIVE              | tpLH   | 0.27                                               | 0.95                  | 1.14                                             |

|          |       |                                  | tpLH   | 0.18                                               | 0.64                  | 0.76                                             |

| NAND2    | 1     | 2-INPUT NAND GATE                | tpHL   | 0.39                                               | 1.37                  | 1.75                                             |

|          |       |                                  | tpLH   | 0.30                                               | 1.07                  | 1.41                                             |

| NOR2     | 1     | 2-INPUT NOR GATE                 | tpLH   | 0.50                                               | 1.77                  | 2.46                                             |

|          |       |                                  | tpLH   | 0.22                                               | 0.78                  | 1.09                                             |

| DF       | 4     | MASTER SLAVE<br>D-TYPE FLIP FLOP | tpHL   | 0.54                                               | 1.90                  | 2.18                                             |

|          |       |                                  | tpLH   | 0.55                                               | 1.96                  | 2.11                                             |

| INTERMED | Typical<br>propagation<br>Delay Ns<br>5 volts 25°C | Propa<br>Dela<br>3 volt                 | agation<br>y (ns)<br>s 70°C<br>nout |            |      |      |

|----------|----------------------------------------------------|-----------------------------------------|-------------------------------------|------------|------|------|

| Name     | Cells                                              | Description                             | Symbol                              | Fanout = 2 | 2    | 4    |

| IBGATE   | -                                                  | LARGE 2 INPUT NAND<br>GATE +2 INPUT NOR | tpLH                                | 0.34       | 1.20 | 1.39 |

|          |                                                    | GATE +2 INPUT NOR                       | tpLH                                | 0.27       | 0.97 | 1.14 |

| IBDF     | -                                                  | MASTER SLAVE D-TYPE<br>FLIP FLOP        | tpHL                                | 0.48       | 1.69 | 1.96 |

|          |                                                    |                                         | tpLH                                | 0.50       | 1.78 | 1.93 |

| IBCMOS1  | - CMOS INPUT BUFFER<br>WITH 2 INPUT NAND GATE      |                                         | tpLH                                | 0.60       | 2.15 | 2.28 |

|          |                                                    | WITT 2 INFOT NAND GATE                  | tpLH                                | 0.45       | 1.59 | 1.65 |

| OUTPUT E | BUFFER | CELLS                     |        | Typical<br>propagation<br>Delay Ns<br>5 volts 25°C | Prop<br>Dela<br>3 vol | st case<br>agation<br>ay (ns)<br>ts 70°C<br>nout |

|----------|--------|---------------------------|--------|----------------------------------------------------|-----------------------|--------------------------------------------------|

| Name     | Cells  | Description               | Symbol | Fanout = 10pF                                      | 10pF                  | 50pF                                             |

| OP3      | -      | STANDARD OUTPUT<br>BUFFER | tpLH   | 0.73                                               | 2.58                  | 8.83                                             |

|          |        | BUFFER                    | tpLH   | 0.49                                               | 1.73                  | 5.98                                             |

| OP6      | -      | MEDIUM OUTPUT<br>BUFFER   | tpHL   | 0.50                                               | 1.77                  | 4.88                                             |

|          |        | BUFFER                    | tpLH   | 0.33                                               | 1.16                  | 3.29                                             |

| OP12     | -      | LARGE OUTPUT BUFFER       | tpLH   | 0.38                                               | 1.35                  | 2.91                                             |

|          |        |                           | tpLH   | 0.25                                               | 0.90                  | 2.04                                             |

DC ELECTRICAL CHARACTERISTICS All characteristics at 3 - 5.5 volts and 0 -70°C temperature

|                                                                                                                                                                                                                                  |                          |                                                                | VALUE                                                                  |                                 |                            |                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|----------------------------------------------------------------|------------------------------------------------------------------------|---------------------------------|----------------------------|----------------------------------------------------------------------------------------|

| CHARACTERISTIC                                                                                                                                                                                                                   | SYM                      | Min                                                            | Тур                                                                    | Max                             | UNIT                       | CONDITIONS                                                                             |

| LOW LEVEL INPUT VOLTAGE                                                                                                                                                                                                          | VIL                      |                                                                |                                                                        |                                 | V                          |                                                                                        |

| TTL Inputs (IBTTL1/IBTTL2)<br>CMOS Inputs (IBCMOS1/IBCMOS2)                                                                                                                                                                      |                          |                                                                |                                                                        | 0.6<br>0.2VDD                   |                            |                                                                                        |

| HIGH LEVEL INPUT VOLTAGE                                                                                                                                                                                                         | VIH                      |                                                                |                                                                        |                                 | V                          |                                                                                        |

| TTL Inputs (IBTTL1/IBTTL2)<br>CMOS Inputs (IBCMOS1/IBCMOS2)                                                                                                                                                                      |                          | 2.2V<br>0.75VDD                                                |                                                                        |                                 |                            |                                                                                        |

| INPUT HYSTERESIS<br>(IBST1) Rising<br>Falling<br>(IBST2) Rising<br>Falling                                                                                                                                                       | VT+<br>VT-<br>VT+<br>VT- |                                                                | 1.9<br>1.2<br>1.3<br>0.8                                               |                                 | V                          | VIL to VIH<br>VIH to VIL<br>VIL to VIH<br>VIH to VIL<br>VIH to VIL                     |

| INPUT CURRENT/RESISTANCE (CMOS / TTL INPUTS)<br>No Resistor<br>Inputs with 1Kohm Resistors<br>Inputs with 2Kohm Resistors<br>Inputs with 4Kohm Resistors<br>Inputs with 75Kohm Resistors<br>Resistor values nominal - See note 1 | IIN                      | 0.50<br>1.00<br>2.00<br>20.00                                  | 1.00<br>2.00<br>4.00<br>75.00                                          | 1<br>2<br>4<br>8<br>250         | μΑ<br>ΚΩ<br>ΚΩ<br>ΚΩ<br>ΚΩ | VIN = VDD or VSS                                                                       |

| HIGH LEVEL OUTPUT VOLTAGE<br>All outputs<br>Smallest drive cell OP1/OPT1/OPOS1<br>Low drive cell OP2/OPT2/OPOS2<br>Standard drive cell OP3/OPT3/OPOS3<br>Medium drive cell OP6/OPT6/OPOS6<br>Large drive cell OP12/OPT12/OPOS12  | VOH                      | 0.75VDD<br>0.75VDD<br>0.75VDD<br>0.75VDD<br>0.75VDD<br>0.75VDD | VDD - 0.05<br>0.9VDD<br>0.9VDD<br>0.9VDD<br>0.9VDD<br>0.9VDD<br>0.9VDD |                                 | V                          | $IOH = -1\mu A$<br>IOH = -1mA<br>IOH = -2mA<br>IOH = -3mA<br>IOH = -6mA<br>IOH = -12mA |

| LOW LEVEL OUTPUT VOLTAGE<br>All outputs<br>Smallest drive cell OP1/OPT1/OPOD1<br>Low drive cell OP2/OPT2/OPOD2<br>Standard drive cell OP3/OPT3/OPOD3<br>Medium drive cell OP6/OPT6/OPOD6<br>Large drive cell OP12/OPT12/OPOD12   | VOL                      |                                                                | VSS + 0.05<br>0.2<br>0.2<br>0.2<br>0.2<br>0.2<br>0.2                   | 0.4<br>0.4<br>0.4<br>0.4<br>0.4 | V                          | $IOL = 1\mu A$ $IOL = 1mA$ $IOL = 2mA$ $IOL = 3mA$ $IOL = 6mA$ $IOL = 12mA$            |

| TRISTATE OUTPUT LEAKAGE CURRENT<br>Tristate, open drain and open source output cells                                                                                                                                             | IOZ                      | -1                                                             |                                                                        | 1                               | μΑ                         | VOUT = VSS or VDD                                                                      |

| OUTPUT SHORT CIRCUIT CURRENT<br>Standard outputs OP3/OPT3/OPOD3<br>(See note 2) OP3/OPT3/OPOS3                                                                                                                                   | IOS                      | 67<br>37                                                       | 135<br>75                                                              | 270<br>150                      | mA                         | VDD = MAX, VOUT = VDD<br>VDD = MAX, VOUT = 0V                                          |

| OPERATING SUPPLY CURRENT (per gate) (see note 3)                                                                                                                                                                                 | IDDOP                    |                                                                | 1                                                                      |                                 | μA/MHz                     |                                                                                        |

| INPUT CAPACITANCE                                                                                                                                                                                                                | CI                       |                                                                | 5                                                                      |                                 | pF                         | ANY INPUTS (Note 4)                                                                    |

| OUTPUT CAPACITANCE                                                                                                                                                                                                               | COUT                     |                                                                | 5                                                                      |                                 | pF                         | ANY OUTPUT (Note 4)                                                                    |

| BIDIRECTIONAL PIN CAPACITANCE                                                                                                                                                                                                    | CVO                      |                                                                | 7                                                                      |                                 | pF                         | ANY I/O PIN (Note 5)                                                                   |

Note 1: If resistors are used with outputs the correct value of the resistor must be used to maintain VOL/VOH logic levels.

Note 2: Standard driver output OP3 etc. Short circuit current for other outputs will scale. Not more than one output may be shorted at a time for a maximum duration of one second.

Note 3: Excluding peripheral buffers.

Note 4: Excludes package leadframe capacitance or bidirectional pins.

Note 5: Excludes package.

| ABSOLUTE MAXIMUM RATINGS |     |     |       |  |  |

|--------------------------|-----|-----|-------|--|--|

| PARAMETER                | MIN | MAX | UNITS |  |  |

| Supply                                                                                                         | Voltage | - 0.5 | 7.0     | V |  |

|----------------------------------------------------------------------------------------------------------------|---------|-------|---------|---|--|

| Input                                                                                                          | Voltage | - 0.5 | VDD+0.5 | V |  |

| Output                                                                                                         | Voltage | - 0.5 | VDD+0.5 | V |  |

| Operation above these absolute maximum ratings or prolonged periods above the recommended operating limits may |         |       |         |   |  |

permanently damage device characteristics and may affect reliability.

| Storage | Temperature: |      |     |          |

|---------|--------------|------|-----|----------|

|         | Ceramic      | -65  | 150 | degree C |

|         | Plastic      | - 40 | 125 | degree C |

| RECOMMENDED OPERATING LIMITS                                         |                   |                          |                   |  |  |  |

|----------------------------------------------------------------------|-------------------|--------------------------|-------------------|--|--|--|

| PARAMETER                                                            | MIN               | MAX                      | UNITS             |  |  |  |

| Supply Voltage<br>Input Voltage<br>Output Voltage<br>Current per pad | 3.0<br>VSS<br>VSS | 5.5<br>VDD<br>VDD<br>100 | V<br>V<br>V<br>mA |  |  |  |

| Operating Temperatur                                                 | e:                |                          |                   |  |  |  |

| Commercial Grade                                                     | 0                 | 70                       | degree C          |  |  |  |

| Industrial Grade                                                     | -40               | 85                       | degree C          |  |  |  |

| Military Grade                                                       | -55               | 125                      | degree C          |  |  |  |

#### **DESIGN TOOLS**

The focus of the GEC Plessey design tool methodology is that of maintaining an open CAD system with all interfaces standardized via EDIF 2.0. This enables us to provide full support for a variety of 3rd party ASIC design tools and facilitates rapid updating of associated libraries. It also provides an interface to the GEC Plessey (PDS2) design system, which offers a total design environment including behavioral and functional level modelling.

#### PDS2 - THE GPS ASIC DESIGN SYSTEM

- Behavioral, Functional, and Gate Level Modelling

- VHDL and Third Party Links

- Supports Hierarchical Design Techniques

- EDIF 2.0 Interface

PDS2 is GPS's own proprietary ASIC design system. It provides a fully-integrated, technology independent VLSI design environment for all GPS CMOS SemiCustom products.

#### THIRD PARTY SOFTWARE SUPPORT

- Design Kits for major industry standard ASIC design software tools

- All libraries include fully detailed timing information

- EDIF 2.0 Interface

- Post layout back annotation available

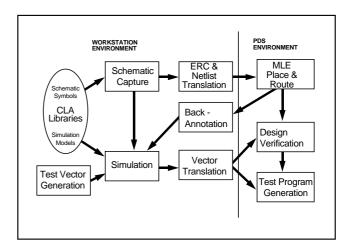

GPS supports a wide range of third party design tools including IKOS, Mentor, Verilog, and Viewlogic. The design kits offer fully detailed timing information for all cell libraries, netlist extraction utilities, and post layout back annotation capability where applicable. An example of a workstation design flow is shown in the figure 5 (opposite). Please contact your local GEC Plessey Semiconductor's sales office for further information about support of particular tools.

#### **DESIGN SUPPORT**

Design support is available from various centres worldwide each of which is connected to our Headquarters via high speed data links. A design centre engineer is assigned to each customers circuit, to ensure good communication, and a smooth and efficient design flow.

As part of the design process GPS operates a thorough design audit procedure to verify compliance with customer specification and to ensure manufacturability. The procedure includes four separate review meetings, with the customer, held a key stages of the design. The standard design audit procedure is outlined opposite. PDS2 runs on Digital Equipment computers and is self configuring according to the available machine resources. It comprises design capture (schematic capture or VHDL), testability analysis, logic simulation, fault simulation, auto place and route, and back annotation. The system offers full support for hierarchical design techniques, maintained from design capture through to layout, as well as advanced design management tools. PDS2 may be used either at a GPS Design Center or under licence at the customer's premises. A three day training course is available for first time users.

Figure 5 : Workstation Design Flow

- Review 1: Held at the beginning of the design cycle to check and agree on specifications and design timescales.

- Review 2 Held after Logic Simulation and prior to Layout. Checks to ensure satisfactory functionality, timing performance, and adequate fault coverage

- Review 3 Held after Layout and Post layout Simulation. Verification of design performance after insertion of actual track loads. Final check of all device specifications before prototype manufacture.

- Review 4 Held after prototype delivery. Confirms that the devices meet the specification and are suitable for full scale production.

#### PACKAGING

Production quantities of the CLA70000 family are available in industry-standard ceramic and plastic packages according the codes shown below. Prototype samples are normally supplied in ceramic only.

| DC     | DILMON                    | Dual in Line, Multilayer ceramic. Brazed leads Metal Sealed Lid. Through Board.       |

|--------|---------------------------|---------------------------------------------------------------------------------------|

| DG     | CERDIP                    | Dual In Line, Ceramic body, Alloy leadframe, Glass Sealed, Through Board.             |

| DP     | PLASDIP                   | Dual In Line, Copper or Alloy leadframe, Plastic Moulded. Through Board.              |

| AC     | P.G.A.                    | Pin Grid Array, Multilayer Ceramic. Metal Sealed lid. Through Board.                  |

| AC (P) | POWER P.G.A.              | As above with cavity down and Cu/W heat plate.                                        |

| MP     | SMALL OUTLINE (S.O.)      | Dual In Line, 'Gullwing' Formed Leads. Plastic Moulded Surface Mount.                 |

| LC     | LCC                       | Leadless Chip Carrier. Multilayer Ceramic. Metal Sealed Lid. Surface Mount.           |

| HC     | LEADED CHIP CARRIER       | Quad Multilayer Ceramic. Brazed J Formed Leads. Metal Sealed Lid.<br>Surface Mount    |

| GC     | LEADED CHIP CARRIER       | Quad Multilayer Ceramic. Brazed Leads. Metal Sealed Lid. Surface Mount.               |

| GC (P) | POWER LEADED CHIP CARRIER | As above with cavity down, and Cu/W heat plate.                                       |

| HG     | QUAD CERPAC               | Quad Ceramic Body, 'J' Formed Leads. Glass Sealed. Surface Mount.                     |

| GG     | CERAMIC QUAD FLATPACK     | Quad Ceramic Body, 'Gullwing' Formed Leads. Glass Sealed. Surface Mount.              |

| HP     | PLCC                      | Quad Plastic Leaded Chip Carrier. 'J' Formed Leads. Plastic Moulded.<br>Surface Mount |

| GP     | PQFP                      | Plastic Quad Flat Pack. 'Gullwing' Formed Leads. Plastic Moulded. Surface Mount.      |

#### PRIMARY SEMI-CUSTOM DESIGN CENTRES

**UNITED KINGDOM:** Swindon, Tel: (0793) 518000 Tx: 449637 Fax: (0793) 518411. Oldham, Tel: (061) 682 6844, Fax: (061) 688 7898. Lincoln, Tel: (0522) 500500 Tx: 56380 Fax: (0522) 500550. Wembley, Tel: (081) 908 4111 Tx: 28817 Fax: (081) 908 3801. **UNITED STATES OF AMERICA:** Scotts Valley, Tel: (408) 438 2900 ITT Tx: 4940840 Fax: (408) 438 5576. Dedham, Tel: (617) 320-9369. Fax: (617) 320-9383. Irvine, Tel: (714) 455-2950. Fax: (714) 455-9671. **AUSTRALIA:** Rydalmere, NSW, Tel: (612) 638 1888. Fax: (612) 638 1798. **FRANCE:** Les Ulis Cedex, Tel: (6) 446 23 45 Tx: 602858F. Fax: (6) 446 06 07. **ITALY:** Milan, Tel: (02) 33001044/45 Tx: 331347 Fax: (GR3) 2316904. **GERMANY:** Munich, Tel: (089) 3609 06 0 Tx: 523980. Fax: (089) 3609 06 55. **JAPAN:** Tokyo, Tel: (3) 839 3001. Fax: (3) 839 3005.

# GEC PLESSEY

#### HEADQUARTERS OPERATIONS GEC PLESSEY SEMICONDUCTORS Cheney Manor, Swindon, Wiltshire SN2 2QW, United Kingdom. Tel: (0793) 518000 Tx: 449637 Fax: (0793) 518411

#### GEC PLESSEY SEMICONDUCTORS

Sequoia Research Park, 1500 Green Hills Road, Scotts Valley, California 95066, United States of America. Tel (408) 438 2900 ITT Telex: 4940840 Fax: (408) 438 5576 CUSTOMER SERVICE CENTRES

- FRANCE & BENELUX Les Ulis Cedex Tel: (1) 64 46 23 45 Tx: 602858F Fax : (1) 64 46 06 07

- GERMANY Munich Tel: (089) 3609 06-0 Tx: 523980 Fax : (089) 3609 06-55

- ITALY Milan Tel: (02) 33001044/45 Tx: 331347 Fax: (GR3) 316904

- JAPAN Tokyo Tel: (03) 3296-0281 Fax: (03) 3296-0228

- NORTH AMERICA Integrated Circuits, Scotts Valley, USA Tel (408) 438 2900 ITT Tx: 4940840 Fax: (408) 438 7023.

- SOS, Microwave and Hybrid Products, Farmingdale, USA Tel (516) 293 8686 Fax: (516) 293 0061.

- SOUTH EAST ASIA Singapore Tel: 2919291 Fax: 2916455

- SWEDEN Johanneshov Tel: 46 8 7228690 Fax: 46 8 7227879

- UNITED KINGDOM & SCANDINAVIA

- Swindon Tel: (0793) 518510 Tx: 444410 Fax : (0793) 518582

- These are supported by Agents and Distributors in major countries world-wide.

© GEC Plessey Semiconductors 1992 Publication No. DS 3535 Issue No. 1.0 August 1992

This publication is issued to provide outline information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose or form part of any order or contract or be regarded as a representation relating to the products or services concerned. The Company reserves the right to alter without notice the specification, design, price or conditions of supply of any product or service.