### \_ μPD3570 2560-BIT CCD LINEAR IMAGE SENSOR

# NEC Electronics Inc.

#### PRELIMINARY

#### Description

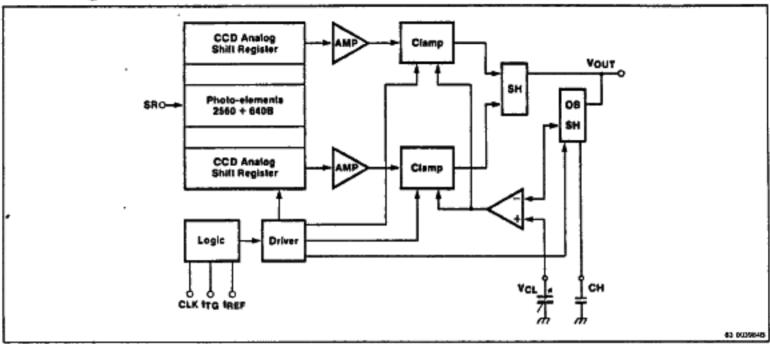

The µPD3570 is a CCD (charge-coupled device) linear image sensor that changes optical images to electrical signals. It has 2560 photo-elements, 64 optical-black elements, two lines of CCD charge transfer registers, a drive unit, a sample-and-hold circuit, and an output amplifier. The drive unit simplifies the external circuit and reduces total drive power, and the sample-and-hold circuit substantially reduces output signal noise.

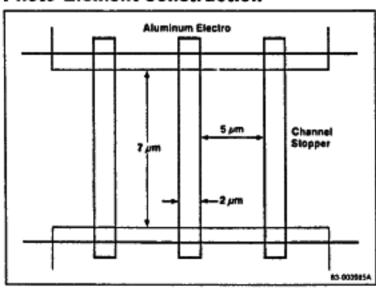

The photo-elements have excellent response characteristics because of their PN junction construction. They are  $7 \times 5 \mu m$ , separated by  $2 \mu m$  channel stoppers.

The charge transfer registers feature extremely high transfer efficiencies, above 99.996%.

#### Features

| Clock generator and drive unit on-chip allows    |

|--------------------------------------------------|

| direct drive by +5 V logic system                |

| Excellent photo-electrical characteristics       |

| Optical-black clamp circuit controls dark-level  |

| DC voltage                                       |

| Sensor reset function controls storage charges   |

| High resolution                                  |

| Similar response characteristics to those of the |

### Ordering Information

human eye

| Part No. | Package                   |

|----------|---------------------------|

| µPD3570D | 20-pin ceramic shrink-DIP |

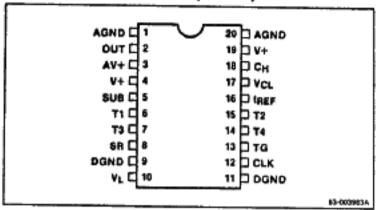

#### Pin Configuration

20-Pin Ceramic Shrink DIP (300 mil)

#### Pin Identification

| Analog ground Output +12 V analog supply voltage |  |  |  |  |  |

|--------------------------------------------------|--|--|--|--|--|

|                                                  |  |  |  |  |  |

| +12 V analog supply voltage                      |  |  |  |  |  |

|                                                  |  |  |  |  |  |

| +12 V driver supply voltage<br>Substrate         |  |  |  |  |  |

|                                                  |  |  |  |  |  |

| Sensor reset                                     |  |  |  |  |  |

| Digital ground                                   |  |  |  |  |  |

| +5 V logic supply voltage                        |  |  |  |  |  |

| Master clock                                     |  |  |  |  |  |

| Transfer gate clock                              |  |  |  |  |  |

| Reference timing output                          |  |  |  |  |  |

| Clamp voltage                                    |  |  |  |  |  |

| Hold capacitance                                 |  |  |  |  |  |

|                                                  |  |  |  |  |  |

#### Note:

During normal operation, T1 and T2 should be tied to DGND, and T3 and T4 to  $\pm$ 12 V.

#### **Block Diagram**

### **Absolute Maximum Ratings**

TA = 25 °C

| Driver supply voltage, AV+ or V+        | -0.3 to +15 V  |

|-----------------------------------------|----------------|

| Logic supply voltage, V <sub>L</sub>    | -0.3 to +7 V   |

| Input voltage, pins 6, 7, 8, 14, 15, 17 | -0.3 to + 15 V |

| Input voltage, pins 5, 12, 13           | -0.3 to +7 V   |

| Operating temperature range             | -25 to +55°C   |

| Storage temperature range               | -40 to +100°C  |

Comment: Exposure to Absolute Maximum Ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage.

#### **Photo-Element Construction**

### **Recommended Operating Conditions**

$T_A = -25 \text{ to } +55 ^{\circ}\text{C}$

|                          |                       |                | Limits |      |      |  |

|--------------------------|-----------------------|----------------|--------|------|------|--|

| Parameter                | Symbol                | Min            | Тур    | Max  | Unit |  |

| Driver supply voltage    | V+, AV+               | 11.4           | 12.0   | 12.6 | ٧    |  |

| Logic supply voltage     | VL                    | 4.75           | 5.0    | 5.25 | ٧    |  |

| Substrate voltage        | V <sub>SUB</sub>      | 4.75           | 5.0    | 5.25 | ٧    |  |

| Sensor reset ON voltage  | V <sub>SR</sub> (on)  | 11             | 12     |      | ٧    |  |

| Sensor reset OFF voltage | V <sub>SR</sub> (off) | 1.5            | 2.5    | 3.5  | v    |  |

| Input voltage, high      | VINH                  | 2.4            |        |      | ٧    |  |

| Input voltage, low       | VINL                  |                |        | 0.5  | ٧    |  |

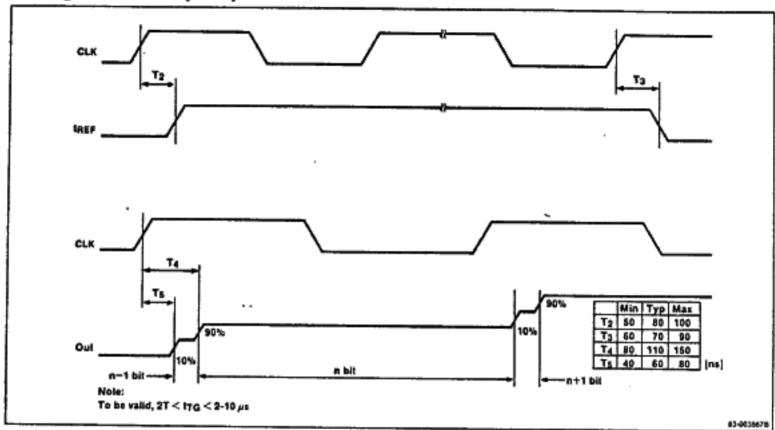

| Master clock frequency   | CLK                   | 0.2            | 1.0    | 3.0  | MHz  |  |

| TG clock                 | trg                   | 2t<br>(Note 1) |        | 10   | μS   |  |

| Clamp voltage            | V <sub>CL</sub>       | 3.0            | 3.5    | 4.0  | V    |  |

| Hold capacitance         | Сн                    | 2.2            | 4.7    | 10   | μF   |  |

#### Note:

(1) t = 1/CLK Test pin voltage T1 = T2 = 0 V Test pin voltage T3 = T4 = +12 V

#### DC Characteristics

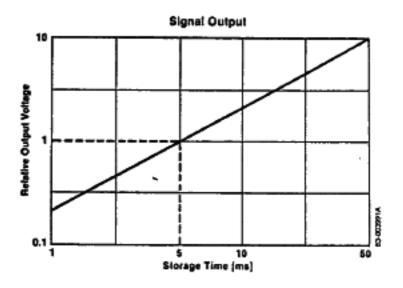

$T_A = 25$  °C; V+ = AV+ = 12 V;  $V_L = +5$  V;  $V_{SR} = 1$  V;  $V_{CL} = 3$  V;  $C_H = 4.7 \, \mu F$ ;  $t_{CLK} = 1$  MHz;  $t_{TG} = 4 \, \mu s$ ;  $t_{STO} = 5 \, ms$

|                               |                     |             | Limits       |             |                  |                                                          |

|-------------------------------|---------------------|-------------|--------------|-------------|------------------|----------------------------------------------------------|

| Parameter                     | Symbol              | Min         | Typ          | Max         | Unit             | Test Conditions                                          |

| Clock input capacitance       | CCLK                |             | 10           |             | pF               |                                                          |

| Clock input leakage current   | †LCLK               |             | 1            | 10          | μА               | V <sub>IN</sub> = 5 V                                    |

| Output voltage, high          | VoH                 | 3.5         | 4.5          | 5.0         | ٧                | R <sub>L</sub> = 5 k; OUT—GND                            |

| Output voltage, low           | V <sub>OL</sub>     |             | 0.2          | 0.8         | v                | R <sub>L</sub> = 5 k; OUT—VDG                            |

| Sensor reset capacitance      | CSR                 |             | 100          |             | pF               |                                                          |

| Sensor reset current          | Isa                 |             |              | 100         | μA               | No transients                                            |

| Test leakage current .        | JLTEST              |             | 1            | 10          | μA               | - Pins 7, 14                                             |

| Clamp leakage current         | ILCLAMP             |             | 1            | 10          | μA               |                                                          |

| Substrate current             | lsua l              |             | 10           | 100         | μA               | V <sub>SUB</sub> = 5 V                                   |

| Analog supply current         | Al+                 | 5           | 8            | 12          | mA               | Pin 3                                                    |

| Driver supply current         | l+                  | 5           | 8            | 12          | mA               | Pins 4, 19 total                                         |

| Logic supply current          | l <u>l</u>          | 20          | 35           | 60          | mA               |                                                          |

| Output signal impedance       | Z <sub>0</sub>      |             | 0.5          | 1.5         | kΩ               |                                                          |

| Clamp offset voltage          | V <sub>CL(os)</sub> | -70         | 0            | +80         | mV               | V <sub>08</sub> V <sub>CL</sub> at V <sub>CL</sub> = 3 V |

| Output saturation voltage     | V <sub>0(sat)</sub> | 2.5         | 3.5          | 4.5         | ٧                | -02                                                      |

| Saturation exposure SE        |                     |             | 0.83<br>2.50 |             | lx.s<br>lx.s     | 2856 K tungsten famp<br>White fluorescent                |

| Photo-response non-uniformity |                     |             | ±5           | ±10         | %                | V <sub>OUT</sub> = 2 V, 3200 K                           |

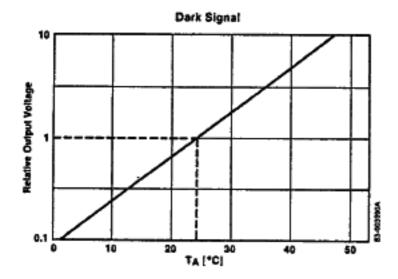

| Average dark signal           |                     |             | 2            | 10          | mV               | See timing chart                                         |

| Dark signal non-uniformity    |                     |             | 2            | 15          | m∀               |                                                          |

| Sensitivity                   |                     | 3.0<br>0.98 | 4.2<br>1.4   | 5.4<br>1.82 | V/Ix.s<br>V/Ix.s | 2856 K tungsten lamp<br>White fluorescent                |

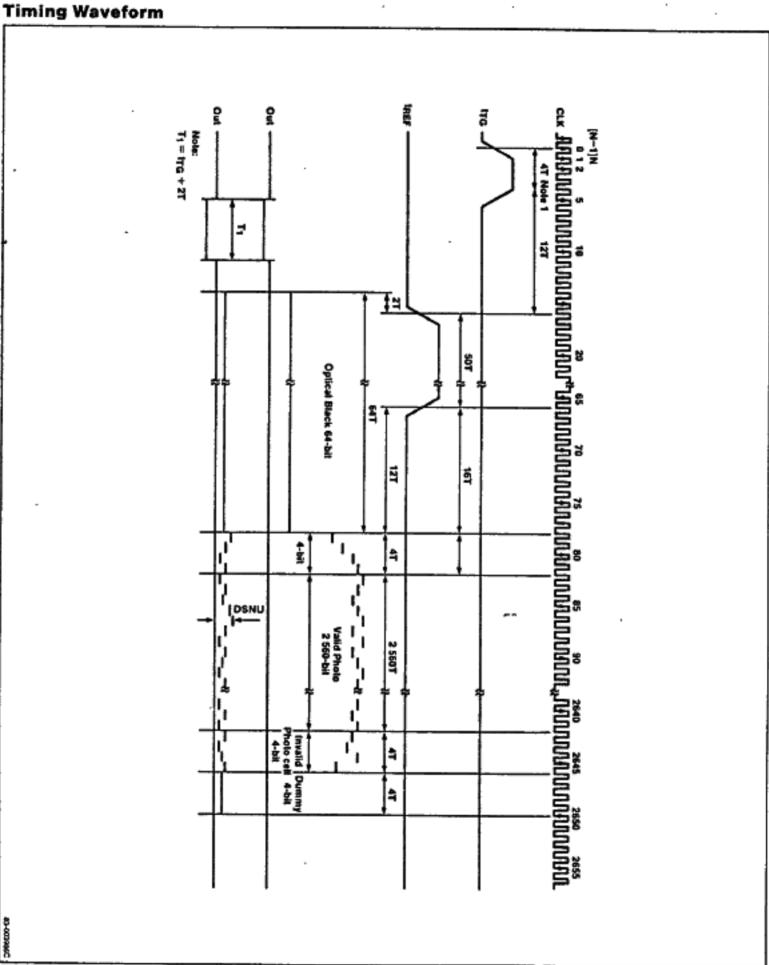

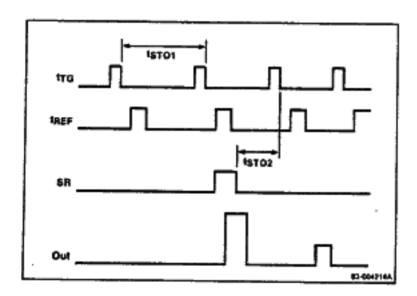

#### Sensor Reset

Sensor reset is a function that controls the signal charge generated by the photo-electric conversion of the photo-transistors. The following timing diagram shows the relationship between SR and the transfer gate timing signal (trg).

Note that when SR is held low, the storage time is determined strictly by trg, and is defined to be the time between falling edges of successive trg pulses (shown in the drawing as tSTO1).

With SR high, the storage time is defined as the time between the falling edge of the SR pulse and the falling edge of the t<sub>TG</sub> pulse. Thus, storage time is controlled by the width of the SR pulse.

Using the SR function, the output signal can be held at a fixed level, even if the input varies.

## Timing Waveforms (cont)

## Operating Characteristics T<sub>A</sub> = 25°C

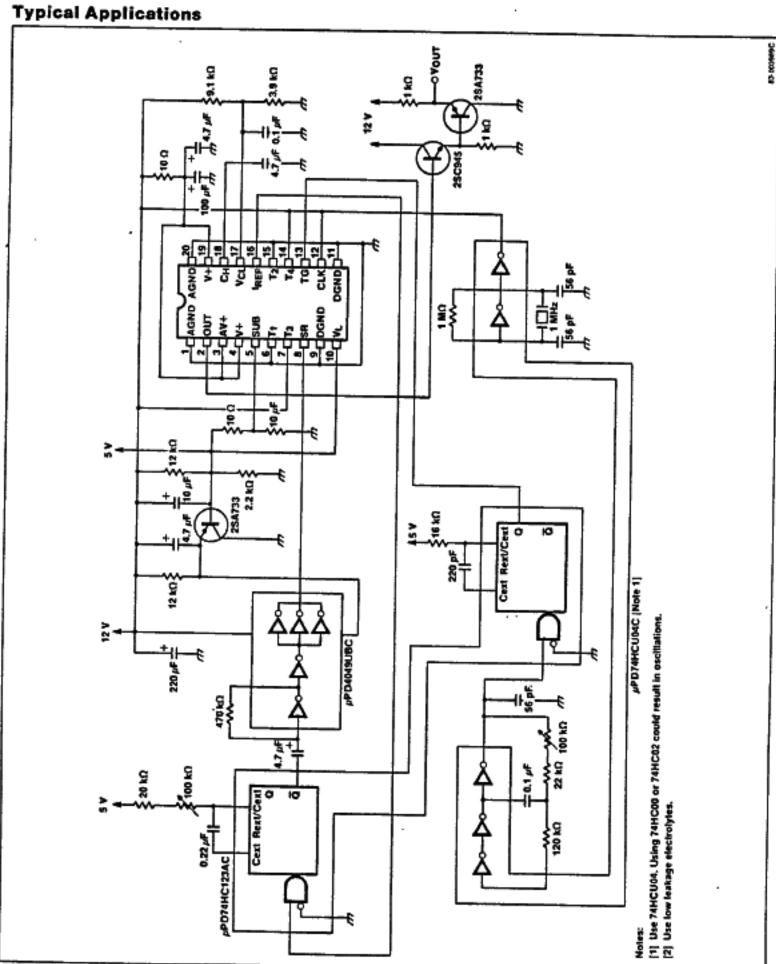

#### Application Notes

#### Electrostatic Damage

Normal precautions for MOS devices should be taken.

#### Surge Voltages

The power supply pins (pins 3, 4, 14) can be easily damaged by surge voltages. Use normal current limiting and bypass techniques.

#### Sensor Reset

Voltage applied to this pin must not be allowed to fall below 1.5 V. Serious damage to the device could result. Orive signal must be pulsed. Driving the SR pin by anything other than a pulse will change the characteristics of the device. Drive pulse to the SR pin should be applied after the leading edge of the  $t_{TG}$  pulse.

#### Window Glass

If some dust gets on the glass it is possible that the resultant output signal may be misinterpreted as a black level signal. So the surface of the glass must always be kept clean. Avoid abrasives and strong chemicals; if glass needs to be cleaned, use soap and water and wipe with a soft cloth.

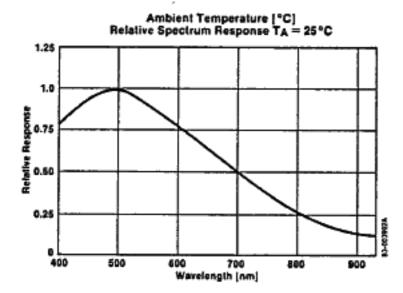

#### **Ambient Temperature**

The dark current of the device is very temperature sensitive, so care must be taken to ensure a constant ambient temperature.

#### Substrate Pin

+5 power should be applied prior to the application of +12 V.