# **AV CMOS SERIES GATE ARRAYS**

## MB65xxxx MB66xxxx MB67xxxx

June 1986 Edition 2.0

#### DESCRIPTION

The Fujitsu MB65xxxx/MB66xxxx/MB67xxxx family are a series of high performance CMOS gate arrays designed to provide high density, low power, and operating speeds that are comparable to standard bipolar logic. The AV (MB65xxxx) series is an ideal choice for LSI and VLSI applications that require up to 8000 gates, 2304 bits of RAM, 4608 bits of ROM or for bus interface circuits with high-drive requirements. The AVB (MB67xxxx) series include optional 10 mA buffered outputs and input pull-up/pull-down resistors for easy interfacing with bus organized logic. The AVM (MB66xxxx) series of memory arrays include, in addition to the 1.5K, 2.3K, and 4K gates of logic, two basic sizes of static registered memories:

The C4002 and C1502 have up to 2304 bits of RAM organized in an optional by-nine memory configuration that is system compatible with most modern designs. The 2301 has 1024 bits of RAM that may be configured into any by-four multiple from 256-by-4 to 32-by-32.

The AVM memories contain duplicate decoder and address register logic so that they may be split and used as two independent memories without borrowing any of the unit ceils.

All AV, AVB and AVM arrays use the same basic internal cell structure and common logic Macros.

#### **FEATURES**

- 1.4 ns gate delay typical. (2-Input NAND gate, F.O.=2)

- Static RAM or ROM on chip.

- Silicon-gate 1.8 micron dual metal.

- 100% automatic placement and routing with guaranteed 90% cell utilization.

- Three-state and bidirectional outputs available.

- High-drive output.

- Buffers, I <sub>OL</sub> = 10.0 mA, available.

- Pull-up/pull-down input buffers available.

- Single 5V power supply.

- TTL compatible I/O, CMOS input and Schmitt trigger input.

- Popular CAE workstations supported.

- Over 100 unit cells available for design.

- Predesigned software macros available. (F-Macros).

- Fast turnaround: 5 weeks after final validation.

- Evaluation samples available.

- Extended temperature range available.

| AV-CMOS SERIES  | Device   | Part No. | Gates | 1/0                    | Gate Spee  | d Features     |

|-----------------|----------|----------|-------|------------------------|------------|----------------|

|                 | C2600AV  | MB654xxx | 2640  | 106                    | 1.4 ns     | High Density   |

|                 | C3900AV  | MB653xxx | 3900  | 127                    | 127 1.4 ns |                |

|                 | C5000AV  | MB652xxx | 5022  | 127 1.4 ns             |            | High Density   |

|                 | C6600AV  | MB651xxx | 6664  | 160                    | 1.4 ns     | High Density   |

|                 | C8000AV  | MB650xxx | 8000  | 160                    | 1.4 ns     | High Density   |

| AVB-CMOS SERIES | C350AVB  | MB675xxx | 357   | 38 (42)                | 1.4 ns     | High-Drive     |

|                 | C540AVB  | MB674xxx | 549   | 48 (50) <sup>1</sup>   | 1.4 ns     | High-Drive     |

|                 | C850AVB  | MB673xxx | 852   | 58 (60) <sup>1</sup>   | 1.4 ns     | High-Drive     |

|                 | C1200AVB | MB672xxx | 1245  | 68 (68) <sup>1</sup>   | 1.4 ns     | High-Drive     |

|                 | C1600AVB | MB671xxx | 1674  | 74 (76) <sup>1</sup>   | 1.4 ns     | High-Drive     |

|                 | C2000AVB | MB670xxx | 2052  | 88 (92) <sup>1</sup>   | 1.4 ns     | High-Drive     |

| AVM-CMOS SERIES | C1502AVM | MB662xxx | 1564  | 107 (109) <sup>2</sup> | 1.4 ns 4   | K ROM/2K RAM 3 |

|                 | C2301AVM | MB661xxx | 2375  | 117 (119) <sup>2</sup> |            | K ROM/1K RAM 3 |

| Notes:          | C4002AVM | MB660xxx | 4087  | 120 (122) <sup>2</sup> | 1.4 ns 4   | K ROM/2K RAM 3 |

- 1. I/O numbers in parentheses indicate I/O available when no high-drive outputs are used.

- 2. When BOM is provided.

- 3. Available options.

Copyright • 1986 by Fujitsu Limited and Fujitsu Microelectronics, Inc.

This document contains information considered proprietary by Fujitsu Limited, Tokyo, Japan and its subsidiaries. No part of this document may be copied or reproduced in any form or by any means, or transferred to any third party without the prior written consent of Fujitsu Limited.

#### **ELECTRICAL CHARACTERISTICS**

#### ABSOLUTE MAXIMUM RATINGS 1

(V<sub>ss</sub> = 0V.)

| Rating                  | Symbol           | Minimum               | Typical | Maximum               | Unit  |

|-------------------------|------------------|-----------------------|---------|-----------------------|-------|

| Supply Voltage          | V <sub>DD</sub>  | V <sub>SS</sub> - 0.5 | -       | 6.0                   | volts |

| Input Voltage           | Vı               | V <sub>ss</sub> - 0.5 | -       | V <sub>DD</sub> + 0.5 | volts |

| Output Voltage          | V <sub>0</sub>   | V <sub>SS</sub> - 0.5 | - [     | V <sub>DD</sub> + 0.5 | volts |

| Output Current 2 AVB    | los              | -80                   | -       | 140                   | mA    |

| Output Current 2AV, AVM | los              | -40                   | -       | 70                    | mA    |

| Ot T                    | T                | -65 Ceramic           | -       | 150 Ceramic           | °င    |

| Storage Temperature     | T <sub>STG</sub> | -40 Plastic           | -       | 125 Plastic           | °c    |

| Bias Temperature        | Tbias            | -40 Ceramic           | -       | 125 Ceramic           | °c    |

|                         | · Dias           | -25 Plastic           | _       | 85 Plastic            | °c    |

#### Notes:

- 1. Permanent device damage may occur if the absolute maximum ratings are exceeded. Functional operation should be restricted to the conditions of recommended operation. Exposure to absolute maximum ratings for extended periods may affect device reliability.

- 2. No more than one output can be shorted at a time and no output can be shorted for more than one second.

#### RECOMMENDED OPERATING CONDITIONS

$(V_{ss} = 0V.)$

| Parameter           | Symbol          | Minimum               | Typical | Maximum               | Unit  |  |

|---------------------|-----------------|-----------------------|---------|-----------------------|-------|--|

| Supply Voltage      | V <sub>DD</sub> | 4.75                  | 5.0     | 5.25                  | volts |  |

| Input High Voltage  | VIH             | 2.2                   | -       | -                     | volts |  |

| for CMOS Inputs     | V <sub>IH</sub> | V <sub>DD</sub> x 0.7 | -       | -                     | volts |  |

| Input Low Voltage   | V <sub>IL</sub> | _                     | -       | 0.8                   | volts |  |

| for CMOS Inputs     | V <sub>IL</sub> | -                     | _       | V <sub>DD</sub> x 0.3 | volts |  |

| Ambient Temperature | TA              | 0                     | -       | 70                    | °c    |  |

AV, AVM SERIES CAPACITANCE (Ta = 25  $^{\circ}$ C,  $V_{OD}$ =  $V_{I}$  = 0 volts, f = 1 MHz.)

| Parameter           | Symbol           | Minimum | Typical | Maximum | Unit |

|---------------------|------------------|---------|---------|---------|------|

| Input Capacitance   | CIN              | _       | -       | 9       | pF   |

| Output Capacitance  | C <sub>OUT</sub> | -       | -       | 9       | pF   |

| I/O Pin Capacitance | C <sub>1/O</sub> |         | -       | 11      | pF   |

### AVB SERIES CAPACITANCE

(Ta = 25 °C, V<sub>DD</sub>= V<sub>I</sub> = 0 volts, f = 1 MHz.)

| Parameter           | Symbol           | Minimum | Typical | Maximum | Unit |

|---------------------|------------------|---------|---------|---------|------|

| Input Capacitance   | CIN              | -       | -       | 8       | pF   |

| Output Capacitance  | Cout             | -       | -       | 16      | pF   |

| I/O Pin Capacitance | G <sub>1/0</sub> | -       | _       | 21      | pF   |

#### DC CHARACTERISTICS

(Recommended operating conditions unless otherwise noted.)

| Parameter                                                                                                          | Symbol           | Minimum               | Typical | Maximum               | Unit  |

|--------------------------------------------------------------------------------------------------------------------|------------------|-----------------------|---------|-----------------------|-------|

| Power Supply Current (Steady state, V <sub>I</sub> = 0V or V <sub>DD</sub> )                                       | I <sub>DDS</sub> | -                     | -       | 100                   | μА    |

| Output High Voltage<br>(I <sub>OH</sub> = -0.4 mA)                                                                 | V <sub>OH</sub>  | 4.2                   | -       | V <sub>DD</sub>       | volts |

| for Driver Output<br>(I <sub>OH</sub> = -0.4 mA)                                                                   | V <sub>OH</sub>  | 4.2                   | -       | V <sub>DD</sub>       | volts |

| Output Low Voltage<br>(I <sub>OL</sub> = 3.2 mA)                                                                   | V <sub>OL</sub>  | V <sub>SS</sub>       | -       | 0.4                   | volts |

| for Driver Output<br>(I <sub>OL</sub> = 10.0 mA)                                                                   | V <sub>OL</sub>  | V <sub>SS</sub>       | -       | 0.5                   | volts |

| Input High Voltage                                                                                                 | VIH              | 2.2                   |         | _                     | volts |

| for CMOS Input                                                                                                     | V <sub>IH</sub>  | V <sub>DD</sub> x 0.7 | -       | _                     | volts |

| Input Low Voltage                                                                                                  | V <sub>IL</sub>  | -                     | -       | 0.8                   | volts |

| for CMOS Input                                                                                                     | V <sub>IL</sub>  |                       | -       | V <sub>DD</sub> x 0.3 | volts |

| Input Leakage Current<br>(V <sub>i</sub> = 0 - V <sub>DD</sub> )                                                   | lu               | -10                   | -       | 10                    | μА    |

| Input Leakage Current<br>(3-state, V <sub>I</sub> = 0 - V <sub>DD</sub> )                                          | I <sub>LZ</sub>  | -10                   | -       | 10                    | μА    |

| Input Pull-Up/Down<br>Resistor<br>(Pull up: V <sub>IL</sub> = 0V,<br>Pull down V <sub>IH</sub> = V <sub>DD</sub> ) | RP               | 25                    | 50      | 100                   | kΩ    |

## AC CHARACTERISTICS DELAY MULTIPLIERS FOR PRE-LAYOUT SIMULATION

(See AV Series Gate Arrays Unit Cell Library)

| Parameter         | Symbol                             | Minimum    | Typical | Maximum   | Unit |

|-------------------|------------------------------------|------------|---------|-----------|------|

| Propagation Delay | t <sub>pd</sub>                    |            |         |           |      |

| Enable Time       | t <sub>PZL</sub> /t <sub>PZH</sub> |            |         |           |      |

| Disable Time      | t <sub>PLZ</sub> /t <sub>PHZ</sub> | Typ x 0.45 |         | Typ x 1.6 | ns   |

| Set-up Time       | t <sub>SD</sub>                    |            |         |           |      |

| Hold Time         | t <sub>HD</sub>                    |            |         |           |      |

| Pulse Width       | t <sub>cw</sub>                    |            |         |           |      |

# AC CHARACTERISTICS DELAY MULTIPLIERS FOR POST-LAYOUT SIMULATION (See AV Series Gate Arrays Unit Cell Library)

| Parameter | Symbol | Minimum    | Typical | Maximum    | Unit |

|-----------|--------|------------|---------|------------|------|

|           | -      | Typ x 0.50 | -       | Typ x 1.55 | ns   |

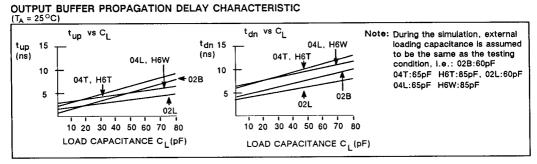

## AV AND AVB-CMOS GATE ARRAY CHIP LAYOUT AND ORGANIZATION

#### CHIP LAYOUT AV AND AVB SERIES EXCEPT C6600AV AND C8000AV

#### AV AND AVB ORGANIZATION

| Device   | Total Basic Cells | Columns | Basic Celis per Column | Total I/O Cells      |

|----------|-------------------|---------|------------------------|----------------------|

| C350AVB  | 357               | 7       | 51                     | 38 (42) <sup>1</sup> |

| C540AVB  | 549               | 9       | 61                     | 48 (50) <sup>1</sup> |

| C850AVB  | 852               | 12      | 71                     | 58 (60) <sup>1</sup> |

| C1200AVB | 1245              | 15      | 83                     | 68 (68) <sup>1</sup> |

| C1600AVB | 1674              | 18      | 93                     | 74 (76) <sup>1</sup> |

| C2000AVB | 2052              | 18      | 114                    | 88 (92)              |

| C2600AV  | 2640              | 22      | 120                    | 106                  |

| C3900AV  | 3900              | 25      | 156                    | 127                  |

| C5000AV  | 5022              | 27      | 186                    | 127                  |

#### Note:

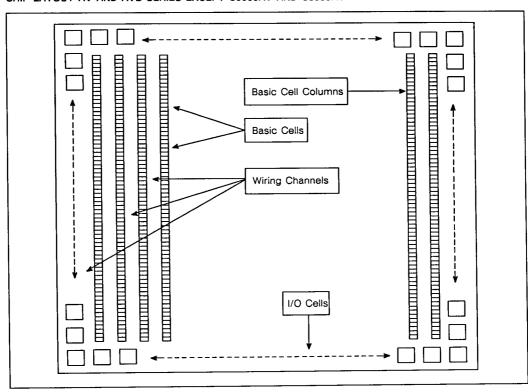

# C6600AV, C8000AV AND AVM GATE ARRAY CHIP LAYOUT AND ORGANIZATION

#### C6600AV, C8000AV CHIP LAYOUT

#### C6600AV, C8000AV ORGANIZATION

| Device  | Total Basic Cells | Blocks | BC/Block    | Rows/Block | Columns/Block | Total I/O Cells |

|---------|-------------------|--------|-------------|------------|---------------|-----------------|

| C6600AV | 6664              | 4      | 1000 - 2000 | -          | Variable      | 160             |

| C8000AV | 8000              | 4      | 2000        | 100        | 20            | 160             |

<sup>1.</sup> I/O numbers in parentheses indicate I/O available when no high-drive outputs are used.

#### C1502AVM, C2301AVM CHIP LAYOUT

The maximum basic cells used for the basic cell block should not exceed 90% of the total available. The block is configurable for either 1024 or 2304 total bits BASIC CELL BLOCK organized from 2-bits per word to 32-bits per word, or 9-bits per word to 36-bits per word. 8-bit word sizes and larger (for C2301AVM) or 18-bit word sizes and larger (for C1502AVM) allow division of the RAM block into two separate RAMSs. ROM can be provided in place of RAM. The ROM block is configurable for either 2048 or 4608 total bits.

#### C4002AVM CHIP LAYOUT

For automatic placement and routing the maximum basic cells should not exceed 90% of the total available.

The RAM block is configurable for 2304 total bits organized from 9 bits per word to 36 bits per word.

18-bit word sizes and larger allow division of the RAM block into two separate RAMs.

ROM can be provided in place of RAM. The ROM block is configured for 4608 total bits.

#### C1502AVM, C2301AVM, C4002AVM ORGANIZATION

| Device   | Total Basic Cells | Columns | BC/Column  | RAM Size            | Total I/O Cells        |

|----------|-------------------|---------|------------|---------------------|------------------------|

| C1502AVM | 1564              | 23      | 68         | 2K, 9-bit to 36-bit | 107 (109) <sup>1</sup> |

| C2301AVM | 2375              | 25      | 95         | 1K, 4-bit to 32-bit | 117 (119) <sup>1</sup> |

| C4002AVM | 4087              | 6<br>25 | 202<br>115 | 2K, 9-bit to 36-bit | 120 (122) <sup>1</sup> |

#### Note:

#### **DESIGN COMPONENTS**

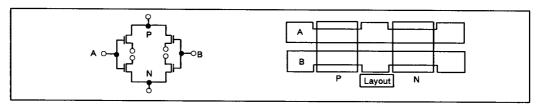

#### BASIC CELL

An unprogrammed gate array is an array of basic cells. Thus the "gates" in a gate array are actually the basic cells which will make up final logic. Fujitsu's basic cell contains enough transistors to form a two-input NAND gate.

Unprogrammmed Basic Cell

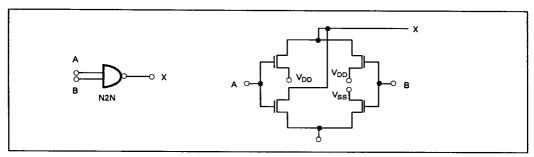

#### UNIT CELL

A design is implemented in a gate array by logicially combining unit cells from the Fujitsu unit cell library to form the logic. Fujitsu provides unit cells to perform most common logic functions and the designer need only name the unit cells required to form the higher level logic functions of his design.

Two-Input NAND Gate Unit Cell (One Basic Cell)

A two-input NAND gate requires only one basic cell to implement. Other unit cells may require as many as 60 or more basic cells. (C47, a counter, requires 68.) Over 100 unit cells are available for design with AV/AVB/AVM-CMOS arrays.

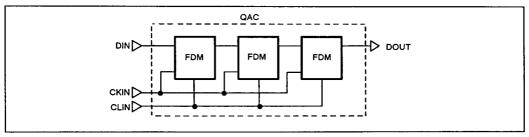

#### **USER MACROS**

User Macros are groups of unit cells which perform an identifiable function within the design. It is a user macro because it is defined by the designer. The primary utility of a user macro is that it allows the designer to compose a macro function from unit cells once, then use it any number of times simply by calling it by name.

User Macro QAC is Composed of Three FDM Unit Cells

MB65xxxx MB66xxxx MB67xxxx

#### F-MACROS

F-Macros are created and offered by Fujitsu to emulate the function of popular industry-standard TTL devices. They are identical in application to user macros. Using F-Macros, a designer may convert an existing design directly into gate array. For example, the 74LS191 function is emulated by the Fujitsu F191 F-Macro.

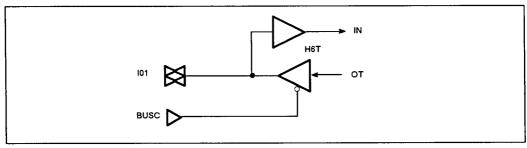

#### I/O Cells

The I/O cells located on the periphery of the gate array chip are programmable to any of the input or output buffers available. The actual location of an I/O buffer on the chip is determined by the location on the chip of the associated circuitry and any pin location requirements that may be in effect.

**Bidirectional Buffer**

#### **DESIGN DESCRIPTION**

#### **DESIGN DESCRIPTION**

Fujitsu requires only two basic inputs to complete a gate array design: A Logic Description and a Test Description. The logic description defines the logical function of the circuit to be implemented in the array. The test description defines the electrical operation required.

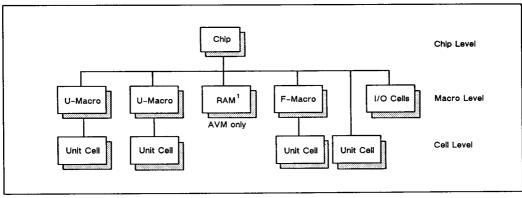

#### AV. AVB AND AVM LOGIC HIERARCHY

#### Note:

1. ROM can be made available in place of RAM.

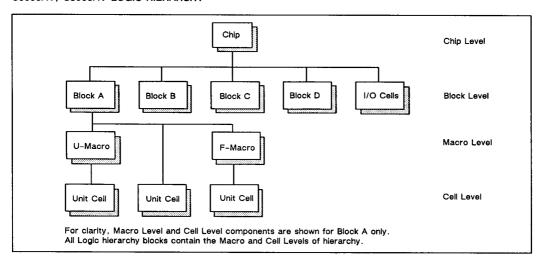

#### C6600AV, C8000AV LOGIC HIERARCHY

#### LOGIC DESCRIPTION

The Logic Description, sometimes called a "netlist," calls out the unit cells utilized and their interconnection to form the designer's circuit. Fujitsu uses a proprietary description language, the Fujitsu Logic Description Language (FLDL), to enter the logic description language into the design flow to produce the array design. Designers may prepare their logic description using FLDL or use other description media which Fujitsu will convert to FLDL. Designers using Daisy, Valid or Mentor design workstations are provided with conversion programs as part of the Fujitsu Design Kits for these workstations. In all cases, the design description must follow the fundamental design description structure provided by the logic hierarchy. In many cases Fujitsu will provide turnkey design services.

#### LOGIC HIERARCHY

The Logic Description is organized into a hierarchy of design components. The logic hierarchy provides the fundamental structure for all logic description inputs and allows a designer to divide his logic into major macro functions and follow a step-by-step approach in describing their interconnection. User Macros may be created to allow repeating the same logic function many times in the design without describing the entire function each time. Fujitsu provides predefined macros (F-Macros) which duplicate the function of many popular industry-standard TTL devices and RAM macros which provide from 1K to 2K of single-port static RAM on chip. Also, ROM macros can be provided. The C6600AV and C8000AV are further divided into "blocks" of cells to ease the layout operations.

#### CHIP LEVEL

The Chip Level of the logic description defines the interconnection of the design components to each other and the I/O cells. For most AV-CMOS family devices, all types of design components including user macros, F-Macros, RAM macros, ROM macros, and unit cells may be interconnected with each other and the I/O cells to form the chip level logic provided the basic cells total required does not exceed 90% of the basic cell total on the array. For the C6600AV and C8000AV, the same basic cells total restriction applies; the chip level of hierarchy describes only the interconnection of the blocks with the I/O cells to form the chip level logic.

#### BLOCK LEVEL

The Block Level of the logic description defines the interconnection of design components to form each block of the logic description. C6600AV and C8000AV allow up to 90% of the available basic cells to be utilized for each block. Designers may utilize any of the available design components, including user macros, F-Macros and unit cells for interconnection within the blocks provided the basic cell total required to implement the block design does not exceed the maximum allowed for the block. C6600AV provides a flexible block arrangement, allowing block sizes to range between 1000 and 2000 basic cells provided the total does not exceed 90% of the total available on the array.

#### MACRO LEVEL

The Macro Level of the logic description defines the interconnection of unit cells to form user macros. F-Macros may not be used to form user macros. Nor may user macros be nested to form other user macros. The total number of basic cells included in one User Macro can be larger than the total number of basic cells available in one column of the array provided the number of BCs in any of the Unit Cells used in the User Macro does not exceed the total number of basic cells available in one column of the array.

#### **TEST DESCRIPTION**

The Test Description defines the electrical performance required of the finished array. Test descriptions are used for all simulation operations and are ultimately converted into final test programs for prototype and production testing. Fujitsu utilizes the proprietary Fujitsu Test Data Description Language (FTDL) for all test description inputs to the design operation. As with the logic description, designers may submit test descriptions utilizing other media and Fujitsu will convert to FTDL. Designers using Daisy, Valid or Mentor design workstations are provided with conversion programs as part of the Fujitsu Design Kits for these workstations. Turnkey services may be available. A complete test description will include D.C. testing and functional testing. Delay testing may be performed under some conditions.

#### **DESIGN DEVELOPMENT FLOW**

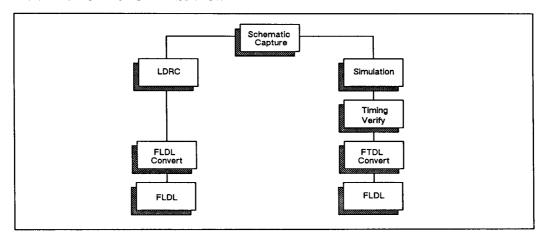

#### DESIGN WORKSTATION SIMPLIFIED FLOW

#### WORKSTATION DESIGN

Fujitsu provides workstation support software free of charge to designers using workstations manufactured by Dalsy, Valid or Mentor. This software includes a complete design library of unit cells, I/O cells, and memory macros for AV-CMOS gate arrays and conversion programs which generate the logic and test descriptions in the FLDL and FTDL languages required for design input to Fulitsu.

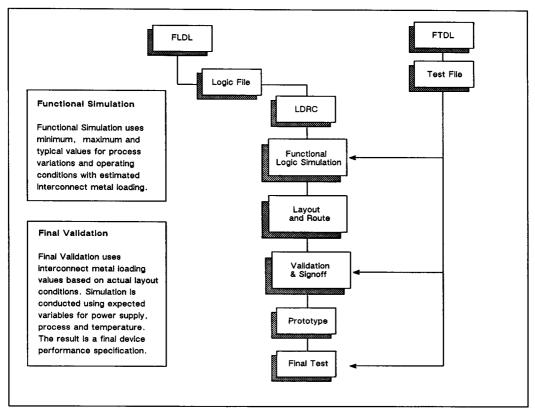

#### FUJITSU DESIGN DEVELOPMENT FLOW SUMMARY

Fujitsu accepts a variety of design input media but all media must be converted to logic and test descriptions using the FLDL and FTDL description languages. Fujitsu may request additional engineering fees for conversion. Logic and test descriptions are collected into data files for access by the Fujitsu CAD system. The test data file provides the basic information used to conduct simulations and generate the final test program.

#### LDRC

The Logic Design Rule Check conducts a verification that no design rule violations for interconnect, hierarchy or design description language syntax have occurred, and that the description is complete. Fujitsu will work with the designer to resolve any discrepancies before proceeding with the design development.

1-50

#### SIMULATION

The Functional Logic Simulation is conducted using minimum, maximum and typical values for process, power supply and temperature conditions, with estimated interconnect metal loading. The functional logic simulation must successfully demonstrate device operation according to the designer's test description before any layout operations are attempted.

#### FINAL VALIDATION

Final Validation is conducted to produce the device operating specification for approval and signoff by the designer. The simulation is conducted using values for interconnect metal loading based on the actual layout. Full range values for process, temperature and power supply variation are also used. A final operating specification is presented to the designer which defines the parameters which will be guaranteed by Fujitsu in the prototype and production devices.

#### FUJITSU DESIGN DEVELOPMENT FLOW SUMMARY

#### **PROTOTYPES**

At the completion of the design development Fujitsu provides the designer with prototypes for on-site design evaluation. Ten prototype devices (Five for C8000AV) are provided with the development fee. Additional prototypes may be provided for an additional fee.

## UNIT CELL LIBRARY

|                    | Unit<br>Cell | Function                              | Basic<br>Cells | Unit<br>Cell | Function                                   | Basic<br>Cells |

|--------------------|--------------|---------------------------------------|----------------|--------------|--------------------------------------------|----------------|

| INVERTER,<br>CLOCK | V1N          | Inverter                              | 1              | КЗВ          | Gated Clock Buffer (AND)                   | 3              |

| BUFFER FAMILY      | V2B          | Power Inverter                        | 1              | K4B          | Gated Clock Buffer (OR)                    | 3              |

|                    | K1B          | Clock Buffer                          | 2              | ксв          | Block Clock Buffer                         | 11             |

|                    | K2B          | Power Clock Buffer                    | 3              | -            | _                                          |                |

|                    |              |                                       |                |              |                                            |                |

| NAND FAMILY        | N2N          | 2-Input NAND                          | 1              | N6B          | 6-Input Power NAND                         | 5              |

|                    | N3N          | 3-input NAND                          | 2              | N8B          | 8-input Power NAND                         | 6              |

|                    | N4N          | 4-input NAND                          | 2              | N9B          | 9-input Power NAND                         | 7              |

|                    | N2B          | 2-Input Power NAND                    | 3              | NCB          | 12-input Power NAND                        | 9              |

|                    | N3B          | 3-input Power NAND                    | 3              | NGB          | 16-Input Power NAND                        | 11             |

|                    | N4B          | 4-Input Power NAND                    | 4              | -            | -                                          |                |

|                    |              |                                       |                |              |                                            |                |

| AND FAMILY         | N2P          | 2-Input Power AND                     | 2              | N4P          | 4-Input Power AND                          | 3              |

|                    | N3P          | 3-Input Power AND                     | 3              | _            |                                            |                |

|                    |              |                                       |                |              |                                            |                |

| NOR FAMILY         | R2N          | 2-input NOR                           | 1              | R6B          | 6-input Power NOR                          | 5              |

|                    | R3N          | 3-Input NOR                           | 2              | R8B          | 8-Input Power NOR                          | 6              |

|                    | R4N          | 4-input NOR                           | 2              | R9B          | 9-input Power NOR                          | 7              |

|                    | R2B          | 2-input Power NOR                     | 3              | RCB          | 12-Input Power NOR                         | 9              |

|                    | R3B          | 3-input Power NOR                     | 3              | RGB          | 16-input Power NOR                         | 11             |

|                    | R4B          | 4-input Power NOR                     | 4              |              | _                                          |                |

|                    |              |                                       |                |              |                                            |                |

| OR FAMILY          | R2P          | 2-input Power OR                      | 2              | R4P          | 4-input Power OR                           | 3              |

|                    | R3P          | 3-input Power OR                      | 3              | -            | -                                          | -              |

| •                  |              |                                       |                |              |                                            |                |

| ENOR/EOR           | X1B          | Power ENOR                            | 4              | X2B          | Power EOR                                  | 4              |

|                    |              |                                       |                |              |                                            |                |

| AND-NOR FAMILY     | D14          | 2-wide 3-AND 4-input<br>AND-OR invert | 2              | D34          | 3-wide 2-AND 4-input<br>AND-OR invert      | 2              |

|                    | D23          | 2-wide 2-AND 3-input<br>AND-OR Invert | 2              | D44          | 2-wide 2-OR 2 AND 4-input<br>AND-OR invert | 2              |

|                    | D24          | 2-wide 2-AND 4-Input<br>AND-OR Invert | 2              |              | _                                          | -              |

|                    |              |                                       |                |              |                                            |                |

| OR-NAND FAMILY     | G14          | 2-wide 3-OR 4-input<br>OR-AND invert  | 2              | G34          | 3-wide 2-OR 4-input<br>OR-AND invert       | 2              |

|                    | G23          | 2-wide 2-OR 3-input<br>OR-AND Invert  | 2              | G44          | 2-wide 2-AND 2-OR<br>4-input OR-AND invert | 2              |

|                    | G24          | 2-wide 2-OR 4-input<br>OR-AND Invert  | 2              | -            | -                                          | -              |

### UNIT CELL LIBRARY

| MULTIPLEXER | 4 |

|-------------|---|

| FAMILY      |   |

| Unit<br>Cell | Function           | Basic<br>Cells | Unit<br>Cell | Function          | Basic<br>Cells |

|--------------|--------------------|----------------|--------------|-------------------|----------------|

| T24          | Power 2-AND 4-wide | 6              | U24          | Power 2-OR 4-wide | 6              |

| T26          | Power 2-AND 6-wide | 9              | U26          | Power 2-OR 6-wide | 9              |

| T28          | Power 2-AND 8-wide | 11             | U28          | Power 2-OR 8-wide | 11             |

| T32          | Power 3-AND 2-wide | 5              | U32          | Power 3-OR 2-wide | 5              |

| T33          | Power 3-AND 3-wide | 7              | U33          | Power 3-OR 3-wide | 7              |

| T34          | Power 3-AND 4-wide | 9              | U34          | Power 3-OR 4-wide | 9              |

| T42          | Power 4-AND 2-wide | 6              | U42          | Power 4-OR 2-wide | 6              |

| T43          | Power 4-AND 3-wide | 9              | U43          | Power 4-OR 3-wide | 9              |

| T44          | Power 4-AND 4-wide | 11             | U44          | Power 4-OR 4-wide | 11             |

#### FLIP-FLOP FAMILY

| FD2 | Power DFF                       | 8  | FDD | Positive Edge Power DFF with Clear/Preset | 11 |

|-----|---------------------------------|----|-----|-------------------------------------------|----|

| FD3 | Power DFF with Preset           | 9  | FDE | Positive Edge Power DFF with Clear        | 10 |

| FD4 | Power DFF with Clear/<br>Preset | 10 | FDG | Positive Edge with Clear                  | 9  |

| FD5 | Power DFF with Clear            | 9  | FJD | Positive Edge Power JKFF with Clear       | 12 |

| FD6 | DFF                             | 7  | FJ4 | Power JKFF with Clear                     | 11 |

| FD7 | DFF with Clear                  | 8  | FJ5 | Power JKFF with Clear/<br>Preset          | 12 |

| FD8 | DFF with Latch                  | 9  | -   | _                                         | _  |

FLIP-FLOP FAMILY USING TRANSMISSION GATES

| FDM | DFF            | 6  | FDP | DFF with Set/Reset   | 8  |

|-----|----------------|----|-----|----------------------|----|

| FDN | DFF with Set   | 7  | FDQ | 4-bit DFF            | 21 |

| FDO | DFF with Reset | 7  | FDR | 4-bit DFF with Clear | 26 |

| FDS | 4-Bit DFF      | 20 | -   | -                    | _  |

#### LATCH FAMILY

| LT1 | SET-RESET with Clear           | 4  | LT3 | 4-bit Data Latch      | 15 |

|-----|--------------------------------|----|-----|-----------------------|----|

| LT2 | 1-bit Data Latch               | 4  | LT4 | 4-bit Data Latch      | 13 |

| LTK | Data Latch                     | 4  | LTL | Data Latch with Clear | 5  |

| LTM | 4-Bit Data Latch with<br>Clear | 15 | -   | -                     | -  |

# SHIFT REGISTER FAMILY

| FS1 | 4-bit S <sub>in</sub> -P <sub>out</sub> | 18 | FS3 | 4-bit with Async Load | 34 |

|-----|-----------------------------------------|----|-----|-----------------------|----|

| FS2 | 4 bit S in -Pout with Sync Load         | 30 | _   | _                     | -  |

## DECODER FAMILY

| DE2 2:4 Decoder 5 DE3 3:8 Decoder 1 | 15 |

|-------------------------------------|----|

|-------------------------------------|----|

### **COUNTER FAMILY**

| 1 | C11 | Flip-Flop for Counter | 11 | C43              | 4-bit Sync UP with Clear | 48 |

|---|-----|-----------------------|----|------------------|--------------------------|----|

|   | C41 | 4-bit Async           | 24 | C45              | 4-bit Sync UP            | 48 |

|   | C42 | 4-bit Sync            | 32 | C47 <sup>1</sup> | 4-bit Sync UP/DOWN       | 68 |

#### Note:

<sup>1.</sup> C47 is not available for C-350AVB and C540AVB.

### **UNIT CELL LIBRARY**

| SELECTO | OR FA | MILY |

|---------|-------|------|

|   | Unit<br>Cell | Function          | Basic<br>Cells | Unit<br>Cell | Function          | Basic<br>Cells |

|---|--------------|-------------------|----------------|--------------|-------------------|----------------|

| Ē | T2B          | 2:1 Selector      | 2              | V3A          | 1:2 Selector      | 2              |

|   | T2C          | Dual 2:1 Selector | 4              | V3B          | Dual 1:2 Selector | 3              |

|   | T2D          | 2:1 Selector      | 2              | T5A          | 4:1 Selector      | 5              |

#### COMPARATOR

| MC4 | 4-bit Magnitude<br>Comparator | 42 | 1 | - | - |

|-----|-------------------------------|----|---|---|---|

#### ADDER FAMILY

| A1N | 1-bit Full Adder | 8  | A4H | 4-bit Full Adder | 50 |

|-----|------------------|----|-----|------------------|----|

| A2N | 2-bit Full Adder | 16 | _   | _                | _  |

#### SCHMITT TRIGGER

# SM1 Schmitt Trigger 8 SM2 Schmitt Trigger 7

# DELAY UNIT

| BD3 | Buffer (Delay Cell) | 5 | BD6 | Buffer (Delay Cell) | 17 |

|-----|---------------------|---|-----|---------------------|----|

| BD5 | Buffer (Delay Cell) | 9 | _   |                     | -  |

### I/O CELL FAMILY

| IOD               | Input Buffer                | 0 | 11/0              | Classed Innex Bufforthurantinus  | 0 |

|-------------------|-----------------------------|---|-------------------|----------------------------------|---|

| I2B               | Input Buffer                |   | IKB               | Clocked Input Buffer (Inverting) |   |

| I2BU <sup>2</sup> | I2B with Input Pull-up      | 0 | IKBU <sup>2</sup> | iKB with Input Pull-up           | 0 |

| 12BD <sup>2</sup> | I2B with Input Pull-down    | 0 | IKBD <sup>2</sup> | IKB with Input Pull-down         | 0 |

| ILB               | Clocked Input Buffer        | 0 | I2C               | CMOS Interface Input Buffer      | 0 |

| ILBU <sup>2</sup> | ILB with Input Pull-up      | 0 | 120               | (True & Inverter)                |   |

| ILBD <sup>2</sup> | ILB with Input Pull-down    | 0 | I2CU <sup>2</sup> | I2C with input Pull-up           | 0 |

| IT1               | Input Buffer for Schmitt-   | 0 | I2CD <sup>2</sup> | I2C with Input Pull-down         | 0 |

|                   | Trigger Input               |   | н6Т               | Tri-state Output & Input Buffer  | 0 |

| IT1U <sup>2</sup> | IT1 with Input Pull-up      | 0 | H6TU <sup>2</sup> | H6T with Input Pull-up           | 0 |

| IT1D <sup>2</sup> | IT1 with Input Pull-down    | 0 | H6TD <sup>2</sup> | H6T with Input Pull-down         | 0 |

| O2B               | Output Buffer               | 0 | O4T               | Tri-state Output Buffer          | 0 |

| 02L <sup>2</sup>  | Power Output Buffer (True)  | 0 | O4W <sup>2</sup>  | Power Tri-state Output Buffer    | 0 |

| H6W <sup>2</sup>  | Power Tri-state Output and  | 0 | 04                | (True)                           |   |

| HOW               | Input Buffer (True)         | • | H6C <sup>2</sup>  | Tri-state Output and CMOS        | 0 |

| H6WU <sup>2</sup> | H6W with Input Pull-up      | 0 | noc .             | Interface Input Buffer (True)    | , |

| H6WD <sup>2</sup> | H6W with Input Pull-down    | 0 | H6CU <sup>2</sup> | H6C with Input Pull-up           | 0 |

|                   | Power Tri-state Output and  | 0 | H6CD <sup>2</sup> | H6C with input Pull-down         | 0 |

| H6E <sup>2</sup>  | CMOS Interface Input Buffer | ۰ | H6EU <sup>2</sup> | H6E with input Pull-up           | 0 |

|                   | (True)                      |   | H6ED <sup>2</sup> | H6E with Input Pull-down         | 0 |

#### Note

- 1. SM1 and SM2 must not be used together in one chip.

- 2. Available only for AVB.

### F-MACRO LIBRARY

#### F-MACRO FUNCTION

Fujitsu's F-Macros are direct software macro implementations of popular industry-standard TTL functions. They may be used in the design exactly the same as user macros. Designers's converting existing TTL designs to gate array will find the F-Macro a particularly useful implementation.

F-MACROS AVAILABLE TO REPLACE THESE TTL DEVICES

| Device       | Basic Cells                                      | Device         | Basic Celis | Device | Basic Cell                                       |

|--------------|--------------------------------------------------|----------------|-------------|--------|--------------------------------------------------|

| 7400         |                                                  | 7498           | 36          | 74176  | 76                                               |

| 7402         |                                                  | 7499           |             | 74177  | 72                                               |

| 7404         |                                                  | 74100          | 60          | 74178  | 63                                               |

| 7408         |                                                  | 74101          |             | 74179  | 71                                               |

| 7410         |                                                  | 74102          |             | 74180  | 33                                               |

| 7411         |                                                  | 74103          |             | 74181  |                                                  |

| 7420         |                                                  | 74106          |             | 74182  | 49                                               |

| 7421         |                                                  | 74107          |             | 74183  | 36                                               |

| 7425         |                                                  | 74108          |             | 74190  | 106                                              |

| 7427         |                                                  | 74109          |             | 74191  | 73 <sup>1</sup>                                  |

| 7430         |                                                  | 74112          |             | 74192  | 92                                               |

| 7432         |                                                  | 74113          |             | 74193  | 82                                               |

| 7442         | 32                                               | 74114          |             | 74194  | 78                                               |

| 7443         | 32                                               | 74116          | 82          | 74195  | 51                                               |

| 7444         | 32                                               | 74120          | 34          | 74198  | 132                                              |

| 7451         | 7                                                | 74135          |             | 74199  | 98                                               |

| 7454         | 9                                                | 74137          | 48          | 74260  | <del>                                     </del> |

| 7455         | 6                                                | 74138          | 28          | 74261  | 107                                              |

| 7456         | T                                                | 74139          | 26          | 74273  | 1                                                |

| 7457         |                                                  | 74147          | 49          | 74278  | 46                                               |

| 7464         | 9                                                | 74148          | 53          | 74279  | 18                                               |

| 7468         | 89                                               | 74150          | 112         | 74280  | 57                                               |

| 7469         | 79                                               | 74151          | 54          | 74283  | 50                                               |

| 7473         | ,,,                                              | 74152          | 29          | 74290  | 45                                               |

| 7474         | <del>                                     </del> | 74153          | 24          | 74293  | 33                                               |

| 7475         | 32                                               | 74154          | 96          | 74298  | 36                                               |

| 7476         | 32                                               | 74155          | 29          | 74298  | 28                                               |

|              | 18                                               | 74157          | 23          | 74375  | +                                                |

| 7477         | 10                                               |                |             |        | 18                                               |

| 7478         | 10                                               | 74158          | 23          | 74377  | 71                                               |

| 7482         | 16                                               | 74160          | 82          | 74378  | 55                                               |

| 7483         | 50                                               | 74161          | 48          | 74379  | 39                                               |

| 7485         | 42                                               | 74162          | 83          | 74381  | 192                                              |

| 7486         |                                                  | 74163          | 48          | 74382  | 201                                              |

| 7487         | <del>                                     </del> | 74164          | 70          | 74386  |                                                  |

| 7490         | 41                                               | 74165          | 73          | 74390  | 82                                               |

| 7491         | 43                                               | 74166          | 80          | 74393  | 52                                               |

| 7492         | 64                                               | 74168          | 111         | 74396  | 60                                               |

| 7493         | 33                                               | 74169          | 741         | 74398  | 37                                               |

| 7494<br>7495 | 47                                               | 74171<br>74174 | 16          | 74399  | 37                                               |

|              | +                                                |                | 46          |        | <del> </del>                                     |

| 7496<br>7497 | 56                                               | 74175          | 32          |        | ļ                                                |

Note:

1. These F-Macros utilize complex unit cells and may not be available for smaller arrays.

### RAM MACRO LIBRARY

### C2301AVM

| 32-W | ORD    |

|------|--------|

|      |        |

| KAM  | MACROS |

| RAM Macro Name | RAM 1 Configuration | RAM 2 Configuration |

|----------------|---------------------|---------------------|

| R51            | 32-word x 32-bit    | <u>-</u>            |

| R51A           | 32-word x 28-bit    | 32-word x 4-bit     |

| R51B           | 32-word x 24-bit    | 32-word x 8-bit     |

| R51C           | 32-word x 20-bit    | 32-word x 12-bit    |

| R51D           | 32-word x 16-bit    | 32-word x 16-bit    |

#### 64-WORD RAM MACROS

| R61  | 64-word x 16-bit | _               |

|------|------------------|-----------------|

| R61A | 64-word x 12-bit | 64-word x 4-bit |

| R61B | 64-word x 8-bit  | 64-word x 8-bit |

#### 128-WORD RAM MACROS

| R71  | 128-word x 8-bit | <del>-</del>     |

|------|------------------|------------------|

| R71A | 128-word x 4-bit | 128-word x 4-bit |

#### 256-WORD RAM MACROS

| R83  | 256-word x 4-bit | _                |

|------|------------------|------------------|

| R83A | 256-word x 2-bit | 256-word x 2-bit |

#### C1502AVM/C4002AVM

| 64-W | ORD .  |

|------|--------|

| RAM  | MACROS |

| RAM Macro Name | RAM 1 Configuration | RAM 2 Configuration |

|----------------|---------------------|---------------------|

| R610           | 64-word x 36-bit    | -                   |

| R611           | 64-word x 20-blt    | 64-word x 16-bit    |

#### 128-WORD RAM MACROS

|   | -                | 128-word x 18-bit | R711 |  |

|---|------------------|-------------------|------|--|

| t | 128-word x 9-bit | 128-word x 9-bit  | R712 |  |

| i | 128-word x 9-b   | 128-word x 9-bit  |      |  |

256-word x 9-blt

256-WORD RAM MACROS

#### **ROM MACRO LIBRARY**

#### C2301AVM

256-WORD ROM MACROS

| ROM Macro Name | Configuration    |          |

|----------------|------------------|----------|

| YRn            | 256-word x 8-bit | <u>-</u> |

#### Note:

R87

### PACKAGE AVAILABILITY MATRIX

# DUAL IN-LINE PACKAGES, PLASTIC SHRINK TYPE (SH-DIP)

# DUAL IN-LINE PACKAGES PLASTIC SKINNY TYPE (SK-DIP)

#### DUAL IN-LINE PACKAGES, PLASTIC (PDIP) PACKAGE PDIP-PRODUCT 16 PDIP-PDIP-PDIP-PDIP PDIP PDIP PDIP PDIP 18 20 22 40 350AVB • • ٠ • • • 540AVB • ٠ • 850AVB • • • • 1200AVB • • • • 1502AVM ٠ • • • 1600AVB • • • • • • 2000AVB ٠ • • ٠ • 2301AVM • ٠ 2600AV • • 3900AV ٠ • • 4002AVM 5000AV • 6600AV 8000AV

| PACKAGE<br>PRODUCT | DIP-<br>28SH<br>SHRINK | DIP-<br>42SH<br>SHRINK | DIP-<br>48SH<br>SHRINK | DIP~<br>64SH<br>SHRINK | DIP-<br>24SK<br>SKINNY |

|--------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 350AVB             | •                      | •                      | •                      |                        |                        |

| 540AVB             | •                      | •                      | •                      | •                      |                        |

| 850AVB             | •                      | •                      | •                      | •                      | Ĭ                      |

| 1200AVB            | •                      | •                      | •                      | •                      |                        |

| 1502AVM            |                        | •                      | •                      | •                      |                        |

| 1600AVB            | •                      | •                      | •                      | •                      |                        |

| 2000AVB            |                        | •                      | •                      | •                      |                        |

| 2301AVM            |                        |                        | •                      | •                      |                        |

| 2600AV             |                        | •                      | •                      | •                      |                        |

| 3900AV             |                        |                        | •                      | •                      |                        |

| 4002AVM            |                        |                        |                        |                        |                        |

| 5000AV             |                        |                        |                        |                        |                        |

| 6600AV             |                        |                        |                        |                        |                        |

| 8000AV             |                        |                        |                        |                        |                        |

#### PLASTIC LEADED CHIP CARRIERS (PLCC)

**CMOS**

**CMOS**

### FLAT PACKS, PLASTIC (FPT)

| PACKAGE<br>PRODUCT |   | PLCC-<br>44 | PLCC-<br>68 | PLCC-<br>84 |

|--------------------|---|-------------|-------------|-------------|

| 350AVB             | • | •           |             |             |

| 540AVB             | • | •           |             |             |

| 850AVB             | • | •           |             | -           |

| 1200AVB            | • | •           |             |             |

| 1502AVM            |   | •           | •           | •           |

| 1600AVB            | • | •           | •           |             |

| 2000AVB            |   | •           | •           |             |

| 2301AVM            |   | •           | •           | •           |

| 2600AV             | • | •           | •           | •           |

| 3900AV             |   | •           | •           | •           |

| 4002AVM            |   |             |             |             |

| 5000AV             |   |             | •           | •           |

| 6600AV             |   |             |             |             |

| 8000AV             |   |             |             |             |

| PACKAGE<br>PRODUCT | FPT-<br>16 | FPT-<br>20 | FPT-<br>24 | FPT-<br>28 | FPT-<br>48 | FPT-<br>64 | FPT-<br>80 | FPT~<br>100 | FPT-<br>120 | FPT-<br>160 |

|--------------------|------------|------------|------------|------------|------------|------------|------------|-------------|-------------|-------------|

| 350AVB             | •          | •          | •          | •          | •          |            |            |             |             |             |

| 540AVB             | •          | •          | •          | •          | •          | •          |            |             |             |             |

| 850AVB             |            |            | •          | •          | •          | •          |            |             |             |             |

| 1200AVB            |            |            | •          | •          | •          | •          | •          |             |             |             |

| 1502AVM            |            |            |            |            | •          | •          | •          | •           |             |             |

| 1600AVB            |            |            |            |            | •          | •          | •          |             |             |             |

| 2000AVB            |            |            |            |            | •          | •          | •          | •           |             |             |

| 2301AVM            |            |            |            |            | •          | •          | •          | •           |             |             |

| 2600AV             |            |            |            |            | •          | •          | •          | •           |             |             |

| 3900AV             |            |            |            |            | •          | •          | •          | •           |             |             |

| 4002AVM            |            |            |            |            |            |            |            |             |             |             |

| 5000AV             |            |            |            |            |            |            | •          | •           |             |             |

| 6600AV             |            |            |            |            |            |            |            |             |             |             |

| 8000AV             |            |            |            |            |            |            |            |             |             |             |

- . QUALIFIED PRODUCTION OFFICIALLY AVAILABLE NOW

- ☐ PACKAGE COMBINATION UNDER DEVELOPMENT

Note:

Contact nearest Fujitsu Design Center for current package information and power supply pin restrictions. Plastic PGA packages (64, 88, 135, 179-pin) are now under development.

### PACKAGE AVAILABILITY MATRIX

#### DUAL IN-LINE PACKAGES, CERAMIC (CDIP)

#### CMOS

| PACKAGE<br>PRODUCT |   | CDIP-<br>18 | CDIP-<br>20 | CDIP-<br>22 | CDIP- | CDIP-<br>28 | CDIP-<br>40 | CDIP- | CDIP-<br>48 |

|--------------------|---|-------------|-------------|-------------|-------|-------------|-------------|-------|-------------|

| 350AVB             | • | •           | •           | •           | •     | •           | •           |       |             |

| 540AVB             | • | •           | •           | •           | •     | •           | •           |       |             |

| 850AVB             |   |             |             | •           | •     | •           | •           |       |             |

| 1200AVB            |   |             |             | •           | •     | •           | •           | •     | •           |

| 1502AVM            |   |             |             |             |       |             | •           | •     | •           |

| 1600AVB            |   |             |             | •           | •     | •           | •           | •     | •           |

| 2000AVB            |   |             |             |             |       | •           | •           | •     | •           |

| 2301AVM            |   |             |             |             |       |             | •           | •     | •           |

| 2600AV             |   |             |             |             |       | •           | •           | •     | •           |

| 3900AV             |   |             |             |             |       |             | •           | •     | •           |

| 4002AVM            |   |             |             |             |       |             |             |       |             |

| 5000AV             |   | Ī           |             |             |       |             |             |       |             |

| 6600AV             |   |             |             |             |       |             |             |       |             |

| 8000AV             |   |             |             |             |       |             |             |       |             |

CERAMIC LEADLESS CHIP CARRIERS (LCC) CERAMIC J-LEADED CHIP CARRIERS (JLCC) CERAMIC PIN GRID ARRAY (PGA)

#### CMOS

| PACKAGE<br>PRODUCT | LCC-<br>28 | LCC-<br>48 | LCC-<br>64 | LCC-<br>68 | JLCC-<br>68 | JLCC-<br>84 | PGA-<br>64 | PGA-<br>88 | PGA-<br>135 | PGA-<br>179 | PGA-<br>256 |

|--------------------|------------|------------|------------|------------|-------------|-------------|------------|------------|-------------|-------------|-------------|

| 350AVB             | •          | •          |            |            |             |             |            |            |             |             |             |

| 540AVB             | •          | •          | •          |            |             |             | •          |            |             |             |             |

| 850AVB             | •          | •          | •          |            |             |             | •          |            |             |             |             |

| 1200AVB            | •          | •          | •          |            |             |             | •          |            |             |             |             |

| 1502AVM            |            | •          | •          |            |             |             | •          | •          | •           |             |             |

| 1600AVB            | •          | •          | •          |            |             |             | •          | •          |             |             |             |

| 2000AVB            |            | •          | •          |            |             |             | •          | •          |             |             |             |

| 2301AVM            |            | •          | •          |            |             |             | •          | •          | •           |             |             |

| 2600AV             |            | •          | •          |            |             |             | •          | •          | •           |             |             |

| 3900AV             |            | •          | •          |            |             |             | •          | •          | •           |             |             |

| 4002AVM            |            |            | •          | •          | 1           |             | •          | •          | •           |             |             |

| 5000AV             |            | •          | •          |            |             |             | •          | •          | •           |             |             |

| 6600AV             |            | 1          | •          |            |             |             | •          | •          | •           | •           |             |

| 8000AV             | 1          |            | •          |            |             |             | •          | •          | •           | •           |             |

- QUALIFIED PRODUCTION OFFICIALLY AVAILABLE NOW

☐ - PACKAGE COMBINATION UNDER DEVELOPMENT

#### Note:

Contact nearest Fujitsu Design Center for current package information and power supply pin restrictions.