# Features

- Contactless power supply and communication interface

- Up to 10 kbaud data rate (R/O)

- Power management for contactless- and battery power supply

- Frequency range 100 to 150 kHz

- 32 x 16-bit EEPROM

- Two wire serial interface

- Shift register supported Biphase and Manchester modulator stage

- Reset I/O line

- Field clock extractor

- Field and gap detection output for wake up and data reception

- · Field modulator with energy-saving damping stage

# Applications

- Overview

- Access control

- Telemetry

- Wireless sensors Par example:

- Wireless passive access and active alarm control for protection of valuables

- Contactless position sensors for alignments of machines

- Contactless status verification and/ or data readout from sensors

# Description

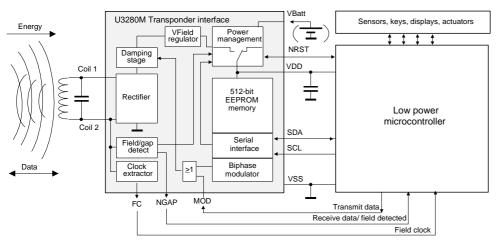

The U3280M IC is a transponder interface which enables contactless ID systems, remote control systems, tag and sensor applications. It is able to supply a microcontroller with power from an RF field via a LC-resonant circuit and it enables the controller for contactless bidirectional data communication via this RF field. It includes a power management which handles switching between magnetic field and battery power supply. To store permanent data like identifiercode and configuration data the U3280M includes a 512-bit EEPROM with an serial interface .

# **Block Diagram**

#### Figure 1.

Iransponder Interface for Microcontroller

# U3280M

Rev. A4, 11-Dec-01

# **Ordering Information**

| Extended Type Number | Package | Remarks          |

|----------------------|---------|------------------|

| U3280M–MFB           | SSO16   | Tube             |

| U3280M–MFBG3         | SSO16   | Taped and reeled |

# **Pin Configuration**

Figure 2.

| VBatt 🗆 | 1 | 16 | 🗆 Coil 2 |

|---------|---|----|----------|

|         | 2 | 15 | 🗆 Coil 1 |

| SCL 🗆   | 3 | 14 | □ n.c.   |

| NRST 🗆  | 4 | 13 | 🗆 n.c.   |

| SDA 🗆   | 5 | 12 | 🗆 n.c.   |

| vss 🗆   | 6 | 11 | 🗆 n.c.   |

| n.c. 🗆  | 7 | 10 | D NGAP   |

| FC 🗆    | 8 | 9  |          |

|         |   |    |          |

# **Pin Description**

| Pin | Symbol            | Function                                                                                                                                                                                     |

|-----|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>Batt</sub> | Power supply voltage input to connect a battery                                                                                                                                              |

| 2   | V <sub>DD</sub>   | Power supply voltage for the $\mu$ C and EEPROM. At this pin a buffer capacitor (0.5 10 $\mu$ F) must be connected to buffer the voltage during field supply and to block the VDD of the mC. |

| 3   | SCL               | Serial clock line                                                                                                                                                                            |

| 4   | NRST              | Reset line bidirectional                                                                                                                                                                     |

| 5   | SDA               | Serial data line                                                                                                                                                                             |

| 6   | V <sub>SS</sub>   | Circuit ground                                                                                                                                                                               |

| 7   | n.c.              | Not connected                                                                                                                                                                                |

| 8   | FC                | Field clock output of the front end clock extractor                                                                                                                                          |

| 9   | MOD               | Modulation input                                                                                                                                                                             |

| 10  | NGAP              | Gap and field detect output                                                                                                                                                                  |

| 11  | n.c.              | Not connected                                                                                                                                                                                |

| 12  | n.c.              | Not connected                                                                                                                                                                                |

| 13  | n.c.              | Not connected                                                                                                                                                                                |

| 14  | n.c.              | Not connected                                                                                                                                                                                |

| 15  | Coil 1            | Coil input 1. Pin to connect a resonant circuitry for communication and field supply                                                                                                         |

| 16  | Coil 2            | Coil input 2, see above                                                                                                                                                                      |

# **Functional Description**

#### The Transponder Interface

The U3280M is a transponder interface IC which is able to operate microcontrollers wireless and battery-independent. Wireless data communication and power supply are handled via an electromagnetic field and the coil antenna of the transponder interface. The U3280M consists of a rectifier stage for the antenna, a power management to handle field and battery power supply, a damping modulator and a field-gap detection stage for contactless data communication, further a field clock extraction and an EEPROM are on the chip.

The internal rectifier stage rectifies the AC from the LC-resonant circuit at the coil inputs and supplies the U3280M device and an additional microcontroller device with power. It is also possible to supply the device via the VBatt input with DC from a battery. The power management handles switching between battery supply (VBatt pin) and field supply automatically. It switches to field supply if a field is applied at the coil and it switches back to battery if the field is removed. The voltage from the coil or the VBatt pin is output at the VDD pin to supply the microcontroller or any other suited device. At the VDD pin a capacitor must be connected to smooth and buffer the supply voltage. This capacitor is also necessary to buffer the supply voltage during the communication (damping and gaps in the field).

For communication, the chip contains a damping stage and a gap-detect circuitry. By means of the damping stage the coil voltage can be modulated to transmit data via the field. It can be controlled with the modulator input (MOD pin) via the microcontroller. The gap-detection circuitry detects gaps in the field and outputs the gap/field signal at the gap-detect output (Pin NGAP).

For the storage of data like keycodes, identifiers and configuration bits a 512-bit EEPROM is available on the chip. It can be read and written by the microcontroller via an  $I^2C$  compatible two-wire serial interface.

The serial interface, the EEPROM and the microcontroller are supplied with the voltage at the VDD pin. That means the microcontroller can read and write the EEPROM if the supply voltage at VDD is in the operating range of the IC.

The U3280M has build in operating modes to support a wide range of applications. These modes can be activated via the serial interface with special mode control bytes.

To support applications with battery supply only, the power management can be switched off by software to disable the automatic switching to field supply.

An on-chip Biphase and Manchester modulator can be activated and controlled by the serial interface. If this modulator is used it modulates the serial data stream at the serial inputs SDA and SCL into a Biphase or Manchester coded signal for the damping stage.

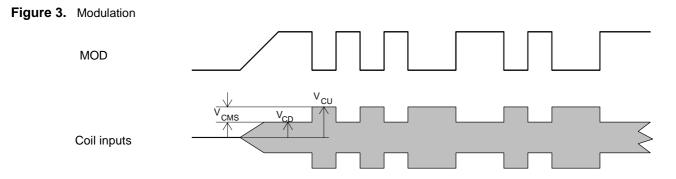

#### Modulation

The transponder interface can modulate the magnetic field by its damping stage to transmit data to a base station. It modulates the coil voltage by varying the coil's load. The modulator can be controlled via the MOD pin. A high level ("1" ) increases the current into the coil and damps the coil voltage. A low level ("0") decreases the current and increases the coil voltage. The modulator generates a voltage stroke of about 2  $V_{pp}$  at the coil. A high level at the MOD pin makes the maximum of the field energy available at VDD. During a reset a high level at the MOD pin causes the optimum conditions for starting the device and charging the capacitor at VDD after the field is applied at the coil.

#### Digital input to control the damping stage (MOD)

MOD = 0: coil not damped

|  | ® |

|--|---|

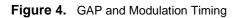

$V_{coil-peak} = VDD \times \sqrt{2} + V_{CMS} = V_{CU}$ MOD = 1: coil damped  $V_{coil-peak} = VDD \times \sqrt{2} = V_{CD}$ V<sub>CMS</sub> = V<sub>CID</sub>: modulation voltage stroke @ coil inputs Note: If the automatic power management is disabled, the internal front end  $V_{\text{DD}}$  is limited at V<sub>DDC</sub>. In this case the value V<sub>DDC</sub> must be used in the above formula. Field Clock The field clock extractor of the interface makes the field clock available for the microcontroller. It can be used to supply timer inputs to synchronize modulation and demodulation with the field clock. **Gap Detect** The transponder interface can also receive data. The base station modulates the data with short gaps in the field. The gap-detection circuit detects these gaps in the magnetic field and outputs the NGAP/field signal at the NGAP pin. A high level indicates that a field is applied at the coil and a low level indicates a gap or that the field is off. The microcontroller must demodulate the incoming data stream at one of its inputs.

# **U3280M Signals and Timing**

#### Digital output of the gap-detection stage (NGAP)

NGAP = 0: gap detected / no field

NGAP = 1: field detected

V<sub>COIL\_peak</sub> = V<sub>FDoff</sub> V<sub>COIL-peak</sub> = V<sub>FDon</sub>

Note: No amplifier is used in the gap-detection stage. A digital Schmitt trigger evaluates the rectified and smoothed coil voltage.

Wake-up Signal If a field is applied at the coil of the transponder interface the microcontroller can be woken up with the wake signal at the NGAP pin. For that purpose the NGAP pin must be connected to an interrupt input of the microcontroller. A high level at the NGAP output indicates an applied field and can be used as wake signal for the microcontroller via an interrupt. The wake signal is generated if the power management switches to field supply. The field-detection stage of the power management has lowpass characteristics to avoid generating of wake signals and unnecessary switching between battery and field supply in case of interferences at the coil inputs.

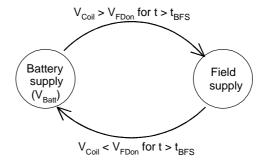

**Power Supply** The U3280M has a power management that handles two power supply sources. Normally the IC is supplied by a battery at the VBatt pin. If a magnetic field is applied at the LC-resonant circuit of the device the field detection circuit switches automatically from VBatt to field supply.

The VDD pin is used to connect a capacitor to smooth the voltage from the rectifier and to buffer the power while the field is modulated by gaps and damping. The EEPROM and the connected controller always operate with the voltage at the VDD pin.

Note: During field supply the maximum energy from the field is used if a high level is applied at the MOD input!

There are different conditions to switch from the battery to field and back from field to the battery.

The power management switches from battery to field if the rectified voltage (Vcoil) from the coil inputs becomes higher than the field-on-detection voltage ( $V_{FDon}$ ), even if no battery voltage is available (0 < VBatt < 1.8 V). It switches back to battery if the coil voltage becomes lower than the field-off-detection voltage ( $V_{FDoff}$ ).

The field detection stage of the power management has lowpass characteristics to suppress noise. An applied field needs a time delay  $t_{BFS}$  (battery-to-field switch delay) to change the power supply. If the field is removed from the coil, the power management will generate a reset that can be connected to the microcontroller.

Figure 5. Switch conditions for the power management

Note: The rectified supply voltage from the coil is limited to  $V_{DDC}$  (2.9 V). During field supply the battery is switched off and  $V_{DD}$  changes to  $V_{DDC}$ .

**Automatic Power**

Management

# AMEL

Controlling the Power Management via the Serial Interface The automatic mode of the power management can be switched off and on by a command from the microcontroller. If the automatic mode is switched off the IC is always supplied by the battery up to the next power-on reset or to a switch on command. The power management-on and -off command must be transferred via the serial interface.

If the power managment is switched off and the device is supplied from the battery it can communicate via the field without load the field. This mode can be used to realize applications with battery supply if the field is to weak to supply the IC with power.

**Buffer Capacitor C**<sub>B</sub> The buffer capacitor connected at VDD is used to buffer the supply voltage for the microcontroller and the EEPROM during field supply. It smoothes the rectified AC from the coil and buffers the supply voltage during modulation and gaps in the field. The size of this capacitor depends on the application. It must be of a dimension so that during modulation and gaps the ripple on the supply voltage is in the range of 100 mV to 300 mV. During gaps and damping the capacitor is used to supply the device, that means the size of the capacitor depends on the length of the gaps and damping cycles.

Example: for a supply current 350  $\mu$ A, 200 mV ripple @ V<sub>DD</sub>

| No Field Supply During | Necessary C <sub>B</sub> |

|------------------------|--------------------------|

| 250 μs                 | 470 nF                   |

| 500 μs                 | 1000 nF                  |

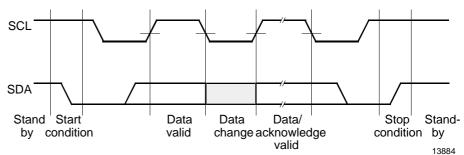

**Serial Interface** The transponder interface has an I<sup>2</sup>C like serial interface to the microcontroller for read and write accesses to the EEPROM. In a special mode the serial interface can also be used to control the Biphase/ Manchester modulator or the ower management of the U3280M.

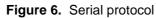

The serial interface of the U3280M device must be controlled by a master device (normally the microcontroller) which generates the serial clock and controls the access via the SCL and SDA line. SCL is used to clock the data in and out of the device. SDA is a bidirectional line and used to transfer data into and out of the device. The following protocol is used for the data transfers.

**Serial Protocol**

- Data states on the SDA line changing only during SCL is low.

- Changes in the SDA line while SCL is high will be interpreted as START or STOP condition.

- A STOP condition is defined as high-to-low transition on the SDA line while the SCL line is high.

- Each data transfer must be initialized with a START condition and terminated with a STOP condition. The START condition wakes the device from standby mode and the STOP condition returns the device to standby mode.

- A receiving device generates an acknowledge (A) after the reception of each byte. For that the master device must generate an extra clock pulse. If the reception was successfull the receiving master or slave device pulls down the SDA line during that clock cycle. If in transmit mode an acknowledge is not detected (N) by the interface, it will terminate further data transmissions and will go into receive mode. A master device must finish its read operation by a not acknowledge and then issue a stop condition to place the device into a known state.

#### **Control Byte Format**

|       |    | EEP   | ROM add | lress | Mode<br>bi |    | Read/<br>NWrite |      |      |

|-------|----|-------|---------|-------|------------|----|-----------------|------|------|

| Start | A4 | A3 A2 |         | A1    | A0         | C1 | C0              | R/NW | Ackn |

The control byte follows the start condition and consists of the 5-bit row address, 2 mode control bits and the read/not-write bit.

#### **Data Transfer Sequence**

| Start Control byte Ackn Data byte Ackn Data byte Ackn Stop |

|------------------------------------------------------------|

|------------------------------------------------------------|

- Before the start condition and after the stop condition the device is in standby mode and the SDA line is switched as input with pull-up resistor.

- The start condition follows a control byte that determines the following operation. Bit 0 of the control byte is used to control the following transfer direction. A "0" defines a write access and a "1" a read access.

The EEPROM has a size of 512 bit and is organized as  $32 \times 16$  bit matrix. To read and

#### EEPROM

write data to and from the EEPROM serial interface must be used. The interface supports one and two byte write accesses and one to n-byte read accesses to the EEPROM.

**EEPROM - Operation Modes** The operating modes of the EEPROM are defined via the control byte. The control byte contains the row address, the mode control bits and the read/not-write bit, that is used to control the direction of the following transfer. A "0" defines a write access and a "1" a read access. The five address bits select one of the 32 rows of EEPROM memory to be accessed. For all accesses the complete16-bit word of the selected row is loaded into a buffer. The buffer must be read or overwritten via the serial interface. The two mode control bits C1 and C2 define in which order the accesses to the buffer are performed: High byte – low byte or low byte – high byte. The EEPROM supports also autoincrement and autodecrement read operations. After sending the start address with the corresponding mode consecutive memory cells can be read row by row without transmission of the row addresses.

Two special control bytes allow to initialize the complete EEPROM with "0" or with "1".

# Write Operations The EEPROM permits 8-bit and 16-bit write operations. A write access starts with the START condition followed by writing a write control byte and one or two data bytes from the master. It is complete with the STOP condition from the master after the acknowledge cycle.

If the EEPROM receives the control byte it loads the addressed memory cell into a 16bit read/write buffer. The following data bytes overwrites the buffer. The internal EEPROM programming cycle is started by a stop condition after the first or second data byte. During the programming cycle the addressed EEPROM cells are cleared and the contents of the buffer is written back to the into the EEPROM cells. The complete erasewrite cycle takes about 10 ms.

# Acknowledge polling If the EEPROM is busy with an internal write cycle all inputs are disabled and the EEPROM will not acknowledge until the write cycle is finished. This can be used to determine when the write cycle is complete. The master must perform acknowledge polling by sending a start condition followed by the control byte. If the device is still busy with the write cycle, it will not return an acknowledge and the master has to generate a stop condition or perform further acknowlege polling sequencies.

If the cycle is complete, it returns an acknowledge and the master can then proceed with the next read or write cycle.

#### Write One Data Byte

Start Control byte A Data byte 1 A Stop

#### Write Two Data Bytes

| Start Control byte A Data byte 1 A Data byte 2 | А | Stop | 1 |

|------------------------------------------------|---|------|---|

|------------------------------------------------|---|------|---|

#### Write Control Byte Only

A -> acknowledge

#### Write Control Bytes

|                       | MSB |     |           |     |     |    |    |      |  |

|-----------------------|-----|-----|-----------|-----|-----|----|----|------|--|

| Write low byte first  | A4  | A3  | A2        | A1  | A0  | C1 | C0 | R/NW |  |

|                       |     | R   | 0         | 1   | 0   |    |    |      |  |

|                       |     |     | 1         |     | I   |    |    |      |  |

| Byte order            | LB  | (R) | HB        | (R) |     |    |    |      |  |

|                       |     |     |           |     |     |    |    |      |  |

|                       | MSB |     |           |     | LSB |    |    |      |  |

| Write high byte first | A4  | A3  | A2        | A1  | A0  | C1 | C0 | R/NW |  |

|                       |     | R   | ow addres | 1   | 0   | 0  |    |      |  |

|                       |     |     | 1         |     | i i |    |    |      |  |

| Byte order            | HB  | (R) | LB        | (R) |     |    |    |      |  |

| Byte order            | HB  | (R) | LB        | (R) |     |    |    | 1    |  |

HB: high byte; LB: low byte; R: row address

#### **Read Operations**

The EEPROM allows byte-, word- and current address read operations. The read operations are initiated in the same way as write operations. Every read access is initiated by sending the start condition followed by the control byte which contains the address and the read mode. After the device receives a read command it returns an acknowledge, loads the addressed word into the read/write buffer and sends the selected data byte to the master. The master has to acknowledge the received byte if it wants to proceed the read operation. If two bytes are read out from the buffer the device increments respectively decrements the word address automatically and loads the buffer with the next word. The read mode bits determines if the low or high byte is read first from the buffer and if the word address is incremented or decremented for the next read access. If the memory address limit is reached, the data word address will "roll over" and the sequential read will continue. The master can terminate the read operation after every byte by not responding with an acknowledge (N) and by issuing a stop condition.

#### **Read One Data Byte**

Start Control byte A Data byte 1 N Stop

#### **Read Two Data Bytes**

#### **Read n Data Bytes**

| Start | Control byte | А | Data byte 1 | А | Data byte 2 |  |  | Data byte n | Ν | Stop |

|-------|--------------|---|-------------|---|-------------|--|--|-------------|---|------|

|       |              |   |             |   |             |  |  |             |   |      |

A -> acknowledge, N -> no acknowledge

#### **Read Control Bytes**

|                          |          | MSB             | 3      |             |        |    |    |     |       | LSB     |

|--------------------------|----------|-----------------|--------|-------------|--------|----|----|-----|-------|---------|

| Read low byte first,     |          | A4              | A3     | A2          | A1     | A0 | C1 | 1   | C0    | R/NW    |

| address increment        |          |                 | F      | Row address |        |    |    | 0 1 |       | 1       |

|                          |          |                 |        |             |        |    |    |     |       |         |

| Byte order               | LB(R)    | )               | HB(R)  | LB(R+1)     | HB(R+  | 1) | -  | LB( | (R+n) | HB(R+n) |

|                          |          |                 |        |             |        |    |    |     |       |         |

|                          |          |                 |        |             |        |    |    |     |       |         |

|                          | _        | MSB             | 5      |             |        |    |    |     |       | LSB     |

| Read high byte first     |          | A4              | A3     | A2          | A1     | A0 | C1 | 1   | C0    | R/NW    |

| address decrement        |          | Row address 1 0 |        |             |        |    |    | 1   |       |         |

|                          | r        |                 |        |             |        |    |    |     |       |         |

| Byte order               | HB(R     | )               | LB(R)  | HB(R-1)     | LB(R-1 | )  | -  | HB  | (R-n) | LB(R-n) |

| HB: high byte; LB: low b | oyte; R: | row ac          | ddress |             |        |    |    |     |       |         |

Initilization after a Reset

The EEPROM with the serial interface has ist own reset circuitry. In systems with microcontrollers that have their own reset circuitry for power-on reset, watchdog reset or

Condition

brown-out reset, it may be necessary to bring the U3280M into a known state independent on the internal reset. This is performed by reading one byte without acknowledging and then generating a stop condition.

#### **Special Modes**

| Control Byte | Description                                                                                 |

|--------------|---------------------------------------------------------------------------------------------|

| 1100x111b    | Biphase modulation                                                                          |

| 1101x111b    | Manchester modulation                                                                       |

| 11xx0111b    | Switch power managment off -> disables switching from battery to field supply               |

| 11xx1111b    | Switch power managment on -> enables automatical switching between battery and field supply |

| xxxxx110b    | Reserved                                                                                    |

#### Data Transfer Sequence for Biphase and Manchester Modulation:

| Start | Control byte | Ackn | Bit 1 | Bit 2 | Bit 3 |  | Bit n | Stop |

|-------|--------------|------|-------|-------|-------|--|-------|------|

|-------|--------------|------|-------|-------|-------|--|-------|------|

With special control bytes the serial interface can be used to control the modulator stage or the power management. The EEPROM access and the serial interface are disabled in these modes until to the next stop condition. If no start or stop condition is generated the SCL and SDA line can be used for the modulator stage. SCL is used for the modulator clock and SDA is used for the data. In that mode the same conditions for clock and data changing like in the normal are valid. The SCL and SDA line can be used for continuous bit transfers, an acknowledge cycle after 8 bits must not be generated.

- Note: After a reset of the microcontroller it is not sure that the transponder interface has been reset too. It could still be in a receive or transmit cycle. To place the serial interface of the device into a known state the microcontroller should read one byte from the device without acknowledge and then generate a stop condition.

- **Power-On Reset, NRST** The U3280M transponder front end starts working with the applied field. For the digital circuits like EEPROM serial interface and registers there is a reset circuitry. A reset is generated by a power-on condition at VDD, by switching back from field to battery supply and if a low signal is applied at the NRST-pin.

The NRST-pin is a bidirectional pin and can also be used as reset output to generate a reset for the microcontroller if the circuit switches over from field to battery supply. This sets the microcontroller in a well defined state after the uncertain power supply condition during switching.

AntennaFor the transponder interface a coil must be used as antenna. Air and ferrite cored coils<br/>can be used. For battery-less operation the working distance resp. the minimum cou-<br/>pling factor of an application depends on the power consumption and on the size of the<br/>antennas of the IC and the base station. With a power consumption of 150 μA a mini-<br/>mum magnetic coupling factor below 0.5% is within reach. For applications with a higher<br/>power consumption the coupling factor must be increased.

The Q-factor of the antenna coil should be in the range between 30 to 80 for read only application and below 40 for bidirectional read-write applications.

U3280M

The antenna coil must be connected together with a capacitor as a parallel LC resonant circuit to the Coil 1 and Coil 2 pins of the IC. The resonance frequency f0 of the antenna circuit should be in the range of 100 to 150 kHz.

The right LC combination can be calculated with the following formula:

**Example**: Antenna frequency:  $f_0 = 125$  kHz, capacitor:  $C_A = 2.2$  nF

$$L_A = \frac{1}{2.2 \text{ nF} \times (2 \times \pi \times 125 \text{ kHz})^2} = 737 \text{ }\mu\text{H}$$

# **Absolute Maximum Ratings**

Voltages are given relative to  $\mathsf{V}_{SS}$  .

| Parameter                                                               | Symbol                              | Value                                      | Unit |

|-------------------------------------------------------------------------|-------------------------------------|--------------------------------------------|------|

| Supply voltage                                                          | V <sub>DD</sub> , V <sub>Batt</sub> | 0 V to +7.0 V with reverse protection      | V    |

| Max. current out of V <sub>SS</sub> pin                                 | I <sub>SS</sub>                     | 15                                         | mA   |

| Max. current into V <sub>Batt</sub> pin                                 | IBatt                               | 15                                         | mA   |

| Input voltage (on any pin)                                              | V <sub>IN</sub>                     | $V_{SS} - 0.6 \le V_{IN} \le V_{DD} + 0.6$ | V    |

| Input/output clamp current (V <sub>SS</sub> > Vi/Vo > V <sub>DD</sub> ) | I <sub>IK</sub> / I <sub>OK</sub>   | +/- 15                                     | mA   |

| Min. ESD protection (100pF through $1.5k\Omega$ )                       |                                     | +/-2                                       | kV   |

| Operating-temperature range                                             | T <sub>AMB</sub>                    | - 40 to + 85                               | °C   |

| Storage-emperature range                                                | T <sub>STG</sub>                    | - 40 to + 125                              | °C   |

| Soldering temperature (t $\leq$ 10 sec)                                 | T <sub>SD</sub>                     | 260                                        | °C   |

Stresses greater than those listed under absolute maximum ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at any condition above those indicated in the operational section of these specification is not implied. Exposure to absolute maximum rating condition for an extended period may affect device reliability. All inputs and outputs are protected against high electrostatic voltages or electric fields. However, precautions to minimize built-up of electrostatic charges during handling are recommended. Reliability of operation is enhanced if unused inputs are connected to an appropriate logic voltage level (e.g. V<sub>DD</sub>).

## **Thermal Resistance**

| Parameter        | Symbol            | Value | Unit |

|------------------|-------------------|-------|------|

| Junction ambient | R <sub>thJA</sub> | 180   | K/W  |

# **DC Characteristics**

Supply voltage  $V_{DD}$  = 1.8 to 6.5 V,  $V_{SS}$  = 0 V,  $T_{amb}$  = -40°C to 85°C unless otherwise specified

| Parameters                                     | Test Conditions                                                                  | Pin | Symbol                               | Min.                | Тур.                                   | Max.                | Unit     |

|------------------------------------------------|----------------------------------------------------------------------------------|-----|--------------------------------------|---------------------|----------------------------------------|---------------------|----------|

| Power supply                                   |                                                                                  |     |                                      | ·                   |                                        |                     |          |

| Operating voltage at VBatt                     |                                                                                  |     | V <sub>Batt</sub>                    | 2.0                 |                                        | 6.5                 | V        |

| Operating voltage at VDD during battery supply |                                                                                  |     | V <sub>DDB</sub>                     |                     | V <sub>Batt</sub> -<br>V <sub>SD</sub> |                     | V        |

| VDD-limiter voltage during coil supply         |                                                                                  |     | V <sub>DDC</sub>                     | 2.6                 | 2.9                                    | 3.2                 | V        |

| Operating current during field supply          | V <sub>DD</sub> > 2.0 V                                                          |     | l <sub>Fi</sub>                      |                     | 40                                     | 80                  | μA       |

| Sleep current                                  |                                                                                  |     | I <sub>SI</sub>                      |                     |                                        | 0.4                 | μA       |

| EEPROM                                         |                                                                                  |     | 1                                    |                     | 1                                      | 1                   |          |

| Operating current during erase/write cycle     | V <sub>DD</sub> = 2.0 V<br>V <sub>DD</sub> = 6.5 V                               |     | I <sub>WR</sub><br>I <sub>WR</sub>   |                     | 400                                    | 500<br>1200         | μΑ<br>μΑ |

| Operating current during read cycle            | $V_{DD} = 2.0 V$<br>$V_{DD} = 6.5 V$<br>Peak current during 1/4 of read<br>cycle |     | I <sub>Rdp</sub><br>I <sub>Rdp</sub> |                     |                                        | 300<br>350          | μΑ<br>μΑ |

| Power management                               |                                                                                  |     |                                      |                     |                                        |                     |          |

| Field-on detection voltage                     | V <sub>DD</sub> > 1.8 V                                                          |     | VFDon                                | 2.3                 | 2.5                                    | 2.9                 | V        |

| Field-off detection voltage                    | V <sub>DD</sub> > 1.8 V                                                          |     | VFDoff                               |                     | 0.8                                    |                     | V        |

| Voltage drop at<br>power-supply switch         | IS = 0.5 mA,<br>V <sub>Batt</sub> = 2 V                                          |     | VSD                                  |                     |                                        | 150                 | mV       |

| Coil inputs Coil 1 and Coil 2                  |                                                                                  |     |                                      |                     |                                        |                     |          |

| Coil input current                             |                                                                                  |     | ICI                                  |                     |                                        | 20                  | mA       |

| Input capacitance                              |                                                                                  |     | C <sub>IN</sub>                      | 30                  |                                        |                     | pF       |

| Coil voltage stroke during modulation          | $V_{CU} > 5V$<br>$I_{coil} = 3 \text{ to } 20 \text{ mA}$                        |     | V <sub>CMS</sub>                     | 1.8                 | 2.3                                    | 4.0                 | V        |

| Pin MOD                                        |                                                                                  |     |                                      |                     |                                        |                     |          |

| Input LOW voltage                              |                                                                                  |     | V <sub>IL</sub>                      | V <sub>IH</sub>     |                                        | $0.2 \times V_{DD}$ | V        |

| Input LOW voltage                              |                                                                                  |     | V <sub>IH</sub>                      | $0.8 \times V_{DD}$ |                                        | V <sub>DD</sub>     | V        |

| Input leakage current                          |                                                                                  |     | I <sub>lleakage</sub>                |                     | 10                                     |                     | nA       |

| Pin NGAP/ FC                                   |                                                                                  |     |                                      |                     | ·                                      |                     |          |

| Output LOW current                             | $V_{DD} = 2.0 V$ $V_{OL} = 0.2 \times V_{DD}$                                    |     | I <sub>OL</sub>                      | 0.08                | 0.2                                    | 0.3                 | mA       |

| Output HIGH current                            | $V_{DD} = 2.0 V$ $V_{OH} = 0.8 \times V_{DD}$                                    |     | I <sub>ОН</sub>                      | -0.06               | -0.15                                  | -0.25               | mA       |

# **DC** Characteristics

Supply voltage V<sub>DD</sub> = 1.8 to 6.5 V, V<sub>SS</sub> = 0 V,  $T_{amb}$  = -40°C to 85°C unless otherwise specified

| Parameters                   | Test Conditions                                                                             | Pin | Symbol                | Min.                | Тур.         | Max.                | Unit     |

|------------------------------|---------------------------------------------------------------------------------------------|-----|-----------------------|---------------------|--------------|---------------------|----------|

| Serial interface I/O pins SO | L and SDA                                                                                   | I   | 1                     |                     | L            | 1                   | I.       |

| Input LOW voltage            |                                                                                             |     | V <sub>IL</sub>       | VIH                 |              | $0.3 \times V_{DD}$ | V        |

| Input HIGH voltage           |                                                                                             |     | V <sub>IH</sub>       | $0.7 \times V_{DD}$ |              | V <sub>DD</sub>     | V        |

| Input leakage current        |                                                                                             |     | I <sub>lleakage</sub> |                     | 10           |                     | nA       |

| Output LOW current           | $V_{DD} = 2.0 V$ $V_{OL} = 0.2 V_{DD}$ $V_{DD} = 6.0 V$                                     |     | IOL                   | 0.7<br>2.8          | 0.9<br>3.5   | 1.1<br>4.2          | mA<br>mA |

| Output HIGH current          | V <sub>DD</sub> = 2.0 V<br>V <sub>OH</sub> = 0.8 V <sub>DD</sub><br>V <sub>DD</sub> = 6.0 V |     | I <sub>ОН</sub>       | -0.5<br>-1.8        | -0.6<br>-2.2 | -0.7<br>-2.6        | mA<br>mA |

# **AC Characteristics**

Supply voltage V<sub>DD</sub> = 1.8 to 6.5 V, V<sub>SS</sub> = 0 V,  $T_{amb}$  = -40°C to 85°C unless otherwise specified

| Parameters                    | Test Conditions                            | Pin | Symbol             | Min. | Тур. | Max. | Unit |

|-------------------------------|--------------------------------------------|-----|--------------------|------|------|------|------|

| Serial interface timing       |                                            |     |                    | L    | L    |      |      |

| SCL clock frequency           |                                            |     | fSCL               | 0    |      | 100  | kHz  |

| Clock low time                |                                            |     | t <sub>LOW</sub>   | 4.7  |      |      | μs   |

| Clock high time               |                                            |     | thigh              | 4.0  |      |      | μs   |

| SDA and SCL rise time         |                                            |     | t <sub>R</sub>     |      |      | 1000 | ns   |

| SDA and SCL fall time         |                                            |     | t <sub>F</sub>     |      |      | 300  | ns   |

| Start condition setup time    |                                            |     | <sup>t</sup> SUSTA | 4.7  |      |      | μs   |

| Start condition hold time     |                                            |     | <sup>t</sup> HDSTA | 4.0  |      |      | μs   |

| Data input setup time         |                                            |     | <sup>t</sup> SUDAT | 250  |      |      | ns   |

| Data input hold time          |                                            |     | <sup>t</sup> HDDAT | 0    |      |      | ns   |

| Stop condition setup time     |                                            |     | tsusto             | 4.7  |      |      | μs   |

| Bus free time                 |                                            |     | <sup>t</sup> BUF   | 4.7  |      |      | μs   |

| Input filter time             |                                            |     | tı                 |      |      | 100  | ns   |

| Data output hold time         |                                            |     | <sup>t</sup> DH    | 300  |      | 1000 | ns   |

| Coil inputs                   |                                            |     |                    | L    | L    |      |      |

| Coil frequency                |                                            |     | fcoil              | 100  | 125  | 150  | kHz  |

| Gap detection                 |                                            |     |                    |      |      |      |      |

| Delay field off to GAP = 0    | V <sub>coilGap</sub> < 0.7 V <sub>DC</sub> |     | T <sub>FGAP0</sub> | 10   |      | 50   | μs   |

| Delay field on to GAP = 1     | V <sub>coilGap</sub> > 3 V <sub>DC</sub>   |     | T <sub>FGAP1</sub> | 1    |      | 50   | μs   |

| Power management              | · ·                                        |     |                    |      |      |      |      |

| Battery to field switch delay |                                            |     | t <sub>BFS</sub>   |      |      | 1000 | μs   |

| Field to battery switch delay | VBatt = 6.5 V                              |     | t <sub>FBS</sub>   | 5    | 10   | 30   | ms   |

# **AC Characteristics**

Supply voltage V<sub>DD</sub> = 1.8 to 6.5 V, V<sub>SS</sub> = 0 V,  $T_{amb}$  = -40°C to 85°C unless otherwise specified

| Parameters                   | Test Conditions                | Pin | Symbol            | Min.   | Тур. | Max. | Unit   |

|------------------------------|--------------------------------|-----|-------------------|--------|------|------|--------|

| EEPROM                       | ·                              |     |                   |        |      |      |        |

| Endurance                    | Erase/ write-cycles            |     | ED                | 500000 |      |      | Cycles |

| Data erase/ write cycle time | For 16 bits access             |     | <sup>t</sup> DEW  |        | 9    | 12   | ms     |

| Data retention time          | Tamb = 25_C                    |     | <sup>t</sup> DR   | 10     |      |      | years  |

| Power up to read operation   |                                |     | t <sub>PUR</sub>  |        |      | 0.2  | ms     |

| Power up to write operation  |                                |     | t <sub>PUw</sub>  |        |      | 0.2  | ms     |

| Reset                        |                                |     |                   |        |      |      |        |

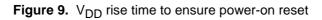

| Power-on reset               | V <sub>DDrise</sub> = 0 to 2 V |     | t <sub>rise</sub> |        |      | 10   | ms     |

| NRST                         | VII < 0.2 V <sub>DD</sub>      |     | t <sub>res</sub>  | 1      |      |      | μs     |

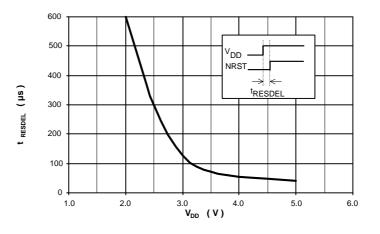

Figure 7. Typical reset delay after switching  $V_{DD}$  on

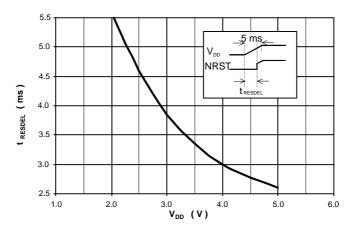

Figure 8. Typical reset delay after switching  $V_{DD}$  on

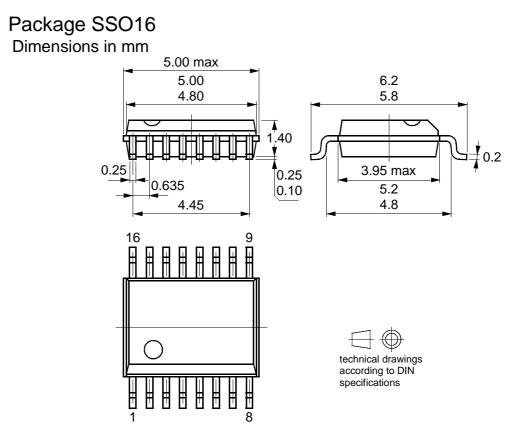

# **Package Information**

# **Ozone Depleting Substances Policy Statement**

It is the policy of Atmel Germany GmbH to

- 1. Meet all present and future national and international statutory requirements.

- 2. Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

Atmel Germany GmbH has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

Atmel Germany GmbH can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

### **Atmel Sales Offices**

#### France

3, Avenue du Centre 78054 St.-Quentin-en-Yvelines Cedex Tel: +33 1 30 60 70 00 Fax: +33 1 30 60 71 11

#### Germany

Erfurter Strasse 31 85386 Eching Tel: +49 89 319 70 0 Fax: +49 89 319 46 21

Kruppstrasse 6 45128 Essen Tel: +49 201 247 30 0 Fax: +49 201 247 30 47

Theresienstrasse 2 74072 Heilbronn Tel: +49 7131 67 36 36 Fax: +49 7131 67 31 63

#### Italy

Via Grosio, 10/8 20151 Milano Tel: +39 02 38 03 71 Fax: +39 02 38 03 72 34

#### Spain

Principe de Vergara, 112 28002 Madrid Tel: +34 91 564 51 81 Fax: +34 91 562 75 14

#### Sweden

Kavallerivaegen 24, Rissne 17402 Sundbyberg Tel: +46 8 587 48 800 Fax: +46 8 587 48 850

#### **United Kingdom**

Easthampstead Road Bracknell Berkshire RG12 1LX Tel: +44 1344 707 300 Fax: +44 1344 427 371

#### USA Western

2325 Orchard Parkway San Jose, California 95131 Tel: +1 408 441 0311 Fax: +1 408 436 4200

#### USA Eastern

1465 Route 31, Fifth floor Annandale New Jersey 08801 Tel: +1 908 848 5208 Fax: +1 908 848 5232

#### Hong Kong

Room #1219, Chinachem Golden Plaza 77 Mody Road, Tsimhatsui East East Kowloon, Hong Kong Tel: +852 23 789 789 Fax: +852 23 755 733

#### Korea

25-4, Yoido-Dong, Suite 605, Singsong Bldg. Youngdeungpo-Ku 150-010 Seoul Tel: +822 785 1136 Fax: +822 785 1137

#### **Rep. of Singapore**

Keppel Building #03-00 25 Tampines Street 92, Singapore 528877 Tel: +65 260 8223 Fax: +65 787 9819

#### Taiwan, R.O.C.

8F-2, 266 Sec.1 Wen Hwa 2 Rd. Lin Kou Hsiang, 244 Taipei Hsien Tel: +886 2 2609 5581 Fax: +886 2 2600 2735

#### Japan

Tonetsushinkawa Bldg. 1-24-8 Shinkawa Chuo Ku Tokyo 104-0033 Tel: +81 3 3523 3551 Fax: +81 3 3523 7581

Web Site

http://www.atmel-wm.com

#### © Atmel Germany GmbH 2001.

Atmel Germany GmbH makes no warranty for the use of its products, other than those expressly contained in the Company's standard warranty which is detailed in Atmel Germany GmbH's Terms and Conditions. The Company assumes no responsibility for any errors which may appear in this document, reserves the right to change devices or specifications detailed herein at any time without notice, and does not make any commitment to update the information contained herein. No licenses to patents or other intellectual property of Atmel Germany GmbH are granted by the Company in connection with the sale of Atmel Germany GmbH products, expressly or by implication. Atmel Germany GmbH's products are not authorized for use as critical components in life support devices or systems.

Data sheets can also be retrieved from the Internet: http://www.atmel-wm.com