S/UNI-622-POS REFERENCE DESIGN ERRATA

PM5357

**S/UNI-622-POS**

# SATURN USER NETWORK INTERFACE (622-POS)

# REFERENCE DESIGN ERRATA

**PRELIMINARY**

**ISSUE 2: APRIL 1999**

S/UNI-622-POS REFERENCE DESIGN ERRATA

# **PUBLIC REVISION HISTORY**

| Issue<br>No. | Issue<br>Date | Details of Change                 |  |

|--------------|---------------|-----------------------------------|--|

| 1            | March<br>1999 | Document created.                 |  |

| 2            | April<br>1999 | Correct Optics module part number |  |

S/UNI-622-POS REFERENCE DESIGN ERRATA

# **CONTENTS**

| 1 | ISSU              | SSUE 2 ERRATA1                             |   |  |

|---|-------------------|--------------------------------------------|---|--|

| 2 | S/UNI             | -622-POS REFERENCE DESIGN SCHEMATIC ERRORS | 2 |  |

|   | 2.1               | MISSED ANALOG POWER FILTERING              | 2 |  |

|   | 2.2               | INCORRECT PULLUP/PULLDOWN RESISTORS        | 2 |  |

|   | 2.3               | INCORRECT LIFSEL AND SYSSEL CONNECTION     | 2 |  |

|   | 2.4               | INCORRECTLY REFERENCED OPTICS MODULE       | 3 |  |

| 3 | ADDI <sup>*</sup> | TIONAL DESIGN NOTES                        | 4 |  |

|   | 3.1               | PECL INTERFACING ISSUES                    | 4 |  |

|   | 3.2               | JTAG PORT                                  | 4 |  |

PM5357 S/UNI-622-POS

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN ERRATA

| LIST OF FIGURES | L | IST | OF | FIG | <b>UR</b> | ES |

|-----------------|---|-----|----|-----|-----------|----|

|-----------------|---|-----|----|-----|-----------|----|

| FIGI  | JRE 1            | FILTERING FOR AVD<19>     |  |

|-------|------------------|---------------------------|--|

| 1 101 | $JI \setminus L$ | 1 IELEINING I ON AVDS 132 |  |

S/UNI-622-POS REFERENCE DESIGN ERRATA

## 1 ISSUE 2 ERRATA

This issue 2 document errata contains errata applied to document PMC-981070 S/UNI-622-POS Reference Design Issue 1.

PMC-990329

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN ERRATA

#### 2 S/UNI-622-POS REFERENCE DESIGN SCHEMATIC ERRORS

This section describes errors and required corrections on the schematics provided with the S/UNI-622-POS Reference Design.

### 2.1 Missed Analog Power Filtering

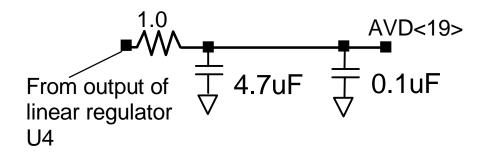

On Page 3 of the S/UNI-622-POS Reference Design schematics, Pin 19 of AVD<31..0> is tied directly to the output of the linear voltage regulator (U4). This pin should be filtered with the circuit shown below. Without this filtering, jitter performance of the device will be degraded.

Figure 1 - Filtering for AVD<19>

#### 2.2 Incorrect Pullup/Pulldown Resistors

On Page 2 of the S/UNI-622-POS Reference Design schematics, pins RRCLK+ and RRCLK- (or RRCLKP and RRCLKN respectively) are both pulled down to ground using 4.7 KOhm resistors. RRCLK+ should be tied to the opposite polarity as pin RRCLK-, e.g. since RRCLK- is tied to ground, RRCLK+ should be tied to 3.3V. When tying an input to ground, the pin may be connected directly to ground. When tying an input to 3.3V or 5V, a 4.7 KOhm resistor should be used in order to prevent latchup during power up. Failure to tie RRCLK+ and RRCLKto complementary values will result in signal contention within the device witch may cause problems with device operation.

#### 2.3 Incorrect LIFSEL and SYSSEL Connection

On Page 2 at A9, the offpage signal named SYSSEL\I is tied to pin LIFSEL on the S/UNI-622-POS. The signal should be tied to pin SYSSEL on the S/UNI-622-POS instead of LIFSEL. LIFSEL should be tied low to enable serial line interface mode on the S/UNI-622-POS.

S/UNI-622-POS REFERENCE DESIGN ERRATA

#### **Incorrectly Referenced Optics Module** 2.4

The optics modules HFBR-5208 and HFCT-5208 should be correctly referenced as HFBR-5208M and HFCT-5208M.

S/UNI-622-POS REFERENCE DESIGN ERRATA

#### 3 ADDITIONAL DESIGN NOTES

This section provides additional recommendations on designing with the S/UNI-622-POS device.

### 3.1 PECL Interfacing Issues

All unused differential PECL inputs should be tied such that the positive input and negative input are complementary (have opposite logic values). For example; RRCLK+ is tied to 3.3V, therefore RRCLK- should be tied to ground. Or; RRCLK+ is tied to ground and RRCLK- should be tied to 3.3V.

The PECLV and PBIAS pins affect both the optical PECL interface as well as the REFCLK+/- interface. Therefore REFCLK+/- must have the same signal reference level as the optical PECL interface.

Traces between the optics and the S/UNI-622-POS should be limited to a maximum of **4 cm** long. No vias should be present on the traces except where required for termination components. Any vias present on the traces will degrade jitter performance. Traces should be equal length with as few bends as possible.

Page 11 of the S/UNI-622-POS Reference design describes the optional use of optics with integrated clock and data recovery (HFBR/HFCT-5207). It should also be noted that, for HFBR/HFCT-5207 devices, the SD signal should be terminated using a 10 KOhm resistor to ground rather than the 330 Ohm specified in Figure 4 of the S/UNI-622-POS Reference design.

#### 3.2 JTAG Port

When unused, the JTAG port of the S/UNI-622-POS should have TRSTB tied to RSTB. This will reset the JTAG port on reset of the system. TMS, TCK and TDI should be tied high. In addition, TMS may be tied high and TCK tied to a free running clock to ensure that the JTAG port logic is continuously put back into the correct state.

PM5357 S/UNI-622-POS

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN ERRATA

# **NOTES**

PM5357 S/UNI-622-POS

S/UNI-622-POS REFERENCE DESIGN ERRATA

ISSUE 2

## **CONTACTING PMC-SIERRA, INC.**

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: <a href="mailto:document@pmc-sierra.com">document@pmc-sierra.com</a>

Corporate Information: <a href="mailto:info@pmc-sierra.com">info@pmc-sierra.com</a>

Application Information: <a href="mailto:apps@pmc-sierra.com">apps@pmc-sierra.com</a>

(604) 415-4533

Web Site: <a href="http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

© 1999 PMC-Sierra, Inc.

PMC-990329 (P2) Issue date: April 1999