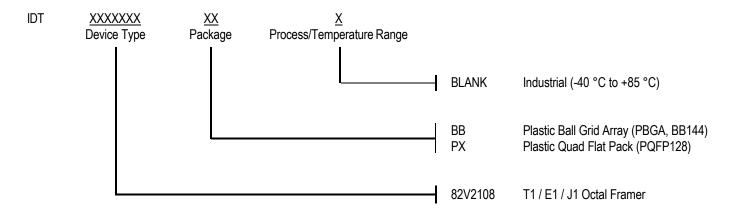

### T1 / E1 / J1 OCTAL FRAMER

IDT82V2108

**PRELIMINARY**

#### **FEATURES**

- Octal Framer supporting T1, E1 and J1 Formats

- Provides programmable system interface to support Mitel® ST-bus, AT&T® CHI and MVIP bus, supporting data rates of 1.544 / 2.048 / 8.192Mb/s; up to four links can be byte interleaved on one system bus without external logic

- Provides up to three internal floating HDLC controllers for each framer to support ISDN PRI and V5.X interface. Each HDLC contains 128-byte deep FIFOs in both the receive and transmit directions

- Provides jitter attenuation performance exceeding the requirements set by the associated standards for both Rx and Tx path

- Provides payload, line and digital loop-backs

- Provides a floating Pseudo Random Bit Sequence / repetitive pattern generator/detector, which can be assigned to any one of eight framers, the pattern may be inserted / detected in an unframed or Nx64K or Nx56K (T1 only) basis

- Provides signaling insertion / extraction for CCS / CAS and RBS signaling system

- Provides programmable codes insertion, data / sign inversion and digital milliwatt code insertion on a per channel / timeslot basis

- Supports automatic / manual alarming transmit and integration

- Provides performance monitor to counter CRC error, framing bit error, far end block CRC error (E1), out of frame event (T1/J1) and change of frame alignment event (T1/J1)

- Provides programmable In-band Loop-back Code transmitter/receiver, Bit Oriented Message generator / detector

- Supports polled or interrupt driven processing for all events

- Supports multiplexed or non-multiplexed address/data bus MPU interface for configuration, control and status monitoring

- JTAG boundary scan meets IEEE 1149.1

- Low power 3.3V CMOS technology with 5V tolerant inputs

- Operating industrial temperature range: -40°C to +85°C

- Package available: 128 pin PQFP 144 pin PBGA

#### **APPLICATIONS**

- High density internet E1 or T1 / J1 interface for routers, multiplexers, switches and digital modems.

- Frame relay switches and access devices (FRADS)

- SONET / SDH add drop multiplexers

- Digital private branch exchanges (PBX)

- Channel service units (CSU) and data service units (DSU)

- Channel banks and multiplexers

- Digital access and cross-connect systems (DACS)

### **STANDARDS**

#### E1 MODE:

ITU-T: G.704, G.706, G.732, G.802, G.737, G.738, G.739, G.742, G.823, G.964, G.965, I.431, O.151, O.152, O.153;

ETSI: ETS 300 011, ETS 300 233, ETS 324-1, ETS 347-1, TBR 4, TBR 12, TBR 13;

GO - MVIP

#### T1/J1 MODE:

ANSI: T1.107, T1.231, T1.403, T1.408;

TR: TSY-000147, TSY-000191, NWT-000303, TSY-000312, TSY-000-

499:

AT&T: TR 54016, TR 62411

TTC: JT-G 703, JT-G 704, JT-G706, JT-G 1431

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

**JANUARY 2003**

#### **DESCRIPTION**

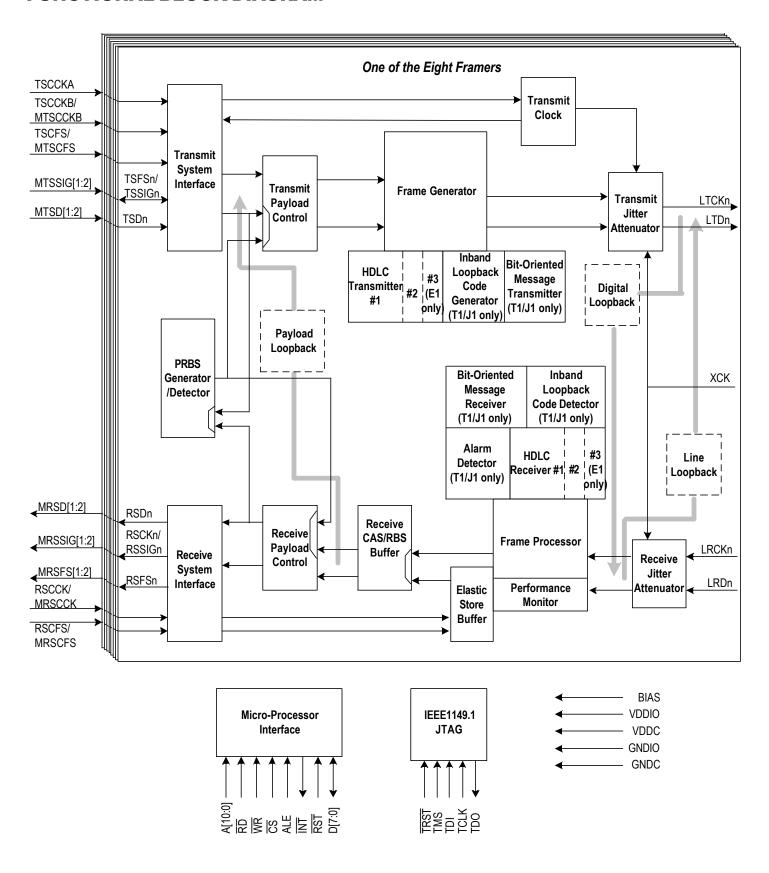

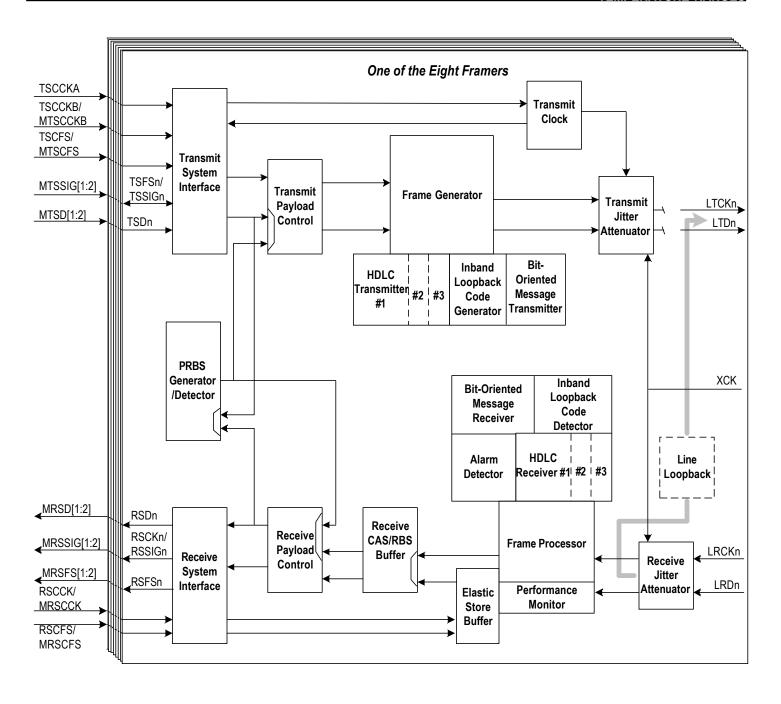

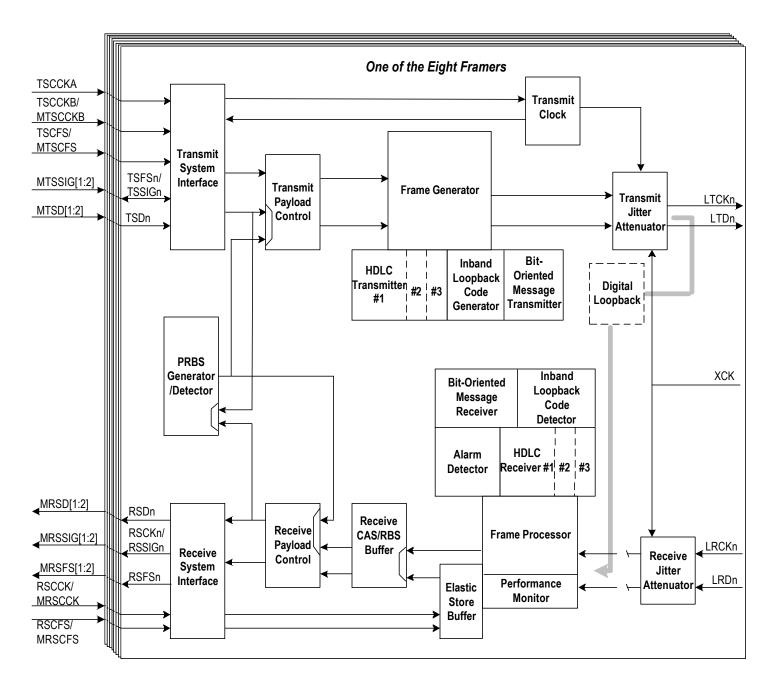

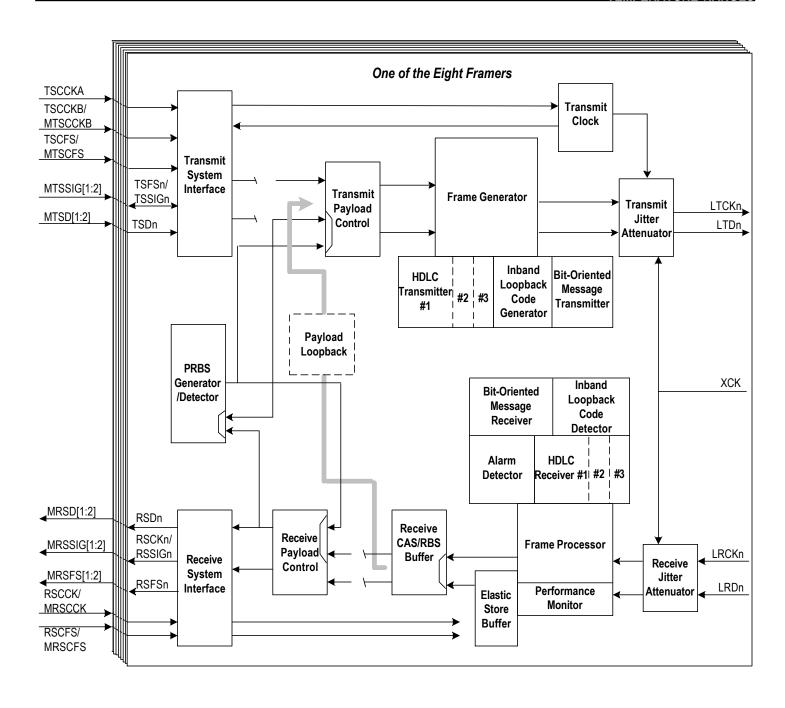

The IDT82V2108 is a flexible feature-rich octal T1/E1/J1 Framer. Controlled by the software, the IDT82V2108 can be globally configured as an Octal E1 or T1/J1 Framer. When E1 or T1/J1 has been set globally, the operation mode of each of the eight framers can be configured independently. The configuration is performed through a parallel Multiplexed/Non-Multiplexed microprocessor interface.

The IDT82V2108 realizes frame synchronization, frame generating, signaling extraction and insertion, alarm and test signals generation and detection in a single chip. It also integrates up to three HDLC receivers and HDLC transmitters for each of the eight framers.

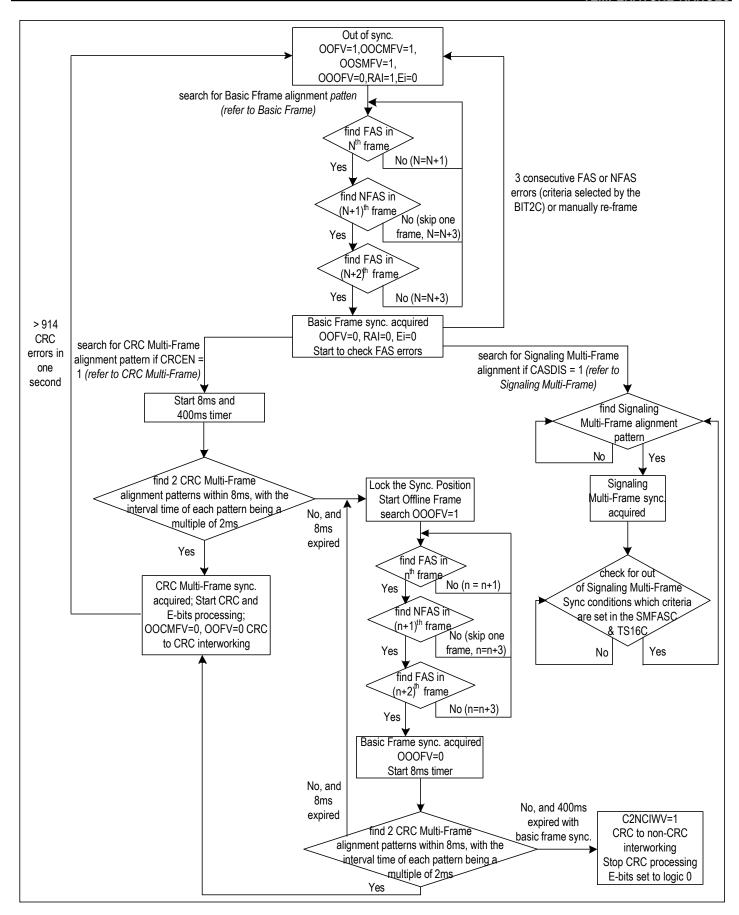

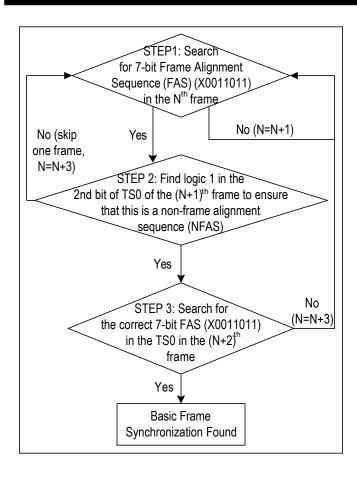

In E1 Mode, the receive path of each framer can be configured to frame to Basic Frame, CRC Multi-Frame and Signaling Multi-Frame. The framing can also be bypassed (unframed mode). It detects and indicates the event of out of Basic Frame Sync, out of CRC Multi-Frame, out of Signaling Multi-Frame, the Remote Alarm Indication signal and the Remote Signaling Multi-Frame Alarm Indication signal. It also monitors the Red and AIS alarms. Basic Frame Alignment Signal errors, Far End Block Errors (FEBE) and CRC errors are counted. Up to three HDLC links are provided to extract the HDLC message on TS16, the Sa National bits and/or any arbitrary timeslot. An Elastic Store Buffer that optionally supports slip buffering and adaptation to backplane timing is provided. In E1 receive path, signaling debounce, signaling freezing, idle code substitution, digital milliwatt code insertion, trunk conditioning, data inversion and pattern generation or detection are also supported on a per-timeslot basis.

In E1 mode, the transmit path of each framer can be configured to generate Basic Frame, CRC Multi-Frame and Signaling Multi-Frame. The framing can also be disabled (unframed mode). It can also transmit Remote Alarm Indication signal, the Remote Signaling Multi-Frame Alarm Indication signal, AIS signal and FEBE. Up to three HDLC links are provided to insert the HDLC message on TS16, the Sa National bits and/or any arbitrary timeslot. The signaling insertion, idle code substitution, data insertion, data inversion and test pattern generation or detection are also supported on a per-timeslot basis.

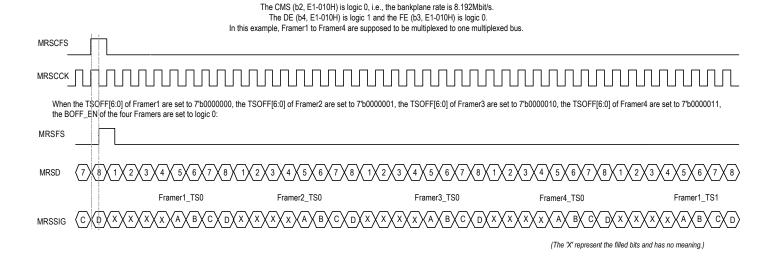

In E1 mode, any four of the eight framers can be multiplexed or demultiplexed to or from one of the two 8.192M bit/s buses.

In T1/J1 mode, the receive path of each framer can be configured to frame to Super Frame (SF) or Extended Super Frame (ESF) formats. The framing can also be bypassed (unframed mode). It detects and indicates the out of SF/ESF sync event, the Yellow, Red and AIS alarms. It also detects the presence of inband loopback codes, bit oriented message. Frame Alignment Signal errors, CRC-6 errors, out of SF/ESF events and Frame Alignment position changes are counted. Up to two HDLC links are provides to extract the HDLC message on the F-bit or any arbitrary channels in ESF mode. An Elastic Store Buffer that optionally supports controlled slip and adaptation to backplane timing is provided. In T1/J1 receive path, signaling debounce, signaling freezing, idle code substitution, digital milliwatt code insertion, idle code insertion, data inversion and pattern generation or detection are also supported on a per-channel basis.

In T1/J1 mode, the transmit path of each framer can be configured to generates SF or ESF. The framing can also be disabled (unframed mode). It can also transmit Yellow signal and AIS signal. Inband loopback codes and bit oriented message can also be transmitted. Up to two HDLC links are provided to insert the HDLC message on the F-

bit or any arbitrary channels in ESF mode. The signaling insertion, idle code substitution, data insertion, data inversion and test pattern generation or detection are also supported on a per-channel basis.

In T1/J1 mode, the data stream of 1.544M bit/s can be converted to/ from the data stream of 2.048M bit/s on the system side by software configuration. In addition, any four of the eight framers can be multiplexed or de-multiplexed to or from one of the two 8.192M bit/s buses.

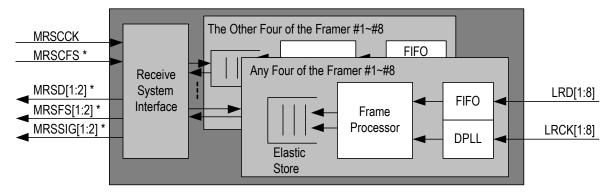

### **FUNCTIONAL BLOCK DIAGRAM**

## **CONTENTS**

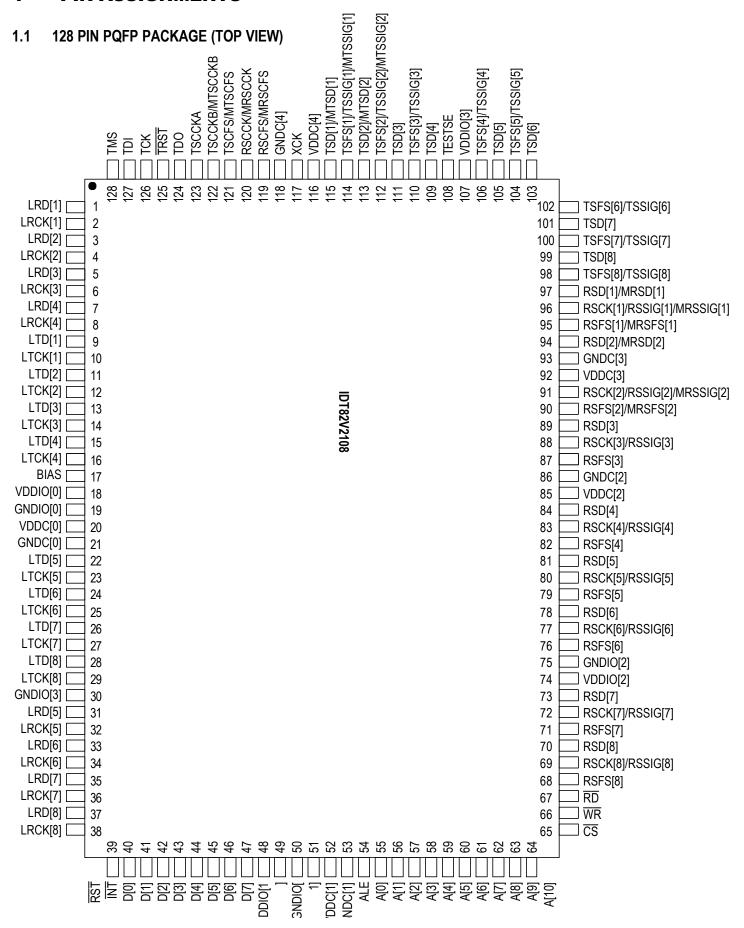

| 1 | PIN ASSIGNMENTS                                                 | . 13 |

|---|-----------------------------------------------------------------|------|

|   | 1.1 128 PIN PQFP PACKAGE (TOP VIEW)                             | 13   |

|   | 1.2 144 PIN PBGA PACKAGE (BOTTOM VIEW)                          | . 14 |

| 2 | PIN DESCRIPTION                                                 | . 15 |

| 3 | FUNCTIONAL DESCRIPTION                                          | . 21 |

|   | 3.1 T1/E1/J1 MODE SELECTION                                     |      |

|   | 3.2 FRAME PROCESSOR (FRMP)                                      |      |

|   | 3.2.1 E1 Mode                                                   |      |

|   | 3.2.2 T1/J1 Mode                                                | 26   |

|   | 3.3 PERFORMANCE MONITOR (PMON)                                  | . 28 |

|   | 3.3.1 E1 Mode                                                   | . 28 |

|   | 3.3.2 T1/J1 Mode                                                | . 28 |

|   | 3.4 ALARM DETECTOR (ALMD) - T1 / J1 ONLY                        | . 28 |

|   | 3.5 HDLC RECEIVER (RHDLC)                                       | . 29 |

|   | 3.5.1 E1 Mode                                                   | . 29 |

|   | 3.5.2 T1 / J1 Mode                                              | . 30 |

|   | 3.6 BIT-ORIENTED MESSAGE RECEIVER (RBOM) - T1 / J1 ONLY         | . 30 |

|   | 3.7 INBAND LOOPBACK CODE DETECTOR (IBCD) - T1 / J1 ONLY         | 31   |

|   | 3.8 ELASTIC STORE BUFFER (ELSB)                                 | . 31 |

|   | 3.8.1 E1 Mode                                                   | 31   |

|   | 3.8.2 T1 / J1 Mode                                              | 31   |

|   | 3.9 RECEIVE CAS/RBS BUFFER (RCRB)                               |      |

|   | 3.9.1 E1 Mode                                                   |      |

|   | 3.9.2 T1 / J1 Mode                                              |      |

|   | 3.10 RECEIVE PAYLOAD CONTROL (RPLC)                             |      |

|   | 3.10.1 E1 Mode                                                  |      |

|   | 3.10.2 T1 / J1 Mode                                             | . 34 |

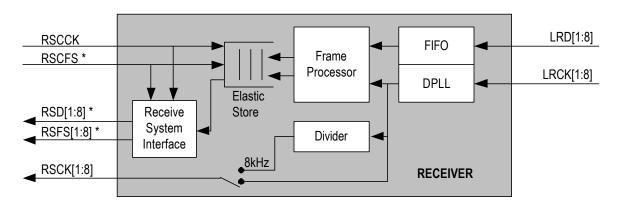

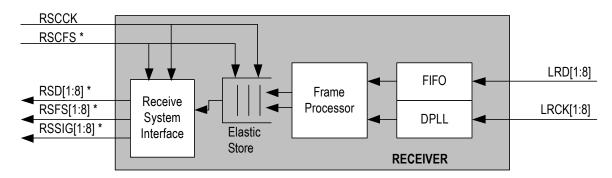

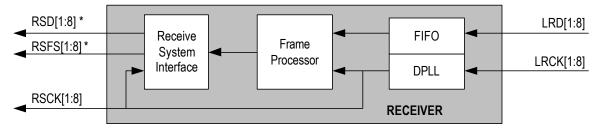

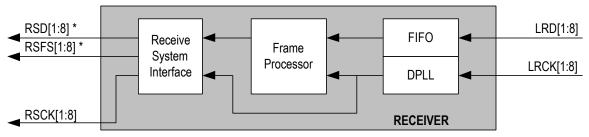

|   | 3.11 RECEIVE SYSTEM INTERFACE (RESI)                            | . 35 |

|   | 3.11.1 E1 Mode                                                  |      |

|   | 3.11.1.1 Receive Clock Slave Mode                               |      |

|   | 3.11.1.1.1 Receive Clock Slave RSCK Reference Mode              |      |

|   | 3.11.1.2 Receive Clock Master Mode                              |      |

|   | 3.11.1.2.1 Receive Clock Master Full E1 Mode                    |      |

|   | 3.11.1.2.2 Receive Clock Master Fractional E1 (with F-bit) Mode |      |

|   | 3.11.1.3 Receive Multiplexed Mode                               |      |

|   | 3.11.1.4 Parity Check & Polarity Fix                            |      |

|   | 3.11.1.5 Offset                                                 |      |

|   | 3.11.1.6 Output On RSDn/MRSD & RSSIGn/MRSSIG                    | . 44 |

| 3.11.2 T1 / J1 Mode                                         | 47 |

|-------------------------------------------------------------|----|

| 3.11.2.1 Receive Clock Slave Mode                           | 47 |

| 3.11.2.1.1 Receive Clock Slave RSCK Reference Mode          |    |

| 3.11.2.1.2 Receive Clock Slave External Signaling Mode      |    |

| 3.11.2.2 Receive Clock Master Mode                          |    |

| 3.11.2.2.1 Receive Clock Master Full 11/J1 Mode             |    |

| 3.11.2.3 Receive Multiplexed Mode                           |    |

| 3.11.2.4 Parity Check                                       | 53 |

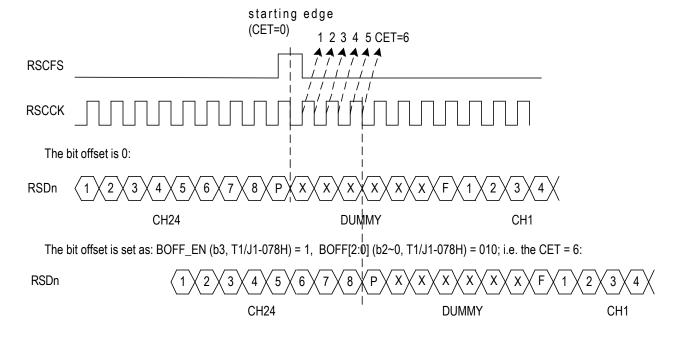

| 3.11.2.5 Offset                                             | 55 |

| 3.11.2.6 Output On RSDn/MRSD & RSSIGn/MRSSIG                | 55 |

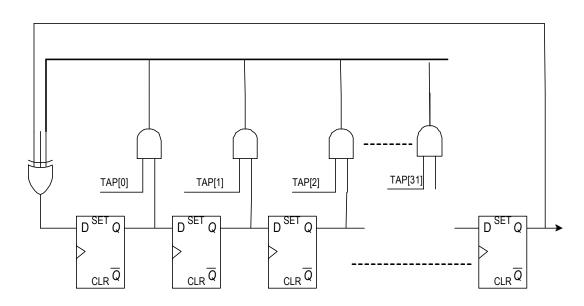

| 3.12 PRBS GENERATOR / DETECT OR (PRGD)                      | 56 |

| 3.12.1 E1 Mode                                              | 56 |

| 3.12.2 T1 / J1 Mode                                         | 57 |

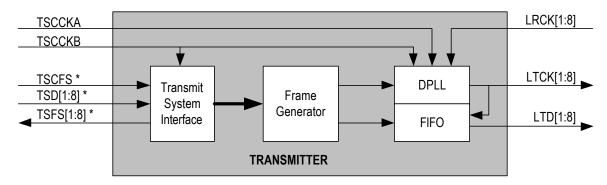

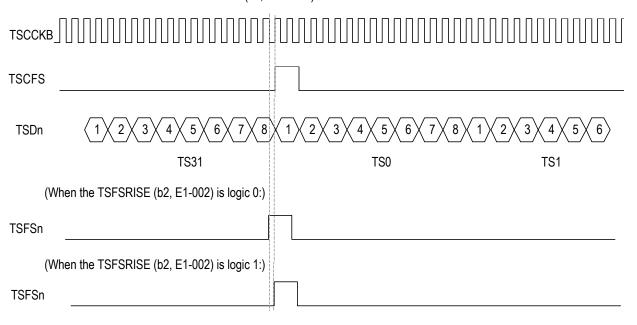

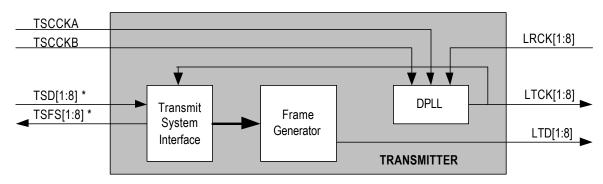

| 3.13 TRANSMIT SYSTEM INTERFACE (TRSI)                       | 57 |

| 3.13.1 E1 Mode                                              |    |

| 3.13.1.1 Transmit Clock Slave Mode                          | 58 |

| 3.13.1.1.1 Transmit Clock Slave TSFS Enable Mode            |    |

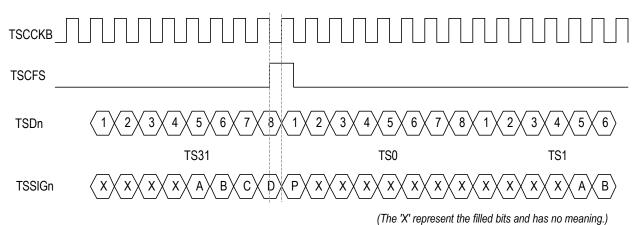

| 3.13.1.1.2 Transmit Clock Slave External Signaling Mode     |    |

| 3.13.1.2 Transmit Clock Master Mode                         |    |

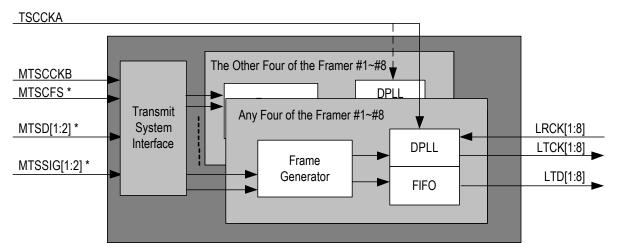

| 3.13.1.3 Transmit Multiplexed Mode                          |    |

| 3.13.1.4 Parity Check                                       |    |

| 3.13.1.5 Offset                                             |    |

| 3.13.2 T1 / J1 Mode                                         |    |

| 3.13.2.1 Transmit Clock Slave Mode                          |    |

| 3.13.2.1.1 Transmit Clock Slave TSFS Enable Mode            |    |

| 3.13.2.2 Transmit Clock Master Mode                         |    |

| 3.13.2.3 Transmit Multiplexed Mode                          | 72 |

| 3.13.2.4 Parity Check                                       | 75 |

| 3.13.2.5 Offset                                             |    |

| 3.14 TRANSMIT PAYLOAD CONTROL (TPLC)                        | 76 |

| 3.14.1 E1 Mode                                              |    |

| 3.14.2 T1 / J1 Mode                                         |    |

| 3.15 FRAME GENERATOR (FRMG)                                 | 77 |

| 3.15.1 E1 Mode                                              |    |

| 3.15.2 T1 / J1 Mode                                         | 78 |

| 3.16 HDLC TRANSMITTER (THDLC)                               |    |

| 3.16.1 E1 Mode                                              |    |

| 3.16.2 T1 / J1 Mode                                         |    |

| 3.17 BIT-ORIENTED MESSAGE TRANSMITTER (TBOM) - T1 / J1 ONLY |    |

| 3.18 INBAND LOOPBACK CODE GENERATOR (IBCG) - T1 / J1 ONLY   |    |

|   | 3.19 JITTER ATTENUATOR (RJAT/TJAT)                       | 80  |

|---|----------------------------------------------------------|-----|

|   | 3.19.1 E1 Mode                                           | 80  |

|   | 3.19.2 T1 / J1 Mode                                      | 83  |

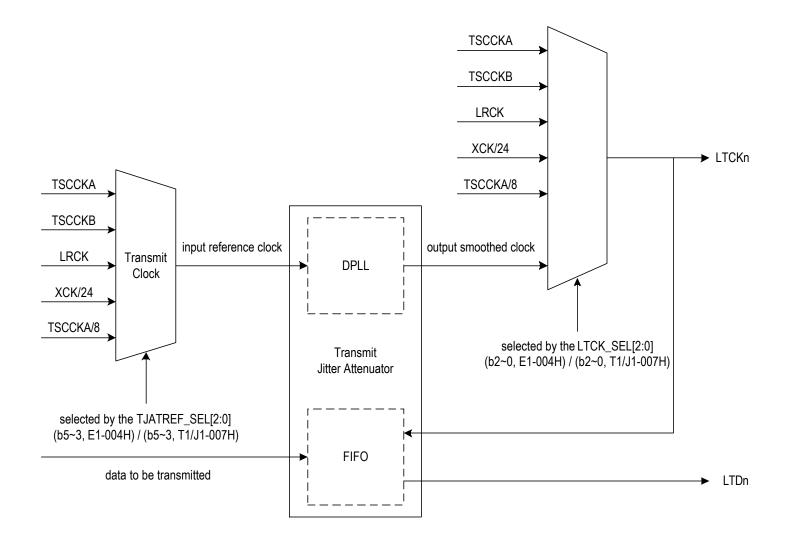

|   | 3.20 TRANSMIT CLOCK                                      | 85  |

|   | 3.20.1 E1 Mode                                           | 85  |

|   | 3.20.2 T1 / J1 Mode                                      | 85  |

|   | 3.21 LINE INTERFACE                                      | 85  |

|   | 3.21.1 E1 Mode                                           | 85  |

|   | 3.21.2 T1 / J1 Mode                                      | 85  |

|   | 3.22 INTERRUPT SUMMARY                                   | 86  |

|   | 3.22.1 E1 Mode                                           | 86  |

|   | 3.22.2 T1 / J1 Mode                                      | 86  |

|   | 3.23 LOOPBACK MODE                                       | 86  |

|   | 3.23.1 Line Loopback                                     | 86  |

|   | 3.23.2 Digital Loopback                                  | 86  |

|   | 3.23.3 Payload Loopback                                  | 86  |

|   | 3.24 CLOCK MONITOR                                       | 86  |

| 4 | OPERATION                                                | 90  |

|   | 4.1 E1 MODE                                              | 90  |

|   | 4.1.1 Default Setting                                    | 90  |

|   | 4.1.2 Various Operation Modes Configuration              | 90  |

|   | 4.1.3 Operation Example                                  | 95  |

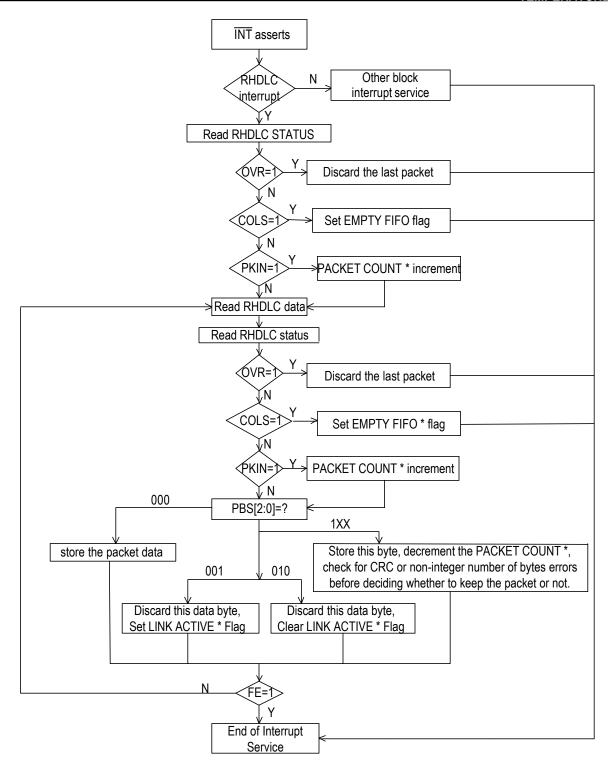

|   | 4.1.3.1 Using The HDLC Receiver                          | 95  |

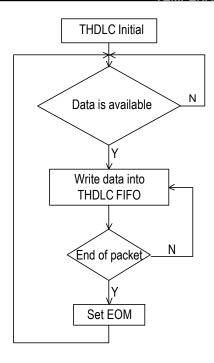

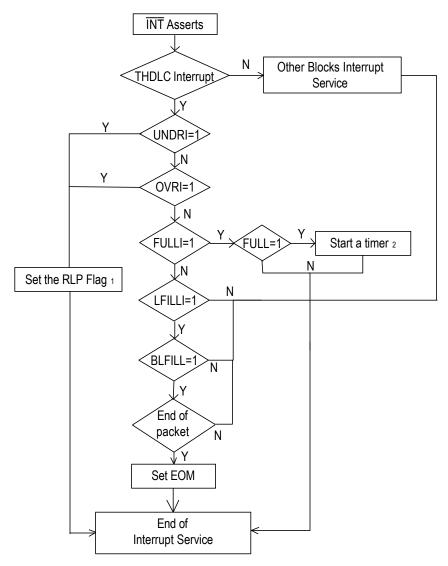

|   | 4.1.3.2 Using The HDLC Transmitter                       | 95  |

|   | 4.1.3.3 Using The PRBS Generator / Detector              | 99  |

|   | 4.1.3.4 Using Payload Control and Receive CAS/RBS Buffer | 104 |

|   | 4.1.3.5 Using TJAT / Timing Option                       | 104 |

|   | 4.2 T1/J1 MODE                                           | 105 |

|   | 4.2.1 Default Setting                                    | 105 |

|   | 4.2.2 OPERATION IN J1 MODE                               | 105 |

|   | 4.2.3 Various Operation Modes Configuration              | 105 |

|   | 4.2.4 Operation Example                                  | 110 |

|   | 4.2.4.1 Using The HDLC Receiver                          | 110 |

|   | 4.2.4.2 Using The HDLC Transmitter                       | 112 |

|   | 4.2.4.3 Using The PRBS Generator / Detector              | 114 |

|   | 4.2.4.4 Using Payload Control and Receive CAS/RBS Buffer | 118 |

|   | 4.2.4.5 Using TJAT / Timing Option                       | 118 |

| 5 | PROGRAMMING INFORMATION                                  | 119 |

|   | 5.1 REGISTER MAP                                         | 119 |

|   |                                                          |     |

|   | 5.1.1 E1 Mode Register Map                          | 120   |

|---|-----------------------------------------------------|-------|

|   | 5.1.2 T1 / J1 Mode Register Map                     | 123   |

|   | 5.2 REGISTER DESCRIPTION                            | 126   |

|   | 5.2.1 E1 Mode                                       | 126   |

|   | 5.2.2 T1 / J1 Mode                                  | 198   |

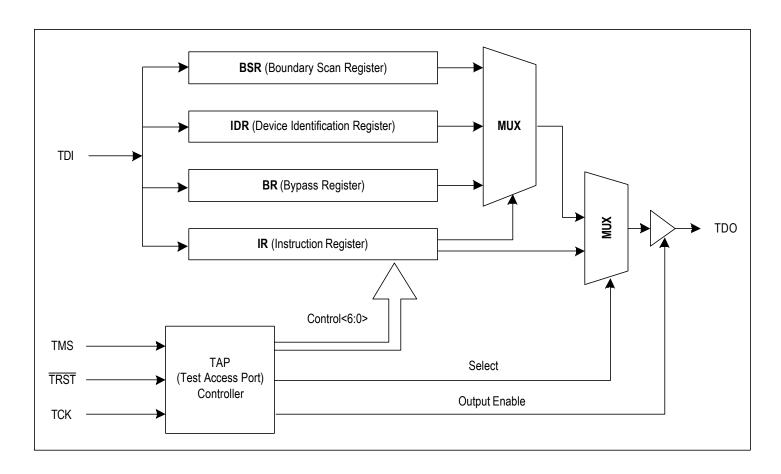

| 6 | IEEE STD 1149.1 JTAG TEST ACCESS PORT               | . 259 |

|   | 6.1 JTAG INSTRUCTIONS AND INSTRUCTION REGISTER (IR) | 261   |

|   | 6.2 JTAG DATA REGISTER                              | 261   |

|   | 6.2.1 Device Identification Register (IDR)          | 261   |

|   | 6.2.2 Bypass Register (BYR)                         | 261   |

|   | 6.2.3 Boundary Scan Register (BSR)                  | 261   |

|   | 6.3 TESTACCESS PORT CONTROLLER                      | 261   |

| 7 | PHYSICAL AND ELECTRICAL SPECIFICATIONS              | . 265 |

|   | 7.1 ABSOLUTE MAXIMUM RATINGS                        | 265   |

|   | 7.2 OPERATING CONDITIONS                            | 265   |

|   | 7.3 D.C. CHARACTERISTICS                            | 265   |

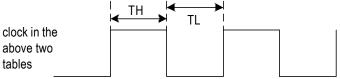

|   | 7.4 CLOCK RESET TIMING                              | 266   |

|   | 7.4.1 Clock Parameters E1 Configuration             | 266   |

|   | 7.4.2 Clock Parameters T1/J1 Configuration          | 266   |

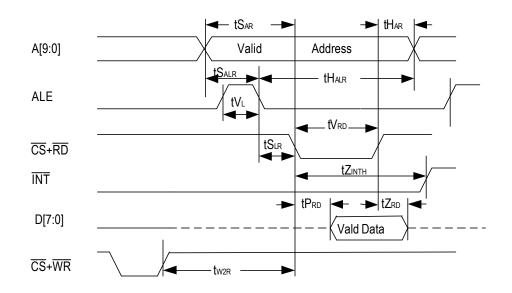

|   | 7.5 MICROPROCESSOR READACCESS TIMING                | 267   |

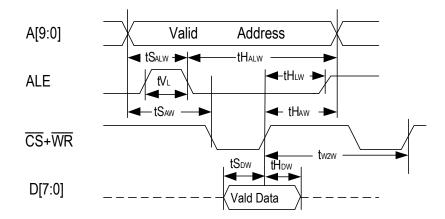

|   | 7.6 MICROPROCESSOR WRITEACCESS TIMING               | 268   |

|   | 7.7 I/O TIMING CHARACTERISTICS                      | 269   |

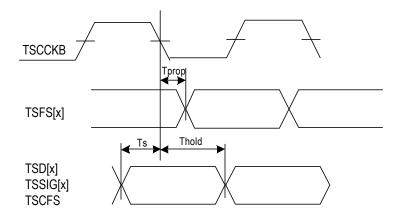

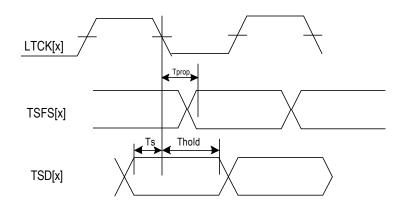

|   | 7.7.1 Transmit System Interface Timing              | 269   |

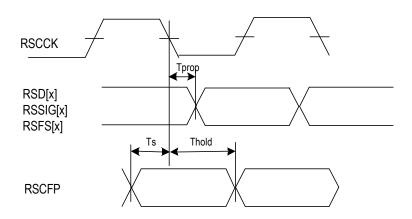

|   | 7.7.2 Receive System Interface Timing               | 270   |

|   | 7.7.3 Receive & Transmit Line Timing                | 271   |

|   | 7.7.3.1 Receive Line Interface Timing               | 271   |

|   | 7 7 3 2 Transmit Line Interface Timing              | 271   |

## **LIST OF FIGURES**

| Figure - 1. E1 Frame Searching Process                                                       | 22 |

|----------------------------------------------------------------------------------------------|----|

| Figure - 2. Basic Frame Searching Process                                                    | 23 |

| Figure - 3. HDLC Packet                                                                      | 29 |

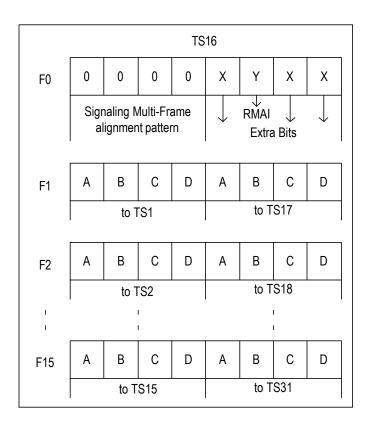

| Figure-4.TS16ArrangementinSignalingMulti-Frame                                               | 32 |

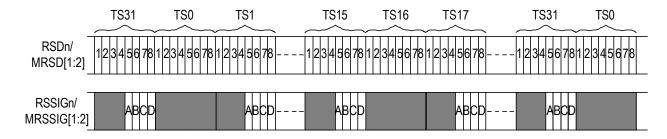

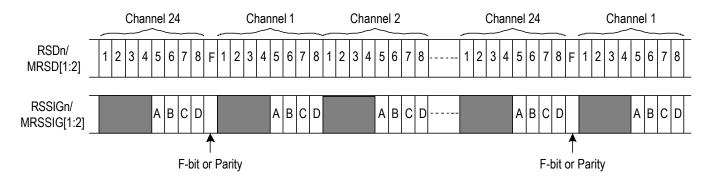

| Figure - 5. Signaling Output in E1 Mode                                                      | 32 |

| Figure - 6. Signaling Output in T1/J1 Mode                                                   | 32 |

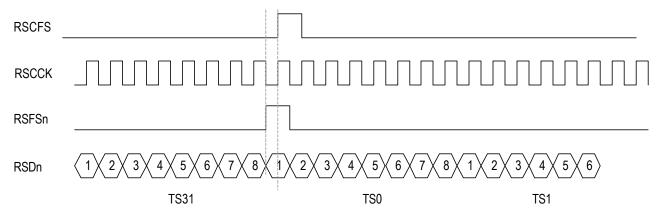

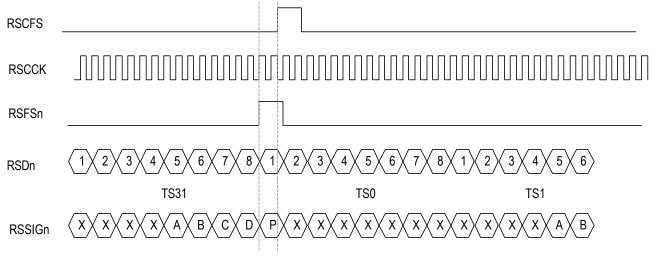

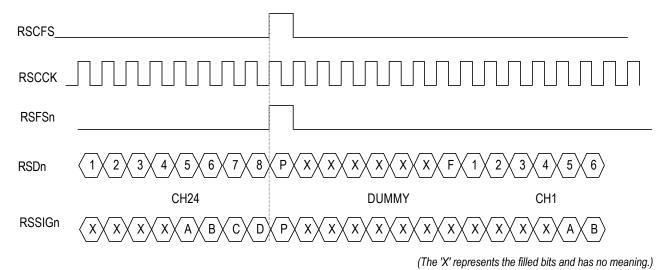

| Figure - 7. Receive Clock Slave RSCK Reference Mode                                          | 36 |

| Figure - 8. E1 Receive Clock Slave RSCK Reference Mode - Functional Timing Example 1         | 37 |

| Figure - 9. E1 Receive Clock Slave RSCK Reference Mode - Functional Timing Example 2         | 37 |

| Figure-10. Receive Clock Slave External Signaling Mode                                       |    |

| Figure - 11. E1 Receive Clock Slave External Signaling Mode - Functional Timing Example 1    | 38 |

| Figure - 12. E1 Receive Clock Slave External Signaling Mode - Functional Timing Example 2    | 39 |

| Figure - 13. Receive Clock Master Full E1 or T1/J1 Mode                                      | 40 |

| Figure - 14. E1 Receive Clock Master Full E1 Mode - Functional Timing Example                | 40 |

| Figure - 15. Receive Clock Master Fractional E1 or T1/J1 Mode                                | 41 |

| Figure-16. E1 Receive Clock Master Fractional E1 Mode-Functional Timing Example              | 42 |

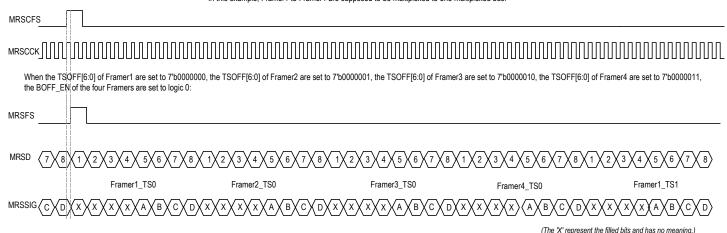

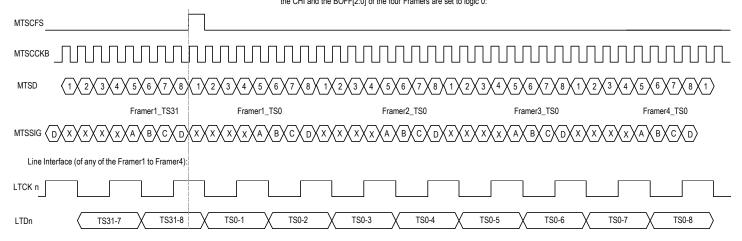

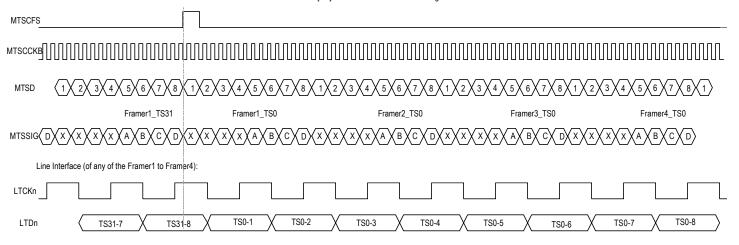

| Figure-17. Receive Multiplexed Mode                                                          | 43 |

| Figure - 18. E1 Receive Multiplexed Mode - Functional Timing Example 1                       | 43 |

| Figure - 19. E1 Receive Multiplexed Mode - Functional Timing Example 2                       | 44 |

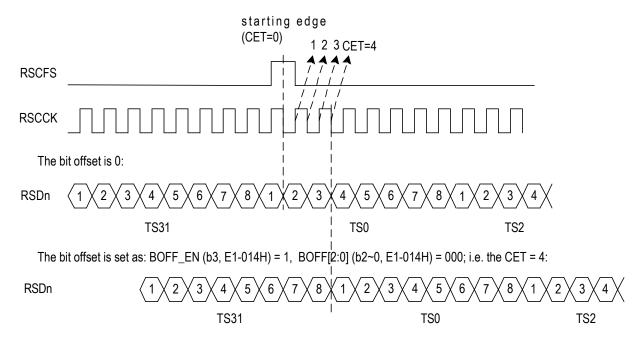

| Figure - 20. Receive Bit Offset - Between RSCFS & RSDn                                       |    |

| Figure - 21. Receive Bit Offset - Between RSFSn & RSDn                                       | 46 |

| Figure - 22. T1/J1 To E1 Format Conversion                                                   | 48 |

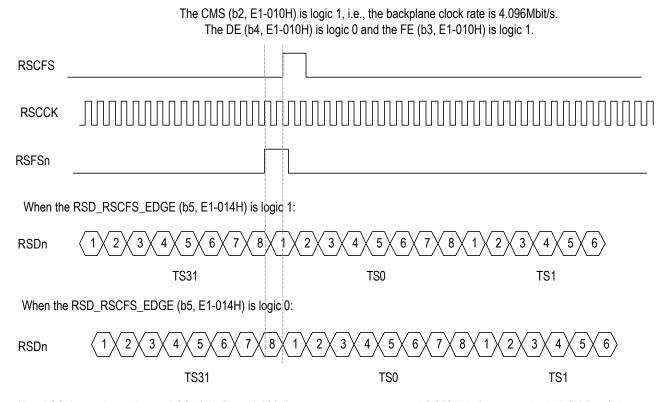

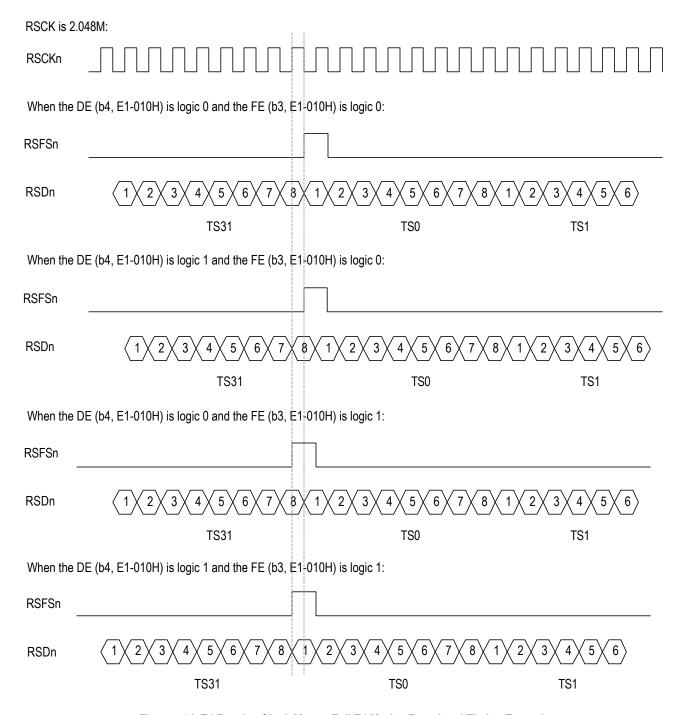

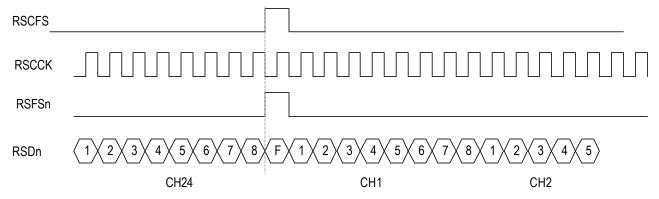

| Figure - 23. T1/J1 Receive Clock Slave RSCK Reference Mode - Functional Timing Example 1     | 48 |

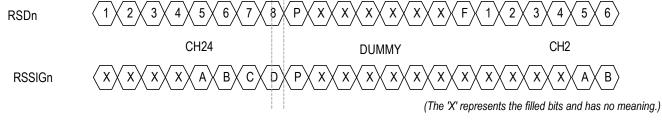

| Figure - 24. T1/J1 Receive Clock Slave RSCK Reference Mode - Functional Timing Example 2     | 49 |

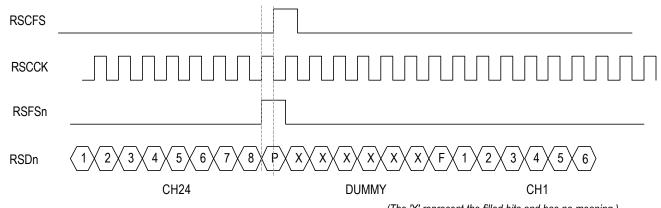

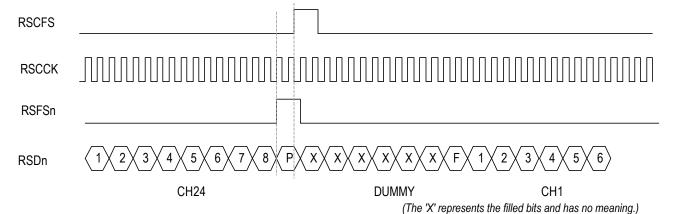

| Figure - 25. T1/J1 Receive Clock Slave RSCK Reference Mode - Functional Timing Example 3     |    |

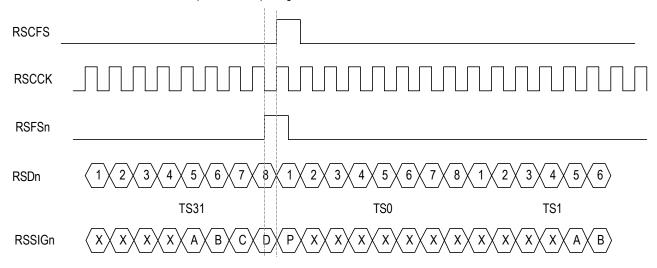

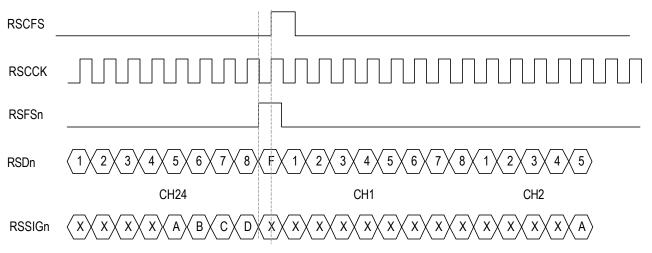

| Figure - 26. T1/J1 Receive Clock Slave External Signaling Mode - Functional Timing Example 1 | 50 |

| Figure - 27. T1/J1 Receive Clock Slave External Signaling Mode - Functional Timing Example 2 | 51 |

| Figure - 28. T1/J1 Receive Clock Slave External Signaling Mode - Functional Timing Example 3 | 51 |

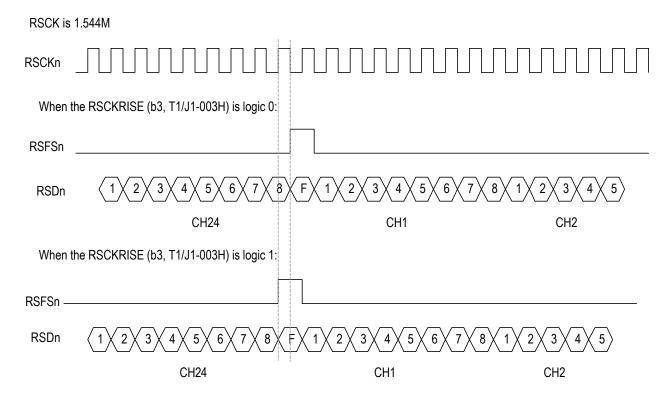

| Figure - 29. T1/J1 Receive Clock Master Full T1/J1 Mode - Functional Timing Example          | 52 |

| Figure-30. T1/J1 Receive Clock Master Fractional T1/J1 Mode-Functional Timing Example        | 53 |

| Figure-31. T1/J1 Receive Multiplexed Mode-Functional Timing Example 1                        | 54 |

| Figure-32. T1/J1 Receive Multiplexed Mode-Functional Timing Example 2                        | 54 |

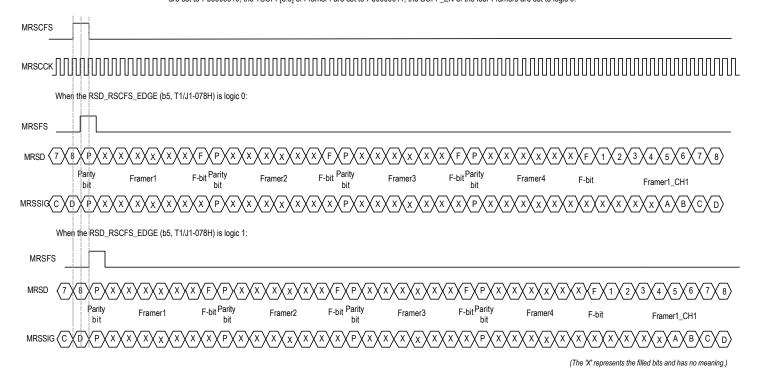

| Figure - 33. Receive Bit Offset in T1/J1 Mode                                                |    |

| Figure - 34. PRBS Pattern Generator                                                          | 56 |

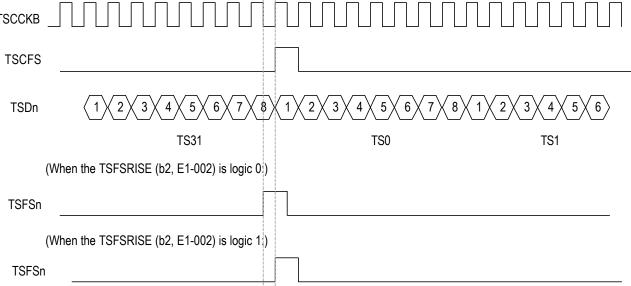

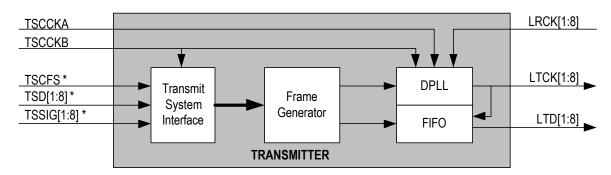

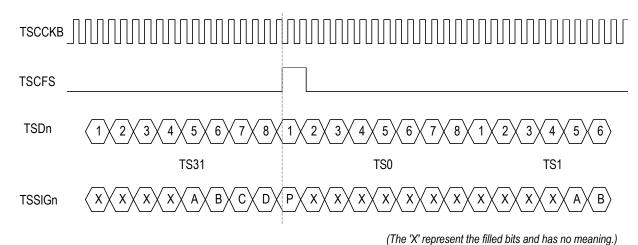

| Figure - 35. Transmit Clock Slave TSFS Enable Mode                                           |    |

| Figure - 36. E1 Transmit Clock Slave TSFS Enable Mode - Functional Timing Example 1          | 59 |

| Figure - 37. E1 Transmit Clock Slave TSFS Enable Mode - Functional Timing Example 2          |    |

| Figure-38. Transmit Clock Slave External Signaling Mode                                      | 60 |

|                                                                                              |    |

| Figure - 39. E1 Transmit Clock Slave External Signaling Mode - Functional Timing Example 1 | 60    |

|--------------------------------------------------------------------------------------------|-------|

| Figure - 40. E1 Transmit Clock Slave External Signaling Mode - Functional Timing Example 2 | 61    |

| Figure - 41. Transmit Clock Master Mode                                                    | 61    |

| Figure - 42. E1 Transmit Clock Master Mode - Functional Timing Example                     | 62    |

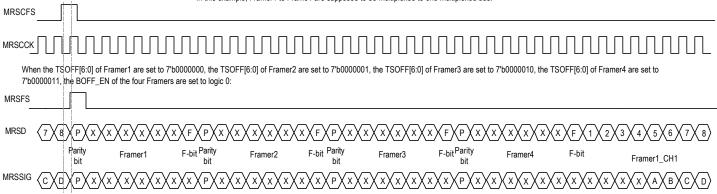

| Figure-43. Transmit Multiplexed Mode                                                       | 63    |

| Figure - 44. E1 Transmit Multiplexed Mode - Functional Timing Example 1                    | 64    |

| Figure - 45. E1 Transmit Multiplexed Mode - Functional Timing Example 2                    | 64    |

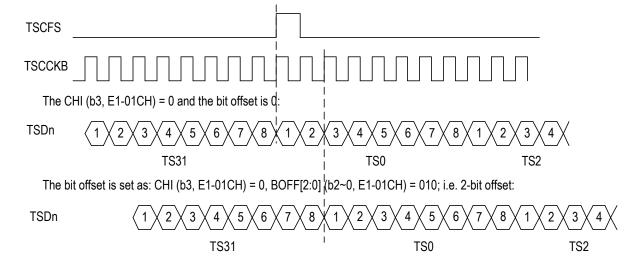

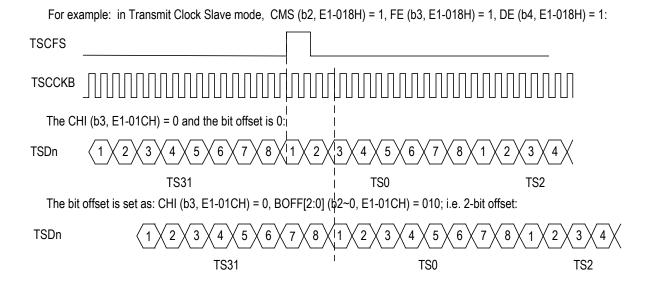

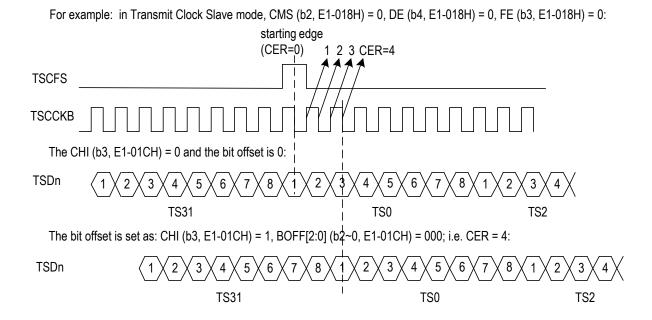

| Figure - 46. Transmit Bit Offset in E1 Mode - 1                                            | 65    |

| Figure - 47. Transmit Bit Offset in E1 Mode - 2                                            | 66    |

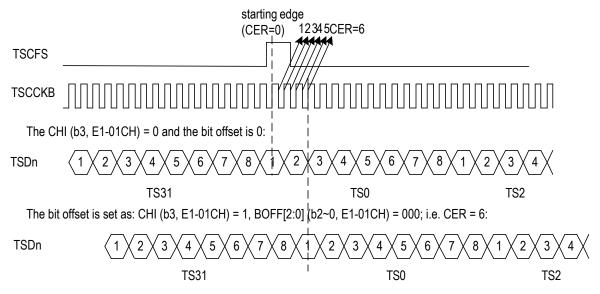

| Figure - 48. Transmit Bit Offset in E1 Mode - 3                                            | 66    |

| Figure - 49. Transmit Bit Offset in E1 Mode - 4                                            | 67    |

| Figure - 50. Transmit Bit Offset in E1 Mode - 5                                            | 67    |

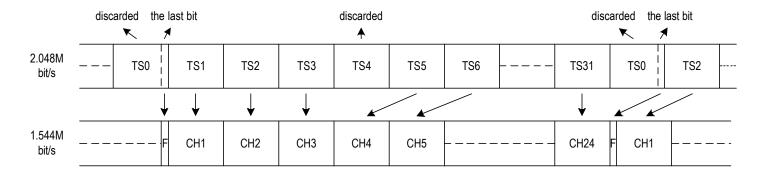

| Figure - 51. E1 To T1/J1 Format Conversion                                                 | 69    |

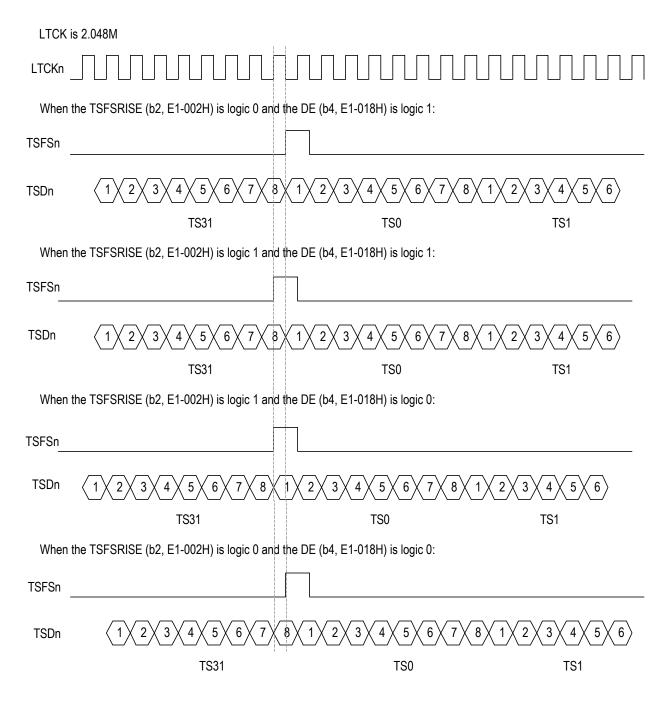

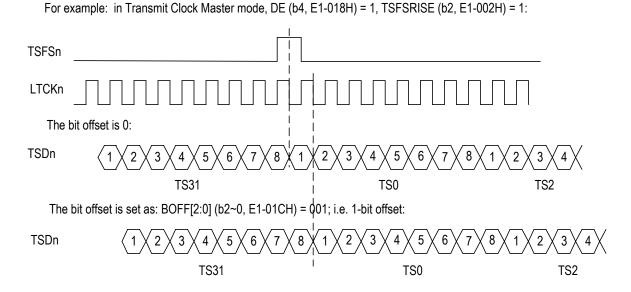

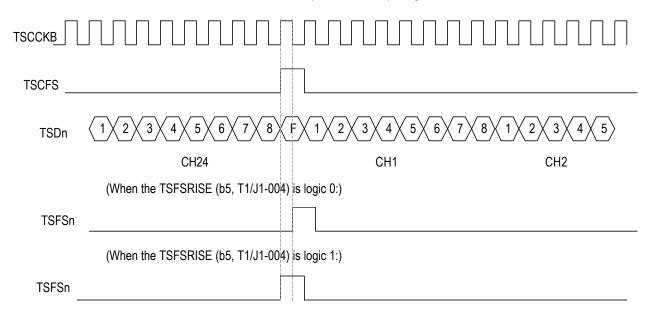

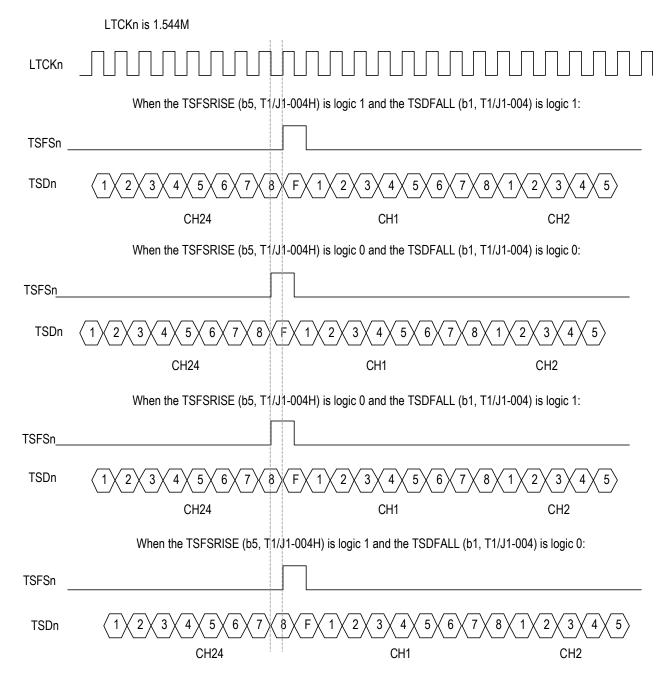

| Figure - 52. T1/J1 Transmit Clock Slave TSFS Enable Mode - Functional Timing Example 1     | 69    |

| Figure - 53. T1/J1 Transmit Clock Slave TSFS Enable Mode - Functional Timing Example 2     | 70    |

| Figure - 54. T1/J1 Transmit Clock Slave TSFS Enable Mode - Functional Timing Example 3     | 70    |

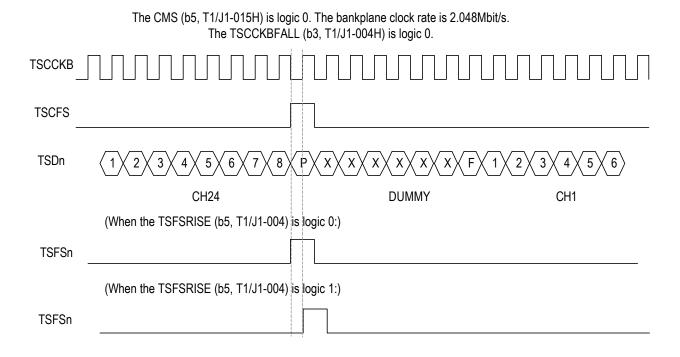

| Figure-55. T1/J1 Transmit Clock Slave External Signaling Mode-Functional Timing Example 1  | 71    |

| Figure-56. T1/J1 Transmit Clock Slave External Signaling Mode-Functional Timing Example 2  | 71    |

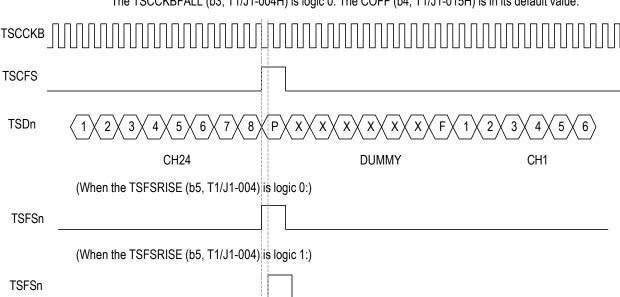

| Figure-57. T1/J1 Transmit Clock Slave External Signaling Mode-Functional Timing Example 3  | 72    |

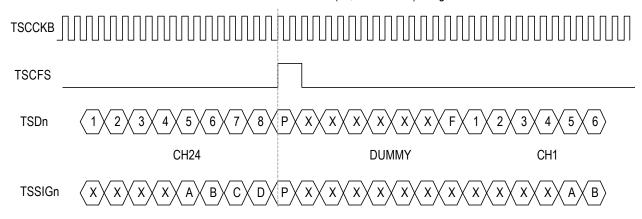

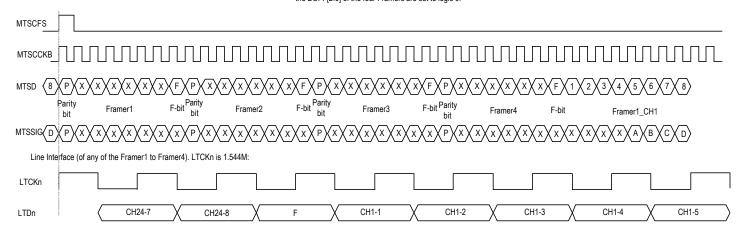

| Figure-58. T1/J1 Transmit Clock Master Mode-Functional Timing Example                      | 73    |

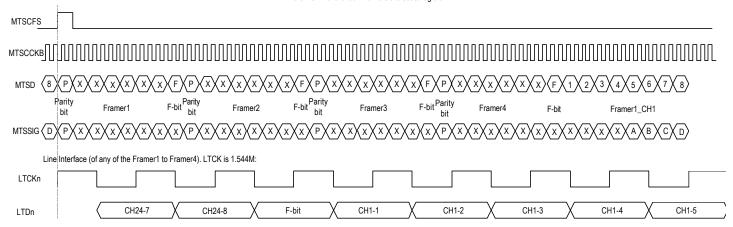

| Figure-59. T1/J1 Transmit Multiplexed Mode-Functional Timing Example 1                     | 74    |

| Figure-60. T1/J1 Transmit Multiplexed Mode-Functional Timing Example 2                     | 74    |

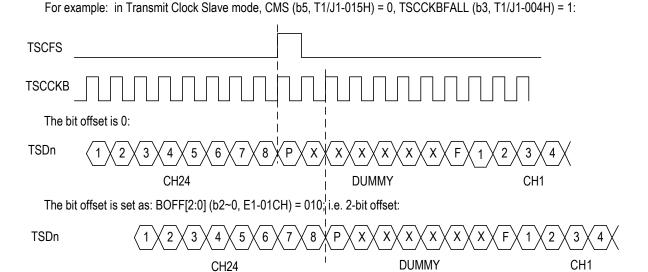

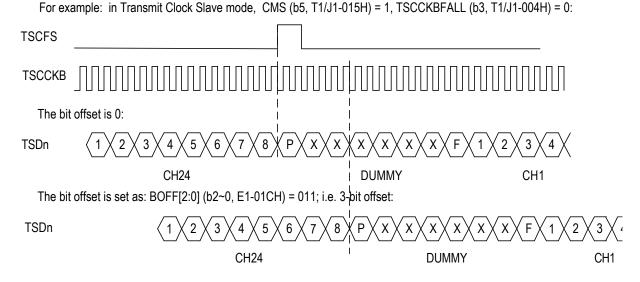

| Figure - 61. Transmit Bit Offset in T1/J1 Mode - 1                                         | 75    |

| Figure - 62. Transmit Bit Offset in T1/J1 Mode - 2                                         | 75    |

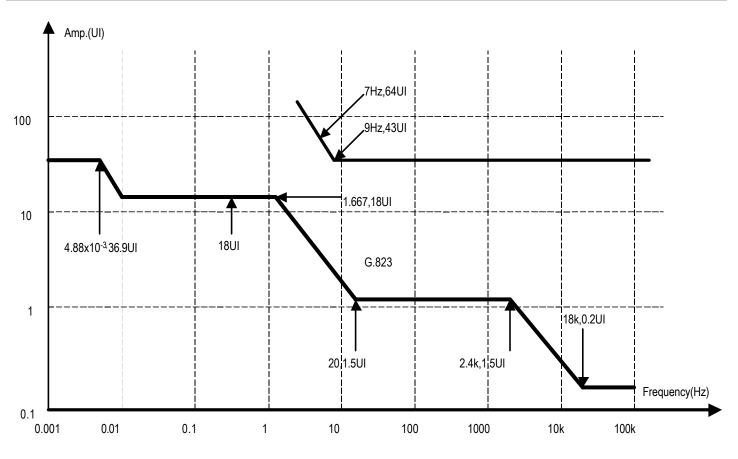

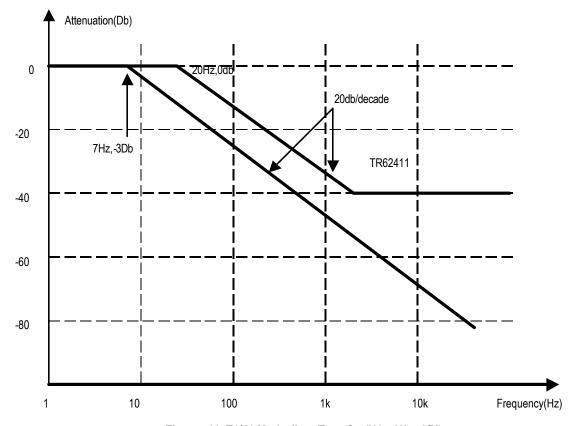

| Figure - 63. E1 Mode Jitter Tolerance (N1 = N2 = 2fH)                                      | 82    |

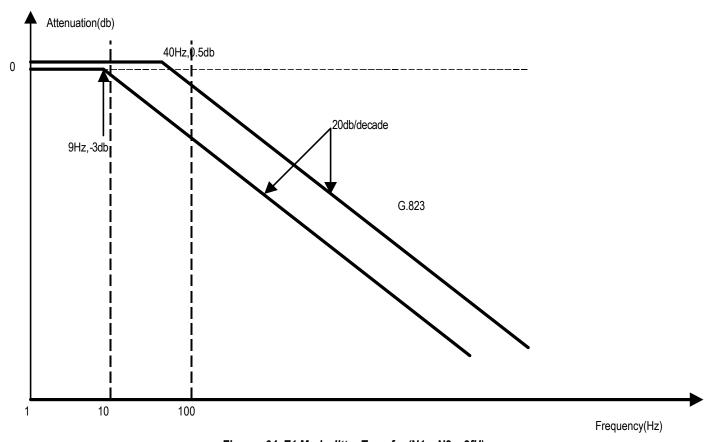

| Figure - 64. E1 Mode Jitter Transfer (N1 = N2 = 2fH)                                       | 82    |

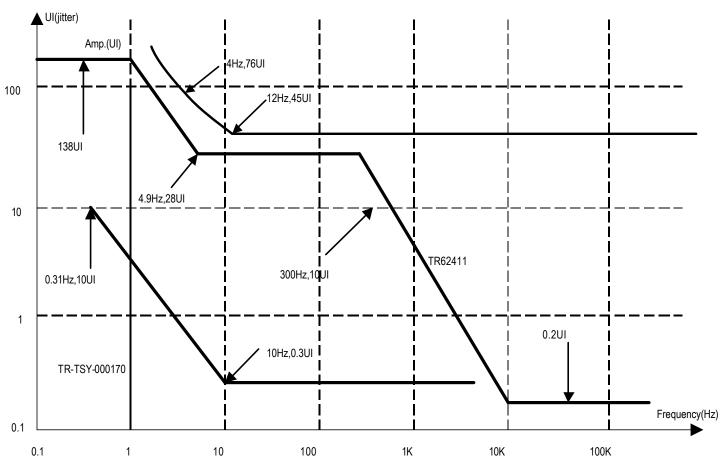

| Figure - 65. T1/J1 Mode Jitter Tolerance (N1 = N2 = 2fH)                                   | 84    |

| Figure - 66. T1/J1 Mode Jitter Transfer (N1 = N2 = 2fH)                                    | 84    |

| Figure - 67. Transmit Clock Select                                                         | 85    |

| Figure-68. Line Loopback                                                                   | 87    |

| Figure-69. Digital Loopback                                                                | 88    |

| Figure-70. Payload Loopback                                                                | 89    |

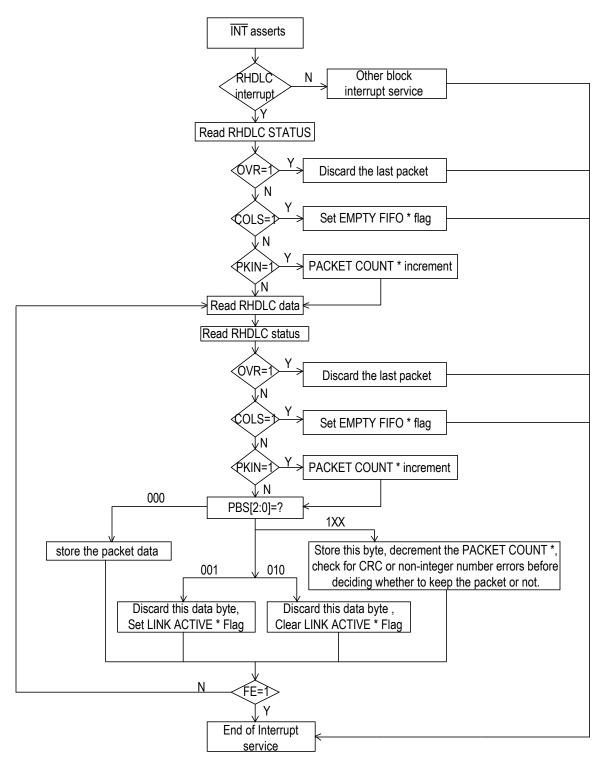

| Figure - 71. Interrupt Service in E1 Mode HDLC Receiver                                    | 96    |

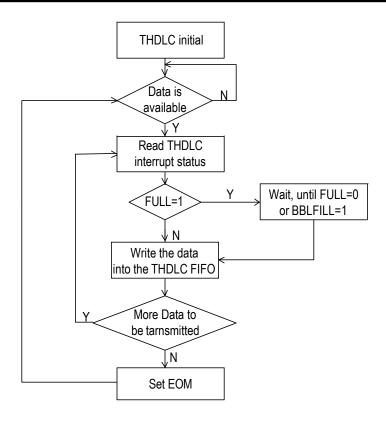

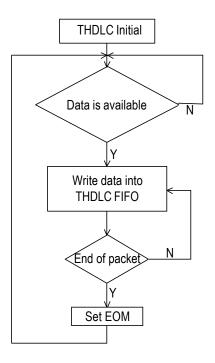

| Figure - 72. Writing Data to E1 Mode THDLC FIFO                                            | 97    |

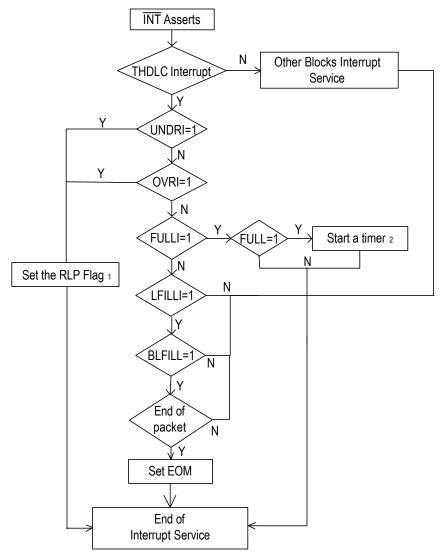

| Figure - 73. Interrupt Service in E1 Mode HDLC Transmitter                                 | 98    |

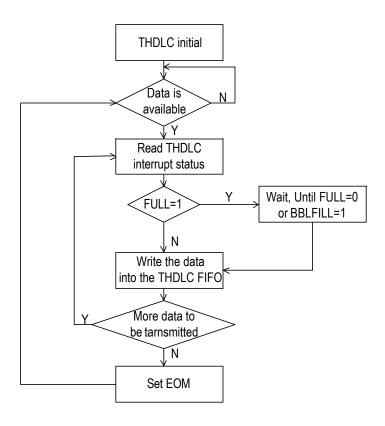

| Figure - 74. Polling Mode in E1 Mode HDLC Transmitter                                      | 99    |

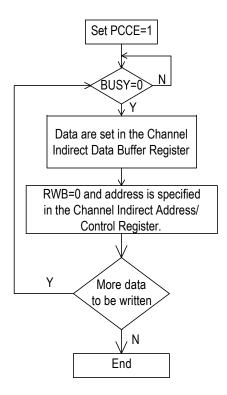

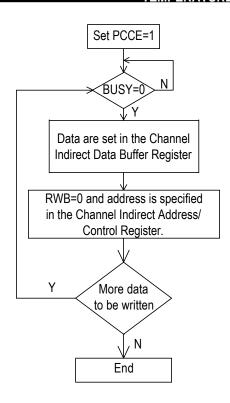

| Figure - 75. Writing Sequence of Indirect Register in E1 Mode                              | 104   |

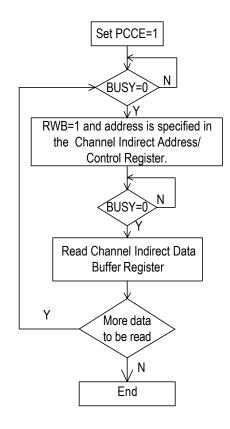

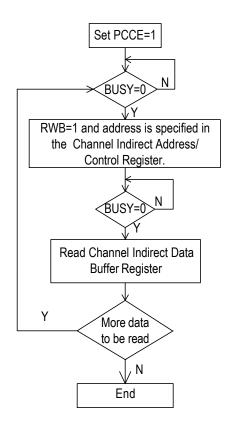

| Figure - 76. Reading Sequence of Indirect Register in E1 Mode                              | 104   |

| Figure - 77. Interrupt Service in T1/J1 Mode HDLC Receiver                                 | . 111 |

| Figure - 78. Writing Data to T1/J1 Mode THDLC FIFO                                         | . 112 |

| Figure - 79. Interrupt Service in T1/J1 Mode HDLC Transmitter           | 113 |

|-------------------------------------------------------------------------|-----|

| Figure - 80. Polling Mode in T1/J1 Mode HDLC Transmitter                | 114 |

| Figure - 81. Writing Sequence of Indirect Register in T1/J1 Mode        | 118 |

| Figure - 82. Reading Sequence of Indirect Register in T1/J1 Mode        | 118 |

| Figure-83.JTAGArchitecture                                              | 259 |

| Figure - 84. JTAG State Diagram                                         | 264 |

| Figure - 85. Read Access Timing                                         | 267 |

| Figure - 86. Write Access Timing                                        | 268 |

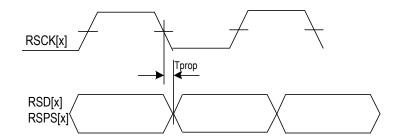

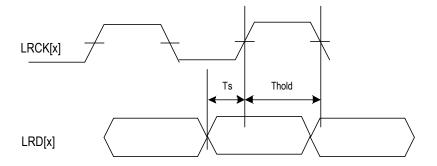

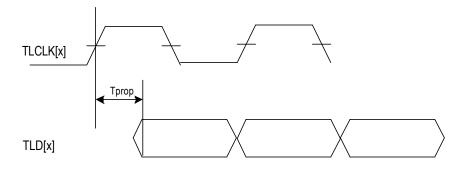

| Figure - 87. Transmit Interface Timing (Transmit System Common Clock#B) | 269 |

| Figure-88. TransmitInterface Timing (Line Transmit Clock)               | 269 |

| Figure - 89. Receive Interface Timing (Receive System Common Clock)     | 270 |

| Figure - 90. Receive Interface Timing (Receive System Clock)            | 270 |

| Figure-91. Receive Line Interface Timing                                | 271 |

| Figure - 92. Transmit Line Interface Timing                             | 271 |

|                                                                         |     |

## **LIST OF TABLES**

| Table - 1. The Structure Of TS0                                                                                           | 23 |

|---------------------------------------------------------------------------------------------------------------------------|----|

| Table - 2. Interrupt Sources In The E1 Frame Processor                                                                    | 25 |

| Table - 3. The Structure Of SF Format                                                                                     | 26 |

| Table - 4. The Structure Of ESF Format                                                                                    | 27 |

| Table - 5. Interrupt Sources In The T1 / J1 Frame Processor                                                               | 27 |

| Table - 6. Basic Frame Alignment Pattern Error Counter                                                                    | 28 |

| Table - 7. Alarm Summary in ALMD                                                                                          | 29 |

| Table - 8. A-Law Digital Milliwatt Pattern                                                                                | 34 |

| Table - 9. u-Law Digital Milliwatt Pattern                                                                                | 34 |

| Table - 10. E1 Mode Receive System Interface in Different Operation Modes                                                 | 35 |

| Table - 11. Operation Mode Selection in E1 Receive Path                                                                   | 35 |

| Table - 12. Active Edge Selection of RSCCK (in E1 Receive Clock Slave RSCK Reference Mode)                                | 36 |

| Table - 13. Active Edge Selection of RSCCK (in E1 Receive Clock Slave External Signaling Mode)                            | 38 |

| Table - 14. Active Edge Selection of RSCK (in E1 Receive Clock Master Mode)                                               | 39 |

| Table - 15. Active Edge Selection of MRSCCK (in E1 Receive Multiplexed Mode)                                              | 41 |

| Table - 16. Offset in Different Operation Modes                                                                           | 45 |

| Table - 17. Receive System Interface Bit Offset (FPMODE [b5, E1-011H] = 0)                                                | 45 |

| Table - 18. Receive System Interface Bit Offset (FPMODE [b5, E1-011H] = 1)                                                | 45 |

| Table - 19. Bit Offset Between RSFSn and RSDn When the BRXSMFP and the ALTIFP (b2, b0, E1-011H) are Both Set To Logical 1 | 45 |

| Table - 20. T1/J1 Mode Receive System Interface in Different Operation Modes                                              | 47 |

| Table - 21. Operation Mode Selection in T1/J1 Receive Path                                                                | 47 |

| Table - 22. Active Edge Selection of RSCCK (in T1/J1 Receive Clock Slave RSCK Reference Mode)                             | 48 |

| Table - 23. Active Edge Selection of RSCCK (in T1/J1 Receive Clock Slave External Signaling Mode)                         | 50 |

| Table - 24. Active Edge Selection of MRSCCK (in T1/J1 Receive Multiplexed Mode)                                           | 52 |

| Table - 25. Receive System Interface Bit Offset                                                                           | 55 |

| Table - 26. E1 Mode Transmit System Interface in Different Operation Modes                                                | 58 |

| Table - 27. Operation Mode Selection in E1 Transmit Path                                                                  | 58 |

| Table - 28. Active Edge Selection of TSCCKB (in E1 Transmit Clock Slave TSFS Enable Mode)                                 | 60 |

| Table - 29. Active Edge Selection of TSCCKB (in E1 Transmit Clock Slave External Signaling Mode)                          | 60 |

| Table - 30. Active Edge Selection of MTSCCKB (in E1 Transmit Multiplexed Mode)                                            | 63 |

| Table - 31. Transmit System Interface Bit Offset (CHI [b3, E1-01CH] = 1, CMS [b2, E1-018H] = 0)                           | 65 |

| Table - 32. Transmit System Interface Bit Offset (CHI [b3, E1-01CH] = 1, CMS [b2, E1-018H] = 1)                           | 65 |

| Table - 33. T1/J1 Mode Transmit System Interface in Different Operation Modes                                             | 68 |

| Table - 34. Operation Mode Selection in T1/J1 Transmit Path                                                               | 68 |

| Table - 35. Active Edge Selection of TSCCKB (in T1/J1 Transmit Clock Slave TSFS Enable Mode)                              | 69 |

| Table - 36. Remote Alarm Indication                                                                                       | 77 |

| Table - 37. Content in International Bits (when the INDIS [b1, E1-040H] is logic 0)                                       | 78 |

| Table - 38. Interrupt Summary                                                                                             | 78 |

|                                                                                                                           |    |

| Table - 39. Default Setting in Receive Path                        | 90  |

|--------------------------------------------------------------------|-----|

| Table - 40. Default Setting in Transmit Path                       | 90  |

| Table - 41. Various Operation Modes in Receive Path for Reference  | 91  |

| Table - 42. Various Operation Modes in Transmit Path for Reference | 93  |

| Table - 43. Example for Using HDLC Receiver                        | 95  |

| Table - 44. Example for Using HDLC Transmitter                     | 97  |

| Table - 45. Test Pattern                                           | 100 |

| Table - 46. The Setting of PRGD                                    | 101 |

| Table - 47. Initializtion of TPLC                                  | 101 |

| Table - 48. Initializtion of RPLC                                  | 103 |

| Table - 49. Error Insertion                                        | 103 |

| Table - 50. Default Setting in Receive Path                        | 105 |

| Table - 51. Default Setting in Transmit Path                       | 105 |

| Table - 52. Various Operation Modes in Receive Path for Reference  | 106 |

| Table - 53. Various Operation Modes in Transmit Path for Reference | 108 |

| Table - 54 . Example for Using HDLC Receiver                       | 110 |

| Table - 55. Example for Using HDLC Transmitter                     | 112 |

| Table - 56. Test Pattern                                           | 115 |

| Table - 57. The Setting of PRGD                                    | 116 |

| Table - 58. Initializtion of TPLC                                  | 116 |

| Table - 59. Initializtion of RPLC                                  | 117 |

| Table - 60. Error Insertion                                        | 118 |

| Table - 61. T1/E1 Mode Selection Register                          | 119 |

| Table - 62a. E1 Mode Register Map - Direct Register                | 120 |

| Table - 62b. E1 Mode Register Map - Indirect Register              | 123 |

| Table - 63a. T1/J1 Mode Register Map - Direct Register             | 123 |

| Table - 63b. T1/J1 Mode Register Map - Indirect Register           | 125 |

| Table - 64. IR Code                                                | 260 |

| Table - 65. IDR                                                    | 261 |

| Table - 66. Boundary Scan Sequence and the I/O Pad Cell Type       | 261 |

| Table - 67. TAP Controller State Description                       | 263 |

### 1 PIN ASSIGNMENTS

## 1.2 144 PIN PBGA PACKAGE (BOTTOM VIEW)

|   | 12                                 | 11                                  | 10                       | 9                    | 8                                   | 7                                   | 6                  | 5                | 4                  | 3       | 2        | 1          | - |

|---|------------------------------------|-------------------------------------|--------------------------|----------------------|-------------------------------------|-------------------------------------|--------------------|------------------|--------------------|---------|----------|------------|---|

| Α | TSD[7]                             | TSD[6]                              | TSFS[4]/<br>TSSIG[4]     | GNDC[4]              | TSD[3]                              | TSFS[1]/<br>TSSIG[1]/<br>MTSSIG[1]/ | VDDC[3]            | RSCCK/<br>MRSCCK | TSCCKA             | TCK     | LRD[1]   | LRD[3]     | A |

| В | RSD[1]/<br>MRSD[1]                 | TSD[8]                              | TSFS[6]/<br>TSSIG[6]     | TSD[5]               | TSFS[2]/<br>TSSIG[2]/<br>MTSSIG[2]/ | TSD[1]/<br>MTSD[1]                  | XCK                | RSCFS/<br>MRSCFS | TSCCKB/<br>MTSCCKB | TMS     | LRD[2]   | LRD[4]     | В |

| С | RSD[2]/<br>MRSD[2]                 | RSCK[1]/<br>RSSIG[1]/<br>MRSSIG[1]/ | TSFS[8]/<br>TSSIG[8]     | TSFS[7]/<br>TSSIG[7] | VDDC[4]                             | TSFS[3]/<br>TSSIG[3]                | GNDC[3]            | TSCFS/<br>MTSCFS | TDO                | LRCK[1] | LRCK[3]  | LTCK[1]    | С |

| D | RSCK[2]\<br>RSSIG[2]\<br>MRSSIG[2] | RSFS[2]/<br>MRSFS[2]                | (VDDIO[3])               | RSFS[1]/<br>MRSFS[1] | TSFS[5]/<br>TSSIG[5]                | TSD[4]                              | TSD[2]/<br>MTSD[2] | TRST             | TDI                | LRCK[2] | LTD[1]   | LTCK[2]    | D |

| Е | RSCK[3]/<br>RSSIG[3]               | RSFS[3]                             | RSD[3]                   | GNDIO[3]             | VDDC[5]                             | VDDC[6]                             | VDDC[7]            | VDDC[8]          | LRCK[4]            | LTD[2]  | LTCK[4]  | LTD[4]     | E |

| F | RSD[4]                             | VDDC[2]                             | GNDC[2]                  | RSD[5]               | (VDDC[9]                            | VDDC[10]                            | VDDC[11]           | VDDC[12]         | LTD[3]             | LTCK[3] | GNDIO[0] | (VDDIO[0]) | F |

| G | RSFS[4]                            | RSCK[4]/<br>RSSIG[4]                | RSD[6]                   | RSCK[6]/<br>RSSIG[6] | GNDC[5]                             | GNDC[6]                             | GNDC[7]            | GNDC[8]          | BIAS               | LTD[5]  | GNDC[0]  | VDDC[0]    | G |

| Н | RSFS[5]                            | RSCK[5]/<br>RSSIG[5]                | TESTSE                   | RSCK[7]/<br>RSSIG[7] | GNDC[9]                             | GNDC[10]                            | GNDC[11]           | GNDC[12]         | LTCK[8]            | LTCK[6] | LTCK[5]  | LTD[6]     | Н |

| J | RSFS[6]                            | RSD[7]                              | RSFS[8]                  | (A[9]                | (A[7]                               | VDDIO[1]                            | D[4]               | (INT)            | LRD[5]             | LTD[8]  | LTD[7]   | LTCK[7]    | J |

| K | VDDIO[2]                           | RSD[8]                              | $\overline{\mathbb{WR}}$ | (A[6]                | A[3]                                | A[0]                                | D[5]               | D[2]             | LRCK[7]            | LRCK[6] | LRCK[5]  | GNDIO[1]   | К |

| L | RSFS[7]                            | $\overline{\mathbb{R}\mathbb{D}}$   | A[10]                    | (A[4]                | A[1]                                | ALE                                 | VDDC[1]            | D[7]             | D[0]               | LRCK[8] | LRD[7]   | LRD[6]     | L |

| M | RSCK[8]/<br>RSSIG[8]               | CS                                  | A[8]                     | A[5]                 | A[2]                                | GNDC[1]                             | GNDIO[2]           | D[6]             | D[3]               | D[1]    | RST      | LRD[8]     | М |

|   | 12                                 | 11                                  | 10                       | 9                    | 8                                   | 7                                   | 6                  | 5                | 4                  | 3       | 2        | 1          | J |

## **2 PIN DESCRIPTION**

| Nama Tima Pin No. |        |      | No          |                                                                                           |

|-------------------|--------|------|-------------|-------------------------------------------------------------------------------------------|

|                   |        | PBGA | Description |                                                                                           |

|                   |        | . 4  |             | Line and System Interface                                                                 |

| LRD[1]            | Input  | 1    | A2          | LRD[1:8]: Line Receive Data for Framer 1 ~ 8                                              |

| LRD[2]            |        | 3    | B2          | These pins receive the data stream from line interface units or from a higher demultiplex |

| LRD[3]            |        | 5    | A1          | interface. Data on these pins are sampled on the active edge of the corresponding         |

| LRD[4]            |        | 7    | B1          | LRCKn.                                                                                    |

|                   |        | 31   | J4          | LIVOIVII.                                                                                 |

| LRD[5]            |        | 33   | L1          |                                                                                           |

| LRD[6]            |        | 35   | L2          |                                                                                           |

| LRD[7]            |        |      |             |                                                                                           |

| LRD[8]            | 1(     | 37   | M1          | LDOVA OLIVEDENIA OLIVETANIA O                                                             |

| LRCK[1]           | Input  | 2    | C3          | LRCK[1:8]: Line Receive Clock for Framer 1 ~ 8                                            |

| LRCK[2]           |        | 4    | D3          | These pins receive externally recovered line clock (2.048 or 1.544 MHz). The clock is     |

| LRCK[3]           |        | 6    | C2          | used to sample the data on the corresponding LRDn.                                        |

| LRCK[4]           |        | 8    | E4          |                                                                                           |

| LRCK[5]           |        | 32   | K2          |                                                                                           |

| LRCK[6]           |        | 34   | K3          |                                                                                           |

| LRCK[7]           |        | 36   | K4          |                                                                                           |

| LRCK[8]           |        | 38   | L3          |                                                                                           |

| RSCK[1]/RSSIG[1]/ | Output | 96   | C11         | RSCK[1:8]: Receive Side System Clock for Framer 1 ~ 8                                     |

| MRSSIG[1]         |        |      |             | In Receive Clock Master Full E1 or T1/J1 mode, the clock is a smoothed version of the     |

| RSCK[2]/RSSIG[2]/ |        | 91   | D12         | corresponding 2.048 or 1.544 MHz Line Receive Clock (LRCK). The RSCKn is pulsed for       |

| MRSSIG[2]         |        |      |             | each bit in the 256-bit or 193-bit frame. The corresponding RSFSn and RSDn pins are       |

| RSCK[3]/RSSIG[3]  |        | 88   | E12         | updated on the active edge of the RSCKn.                                                  |

| RSCK[4]/RSSIG[4]  |        | 83   | G11         | In Receive Clock Master Nx64K mode, the clock is a gapped version of the associated       |

| RSCK[5]/RSSIG[5]  |        | 80   | H11         | smoothed LRCKn. The pulse number of the RSCKn in each frame is controllable from 0 to     |

| RSCK[6]/RSSIG[6]  |        | 77   | G9          | 255 or from 0 to 192 on a per-timeslot/channel basis. The corresponding RSFSn and         |

| RSCK[7]/RSSIG[7]  |        | 72   | H9          | RSDn pins are updated on the active edge of the RSCKn.                                    |

| RSCK[8]/RSSIG[8]  |        | 69   | M12         | In Receive Clock Slave RSCK Reference mode, the RSCKn can be selected to be either        |

| '''               |        |      |             | a 2.048/1.544 MHz jitter attenuated version of the corresponding LRCKn or an 8KHz clock   |

|                   |        |      |             | divided down from the smoothed line clock LRCKn.                                          |

|                   |        |      |             | RSSIG[1:8]: Receive Side System Signaling for Framer 1 ~ 8                                |

|                   |        |      |             | In Receive Clock Slave External Signaling mode, the extracted signaling is output on      |

|                   |        |      |             | these pins. The signal on these pins is timeslot/channel-aligned with the data output on  |

|                   |        |      |             | the corresponding RSDn pin and is updated on the active edge of the RSCCK. The            |

|                   |        |      |             | extracted signaling is located in the lower nibble (b5 ~ b8). In E1 mode, the extracted   |

|                   |        |      |             | signaling repeats during the entire Signaling Multi-Frame for the same timeslot. In T1/J1 |

|                   |        |      |             | mode, the extracted signaling repeats during the entire SF/ESF for the same channel.      |

|                   |        |      |             | MRSSIG[1:2]: Multiplexed Receive Side System Signaling                                    |

|                   |        |      |             | When the multiplexed bus structure is configured, the extracted signaling data from the   |

|                   |        |      |             | selected framers are multiplexed on these pins using a byte-interleaved multiplexing      |

|                   |        |      |             | scheme. The data on the MRSSIG[1:2] are updated on the active edge of the MRSCCK.         |

| RSD[1]/MRSD[1]    | Output | 97   | B12         | RSD[1:8]: Receive Side System Data for Framer 1 ~ 8                                       |

| RSD[2]/MRSD[2]    |        | 94   | C12         | The processed data stream is output on these pins.                                        |

| RSD[3]            |        | 89   | E10         | In Receive Clock Master mode, the RSDn is updated on the active edge of the               |

| RSD[4]            |        | 84   | F12         | corresponding RSCKn.                                                                      |

| RSD[5]            |        | 81   | F9          | In Receive Clock Slave mode, the RSDn is updated on the active edge of the RSCCK.         |

| RSD[6]            |        | 78   | G10         | This toolive shock share mode, the result is appeared on the active edge of the resource. |

| RSD[7]            |        | 73   | J11         | MRSD[1:2]: Multiplexed Receive Side System Data                                           |

| RSD[8]            |        | 70   | K11         | When the multiplexed bus structure is configured, the processed data stream from the      |

| 1,00[0]           |        | , ,  | '`''        | selected framers is multiplexed on these pins using the byte-interleaved multiplexing     |

|                   |        |      |             | scheme. The data on the MRSD[1:2] are updated on the active edge of the MRSCCK.           |

|                   |        |      |             | Solicing. The data on the Mixod [1.2] are appared on the active edge of the Mixod N.      |

|                                                                                                                   | _      | Pin No.                                      |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------|--------|----------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Name                                                                                                              | Type   | PQFP                                         | PBGA                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| RSFS[1]/MRSFS[1]<br>RSFS[2]/MRSFS[2]<br>RSFS[3]<br>RSFS[4]<br>RSFS[5]<br>RSFS[6]<br>RSFS[7]<br>RSFS[7]<br>RSFS[8] | Output | 95<br>90<br>87<br>82<br>79<br>76<br>71<br>68 | D9<br>D11<br>E11<br>G12<br>H12<br>J12<br>L12<br>J10 | RSFS[1:8]: Receive Side System Frame Pulse for Framer 1 ~ 8  In E1 mode, RSFSn can be configured to indicate the beginning of Basic Frame, or CRC Multi-Frame or/and Signaling Multi-Frame for data stream on RSDn. When configured for the Basic Frame, RSFSn will pulse high/low during the first bit of each Basic Frame. When configured for CRC Multi-Frame, RSFSn will pulse during the first bit of the first frame of the CRC Multi-Frame. When configured for the Signaling Multi-Frame, RSFSn will pulse during the first bit of the first frame of the Signaling Multi-Frame. When configured to indicate both Signaling and CRC Multi-Frame, RSFSn will go high/low on the first bit of the first frame of the Signaling Multi-Frame and go the opposite after the first bit of the first frame of the CRC Multi-Frame.  In T1/J1 mode, RSFSn can be configured to indicate each F-bit, or the first F-bit of every 12-frame SF / every 24-frame ESF. RSFSn pulses during the above F-bit.  In both E1 and T1/J1 mode, when Receive Clock Master mode is active, the RSFSn is updated on the active edge of the RSCCK.  MRSFS[1:2]: Multiplexed Receive Side System Frame Pulse  When the multiplexed bus structure is configured, the signals on these pins indicate the beginning of a multiplexed frame. The MRSFS[1:2] are undeted on the active edge of |  |  |  |  |

| RSCCK/MRSCCK                                                                                                      | Input  | 120                                          | A5                                                  | beginning of a multiplexed frame. The MRSFS[1:2] are updated on the active edge of the MRSCCK.  RSCCK: Receive Side System Common Clock RSCCK is used only in Receive Clock Slave mode. In E1 mode, it is a 2.048 or 4.096 MHz clock. In T1 mode, it is a 1.544 or 2.048 or 4.096 MHz clock. In Receive Clock Slave RSCK Reference mode, the RSDn and the RSFSn are updated and the RSCFS is sampled on the active edge of the RSCCK. In Receive Clock Slave External Signaling mode, the RSDn, the RSFSn and the RSSIGn are updated and the RSCFS is sampled on the active edge of the RSCCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|                                                                                                                   |        |                                              |                                                     | MRSCCK: Multiplexed Receive Side System Common Clock When the multiplexed bus structure is configured, MRSCCK is an 8.192 or 16.384 MHz clock for the receive system multiplexed bus. The MRSCFS is sampled and the MRSD[1:2], the MRSFS[1:2] and the MRSSIG[1:2] are updated on the active edge of the MRSCCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| RSCFS/MRSCFS                                                                                                      | Input  | 119                                          | B5                                                  | RSCFS: Receive Side System Common Frame Pulse In Receive Clock Slave mode, RSCFS can be selected as a frame alignment reference. It is asserted on the request of each Basic Frame or each Multi-Frame in E1 mode, or it is asserted on the request of F-bit in T1/J1 mode. The RSCFS is sampled on the active edge of the RSCCK.  MRSCFS: Multiplexed Receive Side System Common Frame Pulse When the multiplexed bus structure is configured, the signal on this pin aligns the multiplexed frame to the backplane timing. The MRSCFS is sampled on the active edge of the MRSCCK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                                      | _      | Pin        | No.       | <b>-</b>                                                                                                                                                                  |

|--------------------------------------|--------|------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                 | Type   | PQFP       | PBGA      | Description                                                                                                                                                               |

| TSD[1]/MTSD[1]                       | Input  | 115        | B7        | TSD[1:8]: Transmit Side System Data for Framer 1 ~ 8                                                                                                                      |

| TSD[2]/MTSD[2]                       |        | 113        | D6        | The data streams from the system backplane are input on these pins.                                                                                                       |

| TSD[3]                               |        | 111        | A8        | In Transmit Clock Master mode, the TSDn is sampled on the active edge of the                                                                                              |

| TSD[4]                               |        | 109<br>105 | D7<br>B9  | corresponding LTCKn.                                                                                                                                                      |

| TSD[5]<br>TSD[6]                     |        | 103        | A11       | In Transmit Clock Slave mode, the TSDn is sampled on the active edge of the TSCCKB.                                                                                       |

| TSD[7]                               |        | 103        | A12       | MTSD[1:2]: Multiplexed Transmit Side System Data                                                                                                                          |

| TSD[8]                               |        | 99         | B11       | When the multiplexed bus structure is configured, the data stream from the backplane is                                                                                   |

|                                      |        |            |           | carried on the multiplexed bus for the selected framers. The MTSD[1:2] are sampled on                                                                                     |

|                                      |        |            |           | the active edge of the MTSCCKB.                                                                                                                                           |

| TSFS[1]/TSSIG[1]/                    | Output | 114        | A7        | TSFS[1:8]: Transmit Side System Frame Pulse for Framer 1 ~ 8                                                                                                              |

| MTSSIG[1]                            | /Input |            |           | In Transmit Clock Master mode, the TSFSn indicates the beginning of each Basic Frame                                                                                      |

| TSFS[2]/TSSIG[2]/                    |        | 112        | B8        | in E1 mode, or indicates the F-bit of SF/ESF in T1/J1 mode. The TSFSn is updated on the                                                                                   |

| MTSSIG[2]                            |        | 110        | 07        | active edge of the corresponding LTCKn.                                                                                                                                   |

| TSFS[3]/TSSIG[3]<br>TSFS[4]/TSSIG[4] |        | 110<br>106 | C7<br>A10 | In Transmit Clock Slave TSFS Enabled mode, the TSFSn indicates the beginning of each Basic Frame in E1 mode, or indicates the F-bit of SF/ESF in T1/J1 mode. The TSFSn is |

| TSFS[5]/TSSIG[5]                     |        | 104        | D8        | updated on the active edge of the TSCCKB.                                                                                                                                 |

| TSFS[6]/TSSIG[6]                     |        | 102        | B10       | apadiod on the doubte sage of the 1000NB.                                                                                                                                 |

| TSFS[7]/TSSIG[7]                     |        | 100        | C9        | TSSIG[1:8]: Transmit Side System Signaling for Framer 1 ~ 8                                                                                                               |

| TSFS[8]/TSSIG[8]                     |        | 98         | C10       | In Transmit Clock Slave External Signaling mode, these are the TSSIG inputs. The                                                                                          |

|                                      |        |            |           | signaling is located in the lower nibble (b5 ~ b8) and sampled on the active edge of the                                                                                  |

|                                      |        |            |           | TSCCKB. In E1 mode, the signaling repeats during the entire Signaling Multi-Frame for the                                                                                 |

|                                      |        |            |           | same timeslot. In T1/J1 mode, the signaling repeats during the entire SF/ESF for the same                                                                                 |

|                                      |        |            |           | channel.                                                                                                                                                                  |

|                                      |        |            |           | MTSSIG[1:2]: Multiplexed Transmit Side System Signaling                                                                                                                   |

|                                      |        |            |           | When the multiplexed bus structure is configured, the signaling on the bus is organized in                                                                                |

|                                      |        |            |           | a byte-interleaved scheme for the selected framers. The MTSSIG[1:2] are sampled on the                                                                                    |

|                                      |        |            |           | active edge of the MTSCCKB.                                                                                                                                               |

| TSCCKA                               | Input  | 123        | A4        | TSCCKA: Transmit Side System Common Clock A                                                                                                                               |

|                                      |        |            |           | TSCCKA is one of the reference clocks for the transmit jitter attenuator DPLL. TSCCKA                                                                                     |

|                                      |        |            |           | can be configured to input the clock as:                                                                                                                                  |

|                                      |        |            |           | 1. 16.384MHz clock;                                                                                                                                                       |

|                                      |        |            |           | 2. Line rate: 2.048MHz (for E1) or 1.544MHz (for T1); 3. Nx8KHz (N is from 1 to 256) so long as TSCCKA is a jitter-free clock.                                            |

|                                      |        |            |           | The IDT82V2108 can be configured to ignore the TSCCKA and utilize LRCK and TSCCKB                                                                                         |

|                                      |        |            |           | instead. The TSCCKA is replaced by LRCK if line loopback is enabled.                                                                                                      |

| TSCCKB/                              | Input  | 122        | B4        | TSCCKB: Transmit Side System Common Clock B                                                                                                                               |

| MTSCCKB                              | ·      |            |           | In E1 mode, the TSCCKB is a 2.048 or 4.096 MHz clock. In T1/J1 mode, the TSCCKB is a                                                                                      |

|                                      |        |            |           | 1.544 or 2.048 or 4.096 MHz clock.                                                                                                                                        |

|                                      |        |            |           | In Transmit Clock Slave TSFS mode, the TSDn and TSCFS are sampled and the TSFSn                                                                                           |

|                                      |        |            |           | is updated on the active edge of the TSCCKB. In Transmit Clock Slave External Signaling                                                                                   |

|                                      |        |            |           | mode, the TSDn, TSSIGn and TSCFS are sampled on the active edge of the TSCCKB.                                                                                            |

|                                      |        |            |           | MTSCCKB: Multiplexed Transmit Side System Common Clock B                                                                                                                  |

|                                      |        |            |           | When the multiplexed bus structure is configured, MTSCCKB is an 8.192 or 16.384 MHz                                                                                       |

|                                      |        |            |           | reference clock for the transmit system multiplexed bus. The MTSCFS, the MTSD[1:2] and                                                                                    |

|                                      |        |            |           | the MTSSIG[1:2] are sampled on the active edge of the MTSCCKB.                                                                                                            |

|                                                                              |        | Pin                                                            | No.                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------|--------|----------------------------------------------------------------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name                                                                         | Type   | PQFP                                                           | PBGA                                                      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| TSCFS/<br>MTSCFS                                                             | Input  | 121                                                            | C5                                                        | TSCFS: Transmit Side System Common Frame Pulse In Transmit Clock Slave mode, TSCFS is used to frame align all the framers to the system backplane. In E1 mode, the pulse can be configured to indicate the first bit of a Basic Frame, CRC Multi-Frame / Signaling Multi-Frame. In T1/J1 mode, the pulse can be configured to indicate the first bit of SF/ESF. The width of the pulse must be at least 1 TSCCKB cycle wide. The TSCFS is sampled on the active edge of the TSCCKB.  MTSCFS: Multiplexed Transmit Side System Common Frame Pulse When the multiplexed bus structure is configured, MTSCFS is used to frame align the multiplexed frames to the system backplane. The MTSCFS is sampled on the active edge of |

|                                                                              |        |                                                                |                                                           | the MTSCCKB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| LTD[1] LTD[2] LTD[3] LTD[4] LTD[5] LTD[6] LTD[7] LTD[7]                      | Output | 9<br>11<br>13<br>15<br>22<br>24<br>26<br>28                    | D2<br>E3<br>F4<br>E1<br>G3<br>H1<br>J2<br>J3              | LTD[1:8]: Line Transmit Data for Framer 1 ~ 8  These pins output the data stream to line interface units or a higher multiplex interface.  The data on the LTDn is updated on the active edge of the corresponding LTCKn.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| LTCK[1] LTCK[2] LTCK[3] LTCK[4] LTCK[5] LTCK[6] LTCK[7] LTCK[8]              | Output | 10<br>12<br>14<br>16<br>23<br>25<br>27<br>29                   | C1<br>D1<br>F3<br>E2<br>H2<br>H3<br>J1                    | LTCKn: Line Transmit Clock for Framer 1 ~ 8 It is a nominal E1 (2.048MHz) or T1/J1 (1.544MHz) clock. The LTCK can be derived from TSCCKA, TSCCKB, LRCK or XCK. On the active edge of the LTCKn, the corresponding LTDn is updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |