**Subscriber Network Interface Circuit**

Data Sheet

#### Features

- ETS 300-012, CCITT I.430 and ANSI T1.605 S/T interface

- Full-duplex 2B+D, 192 kbit/s transmission

- Link activation/deactivation

- D-channel access contention resolution

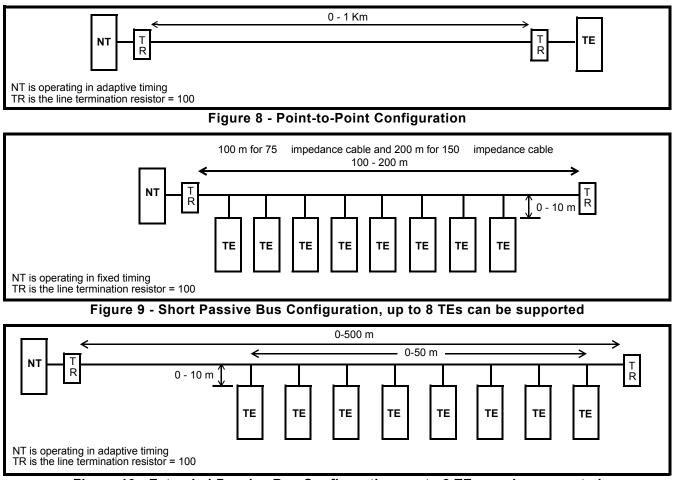

- Point-to-point, point-to-multipoint and star configurations

- Master (NT)/Slave (TE) modes of operation

- Exceeds loop length requirements

- Complete loopback testing capabilities

- On chip HDLC D-channel protocoller

- 8 bit Motorola/Intel microprocessor interface

- · Microprocessor-controlled operation

- Zarlink ST-BUS interface

- Low power CMOS technology

- Single 5 volt power supply

### Applications

- ISDN NT1

- ISDN S or T interface

- ISDN Terminal Adaptor (TA)

- Digital sets (TE1) 4 wire ISDN interface

- Digital PABXs, Digital Line Cards (NT2)

ISSUE 4

November 1997

#### Ordering Information

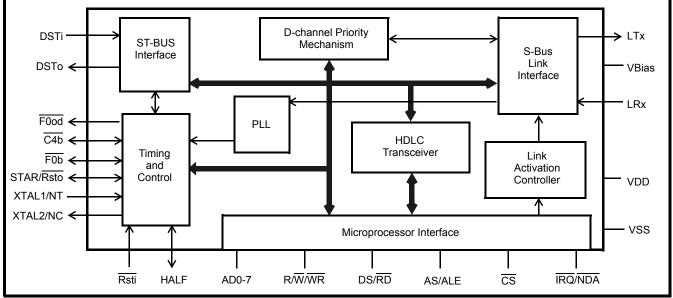

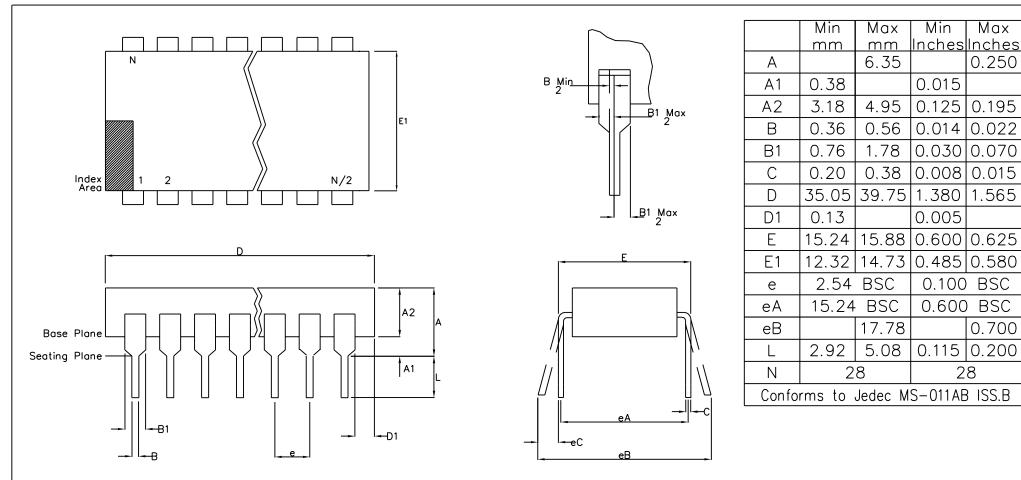

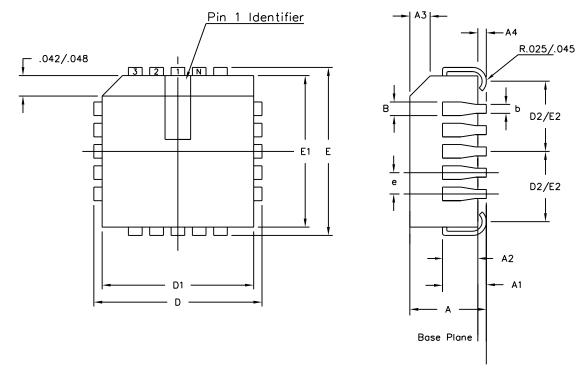

MT8931CE 28 Pin Plastic DIP MT8931CP 44 Pin PLCC -40 ℃ to +85 ℃

### Description

The MT8931C Subscriber Network Interface Circuit (SNIC) implements the ETSI ETS 300-012, CCITT I.430 and ANSI T1.605 Recommendations for the ISDN S and T reference points. Providing point-to-point and point-to-multipoint digital transmission, the SNIC may be used at either end of the subscriber line (NT or TE).

An HDLC D-channel protocoller is included and controlled through a Motorola/Intel microprocessor port.

The MT8931C is fabricated in Zarlink's CMOS process.

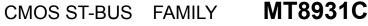

Figure 1 - Functional Block Diagram

## **Pin Description**

| F   | Pin # | N        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|-------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP | PLCC  | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

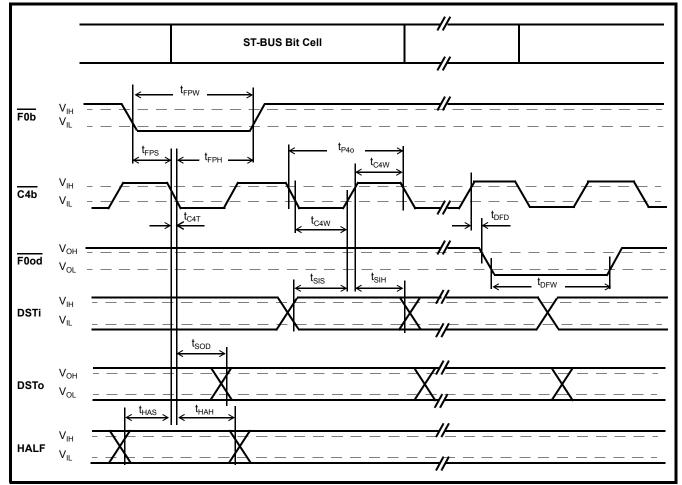

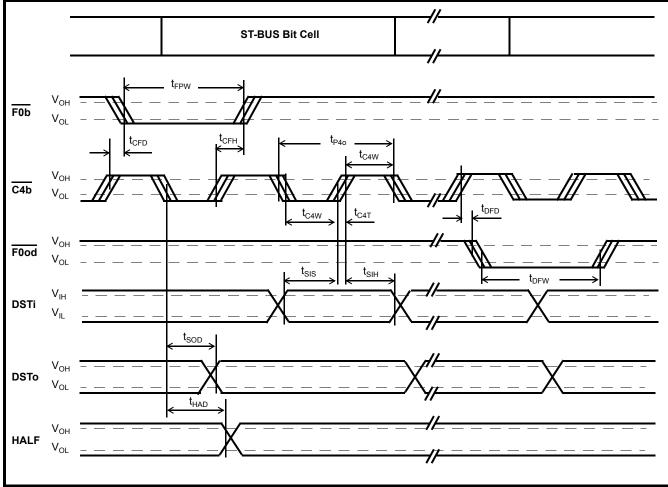

| 1   | 2     | HALF     | <b>HALF Input/Output:</b> this is an input in NT mode and an output in TE mode identifying which half of the S-interface frame is currently being written/read over the ST-BUS (HALF = 0 sampled on the falling edge of C4b within the frame pulse low window, identifies the information to be transmitted/received in the first half of the S-Bus frame while HALF=1 identifies the information to be transmitted/received into the second half of the S-Bus frame). Tying this pin to V <sub>SS</sub> or V <sub>DD</sub> in NT mode will allow the device to free run. This signal can also be accessed from the ST-BUS C-channel. |

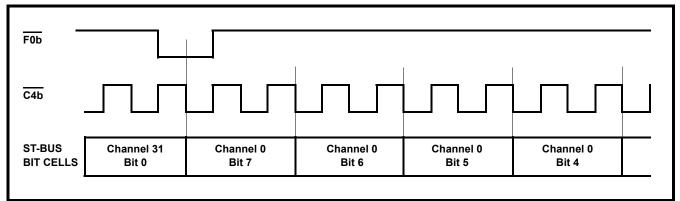

| 2   | 3     | C4b      | <b>4.096 MHz Clock:</b> a 4.096 MHz ST-BUS Data Clock input in NT mode.<br>In TE mode an output 4.096 MHz clock phase-locked to the line data signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

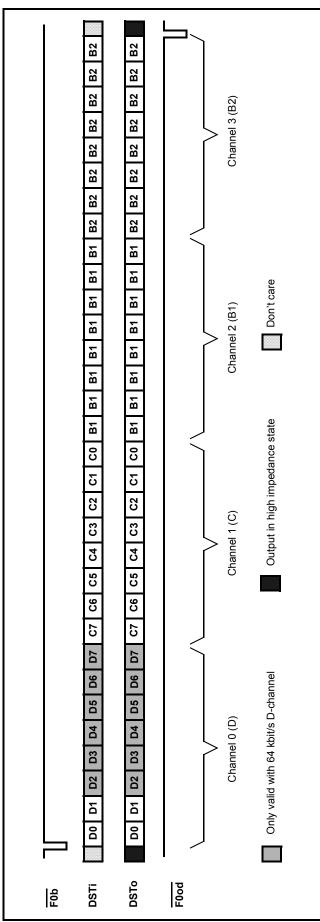

| 3   | 4     | F0b      | <b>Frame Pulse:</b> an active low frame pulse input indicating the beginning of active ST-BUS channel times in NT mode. Frame pulse output in TE mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

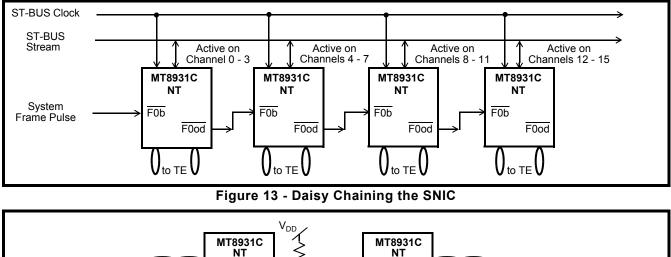

| 4   | 7     | F0od     | <b>Delayed Frame Pulse Output:</b> an active low delayed frame pulse output indicating the end of active ST-BUS channels for this device. Can be used to daisy chain to other ST-BUS devices to share an ST-BUS stream.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5   | 8     | DSTi     | <b>Data ST-BUS Input:</b> a 2048 kbit/s serial PCM/data ST-BUS input with D, C, B1, and B2 channels assigned to the first four timeslots. These channels contain data to be transmitted on the line and chip control information.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6   | 9     | DSTo     | <b>Data ST-BUS Output:</b> a 2048 kbit/s serial PCM/data ST-BUS output with D, C, B1 and B2 channels assigned to the first four timeslots, respectively. The remaining timeslots are placed into high impedance. These channels contain data received from the line and chip status information.                                                                                                                                                                                                                                                                                                                                      |

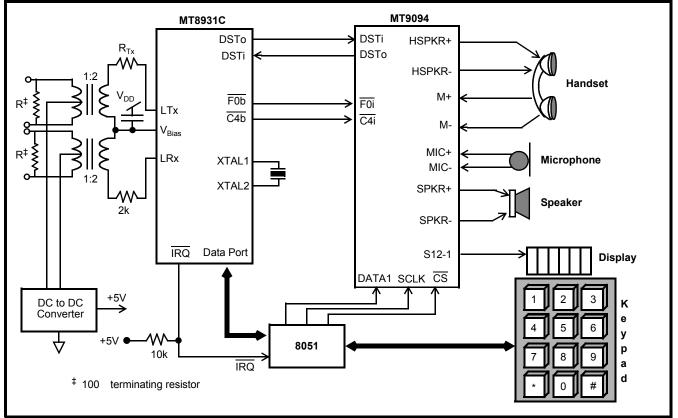

| 7   | 13    | XTAL2/IC | <b>Crystal 2/Internal Connection:</b> in TE mode, XTAL1 and XTAL2 are to be connected to an external 4.096 MHz parallel resonant crystal for the on-chip oscillator. If XTAL1 is connected directly to a 4.096 MHz clock, this pin must be left unconnected. In NT mode, this pin must be left unconnected.                                                                                                                                                                                                                                                                                                                           |

| 8   | 14    | XTAL1/NT | <b>Crystal 1/Network Termination Mode Select Input:</b> for TE mode mode selection, a 4.096 MHz crystal is to be connected between the XTAL1 and XTAL2 pins, or a 4.096 MHz clock can be connected directly to XTAL1. For NT mode selection, this pin must be tied to VDD. A pull-up resistor is needed when driven by a TTL device.                                                                                                                                                                                                                                                                                                  |

## Pin Description (continued)

| F         | Pin #                                                    | Nomo            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------|----------------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP       | PLCC                                                     | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

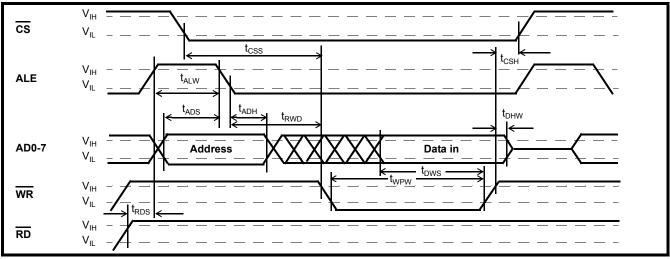

| 9         | 16                                                       | R/W/WR          | <b>Read/Write or Write Input:</b> defines the data <u>bus</u> transfer as a read ( $R/W=1$ ) or a write ( $R/W=0$ ) in Motorola bus mode. Redefined to WR in Intel bus mode.                                                                                                                                                                                                                                                                                                                                                                       |

| 10        | 17                                                       | DS/RD           | <b>Data Strobe/Read Input:</b> active high input indicates to the SNIC that valid data is on the bus during a write operation or that the SNI <u>C must output data during a read operation in Motorola bus mode</u> . Redefined to RD in Intel bus mode.                                                                                                                                                                                                                                                                                          |

| 11        | 19                                                       | AS/ALE          | Address Strobe/Address Latch Enable Input: in Motorola bus mode the falling edge is used to strobe the address into the SNIC during microprocessor access. Redefined to ALE in Intel bus mode.                                                                                                                                                                                                                                                                                                                                                     |

| 12        | 20                                                       | CS              | Chip Select Input: active low, used to select the SNIC for microprocessor access.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 13        | 21                                                       | IRQ<br>NDA      | <b>Interrupt Request (Open Drain Output):</b> an output indicating an unmasked HDLC interrupt. The interrupt remains active until the microprocessor clears it by reading the HDLC Interrupt Status Register. This interrupt source is enabled with B2=0 of Master Control Register.<br><b>New Data Available (Open Drain Output):</b> an active low output signal indicating availability of new data from the S-Bus. This signal is selected with B2=1 of Master Control Register. This pin must be tied to V <sub>DD</sub> with a 10k resistor. |

| 14        | 22                                                       | V <sub>ss</sub> | Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 15-<br>22 | 24-26,<br>30-32,<br>34-35                                | AD0-7           | <b>Bidirectional Address/Data Bus:</b> electrically and logically compatible to either Intel or Motorola micro-bus specifications. If DS/RD is low on the rising edge of AS/ALE then the chip operates to Motorola specs. If DS/RD is high on the rising edge of AS/ALE Intel mode is selected. Taking Rsti low sets Motorola mode.                                                                                                                                                                                                                |

| 23        | 37                                                       | Rsti            | <b>Reset Input:</b> Schmitt trigger reset input. If '0', sets all control registers to the default conditions, resets activation state machines to the deactivated state, resets HDLC, clears the HDLC FIFO's. Sets the microport to Motorola bus mode.                                                                                                                                                                                                                                                                                            |

| 24        | 38                                                       | STAR/Rsto       | <b>Star/Reset (Open Drain Output):</b> 192kbit/s Rx data output fixed relative to the ST-BUS timebase. A group of NTs, in fixed timing mode, can be wire or'ed together to create a Star configuration. Active low reset output in TE mode indicating 128 consecutive marks have been received. Can be connected directly to Rsti to allow NT to reset all TEs on the bus. This pin must be tied to $V_{DD}$ with a 10 k resistor.                                                                                                                 |

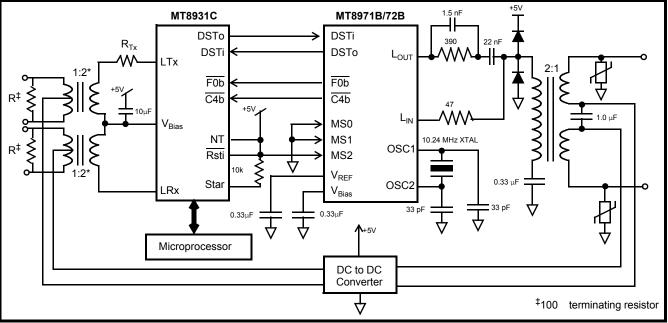

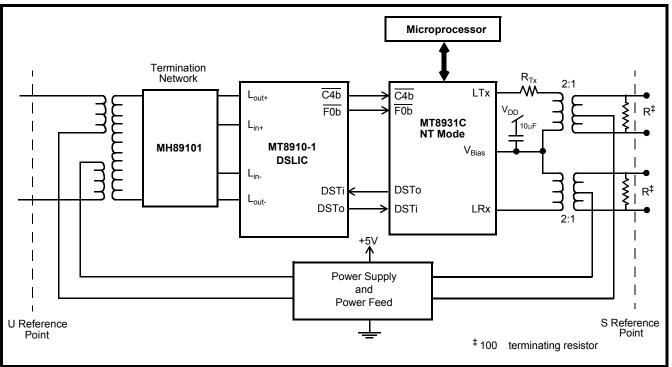

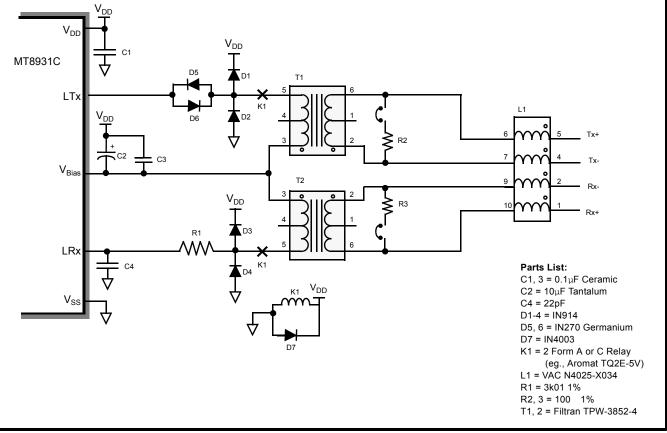

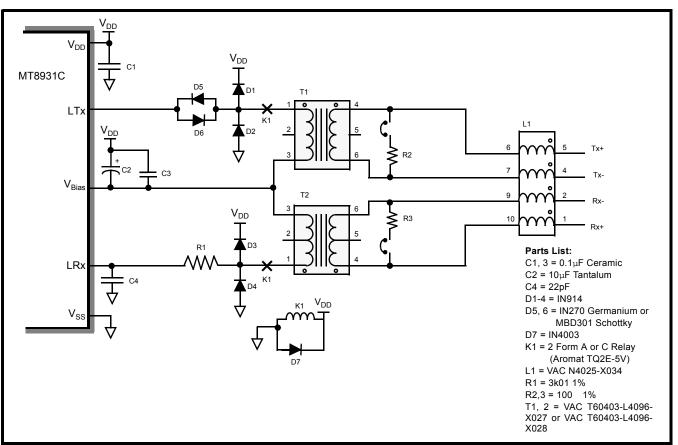

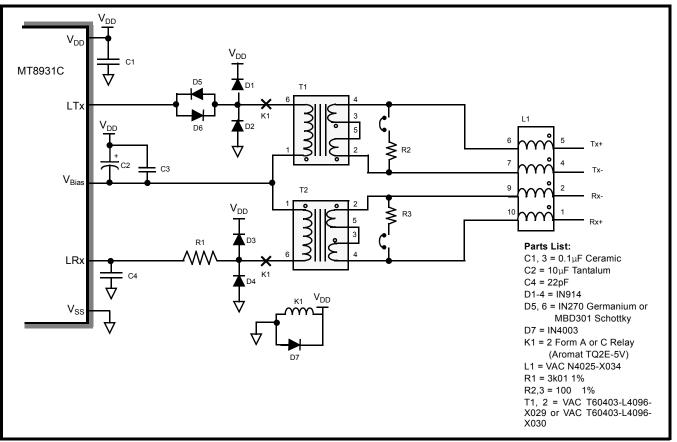

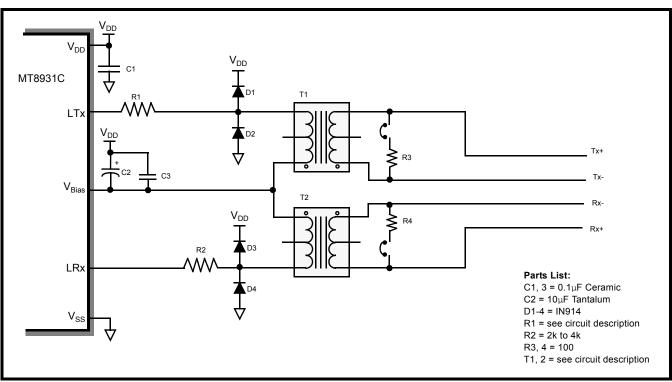

| 25        | 40                                                       | LRx             | <b>Receive Line Signal Input:</b> this is a high impedance input for the pseudoternary line signal to be connected to the line through a 2:1 ratio transformer. See Figures 20 and 21. A DC bias level on this input equal to $V_{\text{Bias}}$ must be maintained.                                                                                                                                                                                                                                                                                |

| 26        | 42                                                       | LTx             | <b>Transmit Line Signal Output:</b> this is a current source output designed to drive a nominal 50 ohm line through a 2:1 ratio transformer. See Figures 20 and 21.                                                                                                                                                                                                                                                                                                                                                                                |

| 27        | 43                                                       | $V_{Bias}$      | <b>Bias Voltage:</b> analog ground for Tx and Rx transformers. This pin must be decoupled to $V_{DD}$ through a 10µF capacitor with good high frequency characteristics.                                                                                                                                                                                                                                                                                                                                                                           |

| 28        | 44                                                       | $V_{\text{DD}}$ | Power Supply Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|           | 1,5-6,10-<br>12,15,18,<br>23,27-29,<br>33, 36,<br>39, 41 | NC              | No Connection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## **Functional Description**

The MT8931C Subscriber Network Interface Circuit (SNIC) is a multifunction transceiver providing a complete interface to the S/T Reference Point as specified in ETS 300-012, CCITT Recommendation I.430 and ANSI T1.605. Implementing both point-to-point and point-to-multipoint voice/data transmission, the SNIC may be used at either end of the digital subscriber loop. A programmable digital interface allows the MT8931C to be configured as a Network Termination (NT) or as a Terminal Equipment (TE) device.

The SNIC supports 192 kbit/s (2B+D + overhead) full duplex data transmission on a 4-wire balanced transmission line. Transmission capability for both B and D channels, as well as related timing and synchronization functions, are provided on chip. The signalling capability and procedures necessary to enable customer terminals (TEs) to be activated and form the MT8931C's deactivated, part of functionality. The SNIC handles D-channel resource allocation and prioritization for access contention resolution and signalling requirements in passive bus line configurations. Control and status information allows implementation of mainten-ance functions and monitoring of the device and the subscriber loop.

An HDLC transceiver is included on the SNIC for link access protocol handling via the D-channel. Depacketized data is passed to and from the transceiver via the microprocessor port. Two 19 byte deep FIFOs, one for transmit and one for receive, are provided to buffer the data. The HDLC block can be set up to transmit or receive to/from either the S-interface port or the ST-BUS port. Further, the transmit destination and receive source can be independently selected, e.g., transmit to S-interface while receiving from ST-BUS. The transmit and receive paths can be separately enabled or disabled. Both, one and two byte address recognition is supported by the SNIC. A transparent mode allows data to be passed directly to the D channel without being packetized.

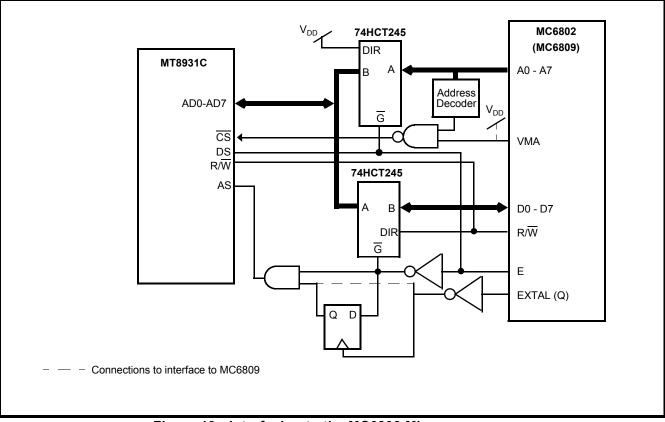

A block diagram of the MT8931C is shown in Figure 1. The SNIC has three interface ports: a 4-wire CCITT compatible S/T interface (subscriber loop interface), a 2048 kbit/s ST-BUS serial port, and a general purpose parallel microprocessor port. This 8-bit parallel port is compatible with both Motorola or Intel microprocessor bus signals and timing.

The three major blocks of the MT8931C, consisting of the system serial interface (ST-BUS), HDLC transceiver, and the digital subscriber loop interface (S-interface) are interconnected by high speed data busses. Data sent to and received from the S-interface port (B1, B2 and D channels) can be accessed from either the parallel microprocessor port or the serial ST-BUS port. This is also true for SNIC control and status information (C-channel). Depacketized D-channel information to and from the HDLC section can only be accessed through the parallel microprocessor port.

#### S-Bus Interface

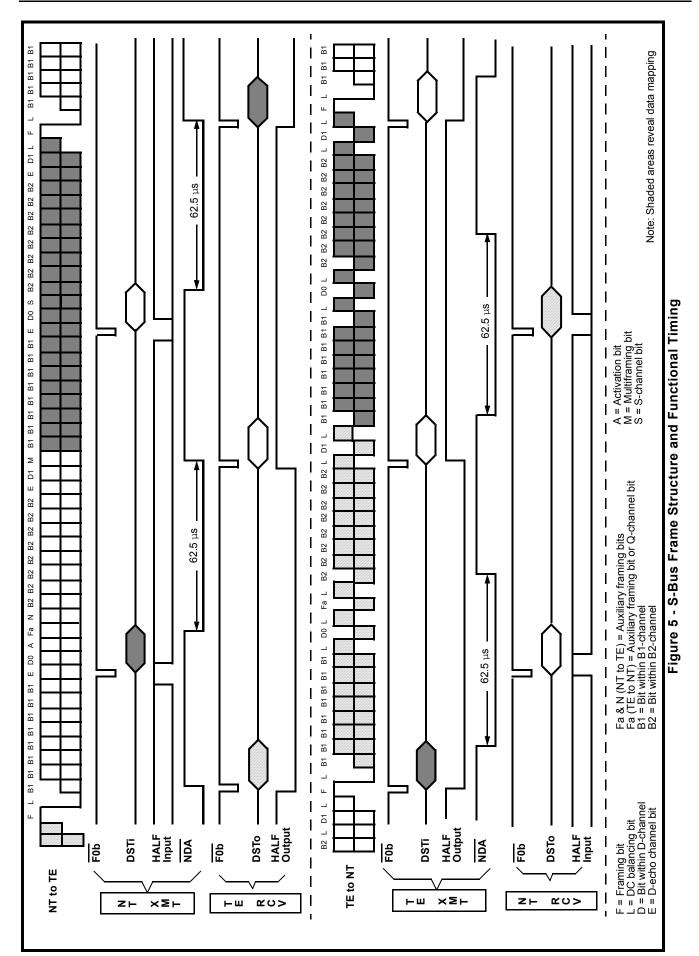

The S-Bus is a four wire, full duplex, time division multiplexed transmission facility which exchanges information at 192 kbit/s rate including two 64 kbit/s PCM voice or data channels, a 16 kbit/s signalling channel and 48 kbit/s for synchronization and overhead. The relative position of these channels with respect to the ST-BUS is shown in Figures 4 and 5.

The SNIC makes use of the first four channels on the ST-BUS to transmit and receive control/status and data to and from the S-interface port. These are the B, D and C-channels (see Figure 4).

Figure 3 - SNIC Pin Connections

The B1 and B2 channels each have a bandwidth of 64 kbit/s and are used to carry PCM voice or data across the network.

The D-channel is primarily intended to carry signalling information for circuit switching through the ISDN network. The SNIC provides the capability of having a 16 kbit/s or full 64 kbit/s D-channel by allocating the B1-channel timeslot to the D-channel. Access to the depacketized D-channel is only granted through the parallel microprocessor port.

The C-channel provides a means for the system to control and monitor the functionality of the SNIC. This control/status channel is accessed by the system through the ST-BUS or microprocessor port. The C-channel provides access to two registers which provide complete control over the state activation machine, the D-channel priority mechanism as well as the various maintenance functions. A detailed description of these registers is discussed in the microprocessor port interface.

#### Line Code

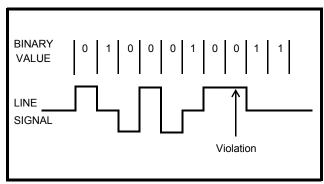

The line code used on the S-interface is a Pseudo ternary code with 100% pulse width as seen in Figure 5 below. Binary zeros are represented as marks on the line and successive marks will alternate in polarity.

Figure 5 - Alternate Zero Inversion Line Code

A mark which does not adhere to the alternating polarity is known as a bipolar violation.

## MT8931C

Data Sheet

#### Framing

The valid frame structure transmitted by the NT and TE contains the following (refer Fig. 6):

NT to TE:

- Framing bit (F)

- B1 and B2 channels (B1,B2)

- DC balancing bits (L)

- D-channel bits (D0, D1)

- Auxiliary framing and N bit (Fa, N), N=Fa

- Activation bit (A)

- D-echo channel bits (E)

- Multiframing bit (M)

- S-channel bit

TE to NT:

- Framing bit (F)

- B1 and B2 channels (B1, B2)

- DC balancing bits (L)

- D-channel bits (D0, D1)

- Auxiliary framing bit (Fa) or Q-channel bit

The framing mechanism on the S-interface makes use of line code violations to identify frame boundaries. The F-bit violates the alternating line code sequence to allow for quick identification of the frame boundaries. To secure the frame alignment, the next mark following the frame balancing bit (L) will also produce a line code violation. If the data following the balancing bit is all binary ones, the zero in the auxiliary framing bit (Fa) or N-bit (for the direction NT to TE) will provide successive violations to ensure that the 14 bit criterion (13 bit criterion in the direction TE to NT) specified in Recommendations I.430 and T1.605 is satisfied. If the B1-channel is not all binary ones, the first zero following the L-bit will violate the line code sequence, thus allowing subsequent marks to alternate without bipolar violations.

The Fa and N bits can also be used to identify a multiframe structure (when this is done, the 14 bit criterion may not be met). This multiframe structure will make provisions for a low speed signalling channel to be used in the TE to NT direction (Q-channel). It will consist of a five frame multiframe which can be identified by the binary inversion of the Fa and N-bit on the first frame and consequently on every fifth frame of the multiframe. Upon detection of the multiframe signal, the TE will replace the next Fa-bit to be transmitted with the Q-bit.

The DC balancing bits (L) are used to remove any DC content from the line. The balancing bit will be a mark if the number of preceding marks up to the previous balancing bit is odd. If the number of marks is even, the L-bit will be a space.

The A-bit is used by the NT during line activation procedures (refer to state activation diagrams). The state of the A-bit will advise the TE if the NT has achieved synchronization.

The E-bit is the D-echo channel. The NT will reflect the binary value of the received D-channel into the E-bits. This is used to establish the access contention resolution in a point-to-multipoint configuration. This is described in more detail in the section of the D-channel priority mechanism.

The M-bit is a second level of multiframing which is used for structuring the Q-bits. The frame with Mbit=1 identifies frame #1 in the twenty frame multiframe. The Q-channel is then received as shown in Table 1. All synchronization with the multiframes must be performed externally.

| FRAME # | Q-BIT | M-BIT |

|---------|-------|-------|

| 1       | Q1    | 1     |

| 6       | Q2    | 0     |

| 11      | Q3    | 0     |

| 16      | Q4    | 0     |

Table 1. Q-channel Allocation

#### Bit Order

When using the B-channels for PCM voice, the first bit to be transmitted on the S-Bus should be the sign bit. This complies with the existing telecom standards which transmit PCM voice as most significant bit first. However, if the B-channels are to carry data, the bit ordering must be reversed to comply with the existing datacom standards (i.e., least significant bit first).

These contradicting standards place a restriction on all information input and output through the serial and parallel ports. Information transferred through the serial ports, will maintain the integrity of the bit order. Data sent to either serial port from the parallel port, will transmit the least significant bit first. Therefore, a PCM byte input through the microprocessor port must be reordered to have the sign bit as the least significant bit.

When the microprocessor reads D, B1 or B2 channel data of either ST-BUS or S-bus serial port, the least significant bit read is the first bit received on that particular channel of either serial port.

The D-channel received on the serial ST-BUS ports must be ordered with the least significant bit first as shown in Figure 4. This also applies to the D-channel directed to the ST-BUS from the microprocessor port. The C-channel bit mapping from the parallel port to the ST-BUS is organized such that the most significant bit is transmitted or received first.

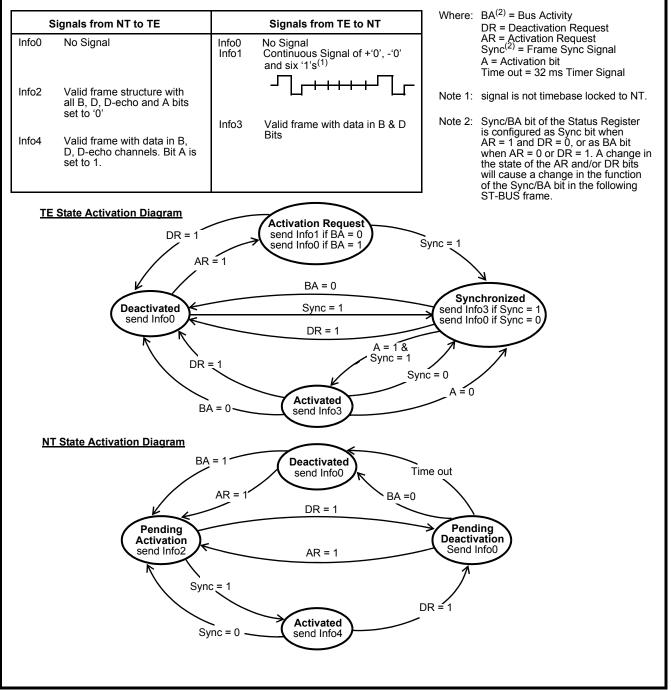

#### State Activation

The state activation controller activates or deactivates the SNIC in response to line activity or external command. The controller is completely hardware driven and need not be initialized by the microprocessor. The state diagram for initialization is shown in Figure 7.

The protocol used by the state activation controller is defined as follows:

- 1) In the deactivated state, neither the NT nor TE assert a signal on the line (Info0).

- If the TE wants to initiate activation, it must begin transmitting a continuous signal consisting of a positive zero, a negative zero followed by six ones (Info1).

- 3) Once the NT has detected Info1, it begins to transmit Info2 which consists of an S-Bus frame

Figure 7 - Link Activation Protocol, State Diagram

with zeros in the B and D-channel and the activation bit (A-bit) set to zero.

- 4) As soon as the TE synchronizes to Info2, it responds with a valid S-Bus frame with data in the B1, B2 and D-channel (Info3).

- 5) The NT will then transmit a valid frame with data in the B1, B2 and D-channel. It will also set the activation bit (A) to binary one once synchronization to Info3 is achieved.

If the NT wishes to initiate the activation, steps 2 and 3 are ignored and the NT starts sending Info2. To initiate a deactivation, either end begins to send Info0 (Idle line).

#### **D-channel Priority Mechanism**

The SNIC contains a hardware priority mechanism for D-channel contention resolution. All TEs connected in a point-to-multipoint configuration are allocated the D-channel using a systematic approach. Allocation of the D-channel is accomplished by monitoring the D-echo channel (E-bit) and incrementing the D-channel priority counter with every consecutive one echoed back in the E bit. Any zero found on the D-echo channel will reset the priority counter.

There are two classes of priority within the SNIC, one user accessible and the other being strictly internal. The user accessible priority selects the class of operation and has precedence over the internal priority. The latter (internal priority), will select the level of priority within each class (i.e., the internal priority is a subsection of the user accessible priority). User accessible priority selects the terminal count as 8/9 or 10/11 consecutive ones on the E-bit (8 being high priority while 10 being low priority). The internal priority selects the terminal between 8 or 9 for high class and 10 or 11 for low class. The first terminal equipment to attain the E-bit priority count will immediately take control of the D-channel by sending the opening flag. If more than one terminal has the same priority, all but one of them will eventually detect a collision. The TEs that detect a collision will immediately stop trans-mitting on the Dchannel, generate an interrupt through the Dcoll bit, reset the DCack bit on the next frame pulse, and restart the counting process. The remainder of the packet in the Tx FIFO is ignored.

Figure 10 - Extended Passive Bus Configuration, up to 8 TEs can be supported

## MT8931C

After successfully completing a transmission, the internal priority level is reduced from high to low. The internal priority will only be increased once the terminal count for the respective level of priority has been achieved. (e.g., if TE has high priority internally and externally, it must count 8 consecutive ones in the D-echo channel. Once this is achieved and successful transmission has been completed, the internal priority is reduced to a lower level (i.e., count = 9). This terminal will not return to the high internal priority until 9 consecutive ones have been monitored on the D-echo channel).

#### Line Wiring Configuration

The MT8931C can interface to any of the three wiring configurations which are specified by the CCITT Recommendation I.430 and ANSI T1.605 (refer to Figures 8 to 10). These consist of a point-to-point or one of the two point-to- multipoint configurations (i.e., short passive bus or the extended passive bus). The selection of line configurations is performed using the timing bit (B4 of NT Mode Control Register).

For the short passive bus, TE devices are connected at random points along the cable. However, for the extended passive bus all connection points are grouped at the far end of the cable from the NT. For an NT SNIC in fixed timing mode, the VCO and Rx filters/peak detectors are disabled and the threshold voltage is fixed. However, for a TE SNIC or an NT SNIC (in adaptive timing mode), the VCO and Rx filters/peak detectors are enabled. In this manner, the device can compensate for variable round trip delays and line attenuation using a threshold voltage set to a fixed percentage of the pulse peak amplitude.

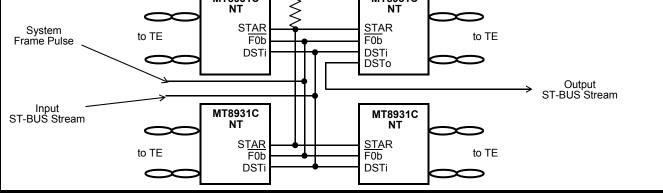

Another operation can be implemented using the SNIC in the star configuration as shown in Figure 14. This mode allows multiple NTs, with physically independent S-Busses, to share a common input source and transfer information down the S-Bus to all TEs . All NT devices connected into the star will receive the information transmitted by all TEs on all branches of the star, exactly as if they were on the same physical S-Bus. All NTs in the star configuration must be operating in fixed timing mode. Refer to the description of the star configuration in the ST-BUS section.

The SNIC has one last mode of operation called the NT slave mode. This has the effect of operating the SNIC in network termination mode (XTAL1/NT pin = 1) but having the frame structure and registers description defined by the TE mode. This can be used where multiple subscriber loops must carry a fixed phase relation between each line. A typical

Figure 12 - Clock & Frame Alignment for ST-BUS Streams

## Data Sheet

situation is when the system is trying to synchronize two nodes of a synchronous network. This allows multiple TEs to share a common ST-BUS timebase. The synchronization of the loops is established by using the clock signals produced by a local TE as an input timing source to the NT slave.

#### Adaptive Timing Operation

On power-up or after a reset, the SNIC in NT mode is set to operate in fixed timing. To switch to adaptive timing, the user should:

- 1) set the DR bit to 1

- 2) set the Timing bit to 1 in the C-channel Control Register

- 3) wait for 100 ms period

- 4) proceed in using the AR and DR bits as desired

Switching from adaptive timing mode is completed by resetting the Timing bit.

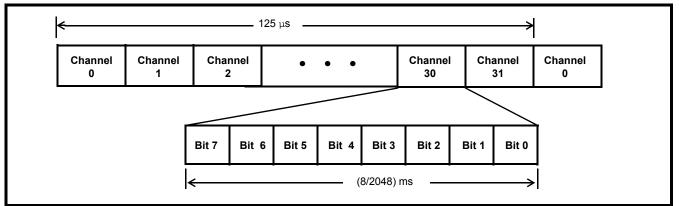

### **ST-BUS Interface**

The ST-BUS is a synchronous time division multiplexed serial bussing scheme with data streams operating at 2048 kbit/s configured as 32, 64 kbit/s channels (refer to Fig. 11). Synchroni-zation of the data transfer is provided from a frame pulse which identifies the frame boundaries and repeats at an 8 kHz rate. Figure 4 shows how the frame pulse (F0b) defines the ST-BUS frame boundaries. All data is clocked into the device on the rising edge of the 4096 kHz clock (C4b) three quarters of the way into the bit cell, while data is clocked out on the falling edge of the 4096 kHz clock at the start of the bit cell.

All timing signals (i.e. F0b & C4b) are identified as bidirectional (denoted by the terminating b). The I/O configuration of these pins is controlled by the mode of operation (NT or TE). In the NT mode, all synchronized signals are supplied from an external source and the SNIC uses this timing while transferring information to and from the S or ST-BUS. In the TE mode, an on-board analog phase-locked loop extracts timing from the received data on the <u>S-Bus</u> and generates the system 4096 kHz (C4b) and frame pulse (F0b). The analog phase-locked loop also maintains proper phase relation between the timing signals as well as

Figure 14 - NT in Star Configuration

## MT8931C

filtering out jitter which may be present on the received line port.

The SNIC uses the first four channels on the ST-BUS (as shown in Figure 4). To simplify the distribution of the serial stream, the SNIC provides a delayed frame pulse (F0od) to eliminate the need for a channel assignment circuit. This signal is used to drive subsequent devices in the daisy chain (refer Figure 13). In this type of arrangement, only the first SNIC in the chain will receive the system frame pulse (F0b) with the following devices receiving its predecessor's delayed output frame pulse (F0od).

The SNIC makes efficient use of its TDM bus through the Star configuration. It does so by sharing four common ST-BUS channels to multiple NT devices. Up to eight SNICs in NT mode with physically independent S-Busses can be connected in parallel to realize a star configuration (as shown in Figure 14). All devices connected into the star will carry the same input, thus information is sent to all TEs simultaneously. The 2B+D data received from every TE is transmitted to all NTs through the STAR pin. Consequently, all the DSTo streams will carry identical 2B+D data reflecting what is being transmitted by the various TEs. The flow of data in the direction of S-Bus to ST-BUS is transparent to the SNIC, regardless of the state machine status. On the other hand, the flow of data in the direction of ST-BUS to S-Bus becomes transparent only after the state machine is in the active state (IS0, IS1=1,1), in case of an NT, or in the synchronization state (IS0, IS1=1), in case of a TE.

#### Microprocessor/Control Interface

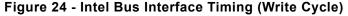

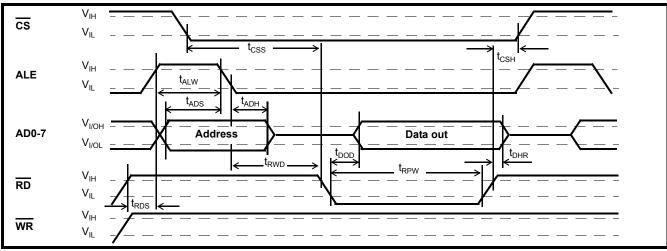

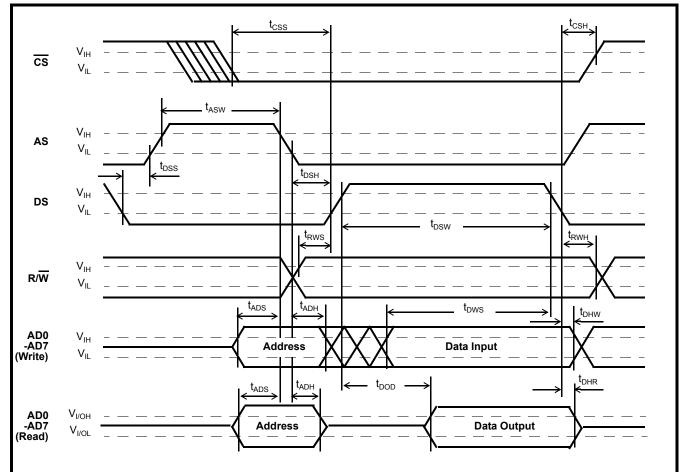

The microprocessor port is compatible with either Motorola or Intel multiplexed bus signals and timing. The MOTEL circuit (**MO**torola and <u>InTEL</u> Compatible bus) uses the level of the DS/RD pin at the rising edge of AS/ALE to select the appropriate bus timing. If DS/RD is low at the rising edge of AS/ALE (refer to Figure 26) then Motorola bus timing is selected. Conversely, if DS/ RD is high at the rising edge of AS/ALE (refer to Figures 24 & 25), then Intel bus timing is selected. This has the effect of redefining the microprocessor port transparently to the user.

The user has the option of writing to the C-channel Control or Diagnostic Register through the parallel port interface or through the C-channel on DSTi. Bit 0 of the Master Control Register provides this option.

|   | Address Lines |    |    |    |            | Write                                | Read                           |

|---|---------------|----|----|----|------------|--------------------------------------|--------------------------------|

|   | A4            | A3 | A2 | A1 | <b>A</b> 0 | Wille                                | Neau                           |

|   | 0             | 0  | 0  | 0  | 0          | Master Control Register              | verify                         |

| Α | 0             | 0  | 0  | 0  | 1          | ST-BUS Control Register              | verify                         |

| S | 0             | 0  | 0  | 1  | 0          | HDLC Control Register 1              | verify                         |

| Y | 0             | 0  | 0  | 1  | 1          | HDLC Control Register 2              | HDLC Status Register           |

| Ν | 0             | 0  | 1  | 0  | 0          | HDLC Interrupt Mask Register         | HDLC Interrupt Status Register |

| С | 0             | 0  | 1  | 0  | 1          | HDLC Tx FIFO                         | HDLC Rx FIFO                   |

|   | 0             | 0  | 1  | 1  | 0          | HDLC Address Byte #1 Register        | verify                         |

|   | 0             | 0  | 1  | 1  | 1          | HDLC Address Byte #2 Register        | verify                         |

|   | 0             | 1  | 0  | 0  | 0          | C-channel Control Register           |                                |

|   | 0             | 1  | 0  | 0  | 1          |                                      | C-channel Status Register      |

|   | 1             | 0  | 0  | 0  | 0          | Control Register 1                   | Not Available                  |

|   | 1             | 0  | 0  | 1  | 0          | Not Available Master Status Register |                                |

|   | 0             | 1  | 0  | 0  | 0          |                                      | DSTi C-channel                 |

|   | 0             | 1  | 0  | 0  | 1          | DSTo C-channel                       |                                |

| S | 0             | 1  | 0  | 1  | 0          | S-Bus Tx D-channel                   | DSTi D-channel                 |

| Y | 0             | 1  | 0  | 1  | 1          | DSTo D-channel                       | S-Bus Rx D-channel             |

| Ν | 0             | 1  | 1  | 0  | 0          | S-Bus Tx B1-channel                  | DSTi B1-channel                |

| С | 0             | 1  | 1  | 0  | 1          | DSTo B1-channel                      | S-Bus Rx B1-channel            |

|   | 0             | 1  | 1  | 1  | 0          | S-Bus Tx B2-channel                  | DSTi B2-channel                |

|   | 0             | 1  | 1  | 1  | 1          | DSTo B2-channel                      | S-Bus Rx B2-channel            |

Table 2. SNIC Address Map

## Data Sheet

The parallel port on the SNIC allows complete control of the HDLC transceiver and access to all data, control and status registers. Reading these registers allows the microprocessor to monitor incoming data on the S or ST-BUS without interrupting the normal data flow.

Some registers are classified as asynchronous and others as synchronous. Synchronous registers are single-buffered and require synchronous access. Not all the synchronous registers have the same access times, but all can be accessed synchronously in the time during which the NDA signal is low (refer to Fig. 5). Therefore, it is recommended that the user make use of the NDA signal to access these registers. Since the synchronous registers use common circuitry, it is essential that the register be read before being written. This sequence is important as a write cycle will overwrite the last data received. These parallel accesses must be refreshed every frame. Asynchronous registers, on the other hand, can be accessed at any time.

The data in TE or NT Mode Status Register, depending upon the mode selected, is always sent out on the C-channel of DSTo. However, in microprocessor control mode the user can overwrite this data by writing to the DSTo C-channel Register. This access can be done anytime outside the frame pulse interval of the ST-BUS frame. Data written in the current ST-BUS frame will only appear in the Cchannel of the following frame.

The least significant bit (B0) of the C-channel Register, selects between the control register or the diagnostic register. Setting the B0 of the C-channel Register to '0' allow access to the control register. Setting the LSB of the C-channel Register to '1' allow access to the diagnostic register. The interpretation of each register is defined in Tables 13 and 14 for NT mode or Tables 16 and 17 for the TE mode.

It is important to note that in TE mode, the C-channel Diagnostic Register should be cleared while the device is not in the active state (IS0, IS1 1,1). This is accomplished by setting the ClrDia bit of the Cchannel Control Register to 1 until the device is activated. In serial control mode, the C-channel on the ST-BUS is loaded into the C-channel Control Register in every ST-BUS frame; the user should make sure that a 1 is written to the ClrDia bit in every frame. However, in parallel control mode the user needs to set the ClrDia bit only once to keep the Diagnostic Register cleared. Once full activation is achieved the Diagnostic Register can be written to in order to enable the various test functions.

#### **HDLC Transceiver**

The HDLC Transceiver handles the bit oriented protocol structure and formats the D-channel as per level 2 of the X.25 packet switching protocol defined by CCITT. It transmits and receives the packetized data (information or control) serially in a format shown in Figure 15, while providing data transparency by zero insertion and deletion. It generates and detects the flags, various link channel states and the abort sequence. Further, it provides a cyclic redundancy check on the data packets using the CCITT defined polynomial. In addition, it can recognize a single byte, dual byte or an all call address in the received frame. There is also a provision to disable the protocol functions and provide transparent access to either serial port through the microprocessor port. Other features provided by the HDLC include, independent port selection for transmit and received data (e.g. transmit on S-Bus and receive from ST-BUS), selectable 16 or 64 kbit/s D-channel as well as an HDLC loopback from the transmit to the receive port. These features are enabled through the HDLC control registers (see Tables 6 and 7).

#### HDLC Frame Format

All frames start with an opening flag and end with a closing flag as shown in Figure 15. Between these two flags, a frame contains the data and the frame check sequence (FCS).

| FLAG | DATA FIELD | FCS   | FLAG |

|------|------------|-------|------|

| One  | n Bytes    | Two   | One  |

| Byte | (n 2)      | Bytes | Byte |

Figure 15 - Frame Format

#### i) Flag

The flag is a unique pattern of 8 bits (0111110) defining the frame boundary. The transmit section generates the flags and appends them automatically to the frame to be transmitted. The receive section searches the incoming packets for flags on a bit-by-bit basis and establishes frame synchronization. The flags are used only to identify and synchronize the received frame and are not transferred to the FIFO.

#### ii) Data

The data field refers to the Address, Control and Information fields defined in the CCITT recommendations. A valid frame should have a data field of at least 16 bits. The first and second byte in the data field is the address of the frame.

#### iii) Frame Check Sequence (FCS)

The 16 bits following the data field are the frame check sequence bits. The generator polynomial is: 16 + 12 + 5

$$G(x)=x^{16}+x^{12}+x^{5}+1$$

The transmitter calculates the FCS on all bits of the data field and transmits the complement of the FCS with most significant bit first. The receiver performs a similar computation on all bits of the received data but also includes the FCS field. The generating polynomial will assure that if the integrity of of the transmitted data was maintained, the remainder will have a consistent pattern and this can be used to identify, with high probability, any bit errors occurred during transmission. The error status of the received packet is indicated by B7 and B6 bits in the HDLC Status Register.

#### iv) Zero Insertion and Deletion

The transmitter, while sending either data from the FIFO or the 16 bits FCS, checks the transmission on a bit-by-bit basis and inserts a ZERO after every sequence of five contiguous ONEs (including the last five bits of FCS) to ensure that the flag sequence is not imitated. Similarly the receiver examines the incoming frame content and discards any ZERO directly following the five contiguous ONEs.

#### v) Abort

The transmitter aborts a frame by sending a zero followed by seven consecutive ONEs. The FA bit in the HDLC Control Register 2 along with a write to the HDLC Transmit FIFO enables the transmission of an abort sequence instead of the byte written to the register (to have a valid abort there must be at least two bytes in the packet). On the receive side, a frame abort is defined as seven or more contiguous ONEs occurring after the start flag and before the end flag of a packet. An interrupt can be generated on reception of the abort sequence using FA bit in the HDLC Interrupt Mask/Vector Registers (refer to Tables 9 and 10).

#### Interframe Time Fill

When the HDLC Tranceiver is not sending packets, the transmitter can be in one of two states mentioned below depending on the status of the IFTF bit in the HDLC Control Register 1.

#### i) Idle State

The Idle state is defined as 15 or more contiguous ONEs. When the HDLC Protocoller is observing this condition on the receiving channel, the Idle bit in the HDLC Status Register is set HIGH. On the transmit side, the Protocoller ends the transmission of all ones (idle state) when data is loaded into the transmit FIFO.

CCITT I.430 Specification requires every TE that does not have layer 2 frames to transmit, to send binary ONEs on the D-channel. In this manner, other TEs on the line will have the opportunity to access the D-channel using the priority mechanism circuitry.

#### ii) Flag Fill State

The HDLC Protocoller transmits continuous flags  $(7E_{Hex})$  in Interframe Time Fill state and ends this state when data is loaded into the transmit FIFO. The reception of the interframe time fill will have the effect of setting the idle bit in the HDLC Status Register is set to '0'.

#### HDLC Transmitter

On power up, the HDLC transmitter is disabled and in the idle state. The transmitter is enabled by setting the TxEN bit in the HDLC Control Register 1. To start a packet, the data is written into the 19 byte Transmit FIFO starting with the address field. All the data must be written to the FIFO in a bytewide manner. When the data is detected in the transmit FIFO, the HDLC protocoller will proceed in one of the following ways:

1) If the transmitter is in idle state, the present byte of ones is completely transmitted before sending the opening flag. The data in the transmit FIFO is then transmitted. A TE transmitting on the D-channel will use the contention circuitry described previously in *Dchannel Priority Mechanism* to access this channel. the flag presently being transmitted is used as the opening flag for the packet stored in the transmit FIFO.

If the HDLC transmitter is in transparent data mode, the protocol functions are disabled and the data in the transmit FIFO is transmitted without a framing structure.

To indicate that the particular byte is the last byte of the packet, the EOP bit in the HDLC Control Register 2 must be set before the last byte is written into the transmit FIFO. The EOP bit is cleared automatically when the data byte is written to the FIFO. After the transmission of the last byte in the packet, the frame check sequence (16 bits) is sent followed by a closing flag. If there is any more data in the transmit FIFO, it is immediately sent after the closing flag. That is, the closing flag of a packet is also used as the opening flag the the next packet.

However, CCITT 1.430 and ANSI T1.605 Recommendations state that after the successful transmission of a packet, a TE must lower its priority level within the specified priority class. The user can meet this requirement by loading the Tx FIFO with no more than one packet and then waiting for the DCack bit to go to zero, or for an HDLC interrupt by the TEOP bit in the HDLC Interrupt Status Register, before attempting to load a new packet. If there is no more data to be transmitted, the transmitter assumes the selected link channel state.

During the transmission of either the data or the frame check sequence, the Protocol Controller checks the transmitted information on a bit by bit basis to insert a ZERO after every sequence of five consecutive ONEs. This is required to eliminate the possibility of imitating the opening or closing flag, the idle code or an abort sequence.

#### i) Transmit Underrun

A transmit underrun occurs when the last byte loaded into the transmit FIFO was not 'flagged' with the 'end of packet' (EOP) bit and there are no more bytes in the FIFO. In such a situation, the Protocol Controller transmits the abort sequence (zero and seven ones) and moves to the selected link channel state.

Conversely, in the event that the transmit FIFO is full, any further writes will overwrite the last byte in the Transmit FIFO.

#### ii) Abort Transmission

If it is desired to abort the packet currently being loaded into the transmit FIFO, the next byte written to the FIFO should be 'flagged' to cause this to happen. The FA bit of the HDLC Control Register 2 must be set HIGH, before writing the next byte into the FIFO. This bit is cleared automatically once the byte is written to the Transmit FIFO. When the 'flagged' byte reaches the bottom of the FIFO, a frame abort sequence is sent instead of the byte and the transmitter operation returns to normal. The frame abort sequence is ignored if the packet has less then two bytes.

#### iii) Transparent Data Transfer

The Trans bit (B4) in the HDLC Control Register 2 can be set to provide transparent data transfer by disabling the protocol functions. The transmitter no longer generates the Flag, Abort and Idle sequences nor does it insert the zeros and calculate the FCS.

It should be noted that none of the protocol related status or interrupt bits are applicable in transparent data transfer state. However, the FIFO related status and interrupt bits are pertinent and carry the same meaning as they do while performing the protocol functions.

#### HDLC Receiver

After a reset on power up, the receive section is disabled. Address detection is also disabled when a reset occurs. If address detection is required, the Receiver Address Registers are loaded with the desired address and the ADRec bit in the HDLC Control Register 1 is set HIGH. The receive section can then be enabled by RxEN bit in this same Control Register 1. All HDLC interrupts are masked, thus the desired interrupt signal must be unmasked through the HDLC Interrupt Mask Register. All active interrupts are cleared by reading the HDLC Interrupt Status Register.

#### i) Normal Packets

After initialization as explained above, the serial data starts to be clocked in and the receiver checks for the idle channel and flags. If an idle channel is detected, the 'Idle' bit in the HDLC Status Register is set HIGH. Once a flag is detected, the receiver synchronizes itself in a bytewide manner to the incoming data stream. The receiver keeps resynchronizing to the flags until an incoming packet appears. The incoming packet is examined on a bit-by-bit basis, inserted zeros are deleted, the FCS is calculated and the data bytes are written into the 19 byte Receive FIFO. However, the FCS and other control characters, i.e., flag and abort, are never stored in the Receive FIFO. If the address detection is enabled, the address field following the flag is compared to the bytes in the Receive Address If one byte address recognition is Registers. enabled, the address field is one byte long and it is compared with the six most significant bits in address recognition register 1. If two byte address recognition is enabled, the address field is two bytes long and is compared with the address recognition registers 1 and 2. The address byte can also be recognized if it is an all call address (i.e., seven most significant bits are 1). If a match is not found, the entire packet is ignored, nothing is written to the Receive FIFO and the receiver waits for the next packet. If the active address byte is valid, the packet is received in normal fashion.

All the bytes written to the receive FIFO are flagged with two status bits. The status bits are found in the HDLC status register and indicate whether the byte to be read from the FIFO is the first byte of the packet, the middle of the packet, the last byte of the packet with good FCS or the last byte of the packet with bad FCS. This status indication is valid for the byte which is to be read from the Receive FIFO.

The incoming data is always written to the FIFO in a bytewide manner. However, in the event of data sent not being a multiple of eight bits, the software associated with the receiver should be able to pick the data bits from the LSB positions of the last byte in the received data written to the FIFO. The Protocoller does not provide any indication as to how many bits this might be.

#### ii) Invalid Packets

In TE mode, if there are less than 25 data bits between the opening and closing flags, the packet is considered invalid and the data never enters the receive FIFO (inserted zeros do not form part of the valid bit count). This is true even with data and the abort sequence, the total of which is less than 25 bits. The data packets that are at least 25 bits but less than 32 bits long are also invalid, but not ignored. They are clocked into the receive FIFO and tagged as having bad FCS.

In NT mode, however, all the data packets that are less than 32 bits long are considered invalid. They are clocked into the receive FIFO with "Bad FCS" status.

#### iii) Frame Abort

When a frame abort is received, the EOPD and FA bits in the HDLC Interrupt Status Register are set. The last byte of the aborted packet is written to the FIFO with a status of "Packet Byte". If there is more than one packet in the FIFO, the aborted packet is distinguished by the fact that it has no "Last Byte" status on any of its bytes.

#### iv) Idle Channel

While receiving the idle channel, the idle bit in the HDLC status register remains set.

#### v) Transparent Data Transfer

By setting the Trans bit in the HDLC Control Register 2 to select the transparent data transfer, the receive section will disable the protocol functions like Flag/ Abort/Idle detection, zero deletion, CRC calculation and address comparison. The received data is shifted in from the active port and written to receive FIFO in bytewide format.

It should be noted that none of the protocol related status or interrupt bits are applicable in transparent data transfer state. However, the FIFO related status and interrupt bits are pertinent and carry the same meaning as they do while performing the protocol functions.

#### vi) Receive Overflow

Receive overflow occurs when the receive section attempts to load a byte to an already full receive FIFO. All attempts to write to the full FIFO will be ignored until the receive FIFO is read. When overflow occurs, the rest of the present packet is ignored as the receiver will be disabled until the reception of the next opening flag.

| BIT   | NAME              | DESCRIPTION                                                                                                                                                                                                                                                                                              |

|-------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7    | NA                | A '1' will allow access to Control Register 1 and Master Status Register.<br>A '0' will prevent it.                                                                                                                                                                                                      |

| B6-B3 | NA <sup>(1)</sup> | Keep at '0' for normal operation.                                                                                                                                                                                                                                                                        |

| B2    | IRQ/NDA           | The state of this pin will select the mode of the IRQ/NDA pin.<br>A '0' will enable the IRQ pin for HDLC interrupts.<br>A '1' will enable the New Data Available signal which identifies the access time to the<br>synchronous registers. (If NDA is enabled, the HDLC interrupts are disabled.)         |

| B1    | M/Sen             | A '0' will enable the transmission of the $M^{(2)}$ or S bit as selected in the NT Mode C-channel<br>Register (refer to Table 13). The selection of M or S is determined by the HALF signal<br>(refer to functional timing).<br>A '1' will disable this feature forcing the M and S bits to binary zero. |

| B0    | P/SC              | The Parallel/Serial Control bit selects the source of the control channel. If '0', then the C-channel Register is access through the ST-BUS stream. If '1', then the C-channel Register is accessed through the microprocessor port.                                                                     |

#### Table 3. Master Control Register (Read/Write Add. 00000<sub>B</sub>)

Note 1: These bits have no designated memory space and will read as the last values written to the microprocessor port. Note 2: The transmission of M=1 is used for a second level of multiframing.

| BIT   | NAME  | DESCRIPTION                                                                                                                                                                              |

|-------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7    | NA    | Keep at '0' for normal operation.                                                                                                                                                        |

| B6    | RxDIS | When set to '1', this bit disables the S-Bus signal receiver. It can be used, for example, to force INFO4 to INFO2 transition in the NT state machine while receiving INFO3 from the TE. |

| B5-B0 | NA    | Keep at '0' for normal operation.                                                                                                                                                        |

Table 4. Control Register 1 (Write Add. 10000<sub>B</sub>)

| BIT | NAME                                                                   | DESCRIPTION                                                                                                                                             |  |  |  |

|-----|------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| B7  | CH3i <sup>(3)</sup>                                                    | If '1', then the ST-BUS channel 3 input port is enabled (B2-channel). If '0', then the channel is disabled, and will read $FF_{H}$ .                    |  |  |  |

| B6  | CH2i <sup>(3)</sup>                                                    | If '1', then the ST-BUS channel 2 input port is enabled (B1-channel). If '0', then the channel is disabled, and will read $FF_H$ .                      |  |  |  |

| B5  | CH1i <sup>(3)</sup>                                                    | If '1', then the ST-BUS channel 1 input port is enabled (C-channel). If '0', then the channel is disabled, and will read $00_{\rm H}$ .                 |  |  |  |

| B4  | CH0i <sup>(3)</sup>                                                    | If '1', then the ST-BUS channel 0 input port is enabled (D-channel). If '0', then the channel is disabled, and will read $FF_H$ .                       |  |  |  |

| B3  | CH3o <sup>(3)</sup>                                                    | If '1', then the ST-BUS channel 3 output port is enabled (B2-channel).<br>If '0', then the channel is disabled and it will be placed in High impedance. |  |  |  |

| B2  | CH2o <sup>(3)</sup>                                                    | If '1', then the ST-BUS channel 2 output port is enabled (B1-channel).<br>If '0', then the channel is disabled and it will be placed in High impedance. |  |  |  |

| B1  | CH10 <sup>(3)</sup>                                                    | If '1', then the ST-BUS channel 1 output port is enabled (C-channel).<br>If '0', then the channel is disabled and it will be placed in High impedance   |  |  |  |

| B0  | CH0o <sup>(3)</sup>                                                    | If '1', then the ST-BUS channel 0 output port is enabled (D-channel).<br>If '0', then the channel is disabled and it will be placed in High impedance.  |  |  |  |

|     | Table 5. ST-BUS Control Register (Read/Write Add. 00001 <sub>B</sub> ) |                                                                                                                                                         |  |  |  |

Note 3: All ST-BUS channels are enabled in controllerless mode.

| BIT | NAME     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                       |

|-----|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7  | TxEn     | A '1' enables the HDLC transmitter for the selected D-channel (i.e., ST-BUS or S-Bus).<br>A '0' disables the HDLC transmitter (i.e., an all 1s signal will be sent).                                                                                                                                                                                              |

| B6  | RxEn     | A '1' enables the HDLC receiver for the selected D-channel (i.e., ST-BUS or S-Bus).<br>A '0' disables the HDLC receiver (i.e., an all 1s signal will be received).                                                                                                                                                                                                |

| B5  | ADRec    | If '1', then the address recognition is enabled. This forces the receiver to recognize only those packets having the unique address as programmed in the Receive Address Registers or if the address byte is the All-Call address (all 1s). If '0', then the address recognition is disabled and every valid packet is stored in the received FIFO.               |

| B4  | TxPrtSel | This bit selects the port of the HDLC transmitted D-channel.<br>A'1' selects the S-Bus port. A '0' selects the ST-BUS port.                                                                                                                                                                                                                                       |

| B3  | RxPrtSel | This bit selects the port of the HDLC received D-channel.<br>A '1' selects the S-Bus port. A '0' selects the ST-BUS port.                                                                                                                                                                                                                                         |

| B2  | IFTF     | This bit selects the Inter Frame Time Fill.<br>A '1' selects continuous flags. A '0' selects an all 1's idle state.                                                                                                                                                                                                                                               |

| B1  | NA       | Keep at '0' for normal operation.                                                                                                                                                                                                                                                                                                                                 |

| B0  | HLoop    | A '1' will activate the HDLC loopback where the transmitted D-channel is looped back to the received D-channel <sup>(1)</sup> . In NT mode, the transmission of the packet is not affected. In TE mode, however, the DReq bit of the C-channel Control Register must be set to '1' for the packet to be transmitted to the S-Bus.<br>A '0' disables the loopback. |

#### Table 6. HDLC Control Register 1 (Read/Write Add. 00010<sub>B</sub>)

Note 1: The HDLC receiver must be enabled as well as the designated channel.

| BIT       | NAME               | DESCRIPTION                                                                                                                                                                                                                                                                                                                         |

|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7-B5     | NA                 | Keep at '0' for normal operation.                                                                                                                                                                                                                                                                                                   |

| B4        | Trans              | A '1' will place the HDLC in a transparent mode. This will perform the serial to parallel or parallel to serial conversion without inserting or deleting the opening and closing flags, CRC bytes or zero insertion. The source or destination of the data is determined by the port selection bits in the HDLC Control Register 1. |

| B3        | RxRst              | A transition from '0' to '1' will reset the receive FIFO. This causes the receiver to be disabled until the reception of the next flag. (The status Register will identify the RxFIFO as being empty.) The device resets this bit to '0' immediately after clearing the receive FIFO.                                               |

| B2        | TxRst              | A transition from '0' to '1' will reset the transmit FIFO. This causes the transmitter to clear all data in the TxFIFO. The device resets this bit to '0' immediately after clearing the transmit FIFO.                                                                                                                             |

| B1        | FA <sup>(2)</sup>  | A '1' will 'tag' the next byte written to the transmit FIFO and cause an abort sequence to be transmitted once it reaches the bottom of the FIFO.                                                                                                                                                                                   |

| В0        | EOP <sup>(2)</sup> | A '1' will 'tag' the next byte written to the transmit FIFO and cause an end of packet sequence to be transmitted once it reaches the bottom of the FIFO.                                                                                                                                                                           |

| <u>  </u> |                    | Table 7. HDLC Control Register 2 (Write Add. 00011 <sub>B</sub> )                                                                                                                                                                                                                                                                   |

Note 2: These bits will be reset after a write to the TxFIFO

| BIT   | NAME             | DESCRIPTION                                                                                                                                                                                                                                                                          |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7-B6 | RxByte<br>Status | These two bits indicate the status of the received byte which is ready to be read from the<br>19 deep received FIFO. The status is encoded as follows:<br><u>B7 - B6</u><br>0 - 0 - Packet Byte<br>0 - 1 - First Byte<br>1 - 0 - Last Byte (Good FCS)<br>1 - 1 - Last Byte (Bad FCS) |

| B5-B4 | RxFIFO<br>Status | These two bits indicate the status of the 19 deep receive FIFO. This status is encoded as follows:<br>B5 - B4         0 - 0       - Rx FIFO Empty         0 - 1       - 14 Bytes         1 - 0       - Rx FIFO Overflow         1 - 1       - 15 Bytes                               |

| B3-B2 | TxFIFO<br>Status | These two bits indicate the status of the 19 deep transmit FIFO as follows:<br>B3 - B2<br>0 - 0 - Tx FIFO Full<br>0 - 1 - 5 Bytes<br>1 - 0 - Tx FIFO Empty<br>1 - 1 - 4 Bytes                                                                                                        |

| B1    | Idle             | If '1', an idle channel state has been detected.                                                                                                                                                                                                                                     |

| B0    | Int              | If '1' an unmasked asynchronous interrupt has been detected.                                                                                                                                                                                                                         |

Figure 8. HDLC Status Register (Read Add. 00011<sub>B</sub>)

| BIT | NAME    | DESCRIPTION                                                                                                           |

|-----|---------|-----------------------------------------------------------------------------------------------------------------------|

| B7  | EnDcoll | A '1' will enable the D-channel collision interrupt.<br>A '0' will disable it. This bit is available only in TE mode. |

| B6  | EnEOPD  | A '1' will enable the received End of Packet interrupt.<br>A '0' will disable it.                                     |

| B5  | EnTEOP  | A '1' will enable the transmit End of Packet interrupt.<br>A '0' will disable it.                                     |

| B4  | EnFA    | A '1' will enable the Frame Abort interrupt.<br>A '0' will disable it.                                                |

| B3  | EnTxFL  | A '1' will enable the Transmit FIFO Low interrupt.<br>A '0' will disable it.                                          |

| B2  | EnTxFun | A '1' will enable the Transmit FIFO Underrun interrupt.<br>A '0' will disable it.                                     |

| B1  | EnRxFF  | A '1' will enable the Receive FIFO Full interrupt.<br>A '0' will disable it.                                          |

| B0  | EnRxFov | A '1' will enable the Receive FIFO Overflow interrupt.<br>A '0' will disable it.                                      |

#### Table 9. HDLC Interrupt Mask Register (Write Add. 00100<sub>B</sub>)

| BIT | NAME                 | DESCRIPTION                                                                                                                                                                                                                                                 |

|-----|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| B7  | Dcoll <sup>(1)</sup> | A '1' indicates that a collision has been detected on the D-channel (i.e., received E-bit does not match with transmitted D-bit). This bit is available only in TE mode and when the HDLC transmitter is enabled. It always reads '0' in NT mode.           |

| B6  | EOPD <sup>(1)</sup>  | A '1'indicates that an end of packet has been detected on the HDLC receiver. This can be<br>in the form of a flag, an abort sequence or as an invalid packet.                                                                                               |

| B5  | TEOP <sup>(1)</sup>  | A '1' indicates that the transmitter has finished sending the closing flag of the last packet in the Tx FIFO, and the internal priority level is reduced from high to low.                                                                                  |

| B4  | FA <sup>(1)</sup>    | A '1' indicates that the receiver has detected a frame abort sequence on the received data stream.                                                                                                                                                          |

| B3  | TxFL <sup>(1)</sup>  | A '1' indicates that the device has only four Bytes remaining in the Tx FIFO. This bit has significance only when the Tx FIFO is being depleted and not when it is getting loaded.                                                                          |

| B2  | TxFun <sup>(1)</sup> | A '1' indicates that the Tx FIFO is empty without being given the 'end of packet' indication.<br>The HDLC will transmit an abort sequence after encountering an underrun condition.                                                                         |