# YAMAHA" L S I

7-77-21

# YM7121C

# Signal Processor & Controller (& RAM) for Compact Disc Player (SPC V)

#### OUTLINE

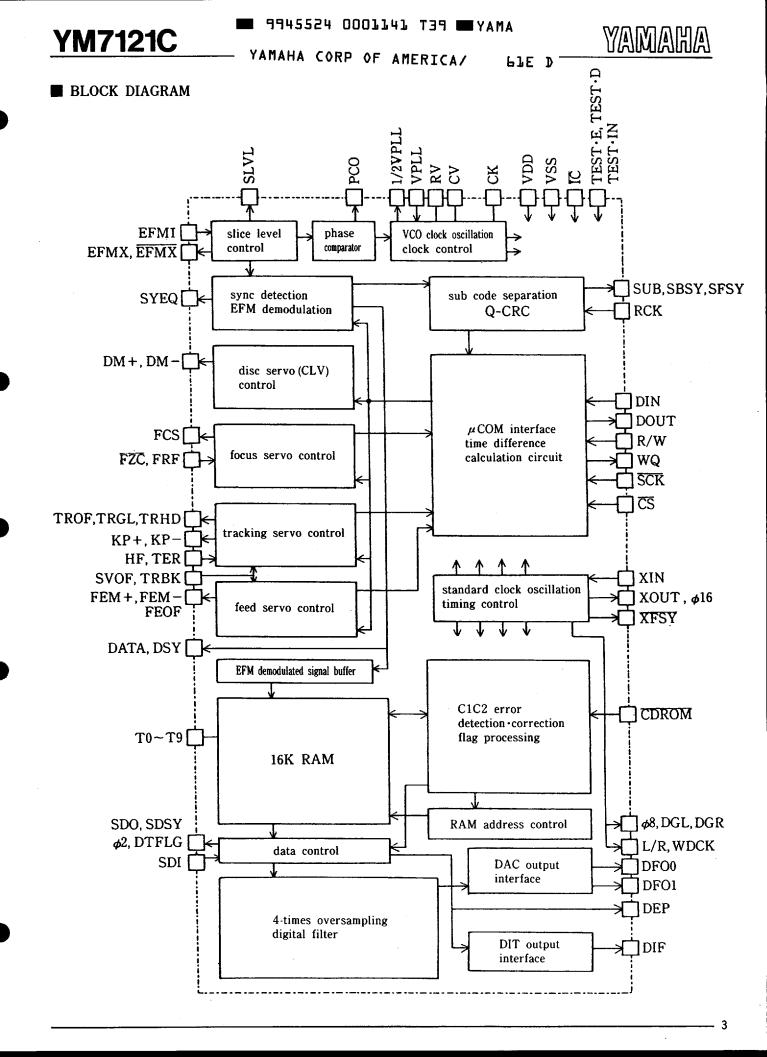

YM7121C is one-chip CMOS LSI to provide various servo control and signal processing capabilities needed in compact disc players.

It has a built-in slice level control for EFM signals from optical pickup and a clock reproduction circuit; it performs EFM demodulation, error detection and correction, jitter absorption by internal RAM, and operation of various intelligent servo controls for focusing, tracking, feeding, and disc motor.

This LSI also has digital audio interface output capability conforming to EIAJ format and four-times oversampling digital filter adaptable to either 1DAC or 2DAC of MSB first output, to realize various applications.

#### ■ FEATURES

- X'tal (16.9344 MHz) is connected to generate standard clock oscillation and necessary timing signals.

- The built-in VCO oscillation and slice level control circuit perform clock reproduction, sync. signal separation, and EFM demodulation.

- In addition to sub code separation and output following to EIAJ format, Q sub codes are CRC checked for output to a microprocessor.

- Phase difference between reproduced and standard clock signals is detected to control the disc motor with PWM.

- Command input on a microprocessor administrates various servo controls for focusing search as well as tracking feed for quick access and skipping.

- In addition to automatic searching capability for quick access, track counter for high-speed searching is built in.

- The built-in RAM buffers the EFM demodulation signals to absorb wow and flutter of the disc. (Jitter absorption range:  $\pm 4$  frames)

- •EFM demodulation signals are unscrambled and de-interleaved.

- Error detection and correction as well as flag processing for digital audio signals (Double error correction for both C1 and C2)

- Linear interpolation is used to replace the uncorrectable error data (up to a maximum if 8 consecutive errors). And preceding data hold is applied for errors over eight.

- The data output is in MSB first format and four-times oversampling digital filter is built in.

YM7121C CATALOG

- PIE D

- Output of digital audio interface signals conforming to EIAJ for interface with other audio equipments.

- Error flag output ,for CD-ROM.

- ●80-pin flat package, silicone gate CMOS LSI, operated by 5V power supply.

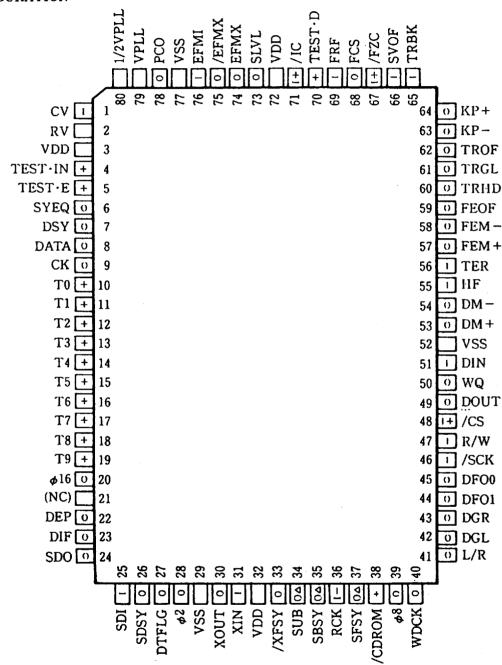

#### **■ PIN CONFIGURATION**

TOP VIEW

- I : Input terminal

- O:Output terminal

- +: Pull-up, -: Pull-down

- $\triangle$ : Open-drain

PJE D

#### PIN DESCRIPTION

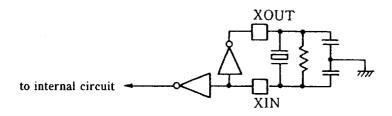

#### 1. Clock Oscillation XIN, XOUT, \$\phi\$16

When X'tal oscillators (16.9344 MHz) are connected to both terminals and capacitors are connected between each terminal and the ground, oscillation is generated. Clock is output from the  $\phi$  16 terminal.

# 2. Slice Level Control Circuit EFMI, EFMX, EFMX, SLVL

To EFMI terminal, signals from optical pickup at an adequate level ( $1 \sim 2 \text{ Vpp}$ ) are input. From EFMX and EFMX, signals antiphased each other are output with amplitude limiting. Slice level control is performed with these signals and external amplifier. At SLVL, amplitude change component for both terminals are output, and by adding an adequate external integral circuit, simple slice level control can be performed.

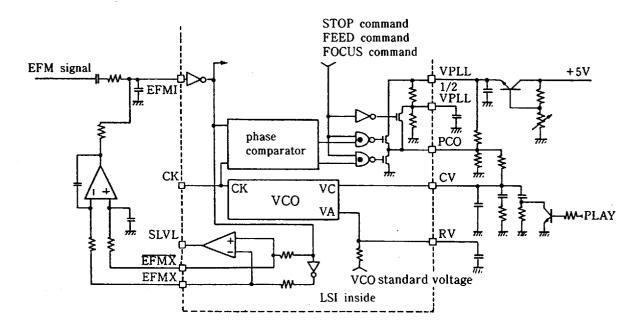

#### 3. Clock reproduction circuit PCO, CK, CV, RV, VPLL, 1/2 VPLL

Output at PCO terminal is phase difference output at the time of polarity change of clock and EFM pattern, and clock reproduction circuit with internal VCO oscillation circuit can be configured by adding certain time constant from outside for input to CV terminal. VPLL terminal is for input of DC voltage adapted to VCO free run frequency (8.6436 MHz). 1/2 VPLL terminal is for output of half cut VPLL terminal input, and voltage stabilizing capacitor shall be mounted here externally.

RV terminal is the standard voltage terminal of internal VCO, and requires mounting of external stabilizing capacitor. CK is the clock of 4.3218 MHz (average) which is obtained by dividing of VCO frequency into four.

PIE D

#### 4. Sync. Equal Signal SYEQ

This is a check output terminal which becomes "H" when the frame synchronizing signals detected from input EFM pattern equals the frame synchronizing signals from internal counter.

#### 5. Output of EFM demodulation signal checking DATA, DSY

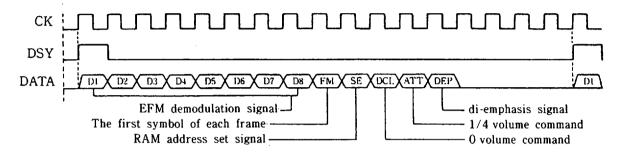

DATA is a serial signal of CK clock bit rate, which consists of 17 bits and includes eight bits of EFM demodulation signal and five bits of data control signal. DSY is the synchroizing signal to turn "H" at the timing which coincides initial of DATA output. These therminals are for checking.

#### 6. Sub code output SUB, SBSY, SFSY, RCK

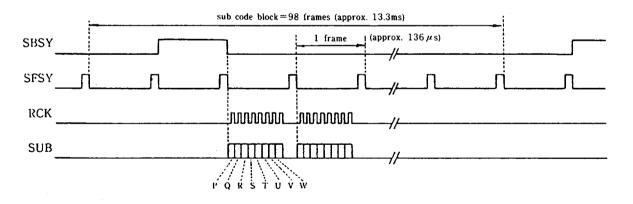

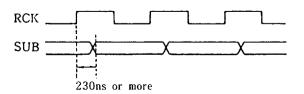

SBSY is for sub code frame synchronizing signal output, which becomes "H" when it finds sub code frame period (Usually two clocks for every 98 clocks for the frame synchronizing signal SFSY) and keeps "H" for that period.

When the change from "H" to "L" of SFSY is checked from outside and eight clocks are input to RCK terminal, sub codes P to W are serially output from SUB terminal. When SBSY is "H", S0·S1 are output at P code timing. Each of these terminal conform to EIAJ sub code interface standard.

PIE D

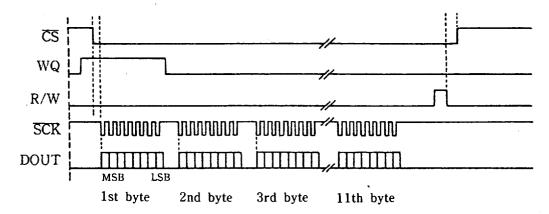

# 7. Q Code Output WQ, R/W, Dout, SCK, CS

These terminals serve as interface to inform the microprocessor of LSI internal status and Q code information.

When WQ turns "H" under the conditions below, the following information for the bytes  $1 \sim 11$  can be read from DOUT by sending clock signals from the microprocessor to the SCK terminal.

| byte | DOUT contents   |

|------|-----------------|

| 1    | internal status |

| 2    | CONT ADR        |

| 3    | TNO             |

| 4    | X               |

| 5    | MIN             |

| 6    | SEC             |

| 7    | FRAME           |

| 8    | P-CODE          |

| 9    | A MIN           |

| 10   | A SEC           |

| 11   | A FRAME         |

|      |                 |

contents of the internal status (1st byte)

| D7   | D6  | D 5 | D4  | D3  | D 2 | D1  | D0 |

|------|-----|-----|-----|-----|-----|-----|----|

| SIGN | S 2 | Sl  | 8 F | 4 F | MZ  | FCO | NQ |

SIGN: search sign

S1,S2: search mode

4F,8F: search frame error

MZ: disc motor stop ('1'=stop)

FCO: focus out ('1'=out)

NQ: new Q code ('1'=new Q code)

\*When track count finishes, D7='1'

$D6 \sim D3 = 0000$

When 1 track kick finishes,

D7~D3='11111'

#### Conditions when WQ becomes "H"

- 1) When the disc motor starts rotation, or when the disc motor stops.

- 2) When focus is in operation, or when focus operation stops.

- 3) When new and correct Q codes are set in the internal register.

- 4) When the track count is completed.

When WQ is "H", at least 1 byte in the internal status needs to be read out, but reading can be stopped at any arbitrary byte afterward.

In search mode, search completion does not cause WQ to be "H", and the internal status shall be always' monitored.

Only when  $\overline{CS} = "L"$ , DOUT is output.

LLE D

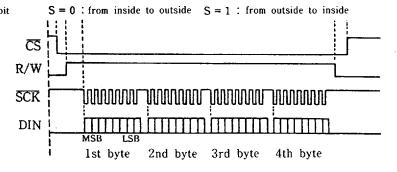

# 8. Microprocessor Instructions R/W, DIN, SCK, CS

The following instructions are available for control of this LSI from microprocessors.

All the instructions except for search and track count consist of 1byte (8 bits). For search and track count instructions, target value of 3 bytes shall be input after the instruction.

$\overline{CS}$  terminal is for chip select when the serial port of microprocessor is used for other interfaces at the same time, and YM7121B receives commands only when  $\overline{CS}$  is "L".

| HEX | commands       | D 7 | D 6 | D 5 | D 4 | D 3 | D 2 | D 1 | D 0 | volume | command bytes |

|-----|----------------|-----|-----|-----|-----|-----|-----|-----|-----|--------|---------------|

| 00H | STOP           | 0   | 0   | 0   | ×   | 0   | 0   | 0   | 0   | 0      | 1             |

| 01H | +1 TRACK KICK  | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | 0      | 1             |

| 11H | -1 TRACK KICK  | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 1   | 0      | 1             |

| 20H | FEED FORWARD   | 0   | 0   | l   | 0   | 0   | 0   | 0   | 0   | 0      | 1             |

| 30H | FEED RETURN    | 0   | 0   | 1   | 1   | 0   | 0   | 0   | 0   | 0      | 1             |

| 40H | FOCUS START    | 0   | 1   | 0   | ×   | 0   | 0   | 0   | 0   | 0      | 1             |

| 60H | DISC START     | 0   | 1   | 1   | 0   | 0   | 0   | 0   | 0   | 0      | 1             |

| 70H | DISC BRAKE +1  | 0   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0      | 1             |

| 80H | PLAY           | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1      | 1             |

| 90H | PLAY MUTE      | 1   | 0   | 0   | 1   | 0   | 0   | 0   | 0   | 0      | 1             |

| AOH | FF +2          | 1   | 0   | 1   | 0   | 0   | 0   | 0   | 0   | 1/4    | 1             |

| BOH | FB +2          | 1   | 0   | 1   | 1   | 0   | 0   | 0   | 0   | 1/4    | 1             |

| COH | FFF +2         | 1   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | 1/4    | 1             |

| DOH | FFB *2         | 1   | 1   | 0   | 1   | 0   | 0   | 0   | 0   | 1/4    | 1             |

| E0H | SEARCH (PAUSE) | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0   | 0      | 4             |

| FOH | TRACK COUNT    | 1   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | 0      | 4             |

| 08H | INITIAL SET    | 0   | 0   | 0   | 0   | 1   | 0   | 0   | 0   | 0      | 1             |

\*1: When stop condition is MZ='1' only, in DISC BRAKE,

$01110000 \rightarrow 01110100$

\*2: When 1/4 volume makes 0,

$101 \times 0000 \rightarrow 101 \times 1100$

$110 \times 0000 \rightarrow 110 \times 1100$

#### SEARCH COMMAND

| COMMAND BYTE | 1      | 2       | 3       | 4      |

|--------------|--------|---------|---------|--------|

| COMMAND      | SEARCH | MINITES | SECONDS | FRAMES |

#### TRACK COUNT COMMAND

| COMMAND BY | TE |    |      | 1   |    |    | 2   |     | 1   | 3   |    | 1  | 4  |    |        |    |

|------------|----|----|------|-----|----|----|-----|-----|-----|-----|----|----|----|----|--------|----|

| COMMAN     | D  | TR | RACK | COU | NT |    | TRA | ACK | NUM | BER |    |    | 0  |    | $\neg$ | ,  |

|            |    |    |      |     |    |    |     |     |     |     |    |    |    |    |        |    |

| D7         | D  | 6  | D5   | D4  | D3 | D2 | Dl  | D0  | D7  | D6  | D5 | D4 | D3 | D2 | DI     | D0 |

| S          | T  | 7  | Т6   | Т5  | T4 | Т3 | T2  | Tl  | T0  | 0   | 0  | 0  | 0  | 0  | 0      | 0  |

track number =  $(1-2S) \times (2^7 \times T7 + 2^6 \times T6 + 2^5 \times T5 + 2^4 \times T4 + 2^3 \times T3 + 2^2 \times T2 + 2^4 \times T1 + T0) \times 128$

PPE D

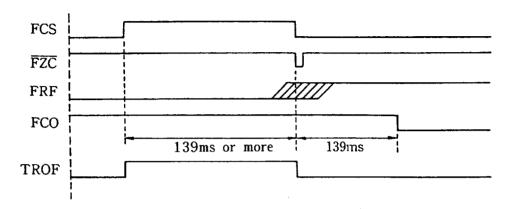

# 9. Focus Servo FZC, FRF, FCS, TROF

These terminals are used for focus searching.

FCS (="H") signal is for focus leading. If  $\overline{FZC}$  signal (="L") which is generated at the focus point is detected, leading operation is stopped and FRF signal which detected the mirror level falls FCO flag in the internal status. And during the focus leading, TROF terminal become "H" to keep tracking servo off.

#### 10. Disc Servo DM+ and DM-

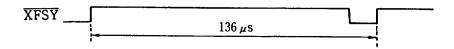

DM+ and DM- terminals are provided for speed control of the disc motor. Using PWM output, they output DM+ = "H" when accelerated and DM- = "H" when braking. PWM resolution is 1/144 (945 nS) of one frame (136  $\mu$ S) and the maximum value is 128/144 (121  $\mu$ S).

#### Combination of command, disc servo internal mode and output

| command<br>(HEX) | 00", 20"<br>30" | 40 <sup>H</sup> | 60 <sup>rt</sup> | 70* | 80". 90'<br>D0". E0 | ", A0", B | 0". C0". | DM+,DM-<br>(YTUQ) | 1 frame (136 μs) |

|------------------|-----------------|-----------------|------------------|-----|---------------------|-----------|----------|-------------------|------------------|

| internal mode    | OFF             | HOLD            | ACC              | BRK | ACC                 | AFC       | PLL      |                   | 121 μs           |

| DM+              |                 |                 | 0                |     | 0                   | 0         | 0        | 128/144           |                  |

| DM+<br>(PWM)     |                 | 0               |                  |     |                     |           | 0        | 1/144~127/144     |                  |

| no output        | 0               | 0               | 0                | 0   | 0                   | 0         | 0        | 0                 |                  |

| DM-<br>(PWM)     |                 |                 |                  |     |                     | -         | 0        | 1/144~127/144     |                  |

| DM-              | 1               | 1               |                  | 0   |                     | 0         | 0        | 128/144           |                  |

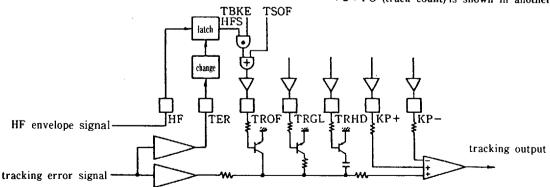

# 11. Tracking Servo HF, TER, TROF, TRGL, TRHD, KP+, KP-, SVOF, TRBK

HF signal amplitude change caused at the time of track crossing during search is sampled at zero cross point of the tracking error signal TER to output TROF signal. This signal turns on (when TROF = "L") and off (TROF="H") the tracking servo, to facilitate the track capturing.

PIE D

For track kick, KP+ (forward) and KP- (backward) signals are output. At this period, TRHD becomes "H" and have the tracking error signal held. And TRGL is the output to raise the tracking gain after track kick, and TRGL="H" for normal gain.

SVOF is the input to turn off the tracking servo and feed servo from outside. "H" input makes TROF = "H", FEOF="H", TRHD="L", KP+="L", and KP-="L".

TRBK is the input to operate the tracking brake mechanism from outside. Input of "H" to this terminal makes TRGL="L" and the internal control signal TBKE="H".

| command                                 | A0*     | 130*               | C0#      | Do"        |         |        | 01"                                    | 11"                                    | others •2 |

|-----------------------------------------|---------|--------------------|----------|------------|---------|--------|----------------------------------------|----------------------------------------|-----------|

| repeat cycle<br>(fast forward)          | 104ms   | 47.9ms             | 104ms    | 104ms      |         |        | once                                   | once                                   |           |

| TSOF •1                                 |         |                    |          |            |         |        |                                        |                                        |           |

| TBKE *1                                 |         |                    |          |            | <u></u> |        |                                        |                                        |           |

| TRGL                                    |         |                    |          |            |         |        |                                        |                                        |           |

| TRHD                                    |         |                    |          | <b>万</b> 正 |         |        |                                        |                                        |           |

| KP+                                     |         |                    | ЛL       |            | 九山      |        | $\int$                                 |                                        |           |

| KP-                                     |         | VIII.              | <u>.</u> |            |         |        |                                        | ЛШ                                     |           |

| pattern<br>(ms)                         | 0.272   | 0.272              | 0.816    | 0.816      | 5.714   | 5.714  | 0.136mor<br>0.181<br>5.6ms<br>TER turn | 0.136mor<br>0.181<br>5.6ms<br>TER turn |           |

| repeat cycle<br>(search)                | 17.4ms  | 17.4ms             | 17.4ms   | 17.4ms     | 34.8ms  | 34.8ms |                                        |                                        |           |

| search (EO <sup>M</sup> )<br>(sub mode) | 7 - 1   | (7 · 4)<br>7 · 5   | 7 · 2    | 7 - 6      | 7 · 3   | 7 · 7  |                                        |                                        | 7 - 0     |

| time difference<br>(unit:s)             | +1/4~+4 | (~-1/4)<br>-1/4~+4 | -4~+128  | -4~-128    | +128~   | -128-  |                                        |                                        | ~+1/4     |

\*1: TSOF, TBKE indicate LSI's intenal terminals.

\*2: FOH(track count) is shown in another fig.

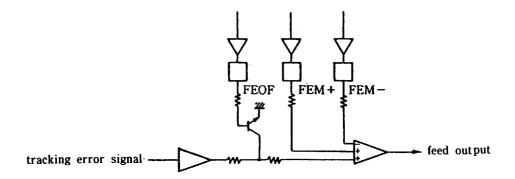

## 12. Feed Servo Mechanism FEOF, FEM+, FEM-

FEM+ or FEM- signals are output as high-speed feed signals.

During this output, FEOF="H" is also output to cut the feed servo operation.

| command                    | .00", 40", 60",<br>70" | 20 <sup>H</sup> | 30" | 80", 90", A0",<br>B0", C0", D0" |        |        |

|----------------------------|------------------------|-----------------|-----|---------------------------------|--------|--------|

| FEOF                       |                        |                 |     |                                 |        |        |

| EFM+                       |                        |                 |     |                                 |        |        |

| EFM-                       |                        |                 |     |                                 |        |        |

| repeat cycle<br>(unit: ms) |                        |                 |     |                                 | 34.8ms | 34.8ms |

| sparch<br>(sub mode)       |                        |                 |     | 7 · 0, 1, 2<br>7 · 4, 5, 6      | 7 · 3  | 7 · 7  |

#### 13. Track count commands

When track count commands are implemented, control signals are set at each terminal as shown below. Since TER signals are used for track count, attention is required for TER noise when using track count. Rising of TER signals is differentiated to obtain count pulse. When counted number becomes equal to target value, each control signal will have the same status as that for play mute.

To stop track count, track count command shall be input with the count target value of "0", before necessary command input.

| FEOF  |       |          |

|-------|-------|----------|

| EFM+  |       |          |

| EFM-  |       |          |

| TSOF* |       |          |

| TRGL  |       |          |

| TRHD  |       |          |

| TBKE* |       |          |

|       | START | ∆<br>end |

\* : TSOF. TBKE are LSI's internal terminals

$EFM + , EFM - : - : inside \rightarrow outside$

--- ; outside→inside

# 14. X'tal clock synchronizing signal XFSY

This output is the frame sync. signal of 7.35 KHz generated from X'tal clock.

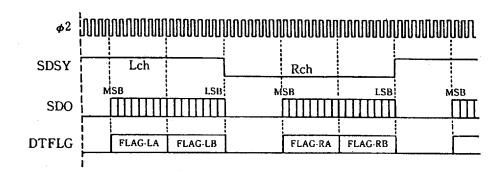

#### 15. Error Correction Check Signals C1 and C2 DTFLG, TEST · IN

DTFLG terminal is usually used for the flag to show that the SDO output is supplemented by interpolation or preceding data hold. When TESE · IN terminal is set to "L", however, check signal to show the operation of C1 and C2 error correction circuit is output from this terminal.

| C1, C2                  | F 1 | F 2 |

|-------------------------|-----|-----|

| no error                | 0   | 0   |

| single error correction | 0   | 1   |

| double error correction | 1   | 0   |

| uncorrerctable          | 1   | 1   |

| - |         |         | lframe (13 | 36 μs)  |          |

|---|---------|---------|------------|---------|----------|

| į | 22.7 μs | 22.7 μs | 22.7 μs    | 22.7 μs |          |

| ŗ | CIFI    | C1F2    | C2F1       | C2F2    | i —      |

| L | CIFI    | CITZ    | CZITI      | L_CZFZ  | <u>l</u> |

# 16. Data Control and Serial Signal Output \$2, SDO, SDSY, DTFLG, CDROM

$\oint 2$  is X'tal clock of 2.1168MHz. SDO is serial signal output with  $\oint 2$  bit rate and is MSB first. DTFLG terminal is used for the error flag to indicate that the SDO output contains interpolation or preceding data hold. This can be used to lighten the burden of software in applications such as CD-ROM. Linear interpolation is used to replace the uncorrectable error data up to eight samples for L/R respectively, and preceding data hold is applied for errors over eight. When  $\overline{\text{CDROM}}$  terminal is set to "L", interpolation and preceding data hold can be masked for CD-ROM and other applications.

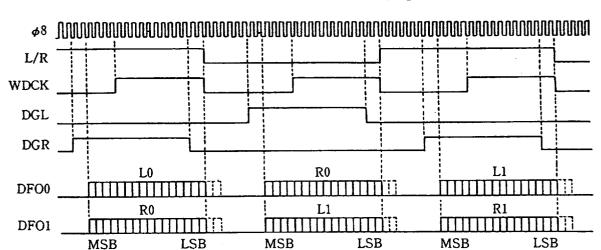

#### 17. Digital Filter SDI, \$\phi 8\$, WDCK, L/R, DFO0, DFO1, DGL, DGR

SDI is an input terminal for four-times oversampling digital filter and usually connected with SDO. DFOO and DFO1 are serial signals for MSB first DAC  $\phi$  8 bit rate (8.4672MHz). WDCK and L/R are sync. signals.

These signals can be used for either of 1DAC or 2DAC system. For 2DAC, Lch output uses DFO0 and Rch output uses DFO1, data latch uses L/R output and deglitcher uses DGL output. For 1DAC, output uses DFO0 and data latch uses WDCK output, and deglitcher uses DGL and DGR outputs.

YM7121C

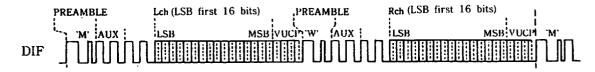

#### 18. Digital Audio Interface Output DIF

DIF terminal output is digital audio interface format output conforming to EIAJ, and biphase marked with bits C and U.

This output depends on sound volume given in the command. (see the table of p.7) When the volume "0" is commanded, audio data and V flag become "0".

#### 19. Di-emphasis signal DEP

When DEP output is "H", di-emphasis is required.

# 20. Initial Clear IC

This LSI needs initial clear operation when turned on.

With VDD at the standard voltage,  $\overline{IC}$  shall be kept at "L" for 400  $\mu$ s or more after clock input to XIN.

#### 21. Test Terminals TEST · IN, TEST · E, TEST · D, T0 to T9

Terminals T0 to T9 are for internal RAM test, and used with non-connected. Other terminals are also for test, but pulled up internally and can be used without connection.

YAMAHA

YAMAHA CORP OF AMERICA/

PTE D

#### ■ ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings

| Parameter             | Symbol | Rating                     | Unit |

|-----------------------|--------|----------------------------|------|

| Power supply voltage  | Voo    | -0.3~+7.0                  | V    |

| Input voltage         | Vı     | -0.3~ V <sub>IM</sub> +0.5 | v    |

| Operating temperature | Тор    | -20-+75                    | c    |

| Storage temperature   | Tstg   | -50-+125                   | c    |

#### **Recommended Operating Conditions**

| Parameter             | Symbol | Minimum | Typical | Maximum | Unit |  |

|-----------------------|--------|---------|---------|---------|------|--|

| Power supply voltage  | Vpp    | 4.75    | 5.00    | 5.25    | ٧    |  |

| Operating temperature | Тор    | 0       | 25      | 75      | c    |  |

**Electrical Characteristics** (Condition:  $T_a = \pm 25$ °C,  $VDD = 5.0 \pm 0.25$ V)

| Parameter                 | Symbol            | Condition                   | Minimum | Typical | Maximum | Unit | Remarks    |

|---------------------------|-------------------|-----------------------------|---------|---------|---------|------|------------|

| Power supply current      | Іов               | V <sub>00</sub> = <b>5V</b> |         | 70      |         | æA   | 1          |

| Output voltage H level    | Voii              | $lor = 20 \mu A$            | 4.0     |         |         | V    |            |

| Output voltage L level    | Vol.              | lo. =lmA                    |         |         | 0.4     | V    |            |

| Input voltage H level (1) | Vini              |                             | 3.5     |         |         | V    | <b>*</b> 1 |

| Input voltage L level (1) | V16.1             |                             |         |         | 1.5     | ٧    | <b>*</b> 1 |

| Input voltage H level (2) | V <sub>IH2</sub>  |                             | 2.0     |         |         | V    | <b>*</b> 2 |

| Input voltage L level (2) | V <sub>11.2</sub> |                             |         |         | 0.8     | V    | <b>*</b> 2 |

**※1**: Applicable to the terminals EFMI, FZC, FRF, HF, TER, RCK.

\*2: Applicable to the terminals DIN, SCK.

PIE D

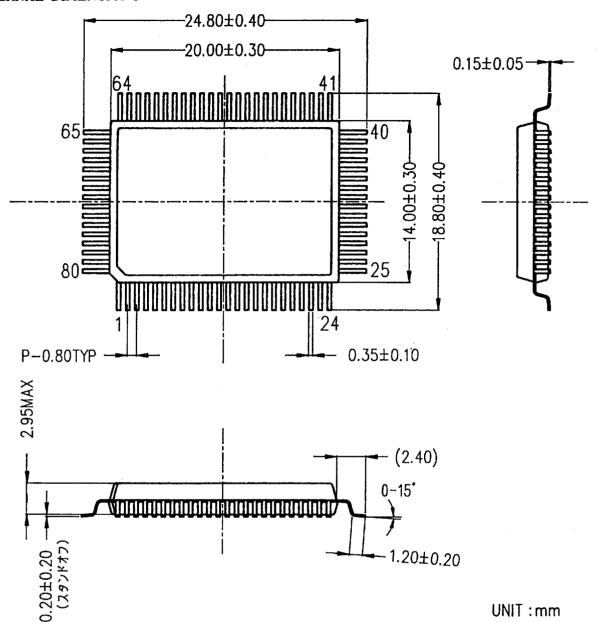

#### **EXTERNAL DIMENSIONS**

#### YAMAHA CORPORATION AGENCY

Address inquiries to : Semi-conductor Sales Department

Head Office

203, Matsunokijima, Toyooka-mura. Iwata-gun, Shizuoka-ken, 438-01

Electronic Equipment business section Tel. 0539-62-4918 Fax. 0539-62-5054

3-4, Surugadai Kanda, Chiyoda-ku, Tokyo, 101 Ryumeikan Bldg. 4F Tel. 03-3255-4481 Fax. 03-3255-4488

■ Tokyo Office

Osaka Office 3-12-9, Minami Senba, Chuo-ku,

Osaka City, Osaka, 542

Shinsaibashi Plaza Bldg. 4F

Tel. 06-252-7980 Fax. 06-252-5615

■ U.S.A. Office YAMAHA Systems Technology,

981 Ridder Park Drive San Jose, CA95131

Tel. 408-437-3133 Fax.408-437-8791

The specifications of this product are subject to improvement changes without prior notice.