# 5-Pin µP Reset Circuits with Watchdog Timer and Manual Reset

## **FEATURES**

- Precision Power Supply Monitoring with ±1.5% Accuracy

- Low Quiescent Current: 3 µA max.

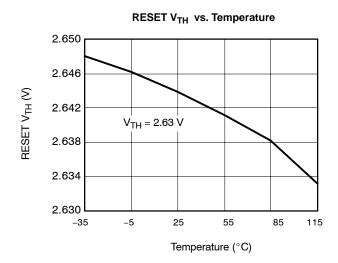

- Low Threshold Voltage Temperature Coefficient: 100 ppm max.

- Guaranteed  $\overline{RESET}$  Valid Dow to  $V_{CC} = 1 \text{ V}$

- Seven Reset Threshold Options

- Small SOT23-5 Packages

- No External Components

- Power Supply Transient Immunity

## **APPLICATIONS**

- Portable Intelligent Electronics

- Computers and Controllers

- Automotive Electronics

- Critical μP/μC Power Supply Monitoring

#### **DESCRIPTION**

SiP823/SiP824/SiP825 series are μProcessor supervisory circuits in a 5-pin SOT23 package, that combine the functions of power supply and µProcessor monitoring.

If the power supply voltage drops, or has been, below a safe level or the µProcessor shows signs of problematic inactivity, the circuit will generate a reset signal at it's output.

The SiP823 and SiP825 have an input to accommodate manual reset.

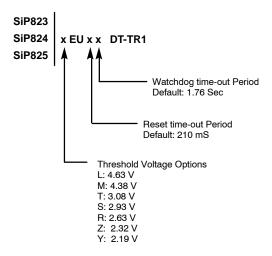

Seven pre-programmed reset threshold voltage levels are available as standard options.

Specially configured options are available upon request, allowing for further customization of reset voltage, reset time-out, and watchdog time-out periods.

The SiP823 has a reset output that is "active low" and the SiP824 and SiP825 have complementary outputs for both "active high" and "active low" resets. Both output drives are push/pull configurations.

Space saving SOT23-5 packages and low quiescent current make this family of products ideally suited for portable battery operated equipment.

These circuits fully ignore fast negative V<sub>CC</sub> transients and have valid reset output signals with power supply levels down to 1 V.

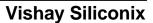

## **PACKAGING AND PIN DEFINITION**

See page 2 for ordering and marking information.

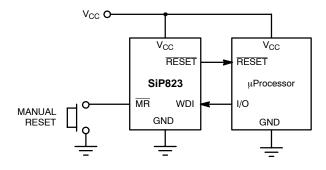

# TYPICAL APPLICATION CIRCUIT

Document Number: 72397 S-41150-Rev. B, 14-Jun-04

# **ORDERING INFORMATION**

Please contact your local Vishay Semiconductor Sales Office for information on customization of reset voltage, reset time-out, and watchdog time-out options.

| MARKING INFORMATION |       |           |        |           |        |  |

|---------------------|-------|-----------|--------|-----------|--------|--|

| SiP823              |       | Si        | SiP824 |           | SiP825 |  |

| SiP823LEU           | AAxxx | SiP824LEU | Alxxx  | SiP825LEU | ARxxx  |  |

| SiP823MEU           | ABxxx | SiP824MEU | AKxxx  | SiP825MEU | ASxxx  |  |

| SiP823TEU           | ACxxx | SiP824TEU | ALxxx  | SiP825TEU | ATxxx  |  |

| SiP823SEU           | ADxxx | SiP824SEU | AMxxx  | SiP825SEU | AVxxx  |  |

| SiP823REU           | AExxx | SiP824REU | ANxxx  | SiP825REU | AWxxx  |  |

| SiP823ZEU           | AGxxx | SiP824ZEU | AOxxx  | SiP825ZEU | AXxxx  |  |

| SiP823YEU           | AHxxx | SiP824YEU | APxxx  | SiP825YEU | AYxxx  |  |

Last two characters denote date code.

| ABSOLUTE MAXIMUM RATINGS ( $T_A = 25^{\circ}C$ unless otherwise noted)            |                      |                                 |      |

|-----------------------------------------------------------------------------------|----------------------|---------------------------------|------|

| Parameter                                                                         | Symbol               | Limit                           | Unit |

| Supply Voltage                                                                    | Vcc                  | -0.3 to 6.0                     |      |

| All Other Pins                                                                    | V <sub>MAX</sub>     | -0.3 to (V <sub>CC</sub> + 0.3) | _ v  |

| Input/Output Current, All Pins                                                    | I <sub>IN(max)</sub> | 20                              | mA   |

| Operating Temperature Range                                                       | T <sub>A</sub>       | -40 to 85                       |      |

| Storage Temperature Range                                                         | T <sub>stg</sub>     | -65 to 150                      | °C   |

| Junction Temperature Range                                                        | TJ                   | -40 to 125                      |      |

| Power Dissipation ( $T_A \le 70^{\circ}$ C)<br>SOT-23 (Derate 4 mW/°C above 70°C) | P <sub>D</sub>       | 310                             | mW   |

Notes a. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

|                                                  |                      | Test Conditions Unless Specified                                       |                       | Limits |                      |                  |  |

|--------------------------------------------------|----------------------|------------------------------------------------------------------------|-----------------------|--------|----------------------|------------------|--|

| Parameter                                        | Symbol               | T <sub>A</sub> = -40°C to 85°C, Typical Values @ T <sub>A</sub> = 25°C | Min <sup>a</sup>      | Typb   | Max <sup>a</sup>     | Unit             |  |

|                                                  |                      |                                                                        |                       |        |                      |                  |  |

| Supply Voltage                                   | V <sub>CC</sub>      |                                                                        | 1                     |        | 5.5                  | V                |  |

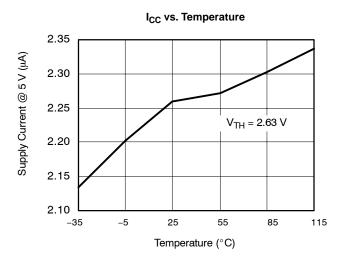

| Supply Current (No. Lood)                        |                      | V <sub>CC</sub> = V <sub>TH</sub> + 10%                                |                       |        | 10.0                 | μА               |  |

| Supply Current (No Load)                         | lcc                  | T <sub>A</sub> = 25°C                                                  |                       |        | 3.0                  |                  |  |

| RESET Threshold                                  | V <sub>TH</sub>      | T <sub>A</sub> = 25°C                                                  | V <sub>TH</sub> -1.5% |        | V <sub>TH</sub> 1.5% | V                |  |

| Threshold Hysteresis                             | V <sub>TH(hys)</sub> |                                                                        |                       | 0.4    |                      | %V <sub>TH</sub> |  |

| RESET Threshold<br>Temperature Coefficient       |                      |                                                                        |                       | 40     |                      | PPM/°C           |  |

|                                                  | V.                   | Sip82_L/M/J: $V_{CC} < V_{TH}$ , $I_{SINK} = 1.2 \text{ mA}$           |                       |        | 0.5                  |                  |  |

| RESET Output Voltage                             | V <sub>OL</sub>      | Sip82_R/S/T/Y/Z: $V_{CC} < V_{TH}$ , $I_{SINK} = 0.5 \text{ mA}$       |                       |        | 0.4                  |                  |  |

|                                                  | V <sub>OH</sub>      | V <sub>CC</sub> > V <sub>TH</sub> , I <sub>SOURCE</sub> = 0.5 mA       | 0.8 V <sub>CC</sub>   |        |                      |                  |  |

|                                                  | .,                   | Sip82_L/M/J: $V_{CC} > V_{TH}$ , $I_{SINK} = 1.2 \text{ mA}$           |                       |        | 0.5                  | - V              |  |

| RESET Output Voltage                             | V <sub>OL</sub>      | Sip82_R/S/T/Y/Z: $V_{CC} > V_{TH}$ , $I_{SINK} = 0.5 \text{ mA}$       |                       |        | 0.4                  |                  |  |

|                                                  | V <sub>OH</sub>      | V <sub>CC</sub> < V <sub>TH</sub> , I <sub>SOURCE</sub> = 0.5 mA       | 0.8 V <sub>CC</sub>   |        |                      |                  |  |

| V <sub>CC</sub> to RESET Delay                   | T <sub>D1</sub>      | V <sub>CC</sub> = V <sub>TH</sub> – 100 mV                             |                       | 40     |                      | μS               |  |

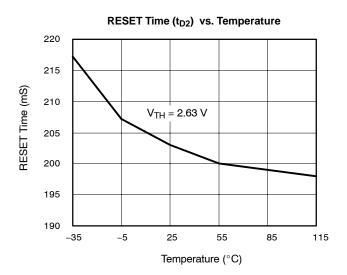

| RESET Time-out Period                            | T <sub>D2</sub>      |                                                                        | 140                   | 210    | 280                  | mS               |  |

| Watchdog Input (SiP82                            | 3/SiP824)            |                                                                        |                       |        |                      | •                |  |

| Watchdog Time-out Period                         | t <sub>WD</sub>      |                                                                        | 1.12                  | 1.76   | 2.40                 | S                |  |

| W <sub>D1</sub> Pulse Width                      | t <sub>WDI</sub>     | $V_{IL} = 0.4 \text{ V}, V_{IH} = 0.8 \text{ V}_{CC}$                  | 50                    |        |                      | nS               |  |

| NA 1 137 H 0                                     | V <sub>IL</sub>      | V V 2007                                                               |                       |        | 0.7                  | V                |  |

| W <sub>DI</sub> Input Voltage <sup>c</sup>       | V <sub>IH</sub>      | V <sub>CC</sub> = V <sub>TH</sub> + 20%                                | 0.8 V <sub>CC</sub>   |        |                      | 7 V              |  |

|                                                  | I <sub>IL</sub>      | W <sub>DI</sub> = 0 V                                                  | -15                   | -8     |                      | μА               |  |

| W <sub>DI</sub> Input Current                    | I <sub>IH</sub>      | W <sub>DI</sub> = V <sub>CC</sub> = 5 V                                |                       | 8      | 15                   |                  |  |

| Manual Reset Input (Si                           | P823/SiP8            | 25)                                                                    |                       |        |                      | •                |  |

| MR Pulse Width                                   | t <sub>MR</sub>      |                                                                        | 1.0                   |        |                      | μS               |  |

|                                                  | V <sub>IL</sub>      |                                                                        |                       |        | 0.7                  | 1                |  |

| MR Input Voltage                                 | V <sub>IH</sub>      | V <sub>CC</sub> = V <sub>TH</sub> + 20%                                | 0.8 V <sub>CC</sub>   |        |                      | \ \ \            |  |

| MR Noise Immunity<br>(Pulse Width with No RESET) |                      |                                                                        |                       | 100    |                      | nS               |  |

| MR to RESET Delay                                | t <sub>MR</sub>      |                                                                        |                       | 500    |                      | 7                |  |

| MR Pull-Up Resistance                            |                      |                                                                        | 80                    |        | 120                  | kΩ               |  |

Notes

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

b. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

c. W<sub>DI</sub> is internally serviced within the watchdog period if W<sub>DI</sub> is left unconnected.

| PIN DESCRIPTION |        |        |                 |                                                                                                                                                                                                                                                                   |  |  |

|-----------------|--------|--------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SiP823          | SiP824 | SiP825 | Name            | Description                                                                                                                                                                                                                                                       |  |  |

| 1               | 1      | 1      | RESET           | RESET is active low. This pin has a push/pull output.                                                                                                                                                                                                             |  |  |

| 2               | 2      | 2      | GND             | Ground                                                                                                                                                                                                                                                            |  |  |

| N/A             | 3      | 3      | RESET           | RESET is active high. This pin has a push/pull output.                                                                                                                                                                                                            |  |  |

| 3               | N/A    | 4      | MR              | Manual RESET. Active low. Pulling this pin low forces a RESET. After a low to high transition RESET remains asserted for exactly one RESET timed period. This pin is internally pulled high. If this function is unused it can be left open or tied to $V_{CC}$ . |  |  |

| 4               | 4      | N/A    | W <sub>DI</sub> | Watchdog Input. Any transition on this pin will RESET the watchdog timer. If this pin remains high or low for longer than the watchdog interval, a RESET is asserted. Float or tristate this pin to disable the watchdog feature.                                 |  |  |

| 5               | 5      | 5      | V <sub>CC</sub> | Positive power supply. A RESET is asserted after this voltage drops below a predetermined level. After V <sub>CC</sub> rises above that level, RESET remains asserted until the end of the RESET time-out period.                                                 |  |  |

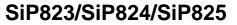

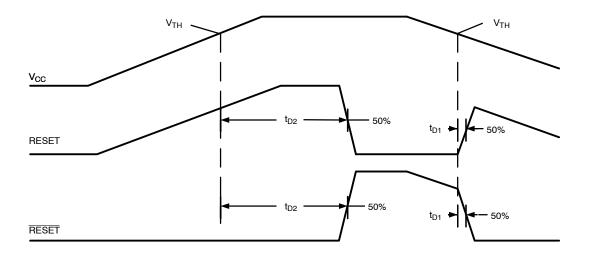

# TIMING DIAGRAMS

Figure 1. RESET Timing Diagram

Figure 2. Watchdog Timing Diagram

# SiP823/SiP824/SiP825

# Vishay Siliconix

#### **DETAILED DESCRIPTION**

An active signal on a microprocessor ( $\mu$ P) RESET input starts the  $\mu$ P in a know state. The SiP823/SiP824/SiP825  $\mu$ P supervisory circuits assert a RESET signal to prevent code execution errors during power-up, power-down and brown-out conditions.

The SiP823/SiP824/SiP825 also monitors the  $\mu$ P's health by checking for problematic inactivity at its W<sub>DI i</sub> input.

# **RESET Output**

A RESET will be asserted for the specified RESET time-out period ( $t_{D2}$ ), if any of three conditions are present:

- 1)  $V_{CC}$  drops below the threshold voltage ( $V_{TH}$ )

- 2) The MR pin is pulled low

- The watchdog timer does not detect a transition within the watchdog interval (t<sub>WD</sub>) and the watchdog input is not left floating.

The RESET output will remain asserted for the specified time-out period (t<sub>D2</sub>) after:

- 1)  $V_{CC}$  rises above the RESET threshold ( $V_{TH}$ )

- 2) MR goes high.

## **Manual RESET Input**

$\mu P$  based products often require a manual RESET capability, which can be activated by manual intervention or external logic circuitry.

A logic low at the  $\overline{\text{MR}}$  pin of the SiP823/SiP824/SiP825 asserts a RESET signal. RESET remains asserted while  $\overline{\text{MR}}$  is low and for a period ( $t_{D2}$ ) after it returns high.

MR has an internal 100-k $\Omega$  pull-up resistor, so it can be left floating when not activated. This input can be driven with CMOS logic levels or with open drain devices. The input is internally de-bounced to reject fast input transients.

## Watchdog Input (SiP823/SiP824)

The SiP823/SiP824 have a watchdog input (WDI), that monitors the  $\mu P$ 's activity. If the  $\mu P$  does not toggle the watchdog input within the watchdog time-out period (t\_WD),

RESET is asserted. The internal RESET timer is cleared by either a RESET pulse or by toggling WDI.

WDI detects pulses as short as 50 nS. While RESET is asserted, the timer remains cleared. As soon as RESET is released the timer starts counting (Figure 2).

The watchdog timer can be disabled by leaving WDI open or by three stating the connected driver. As soon as the WDI input is driven either high or low, the watchdog function resumes with the watchdog timer set to zero.

# **WDI Input Current**

The watchdog input pin (WDI) typically sources or sinks 8  $\mu$ A when driven high or low.

As a result, the power dissipation at the WDI input is independent of duty cycle. When the WDI pin is left floating or tri-stated, the power supply current is less than 3  $\mu$ A.

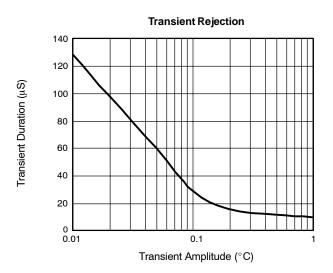

#### **Transient Rejection**

The SiP823/SiP824/SiP825 family has good immunity for negative going transients on the  $\rm V_{\rm CC}$  line.

The smaller the duration of the transient, the larger the amplitude can be without triggering RESET.

The "Transient Rejection" graph below shows the relation between transient amplitude and allowable transient duration, without triggering RESET.

The value on the horizontal scale represents the portion of the amplitude of the transient that is exceeding the  $V_{TH}$  level.

#### RESET Output State at Low VDD

With V $_{CC}$  voltage on the level of MOS transistor thresholds (<1.0 V), the RESET output of the SiP823/SiP824/SiP825 may become undefined. For outputs that are active low (RESET), a resistor placed between RESET and GND on the order of 100 k $\Omega$  will ensure that the RESET output stays low when the V $_{CC}$  drops below the MOS transistor threshold. In a like manner, a resistor placed between RESET and V $_{CC}$  will ensure the correct state for active high RESET outputs.

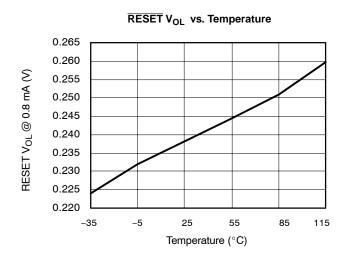

# TYPICAL CHARACTERISTICS ( $T_A = 25^{\circ}C$ Unless Otherwise Noted)