TECHNICAL DATA

TELECOMMUNICATION LSI

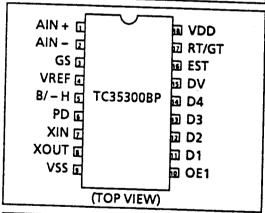

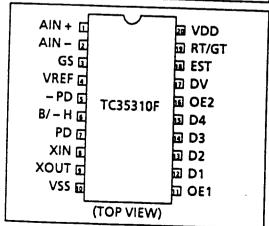

TC35300BP,TC35310F

# TC35300BP,TC35310F

(DTMF RECEIVER)

## 1. GENERAL DESCRIPTION

TC35300BP,TC35310F are the LSI designed for detecting Dual Tone Multi Frequency (DTMF) used for Push Button (PB) signal. The DTMF signal is detected from signal transferred through the telephone line, and is outputted after conversion into 4-bit code. The built-in differential amplifier at the input allows easy connection with the balanced circuit. The latch circuit with 3-state output is applied to the data output stage allowing its easy interfacing with other devices.

### 2. FEATURES

- ☐ Dynamic range over 34dB

- ☐ Power down mode

- ☐ Adjustable reception level

- ☐ 4-bit Hexadecimal code or binary coded 20F-8 selectable

- ☐ External CR for adjusting acquisition and release time

- $\square$  Built in anti-aliasing filter at signal input stage

- ☐ 3-Stage data output

- ☐ 3.5MHz crystal oscillator or ceramic resonator

- ☐ CMOS Low power

- ☐ +5V Single power supply

- ☐ 18-Pin DIP TC35300BP, 20-Pin SOP TC35310F

### 2.1 APPLICATIONS

- ☐ Automatic answering telephone set

- □ PBX

- ☐ Remote control

The products described in this document are strategic products subject to COCOM regulations. They should not be experted without authorization from the appropriate governmental authorities.

TOSHIBA CORPORATION

TECHNICAL DATA

TC35300BP,TC35310F

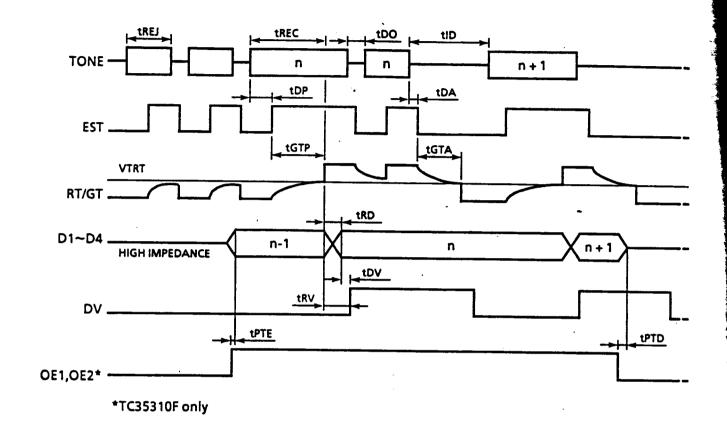

### 3. TIMING CHART

### PIN DESCRIPTION

| PIN NO. |     | NAME  | IN/OUT | FUNCTION                                                                                                                                                                     |

|---------|-----|-------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIP     | SOP | NAME  |        |                                                                                                                                                                              |

| 1       | 1   | AIN+  |        | Non-inverting input of first stage differential amplifier                                                                                                                    |

|         | 2   | AIN-  |        | Inverting input of first stage differential amplifier                                                                                                                        |

| 3       | 3   | GS    | 001    | Output terminal of first stage differential amplifier (Gain is adjusted through connecting with feedback resistance.)                                                        |

| 4       | 4   | VREF  | ОИТ    | Output of reference voltage of VDD/2 to be used for biassing first stage differential amplifier                                                                              |

|         | 5   | - PD  | IN     | At "L", power-down mode is made. Clearing function of D1 to D4 outputs is not provided.                                                                                      |

| 5       | 6   | B/-H  | IN     | Format of D1 to D4 outputs is selected. "L": Hexadecimal Code "H": 2 of 8 Binary Code (For each output code, refer to the attached table.)                                   |

| 6       | 7   | PD    | IN     | At "H", power-down mode is made.<br>Clearing function of D1 to D4 outputs is not provided.                                                                                   |

| 7       | 8   | XIN   | IN     | Connect crystal oscillator of 3.579545MHz. Becomes input terminal when external clock is used.                                                                               |

| 8       | 9   | XOUT  | OUT    | Connect crystal oscillator of 3.579545MHz. Make open for using external clock.                                                                                               |

| 9       | 10  | VSS   | -      | Ground terminal (usually 0V)                                                                                                                                                 |

| 10      | 11  | -OE1  | IN     | 3-state control terminal of D1 to D4 (Pull-up resistance is built in.) OE1 = "H", OE2 = "H": Enable OE1 = "L", OE2 = ANY: High impedance                                     |

| 11      | 12  | D1    | OUT    | Output terminal of receiving data                                                                                                                                            |

| 12      | 13  | D2    | OUT    | At OE1-OE2 = "L" : High impedance At OE1-OE2 = "H" : Enable                                                                                                                  |

| 13      | 14  | D3    | OUT    | (The digital output format is programmed by B/-H.)                                                                                                                           |

| 14      | 15  | D4    | OUT    | <b>-</b>                                                                                                                                                                     |

| -       | 16  | OE2   |        | 3-state control terminal of D1 to D4 OE1 = "H", OE2 = "H" : Enable OE1 = ANY, OE2 = "L" : High impedance                                                                     |

| 15      | 17  | DV    | оит    | When a valid tone-pair is detected continuously for specified time, the level becomes high.                                                                                  |

| 16      | 18  | EST   | OUT    | When a detected tone pair is effective, the level becomes high.                                                                                                              |

| 17      |     | RT/GT | IN/OUT | Tone acquisition time and release time can be set through connection with resistance and capacitor. (For each time setting, refer to calculating formula shown hereinafter.) |

| 18      | 20  | VDD   | -      | Power supply terminal (Normally 5V)                                                                                                                                          |

| T      | C35300BP-3    |

|--------|---------------|

| 22     | - NOV 1989    |

| 200415 | A CORROBATION |

TECHNICAL DATA

### TELECOMMUNICATION LSI

### TC35300BP,TC35310F

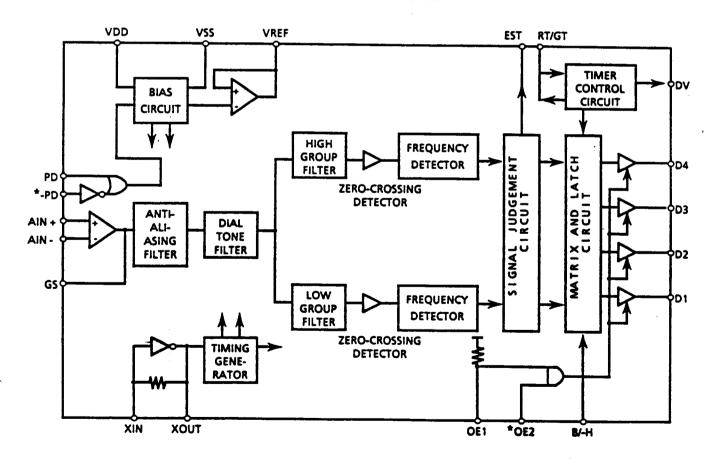

### 5. FUNCTIONAL DESCRIPTION

### 5.1 DESCRIPTION OF CIRCUIT CONSTRUCTION AND OPERATION

TC35300BP,TC35310F consist of the band pass filter which correspond to the frequency band using DTMF signal, and the logic circuit in which verifies the frequency and duration of the received tone to decode a before passing the corresponding code to the output.

The outline of each operations described in the following.

a) Band Pass Filter and Zero-crossing Detector Circuit

The band pass filter section is composed of the high-accuracy switched capacitor filters and the anti-aliasing filter in the first stage.

Anti-aliasing filter reduces the extraneous high frequency components. The first stage of switched capacitor filters is provided a dial tone rejection filter where sufficiently dissipates the frequency components of 350Hz to 440Hz due to suppress the error detection.

Removing the unnecessary signal components, furthermore, the signal is applied band pass filters each enclosing high or low-group frequency.

Each filter output is followed by zero-crossing detector with hysteresis. When the each signal amplitude at the output exceeds specified level, the signal is transformed into full-rail logic signal.

b) Signal Decision Circuit and Timer Controlling Circuit

The signal judgment circuit decides that the each transformed logic signal detected to be effective or not. When these signals are decided to be effective, EST becomes high, and the corresponding code of DTMF digit is transferred to the matrix circuit. When the detected signal is not a DTMF signal or an absence of signal, then EST becomes low.

The timer controlling circuit is used for measuring the effective signal duration and for protecting against the drop out of valid signal by means of the analogical delay by external RC time-constant driven by EST. (These time are measured by the voltage at RT/GT based at the time of EST change. Therefore, the actual tone reception time and release time are added tDP, tDA in each time. tDP and tDA are the delay time of EST after the signal input.) When the voltage at RT/GT changes from 0V to VTRT the input signal is judged to be effective, and the corresponding 4-bit code with the input signal is latched into D1 to D4. After completion of latch,DV output becomes high. When the voltage at RT/GT fall down from VDD to VTRT, DV output becomes low.

The effective tone pair code received lastly is always latched into D1 to D4 outputs.

TC35300BP-4 22-NOV.-1989

TECHNICAL DATA

### TELECOMMUNICATION LSI

### TC35300BP,TC35310F

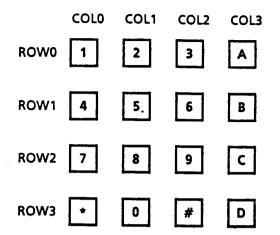

### 5.2 DTMF TO BINARY DECODING (HEXADECIMAL AND 2-OF-8)

As the 4-bit digital outputs of D1 to D4, two kinds of format shown in the following are possible through the setting of B/-H.

When B/-H = "L", the output format becomes that of the hexadecimal code, and when B/-H = "H", becomes the binary coded 2-of-8. In the binary coded 2-of-8, each 2-bit value of D4, D3 and D2, D1 corresponds with m or n of ROW m and COL n. (Refer to the Table.)

|     | FH   | H DIGIT | B/-H L (HEXADECIMAL) |      |    |    | H (2-of-8) |    |    |          |    |      |

|-----|------|---------|----------------------|------|----|----|------------|----|----|----------|----|------|

| FL  |      |         | OE1                  | *OE2 | D4 | D3 | D2         | D1 | D4 | D3       | D2 | D1   |

| 697 | 1209 | 1       | н                    | н    | L  | L  | L          | Н  | L  | L        | L  | L    |

| 697 | 1336 | 2       | Н                    | Н    | L  | L  | H          | L  | L  | L-       | L  | Н    |

| 697 | 1477 | 3       | Н                    | Н    | L  | L  | Н          | Н  | L  | L        | н  | L    |

| 770 | 1209 | 4       | Н                    | Н    | L  | I  | ٦          | L  | L  | Н        | L  | L    |

| 770 | 1336 | 5       | н                    | Ξ    | L  | Н  | L          | Н  | L  | H        | L  | н    |

| 770 | 1477 | 6       | Н                    | Н    | L  | Н  | Н          | L  | L  | Н        | Н  | L    |

| 852 | 1209 | 7       | н                    | Н    | L  | Н  | H          | н  | Н  | L        | L  | L    |

| 852 | 1336 | 8       | н                    | Н    | н  | L  | L          | L  | Н  | L        | L  | н    |

| 852 | 1477 | 9       | Н                    | Н    | Н  | L  | L          | н  | н  | · L      | Н  | Ĺ    |

| 941 | 1336 | 0       | Н                    | Н    | Н  | L  | Н          | L  | Н  | н        | L  | н    |

| 941 | 1209 | *       | н                    | н    | н  | L  | Н          | Н  | н  | н        | L  | L    |

| 941 | 1477 | #       | Н                    | Н    | н  | Н  | L          | L  | н  | н        | н  | L    |

| 697 | 1633 | Α       | Н                    | Н    | Н  | Н  | L          | Н  | L  | L        | н  | н    |

| 770 | 1633 | В       | Н                    | Н    | Н  | н  | н          | L  | L  | Н        | н  | н    |

| 852 | 1633 | С       | Н                    | Н    | Н  | Н  | Н          | Н  | Н  | L        | Н  | Н    |

| 941 | 1633 | D       | Н                    | Н    | L  | L  | L          | L  | Н  | н        | Н  | Н    |

|     |      | ANY     | ANY H L              | Н    |    |    |            |    |    |          | _  |      |

| -   | -    |         |                      | Z    | Z  | Z  | Z          | Z  | Z  | Z        | Z  |      |

|     |      |         | L                    | L    |    |    |            |    |    | <u> </u> |    |      |

|     |      |         |                      |      |    |    |            |    | RO | Wm       | C  | DL n |

<sup>\*</sup> TC35310F only

| TC35300BP-5        |

|--------------------|

| 22-NOV1989         |

| TOSHIBA CORPORATIO |

<sup>&</sup>quot;Z" means high impedance.

#### 5.3 DTMF DIALING MATRIX

### 5.4 TC35300BP, TC35310F INTERNAL BLOCK DIAGRAM

\*TC35310F only

TECHNICAL DATA

### TELECOMMUNICATION LSI

### TC35300BP,TC35310F

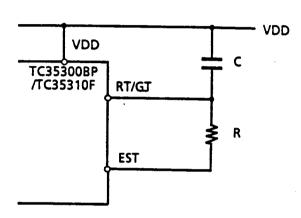

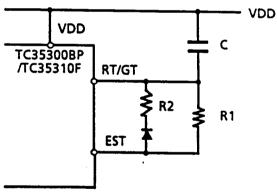

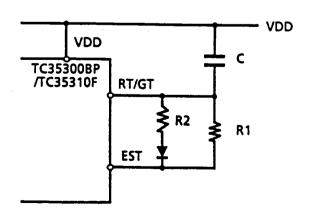

#### 5.5 SETTING OF GUARD TIME

Valid DTMF signal time and the protection time against tone drop out are set through using the time constant of the external resister and capacitor.

Each time is calculated with the formula hereunder. The other methods shown in the following figures b and c can be used according to the application.

$$tREC = tDP + tGTP$$

$tID = tDA + tGTA$

### a) Fundamental Circuit

$$tGTP = R \cdot C \cdot ln[VDD/(VDD-VTRT)]$$

$tGTA = R \cdot C \cdot ln(VDD/VTRT)$

#### b) tGTP<tGTA

$tGTP = (R1\cdot R2)/(R1 + R2)\cdot C\cdot \ln[VDD/(VDD-VTRT)]$  $tGTA = R1\cdot C\cdot \ln(VDD/VTRT)$

#### c) tGTP>tGTA

$tGTP = R1 \cdot C \cdot ln[VDD/(VDD-VTRT)]$  $tGTA = (R1 \cdot R2)/(R1 + R2) \cdot C \cdot ln(VDD/VTRT)$

TOSHIBA

### STECHNICAL DATA

TC35300BP,TC35310F

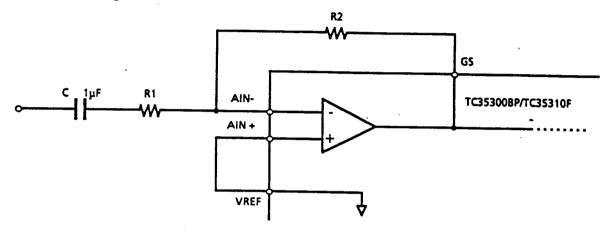

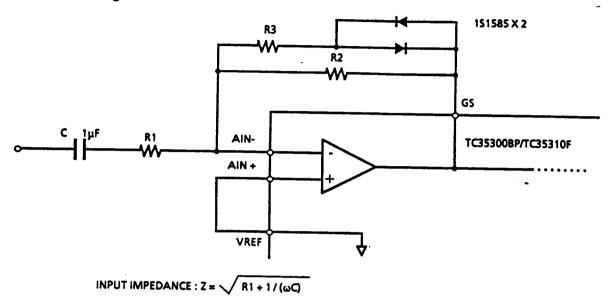

### 5.6 RECEPTION LEVEL ADJUSTMENT AND DYNAMIC RANGE EXPANSION

The reception level of TC35300BP and TC35310F can be set up freely by gain adjustment at the input stage operational amplifier.

The dynamic range can also be expanded over 34dB by composing the logarithmic input circuit configuration, which enables the END to END application.

- a) Standard Input Circuit

- o Configuration

VOLTAGE GAIN : A = 20-log (R2/R1)

INPUT IMPEDANCE :  $Z = \sqrt{R1 + 1/(\omega C)}$

### o Adjustment of Reception Level

The reception level can be set by the value of R1 and R2 keeping the total dynamic range 34-dB MIN. Where R2 is set to be over  $30k\Omega$ .

Minimum Reception Level Vin(min) = -33-20 · log(R2/R1) dBm

Maximum Reception Level Vin(max)=1-20·log(R2/R1) dBm

### o Example

| Reception | signal level | R1   | R2<br>(kΩ) |  |

|-----------|--------------|------|------------|--|

| MIN.(dBm) | MAX.(dBm)    | (kΩ) |            |  |

| -33       | +1           | 100  | 100        |  |

| -36       | -2           | 91   | 130        |  |

| -39       | -5           | 75   | 150        |  |

| -42       | -8           | 56   | 160        |  |

Note) To prevent unrequired signal reception, the gain setting should be done attentively.

| TC35300BP-8 |

|-------------|

| 22-NOV1989  |

|             |

### TELECOMMUNICATION LSI

### TC35300BP,TC35310F

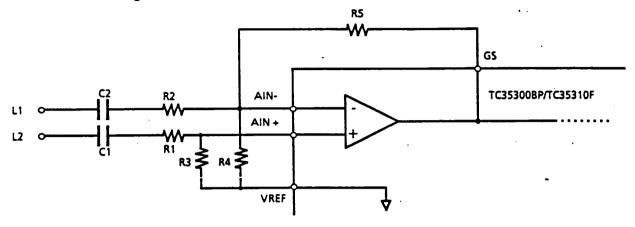

#### b) Differential Input Circuit

Since the differential amplifier is applied to the signal input portion, TC35300BP, TC35310F can also easily be connected to the balanced circuit in the manner shown below.

o Configuration

VOLTAGE GAIN:  $A = 20 \cdot \log (R5/R1)$ INPUT IMPEDANCE :  $Z = 2\sqrt{R1 + 1/(\omega C)}$

### o Adjustment of Reception Level

The reception level can be set by the value of R1 and R5 keeping the total dynamic range 34-dB MIN. Where R5 is set to be over  $30k\Omega$ .

Minimum Reception Level Vin(min) = -33-20·log(R5/R1) dBm Maximum Reception Level Vin(max)=1-20·log(R5/R1) dBm

#### o Example

| Detection :         | signal level | R1   | R5   |  |

|---------------------|--------------|------|------|--|

| MIN.(dBm) MAX.(dBm) |              | (kΩ) | (kΩ) |  |

| -33                 | +1           | 100  | 100  |  |

| -36                 | -2           | 91   | 130  |  |

| -39                 | -5           | 75   | 150  |  |

| -42                 | -8           | 56   | 160  |  |

Note) To prevent unrequired signal reception, the gain setting should be done attentively.

| TC35300BP-9         |

|---------------------|

| 22-NOV1989          |

| TOSHIBA CORPORATION |

c) Logarithmic Input Circuit - for expanding dynamic range

TC35300BP,TC35310F can expand the dynamic range by composing logarithmic amplifier at the input stage operational amplifier.

o Configuration

### o Adjustment of Detection Level

The reception level can be set by the value of R1,R2 and R3. Using a logarithmic input circuit, dynamic range is expanded over 34dB. Where parallel resistance of R2 and R3 is set to be over  $30k\Omega$ .

Minimum Reception Level Vin(min) = -33-20·log(R2/R1) dBm

Maximum Reception Level Vin(max) = 1-20·log [1/R1·(R2·R3)/(R2+R3)] dBm

#### o Example

| Detection | signal level | R1   | R2   | R3   | Dynamic Range |

|-----------|--------------|------|------|------|---------------|

| MiN.(dBm) | MAX.(dBm)    | (kΩ) | (kΩ) | (kΩ) | (kΩ)          |

| -39       | +1           | 51   | 100  | 100  | 40            |

| -43       | +1           | 51   | 160  | 75   | 44            |

| -53       | +1           | 30   | 330  | 36   | 54            |

Note) To prevent unrequired signal reception, the gain setting should be done attentively.

| TC3     | 5300BP-10 |

|---------|-----------|

| 22-N    | IOV 1989  |

| TOSHIBA | CORPORA   |

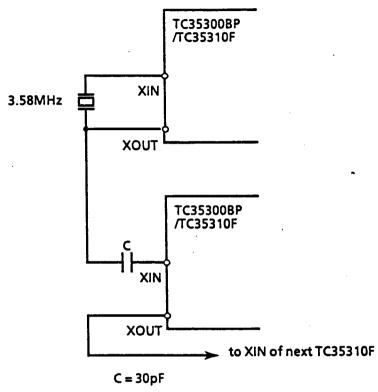

### 5.7 CRYSTAL OSCILLATOR

TC35300BP,TC35310F oscillator output of the first device in the chain is coupled through a 30pF capacitor to the oscillator input(XIN) of the next device. Subsequent device is connected in a similar fashion.

### 6. ELECTRICAL CHARACTERISTICS

#### 6.1 MAXIMUM RATINGS

|                       | 0.01001 | RATING               |                      |      |

|-----------------------|---------|----------------------|----------------------|------|

| ITEM                  | SYMBOL  | TC35300BP            | TC35310F             | TINU |

| Power Supply Voltage  | VDD     | VSS-0.5 to VSS + 7.0 | VSS-0.5 to VSS + 7.0 | V    |

| Input Voltage         | VIN     | VSS-0.5 to VDD + 0.5 | VSS-0.5 to VDD + 0.5 | ٧    |

| Input Current         | IIN     | -10 to +10           | -10 to + 10          | mA   |

| Output Voltage        | VOUT    | VSS-0.5 to VDD + 0.5 | VSS-0.5 to VDD + 0.5 | V    |

| Power Dissipation     | PD      | 300                  | 180                  | mW   |

| Storage Temperature   | Tstg    | -60 to + 150         | -60 to + 150         | °C   |

| Operating Temperature | Topr    | -40 to +85           | -40 to +85           | •c   |

|     | TC35300BP-11     |

|-----|------------------|

|     | 22-NOV1989       |

| TOP | HIBA CORROBATION |

### INTEGRATED CIRCUIT **TOSHIBA**

TECHNICAL DATA

TELECOMMUNICATION LSI

TC35300BP,TC35310F

#### DC ELECTRICAL CHARACTERISTICS 6.2

| ITEM                     | SYMBOL        | TEST CONDITION                                              |           | MIN. | TYP. | MAX. | UNIT |

|--------------------------|---------------|-------------------------------------------------------------|-----------|------|------|------|------|

| Operating Voltage        | VDD           |                                                             |           | 4.75 |      | 5.25 | ٧    |

| Operating Supply Current | IDD<br>(opr)  | PD = 0V,-PD = 5.0V                                          |           |      | 3.0  | 7.0  | mA   |

| Static Supply Current    | IDD<br>(Stby) | PD = 5.0V,-PD = 0V                                          |           |      | 0.01 | 10.0 | uA   |

| High Level Input Voltage | VIH           |                                                             |           | 3.5  |      |      | ٧    |

| Low Level Input Voltage  | VIL           |                                                             |           |      |      | 1.5  | V    |

| High Level               | ЮН            | VOUT = 4.6V<br>(Except for RT/GT)                           |           | 0.4  | 0.8  |      | mA   |

| Output Current           |               | VOUT = 4.6V<br>(RT/GT)                                      |           | 0.8  | 1.0  |      | mA   |

| Low Level                | IOL           | VOUT = 0.4V<br>(Except for RT/GT)<br>VOUT = 0.4V<br>(RT/GT) |           | 1.0  | 2.5  |      | mA   |

| Output Current           |               |                                                             |           | 1.2  | 3.0  |      | mA   |

| High Level Input Current | пн            | VIN = 5.0V                                                  |           | n,   |      | 0.1  | uΑ   |

| Low Level Input Current  | IIL           | VIN = 0V                                                    |           |      |      | 0.1  | uA   |

| Pull-up Current          | ISO           | OE1 = 0V                                                    | TC35300BP |      | 7.5  | 15   | uA   |

|                          |               |                                                             | TC35310F  |      | 50.0 |      |      |

| RT/GT Threshold Voltage  | VTRT          |                                                             |           | 2.2  | 2.35 | 2.5  | ٧    |

| VREF Output Voltage      | VREF          |                                                             |           | 2.4  |      | 2.7  | ٧    |

| VREF Output Resistance   | RREF          | VREF = 2.55V                                                |           |      |      | 1    | kΩ   |

Ta = 25°C,VDD = 5V,VSS = 0V

TECHNICAL DATA

### TELECOMMUNICATION LSI

### TC35300BP,TC35310F

### 6.3 AC ELECTRICAL CHARACTERISTICS

| ITEM                                           | SYMBOL         | TEST CONDITION                 | MIN.   | TYP.   | MAX.   | UNIT |

|------------------------------------------------|----------------|--------------------------------|--------|--------|--------|------|

| Maximum Input Signal *1<br>Level for Reception |                | Each Tone                      | +1     | ·      |        | dBm  |

| Minimum Input Signal *1<br>Level for Reception |                | Composite Signal               |        | - 40   | - 33   | dBm  |

| Tone Amplitude Ratio                           |                |                                |        | ±10    |        | dB   |

| Frequency Deviation Tone Reception             |                |                                | ± 1.5  | ,      |        | %    |

| Frequency Deviation Tone<br>Rejection          |                |                                | ±3.5   | •      |        | %    |

| Third Tone Rejection Ratio                     |                |                                |        | - 16   |        | dB   |

| Dial Tone Rejection Ratio                      |                |                                |        | + 22   |        | dB   |

| Noise Rejection Ratio                          |                |                                |        | - 12   |        | dB   |

| SCT O A Dala Time                              | tDP "L" -> "H" | 5                              | 11     | 14     | mS     |      |

| EST Output Delay Time                          | tDA            | "H" -> "L"                     | 0.5    | 4.0    | 8.5    | mS   |

| Tone-Reception Signal<br>Duration Time         | tREC           | Refer to Test<br>Circuit       | 40     | ٠      |        | m\$  |

| Tone-Rejection Signal<br>Duration Time         | tREJ           |                                |        | •      | 20     | mS   |

| Signal Quiescent Time                          | tID            |                                | 40     |        |        | mS   |

| Signal Hit Protection Time                     | tDO            |                                |        |        | 20     | mS   |

| Data Output Delay Time                         | tRD            | RT->D1 to D4                   |        | 6      | 9      | uS   |

|                                                | tRV            | RT->DV                         |        | 12     |        | uS   |

| DV Output Delay Time                           | tDV            | D1 to D4-DV                    |        | 5      |        | uS   |

| Output Enable Time                             | tPTE           | $RL = 10k\Omega$ , $CL = 50pF$ |        | 50     | 60     | nS   |

| Output Disable Time                            | tPTD           | $RL = 10k\Omega$ , $CL = 50pF$ |        | 300    |        | nS   |

| Clock Frequency                                | fCLK           |                                | 3.5759 | 3.5795 | 3.5831 | MHz  |

| Capacitive Load                                | CLX            | XOUT                           |        |        | 30     | pF   |

$Ta = 25^{\circ}C,VDD = 5V,VSS = 0V,fCLK = 3.579545MHz$

\*1 : Input stage amplifier gain = 0dB

TC35300BP-13

22-NOV.-1989

TOSHIBA CORPORATION

## TOSHIBA

#### OPERATIONAL AMPLIFIER CHARACTERISTICS (AIN+, AIN- to GS) 6.4

| ITEM                            | SYMBOL | TEST CONDITION                     | MIN. | TYP.  | MAX. | UNIT |

|---------------------------------|--------|------------------------------------|------|-------|------|------|

| Input Offset Voltage            | VIO    |                                    |      | ± 25  |      | mV   |

| Input Offset Current            | 110    | VSS≤ VIN≤ VDD                      |      | ± 100 |      | nA   |

| Power Supply<br>Rejection Ratio | PSRR   | 1 KHz                              |      | 60    |      | dB   |

| Common Mode<br>Rejection Ratio  | CMRR   |                                    |      | 60    | ,    | dB   |

| Open Loop Gain                  | AO     |                                    |      | 65    |      | dB   |

| 0 dB Band Width                 | fT     |                                    | -    | 500   |      | kHz  |

| Rated Output<br>Voltage         | vo     | Load Resistance:<br>100 kΩ or over |      | 4.5   |      | Vpp  |

| Load Resistance                 | RL     | GS                                 |      | 30    |      | ·kΩ  |

| Capacitive Load                 | CL     | GS                                 |      | 50    |      | pF   |

Ta = 25°C, VDD = 5V, VSS = 0V

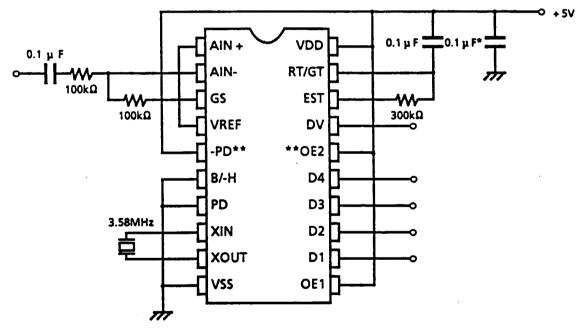

All resistors are ±1% tolerance.

All capacitors are ±5% tolerance.

- The performances of TC35300BP and TC35310F can be optimized by keeping noise on the supply rails to minimum. The decoupling 0.1uF capacitor should be connected close to the device.

- \*\* TC35310F only

**TEST CIRCUIT**

| TC35300BP-   | 14      |

|--------------|---------|

| 22-NOV19     | 39      |

| 7004104 6000 | 20.47.0 |

TECHNICAL DATA

TELECOMMUNICATION LSI

TC35300BP,TC35310F

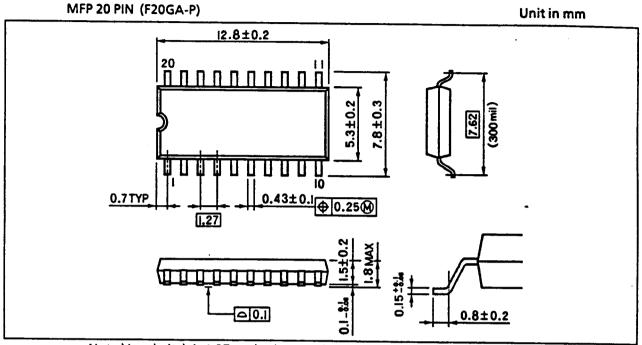

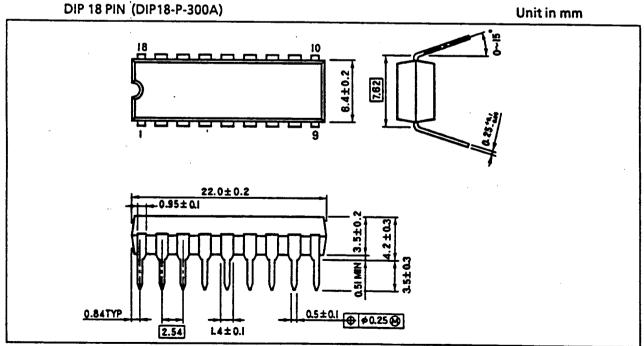

### 7. OUTLINE DRAWING OF PACKAGE

Note ) Lead pitch is 1.27 and tolerance is ± 0.12 to the theoretical center of each lead that is obtained on the basis of No.1 and No.20 leads.

Note ) Lead pitch is 2.54 and tolerance is ± 0.28 to the theoretical center of each lead that is obtained on the basis of No.1 and No.18 leads.

| TC35300BP-15        |

|---------------------|

| 22-NOV1989          |

| TOSHIBA CORPORATION |