# μPD6308 LCD COLUMN DRIVER

# PRELIMINARY INFORMATION

## Description

The  $\mu$ PD6308 can directly drive any multiplexed dotmatrix LCD organized with up to 40 columns. It is easily cascaded to fit the user's system.

#### **Features**

- ☐ High voltage output 21 V maximum

- □ Directly controllable by the µPD72030

- CMOS technology

- ☐ Single 5 V ± 10% power supply

## **Ordering Information**

| Part Number | lumber Package Type                      |  |

|-------------|------------------------------------------|--|

| μPD6308G-F  | 54-pin plastic miniflat                  |  |

| μPD6308G-R  | 54-pin plastic miniflat (inverted leads) |  |

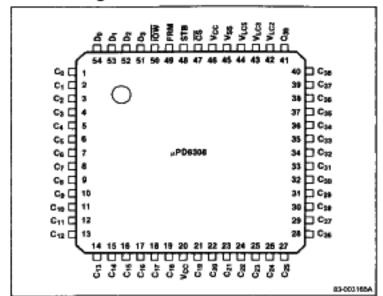

## Pin Configuration

#### Pin Identification

| No.            | Symbol                                                                     | Function<br>Column drive output               |  |

|----------------|----------------------------------------------------------------------------|-----------------------------------------------|--|

| 1-19,<br>21-41 | C <sub>0</sub> -C <sub>39</sub>                                            |                                               |  |

| 20             | Voc                                                                        | Positive power supply                         |  |

| 42-44          | V <sub>LC2</sub> , V <sub>LC3</sub> , LCD drive supply<br>V <sub>LC5</sub> |                                               |  |

| 45             | VSS                                                                        | Ground                                        |  |

| 46             | V <sub>CC</sub><br>(= V <sub>LC0</sub>                                     | Positive power supply and<br>LCD drive supply |  |

| 47             | CS Chip select output                                                      |                                               |  |

| 48             | STB                                                                        | Strobe input                                  |  |

| 49             | FRM                                                                        | Frame input                                   |  |

| 50             | IOW                                                                        | I/O write input                               |  |

| 51-54          | D <sub>3</sub> -D <sub>0</sub>                                             | Data input                                    |  |

#### Pin Functions

## Co-C39 (Column Drive Output)

LCD column drive output.

# V<sub>LC2</sub>, V<sub>LC3</sub>, V<sub>LC5</sub> (LCD Drive Supply)

Reference voltages used to drive Co-C39.

## D<sub>0</sub>-D<sub>3</sub> (Data Input)

This is the display data bus. Data in the 40-bit input latch is written via this bus four bits at a time, a total of 10 times.

## FRM (Frame)

A high level input to this pin displays the positive frame and a low level input displays the negative frame.

#### STB (Strobe)

This is the column driver strobe input. At the leading edge of the STB input, the 40-bit display data in the input latch is transferred to the output latch to appear in the column drive output.

## IOW (I/O Write)

This is the data write input. If  $\overline{CS}$  is active and  $\overline{IOW}$  goes low, data on  $D_0$ - $D_3$  is written to the input latch.

#### CS (Chip Select)

This input pin is connected to the chip select output of the row driver as the IOW enable. CS is active low.

# V<sub>CC</sub> (= V<sub>LC0</sub>) (Power Supply and LCD Drive Supply)

Connect the 5 V power supply between V<sub>CC</sub> and V<sub>SS</sub>. V<sub>CC</sub> is also used for the column drive voltage.

#### Vss (Ground)

Ground.

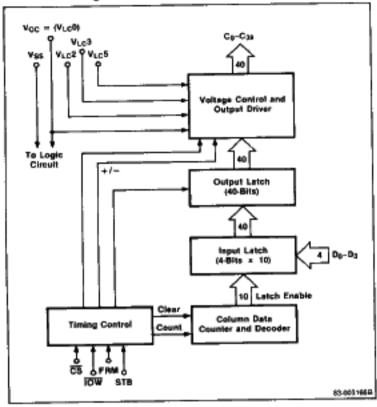

### Block Diagram

## **Functional Description**

### **Timing Control Circuit**

This circuit controls the timing that operates each  $\mu$ PD6308 internal block.

#### Voltage Control Driver Circuit

This circuit generates the column signals for AC drive of the LCD panel. Table 1 lists C<sub>0</sub>-C<sub>39</sub> output levels. FRM' is obtained by internally synchronizing the FRM signal with the leading edge of the STB signal.

Table 1. Co · C39 Output Levels

| Function     |              | + (FRM' = 1)     | - (FRM' = 0)     |

|--------------|--------------|------------------|------------------|

| Select (Data | <b>- 1</b> } | V <sub>LC5</sub> | V <sub>LC0</sub> |

| Clears (Data | = 0)         | V <sub>LC3</sub> | V <sub>LC2</sub> |

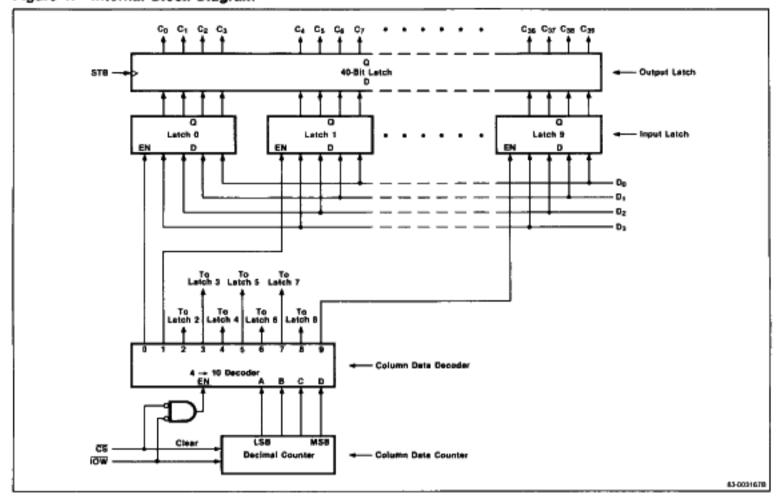

# Column Data Counter/Decoder Circuit

The column data counter/decoder circuit is shown in figure 1. This decimal circuit generates latch enable pulses to the input latches, which latch 40 bits of data (four bits at a time, a total of 10 times). The number of decoder outputs can be increased by cascading µPD6308s under the control of  $\overline{CS}$ . The counter value increments at the leading edge of  $\overline{IOW}$ , and clears when  $\overline{CS}$  goes high.

Figure 1. Internal Block Diagram

#### Input Latch Circuit

The input latch circuit is shown in figure 1. The input latches display data four bits at a time until 40 bits are latched and displayed. When  $\overline{CS}$  is active low, each  $\overline{IOW}$  active low pulse input to the decimal counter causes 1 of 10 latch enable signals to be generated from the column data decoder. Latches 0 to 9 are enabled consecutively to load data  $D_0$ - $D_3$  until 40 bits are latched.

## **Output Latch Circuit**

The output latch circuit is shown in figure 1. The 40 bits output from the input latch circuit are transferred to the output latch circuit at the leading edge of the STB signal and appear on the column drive outputs. Note that  $D_0$  is output to  $C_3$ ,  $D_1$  to  $C_2$ ,  $D_2$ , to  $C_1$ , and  $D_3$  to  $C_0$ .