CMOS LSI

LC78845Q

Sample Rate Converter for Digital Audio

# Preliminary

## **Overview**

The LC78845Q is a synchronous sample rate converter for digital audio signals.

## **Features**

- Converts data sampled at 32 or 48 kHz to 44.1-kHz sampled data.

- Passes 44.1-kHz sampled data trough without change.

- Supports 384fs and 512fs system clock rates.

- 8× oversampling filters

- · Soft muting function

- Built-in PLL circuit

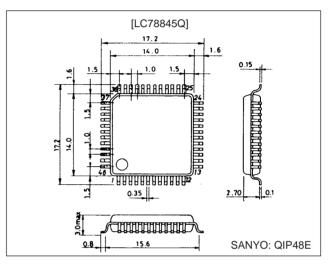

# **Package Dimensions**

unit: mm

3156-QFP48E

# **Specifications**

## Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| Parameter              | Symbol                          | Conditions | Ratings                       | Unit |

|------------------------|---------------------------------|------------|-------------------------------|------|

| Maximum supply voltage | V <sub>DD</sub> max             |            | -0.3 to +7.0                  | V    |

| I/O voltages           | V <sub>I</sub> , V <sub>O</sub> |            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating temperature  | Topr                            |            | -30 to +70                    | °C   |

| Storage temperature    | Tstg                            |            | -55 to +125                   | °C   |

## **DC** Characteristics

| Parameter                 | Symbol          | Conditions             | min                    | typ | max                    | Unit |

|---------------------------|-----------------|------------------------|------------------------|-----|------------------------|------|

| Input voltage range       | V <sub>IN</sub> | Ta = -30 to +70°C      | 0                      |     | V <sub>DD</sub>        | V    |

| Input high-level voltage  | VIH             |                        | 0.7 V <sub>DD</sub>    |     |                        | V    |

| Input low-level voltage   | VIL             |                        |                        |     | 0.3 V <sub>DD</sub>    | V    |

| Output high-level voltage | V <sub>OH</sub> | $I_{OH} = -1 \ \mu A$  | V <sub>DD</sub> - 0.05 |     |                        | V    |

| Output low-level voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 1 μA |                        |     | V <sub>SS</sub> + 0.05 | V    |

This LSI can easily use CCB that is SANYO's original bus format.

- CCB is a trademark of SANYO ELECTRIC CO., LTD.

- CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

SANYO Electric Co., Ltd. Semiconductor Bussiness Headquarters TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-0005 JAPAN

## **AC Characteristics**

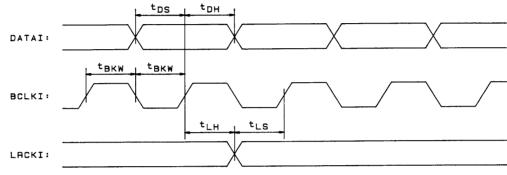

## 1. Audio data input

| Parameter         | Symbol           | Conditions | min | typ | max | Unit |

|-------------------|------------------|------------|-----|-----|-----|------|

| BCLKI pulse width | t <sub>BKW</sub> |            | 50  |     |     | ns   |

| DATAI setup time  | t <sub>DS</sub>  |            | 20  |     |     | ns   |

| DATAI hold time   | t <sub>DH</sub>  |            | 20  |     |     | ns   |

| LRCKI hold time   | t <sub>LH</sub>  |            | 25  |     |     | ns   |

| LRCKI setup time  | t <sub>LS</sub>  |            | 25  |     |     | ns   |

#### A04840

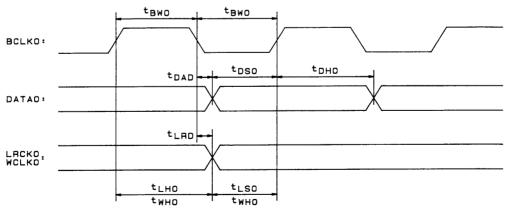

## 2. Audio data output

| Parameter               | Symbol           | Conditions | min | typ | max | Unit |

|-------------------------|------------------|------------|-----|-----|-----|------|

| BCLKO pulse width       | t <sub>BWO</sub> |            | 100 |     |     | ns   |

| DATAO output delay time | t <sub>DAD</sub> |            |     |     | 25  | ns   |

| DATAO setup time        | t <sub>DSO</sub> |            | 50  |     |     | ns   |

| DATAO hold time         | t <sub>DHO</sub> |            | 50  |     |     | ns   |

| LRCKO output delay time | t <sub>LRD</sub> |            |     |     | 25  | ns   |

| LRCKO setup time        | t <sub>LSO</sub> |            | 50  |     |     | ns   |

| LRCKO hold time         | tLHO             |            | 50  |     |     | ns   |

| WCLKO setup time        | twso             |            | 50  |     |     | ns   |

| WCLKO hold time         | t <sub>WHO</sub> |            | 50  |     |     | ns   |

A04841

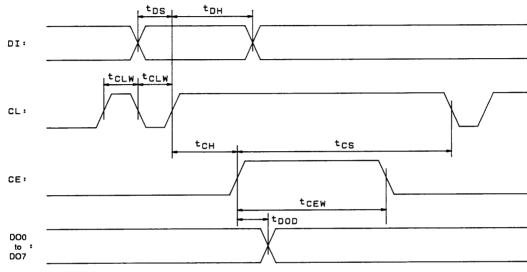

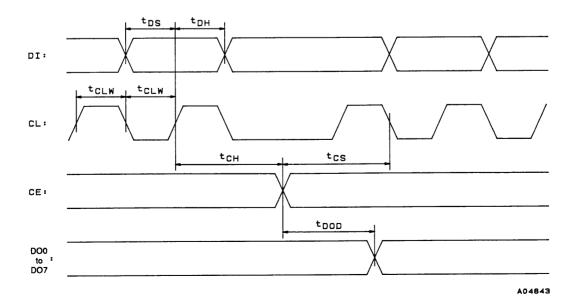

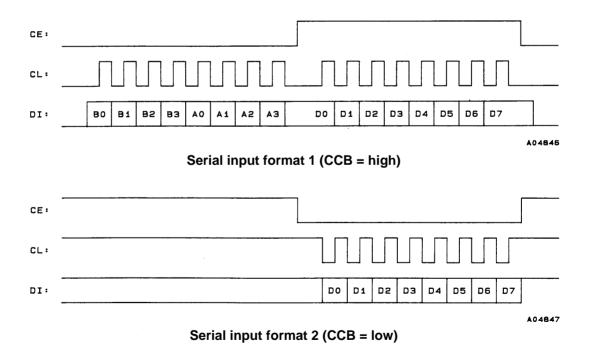

## 3. Serial input (CCB = low)

| Parameter                    | Symbol           | Conditions | min | typ | max | Unit |

|------------------------------|------------------|------------|-----|-----|-----|------|

| CL pulse width               | t <sub>CLW</sub> |            | 50  |     |     | ns   |

| DI setup time                | t <sub>DS</sub>  |            | 20  |     |     | ns   |

| DI hold time                 | t <sub>DH</sub>  |            | 20  |     |     | ns   |

| CE pulse width               | t <sub>CEW</sub> |            | 50  |     |     | ns   |

| CE setup time                | t <sub>CS</sub>  |            | 20  |     |     | ns   |

| CE hold time                 | t <sub>CH</sub>  |            | 20  |     |     | ns   |

| DO0 to DO7 output delay time | t <sub>DOD</sub> |            |     |     | 25  | ns   |

A04842

## 4. Serial input (CCB = high)

| Parameter                                                      | Symbol           | Conditions | min | typ | max | Unit |

|----------------------------------------------------------------|------------------|------------|-----|-----|-----|------|

| CL pulse width                                                 | t <sub>CLW</sub> |            | 50  |     |     | ns   |

| DI setup time                                                  | t <sub>DS</sub>  |            | 20  |     |     | ns   |

| DI hold time                                                   | t <sub>DH</sub>  |            | 20  |     |     | ns   |

| CE setup time                                                  | t <sub>CS</sub>  |            | 20  |     |     | ns   |

| CE hold time                                                   | t <sub>CH</sub>  |            | 20  |     |     | ns   |

| DO0 to DO7 output delay time<br>with respect to the rise of CE | t <sub>DOD</sub> |            |     |     | 25  | ns   |

#### 24 000 мск2 37 D01 AVDD 23 Эв D02 AVDD 22 39 21 DOB MUTE 40 FSEL3 20 D04 19 DVDD TEST1 42 LC78845Q 18 DGND DVDD 43 D05 17 ססעם 44 FSEL2 16 D06 45 15 D07 FSEL1 46 DI 14 TEST2 CL TEST3 48 13 11 AKSEL 1 2 з 4 5 6 7 8 9 10 12 DATAI INITB ۵۷۵D MCK1 BCLKI DGND DGND LRCKI CCB SPSEL ц

Although the DV<sub>DD</sub> and AV<sub>DD</sub> pins in this IC are given different names to correspond to the internal circuit structure, they are connected internally through the circuit substrate. As a result, if different voltages are applied to these pins, abnormal currents will flow in the chip. Since this can cause latchup, power supplies with identical voltages and identical power-on timings must be used.

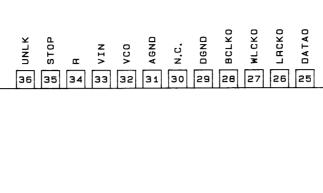

## **Pin Functions**

**Pin Assignment**

| Pin No. | Symbol           | Overview                          | Function                                                                                                                                                   |

|---------|------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | MKSEL            | DF master clock selection         | Low: 384fs, high: 512fs                                                                                                                                    |

| 2       | INITB            | Reset input                       | Low: initialization operation                                                                                                                              |

| 3       | MCK1             | DF master clock input             |                                                                                                                                                            |

| 4       | BCLKI            | Audio signal input                | Audio signal bit clock input pin                                                                                                                           |

| 5       | DGND             | Digital system ground             |                                                                                                                                                            |

| 6       | DGND             | Digital system ground             |                                                                                                                                                            |

| 7       | DV <sub>DD</sub> | Digital system power supply       |                                                                                                                                                            |

| 8<br>9  | LRCKI<br>DATAI   | Audio signal input                | Audio signal left/right clock and data input pins                                                                                                          |

| 10      | ССВ              | Serial input format specification | Selects the input format for data from the microprocessor input pins.                                                                                      |

| 11      | SPSEL            | Serial/parallel control           | Allows certain of the setting pins to be set from serial data over the microprocessor interface.<br>Low: serial, high: parallel (states set by input pins) |

Continued on next page.

Top view

A04838

Continued from preceding page.

| Pin No. | Symbol           | Overview                     | Function                                                                 |

|---------|------------------|------------------------------|--------------------------------------------------------------------------|

| 12      | CE               |                              | Data enable signal input                                                 |

| 13      | CL               | Microprocessor input pins    | Shift clock input                                                        |

| 14      | DI               |                              | Address/data input                                                       |

| 15      | DO7              |                              |                                                                          |

| 16      | DO6              | Parallel data output         | Output of 8-bit parallel data according to microprocessor input          |

| 17      | DO5              |                              |                                                                          |

| 18      | DGND             | Digital system ground        |                                                                          |

| 19      | DV <sub>DD</sub> | Digital system power supply  |                                                                          |

| 20      | DO4              |                              |                                                                          |

| 21      | DO3              |                              |                                                                          |

| 22      | DO2              | Parallel data output         | Output of 8-bit parallel data according to microprocessor input          |

| 23      | DO1              |                              |                                                                          |

| 24      | DO0              |                              |                                                                          |

| 25      | DATAO            |                              |                                                                          |

| 26      | LRCKO            | Audio signal output          | Audio signal outputs (data, left/right clock, word clock, and bit clock) |

| 27      | WCLKO            |                              |                                                                          |

| 28      | BCLKO            |                              |                                                                          |

| 29      | DGND             | Digital system ground        |                                                                          |

| 30      | N.C              | _                            |                                                                          |

| 31      | AGND             | Analog system ground         |                                                                          |

| 32      | VCO              | PLL control                  | Low-pass filter connection                                               |

| 33      | VIN              | PLL control                  | Free-running setting                                                     |

| 34      | R                | PLL control                  | VCO band adjustment                                                      |

| 35      | STOP             | Oscillator stop signal input | Low: oscillator stopped, high: PLL running                               |

| 36      | UNLK             | Unlock detection output      | Outputs a high level when the PLL circuit is unlocked.                   |

| 37      | MCK2             | Synchronization clock output | Outputs the clock generated by the VCO.                                  |

| 38      | AV <sub>DD</sub> | Analog system power supply   |                                                                          |

| 39      | AV <sub>DD</sub> | Analog system power supply   |                                                                          |

| 40      | MUTE             | Muting                       | Low: muting off, high: muting on                                         |

| 41      | FSEL3            | Output data fs selection     | Low: fs data, high: 2fs data                                             |

| 42      | TEST1            | Test pin                     | Must be held low during normal operation.                                |

| 43      | DV <sub>DD</sub> | Digital system power supply  |                                                                          |

| 44      | DV <sub>DD</sub> | Digital system power supply  |                                                                          |

| 45      | FSEL2            |                              |                                                                          |

| 46      | FSEL1            | Input signal fs selection    | Selects the fs for the input signal.                                     |

| 47      | TEST2            | Testaine                     | Must be held buy during a sum 1                                          |

| 48      | TEST3            | Test pins                    | Must be held low during normal operation.                                |

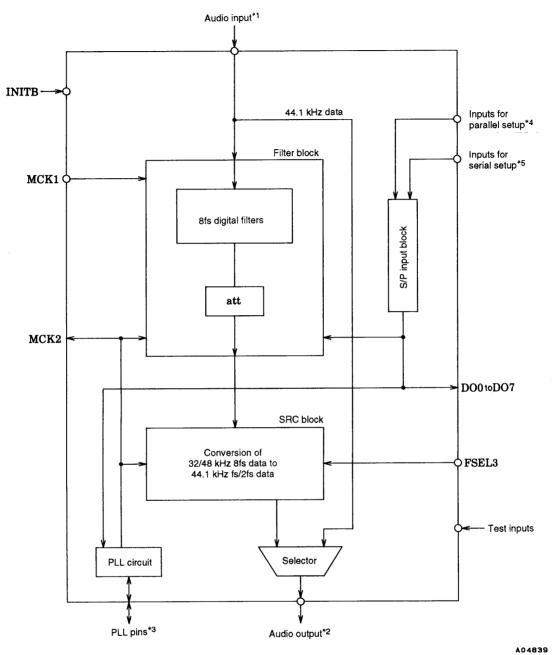

#### **Block Diagram**

- Note: 1. BCLKI, LRCKI, DATAI 2. BCLKO, LRCKO, DATAO, WCLKO

- 3. R, VIN, VCO, UNLK

- MKSEL, FSEL1, FSEL2, MUTE, STOP

CCB, SPSEL, CE, CL, DI

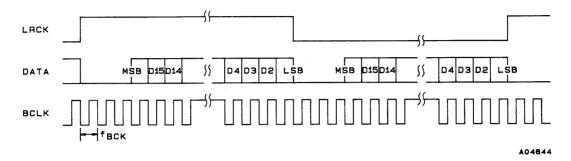

## **Input and Output Formats**

1. Input format

Audio data is input through the audio data input pins (BCLKI, LRCKI, and DATAI) in the following format. MKSEL = L:  $f_{BCK} = 48$ fs

MKSEL = H:  $f_{BCK} = 64$ fs

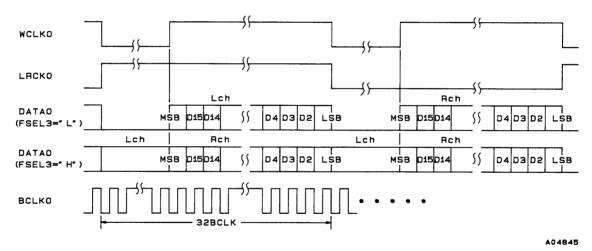

2. Output format 1

Audio data is output through the audio data output pins (BCLKO, WCLKO, LRCKO, and DATAO) in the following format.

BCLKO = 64fs (fixed) LRCKO = fs (fixed)

WCLKO = 2fs (fixed)

Output format 2 (When the input fs is 44.1 kHz) When data sampled at 44.1 kHz is input, that data is output directly without change. The WCLKO output is held low in this case.

## **Pin Settings**

Input master clock setup (when SPSEL is high) Input the master clock for the internal digital filters to MCK1 (pin 3). Also, set whether that clock is 384fs or 512fs with MKSEL (pin 1).

| Pin   | L     | Н     |

|-------|-------|-------|

| MKSEL | 384fs | 512fs |

2. Input data fs setting (when SPSEL is high)

The input data sampling frequency must be set. FSEL1 and FSEL2 (pins 46 and 45) are used for this setting. Data sampled at a 32 or 48 kHz sampling frequency is converted to data with a 44.1 kHz sampling frequency. If data sampled at 44.1 kHz is input, it is passed through unchanged.

| Sampling frequency | FSEL1 | FSEL2 |

|--------------------|-------|-------|

| 44.1 kHz           | 0     | ×     |

| 48 kHz             | 1     | 0     |

| 32 kHz             | 1     | 1     |

## 3. Output data setup

The output data can be switched between fs and 2fs. FSEL3 (pin 41) is used to change this setting.

| Pin   | L  | Н   |

|-------|----|-----|

| FSEL3 | fs | 2fs |

#### 4. Setup from serial input

The MKSEL, FSEL1, FSEL2, MUTE, and STOP settings can be set using the serial bus by setting SPSEL (pin 11) low. The 8 bits of input data is output in parallel regardless of the SPSEL setting.

| INITB = H<br>SPSEL = L | INITB = L                                                                |

|------------------------|--------------------------------------------------------------------------|

| LSI selection          | _                                                                        |

| Address                | —                                                                        |

| MKSEL                  | L                                                                        |

| FSEL1                  | L                                                                        |

| FSEL2                  | L                                                                        |

| MUTE                   | н                                                                        |

| STOP                   | L                                                                        |

| —                      | н                                                                        |

|                        | SPSEL = L<br>LSI selection<br>Address<br>MKSEL<br>FSEL1<br>FSEL2<br>MUTE |

| Address  |    |    |    |            |    |    |    |    |    |  |

|----------|----|----|----|------------|----|----|----|----|----|--|

| LS       | SB |    |    |            |    |    |    | MS | SB |  |

|          | B0 | B1 | B2 | <b>B</b> 3 | A0 | A1 | A2 | A3 |    |  |

|          | 0  | 0  | 1  | 0          | 0  | 1  | 1  | 1  |    |  |

| HEX : E4 |    |    |    |            |    |    |    |    |    |  |

The data and the signals correspond as listed in the tables. Since the external pins (MKSEL etc.) set by the serial input are unused, applications must assure that these pins do not become floating. If initialization is performed, set the initial values listed in the table.

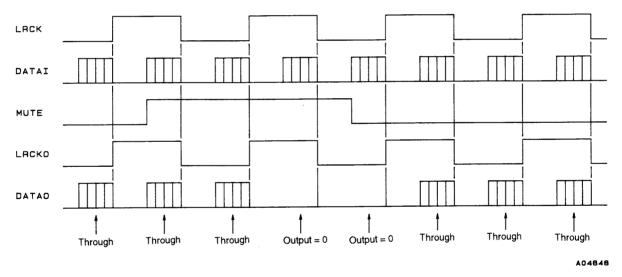

#### 5. Muting

A soft muting function is applied to the data if the MUTE pin (pin 40) is set high when data with a 32 or 48 kHz sampling frequency is input. The input signal values are gradually attenuated so that the data reaches  $-\infty$  1024/fs (seconds) later. When the soft muting function is turned off, the amplitude becomes the same as that of the input 1024/fs (seconds) later.

For input data with a 44.1 sampling frequency, the data is forcibly set to 0 on the next rising edge of the LRCK signal after the MUTE signal goes from low to high. Similarly, data is output on the next rising edge of the LRCK signal after the MUTE signal goes from high to low.

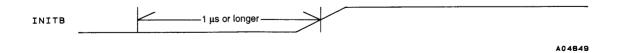

6. Initialization

When power is first applied, the LSI must be initialized when the pin settings are changed. Initialization is performed by holding INITB (pin 2) low for at least 1 µs in the state where the MCK1 signal is input after the power supply voltage has stabilized.

7. PLL block

The PLL block generates a 14.112 MHz master clock (MCK2) that is used for all three frequencies; 32, 44.1, and 48 kHz, when either 32 or 48 kHz is specified as the input data sampling frequency.

• STOP pin setting

| STOP | Function            |  |

|------|---------------------|--|

| L    | The VCO is stopped. |  |

| Н    | The VCO operates.   |  |

• UNLK pin

| UNLK | Function                                                 |  |  |  |

|------|----------------------------------------------------------|--|--|--|

| L    | Indicates that the PLL circuit is locked.                |  |  |  |

| Н    | Indicates that the PLL circuit is in the unlocked state. |  |  |  |

The UNLK pin is high during unlocked periods and during the 1024/fs (seconds) required for the unlocked to locked transition. The LSI performs the same processing during the locked to unlocked transition as it does when MUTE is high.

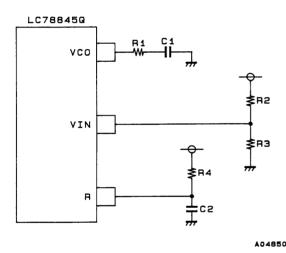

• External circuits

| Symbol | Value | Unit |  |

|--------|-------|------|--|

| R1     | 150   | Ω    |  |

| R2     | 5.1 k |      |  |

| R3     | 5.1 k |      |  |

| R4     | 24 k  |      |  |

| C1     | 0.02  | μF   |  |

| C2     | 0.1   |      |  |

- No products described or contained herein are intended for use in surgical implants, life-support systems, aerospace equipment, nuclear power control systems, vehicles, disaster/crime-prevention equipment and the like, the failure of which may directly or indirectly cause injury, death or property loss.

- Anyone purchasing any products described or contained herein for an above-mentioned use shall:

- ① Accept full responsibility and indemnify and defend SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors and all their officers and employees, jointly and severally, against any and all claims and litigation and all damages, cost and expenses associated with such use:

- ② Not impose any responsibility for any fault or negligence which may be cited in any such claim or litigation on SANYO ELECTRIC CO., LTD., its affiliates, subsidiaries and distributors or any of their officers and employees jointly or severally.

- Information (including circuit diagrams and circuit parameters) herein is for example only; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of February, 1996. Specifications and information herein are subject to change without notice.