# ASCell3912 ISM 868 MHz, 433 MHz and 315 MHz FSK Receiver Cell

**Preliminary Data Sheet**

## **Key Features**

- Supports triple band operation: Europe 868 MHz and 433 MHz-, US and Japan 315 MHz ISM band.

- Designed to be conform to EN 300 220, and FCC 47 CFR Ch.1 par.15 requirements.

- Provides highly reliable packet oriented data transmission in blocks of 128 bit.

- Event oriented single message transmission and status oriented and continuous message transmission supported.

- Special transmission protocol for high reliability even in presence of burst interferer (e.g. GSM) implemented.

- RX sensitivity of the receiver typical -100 dBm.

- Supports clock for an external μC and allows clock free total shut down of the whole system.

- Wide supply range between 2.7 to 5.5 V.

- Low RX current, typical 10 mA @ 2.4 V.

- Low idle mode current, typical 1.2mA.

- Wide operating temperature range from -40 °C to +85 °C.

- Only a low cost XTAL for 25 ppm (868 MHz) or 50 ppm (433 and 315 MHz) reference frequency tolerance required.

- Minimum only 1 XTAL and 4 capacitors externally required.

## **General Description**

The ASCell3912 is a low power, triple ISM band (868 / 433 / 315 MHz), single channel FSK receiver designed to work in a remote control link together with the SC3911 transmitter system cell.

The ASCell3912 performs packet oriented data transmission, in a single message- or continuosmessage mode using a special protocol to ensure high reliability even in presence of strong pulsed interferers in close adjacent bands like e.g. GSM.

A general bi-directional micro-controller ( $\mu$ C) interface is provided, to support the  $\mu$ C with clockand reset- signal, and to operate the highly efficient power up/down management.

As external components the SC3911 need at minimum only a reference XTAL, and 4 capacitors.

## **Applications**

- Key-less car entry systems.

- Short range packet oriented data transmission.

- Security applications and alarm systems.

- Domestic remote control systems.

- Industrial remote control systems.

- Remote metering.

Rev. A, February 2000 Page 2 of 14

This document contains information on products under development. Austria Mikro Systeme International AG reserves the right to change or discontinue this product without notice.

## 1 Functional Description

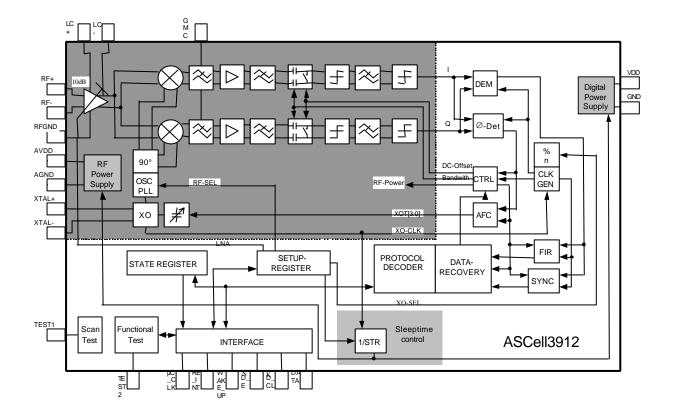

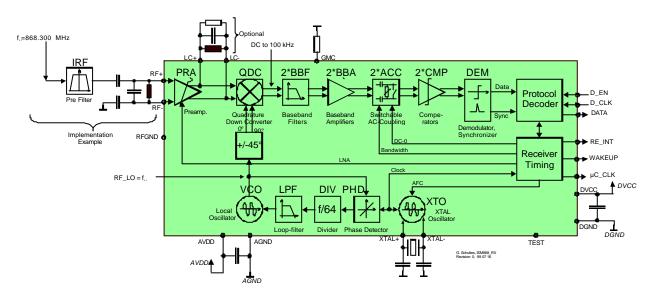

The Figure 1 shows the block diagram of the ASCell3912. The analog part of the ASCell3912 consists of a direct conversion receiver, a triple band RF synthesizer and the DC-cancellation. The digital part includes the burst interference resistant protocol decoder the control logic and the  $\mu$ C interface.

Figure 1: Block diagram of the ASCell3912.

Rev. A, February 2000 Page 3 of 14

#### 1.1 Analog Receiver Part

The input signal is a low to moderately high modulation index continuous phase frequency shift keying modulated RF signal around a carrier Fc. This signal is amplified by the low noise amplifier (LNA) and fed to the In-phase and Quadrature-phase mixers (I/Q mixers). The mixers convert the RF signal directly to base band. The local oscillator signal for the I/Q mixers is generated by the on-chip PLL.

The two base band signals (signals I and Q) are filtered and further amplified. After DC offset cancellation to remove the static and quasi-static DC offsets and to ensure fast wake-up of the receiver, the signals are hard limited. The rectangular signals I' and Q' are fed to the digital part where demodulation and the further signal processing is applied.

#### 1.1.1 RF Synthesizer

Frequency synthesis is performed by a conventional synthesizer consisting of a phase detector, a charge pump, a voltage controlled oscillator working at 315~868.3 MHz, and a feedback divider by 16 (315.00MHz); 32 (315, 433.92MHz), or 64 (868.3MHz). A truth table for the different frequencies is given in Table 1.

| F <sub>XOSC</sub> / MHz | Multiplier | F <sub>C</sub> / MHz | FB1 | FB0 | RF-SEL | XO-SEL |

|-------------------------|------------|----------------------|-----|-----|--------|--------|

| 19,6875                 | 16         | 315.000              | Н   | L   | L      | L      |

| 13.5600                 | 32         | 433.920              | L   | Н   | L      | Н      |

| 13.5672                 | 64         | 868.300              | L   | L   | Н      | Н      |

Table 1: Quartz and RF output frequencies.

Note: XO-SEL and RF-SEL are intenal generated Signals from the FB[1:0] bits of the setup information.

#### 1.1.2 LNA

The amplification of the LNA can be switched in two states. The gain can be switched of about 10dB with the LNA bit of the setup command.

Note: LNA is one bit of the setup information.

#### 1.1.3 I/Q Down Converter

The ASCell3912 contains a high performance quadrature down converter with low DC offset and high isolation of RF- and LO-ports.

#### 1.1.4 Base Band Filter

To achieve optimum blocking performance, the base band filter is realized in two separated circuit blocks. The first filter block removes high level blocking signals out of receive band, the second filter block serves for high selectivity of adjacent interferers.

#### 1.1.5 DC-Cancellation and Adjustment of Lower Cut-Off Frequency

The DC offset is removed by a first order high-pass with switchable limit frequency. In the first step the frequency offset of transmitter and receiver is not compensated, therefore the lower band limit is about 10 kHz. In the second step, the receiver frequency is adjusted and the lower limit frequency of the DC-block is set to about 40 kHz and therefore the total bandwidth of pass band is reduced. At the output of the DC block is a switch to initialize the DC-offset in the power-up instant, at the instant of switching, and after appearance of high level interfering signals.

Rev. A, February 2000 Page 4 of 14

#### 1.2 Digital Controller

The principal function of the digital controller is demodulation, bit synchronization and the detection of the received data protocol, according to the definition of transmitted bits. Furthermore, a first syntax check and plausibility check of detected data is provided. A data protocol received completely is put into a receive buffer, where a micro controller ( $\mu$ C) can read it out via a serial interface.

The receiver can be externally configured with several operation parameters, LNA gain setting, used frequency band, and timing constant for the watch dog timer. The serial interface also allows to configure the digital controller by the  $\mu$ C.

The receiver writes the state information into a status register. This status information can be read out from the  $\mu$ C out of the status register of the receiver.

#### 1.2.1 Microprocessor Clock

The microprocessor clock frequency  $F_{CLK}$  is generated by dividing the XTAL frequency  $F_{XOSC}$  by 4 if XO-SEL is 'H' and by dividing the XTAL frequency  $F_{XOSC}$  by 6 if XO-SEL is 'L'.

Note: XO-SEL and RF-SEL are internal generated signals from the FB[1:0] bits of the setup information.

#### 1.2.2 ASCell3912 Digital Part Timing

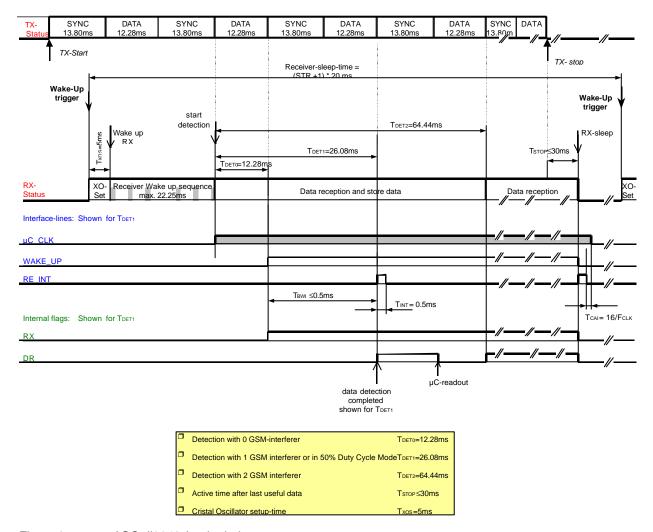

In Figure 2 the timing of a complete receive sequence can be seen. Transmission starts at an arbitrary point in time. First the crystal oscillator is switched on. A minimum time of 5 ms is allowed for the frequency to settle to the final value. Then the receiver executes a wake-up sequence consisting of 6 wake-up bursts. The wake-up bursts are unequally spaced to guarantee interference free detection of an ongoing transmission also in the presence of burst interferers. During a wake-up burst the receiver scans for an active transmission on the air interface. The wake-up sequence is optimized to combat GSM and CT2 type interferers.

After an ongoing transmission has been detected the receiver goes to receiving mode, the WAKE\_UP line goes high, and reception of data starts. Depending on the number of interferers present, reception of all data may take up to 3 data blocks. As soon as all data has been detected successfully, the RE\_INT pin issues a positive pulse, to indicate the availability of data, and the internal data ready flag (DR) in the ASCell3912 state register is set. The RE\_INT line may be used to trigger a interrupt procedure, which is executed at the availability of data. When data is read out by the micro controller the internal data ready flag (DR) in the RX-status register is cleared and it is only set, when a complete data sequence has received again. No further pulse is issued on the RE\_INT line, but the micro controller has to poll for new data during an ongoing reception. If transmission stops, the WAKE\_UP line goes low and a pulse is issued on the RE\_INT line to indicate the termination of transmission at CMT.

In Figure 2 also the timing where the microprocessor clock (µC\_CLK) is active is shown. The clock is active with the start of the detection phase of the SC3911. The clock is shut down 16 clock cycles (T<sub>CAI</sub>) after the falling edge of the second interrupt on the RE\_INT pin.

Rev. A, February 2000 Page 5 of 14

Figure 2: ASCell3912 basic timing.

Note: The Interface timing and the timing of the internal flags are shown in Figure 2 for a detection time of T<sub>DET1</sub>.

#### 1.2.3 Receiver Configuration

The configuration register can be loaded from a  $\mu$ C via the serial interface. The Table 2 below shows the contents of the configuration register. Bit b0 is the first transmitted bit. The setup contains the LNA set, frequency band and the sleep time interval of the receiver.

| bit # | Name     | Description                                                     | Configuration                                                                         | Comments                                                                                      |

|-------|----------|-----------------------------------------------------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| 0     | LNA      | LNA gain switch                                                 | L= LNA Gain is high<br>H= LNA Gain is -10dB                                           | default                                                                                       |

| [12]  | FB[1:0]  | Frequency band select with FB1 is MSB                           | L, L (FB1, FB0) = 868.3 MHz<br>L, H = 433.92 MHz<br>H, L = 315 MHz<br>H, H = not used | default                                                                                       |

| [38]  | STR[5:0] | Sleep time interval set of<br>the receiver, with STR5 is<br>MSB | t <sub>sleep</sub> = (STR + 1) * 20ms                                                 | Note: for STR = 00h the witing period between two consecutive wake-up cycles will be 148 bit. |

Table 2: Format of the configuration Register

Rev. A, February 2000 Page 6 of 14

#### 1.2.4 Receiver Status

Table 3 below shows the format of the state register. Bit b0 is the first which is transmitted by a readout of the  $\mu$ C. The status register contains the information about a successful received date, active receiver and the information about the quality of the received signal.

| bit # | Name    | Description                                                                                    | Status                                                                                | Comments                                                                                                                                                                                        |

|-------|---------|------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | DR      | Data received a complete message was received                                                  | L= no data received<br>H= data received successfully                                  |                                                                                                                                                                                                 |

| 1     | RX      | Receiver is active                                                                             | L= receiver not active H= data reception in progress                                  | Note: This bit is set by the receiver when 6 bytes of a packet are correct. This bit in the status register is necessary for the comfort-orientated functions of the central locking functions. |

| [23]  | RQ[1:0] | Signal quality indicates<br>how many data packets<br>are necessary for a com-<br>plete message | L, L (RQ1, RQ0) = 1 packet<br>L, H = 2 packets<br>H, L = 3 packets<br>H, H =4 packets |                                                                                                                                                                                                 |

Table 3: Format of the status register.

#### 1.2.5 µC Interface

The ASCell3912 contains a direct interface to a micro controller ( $\mu$ C). The  $\mu$ C interface of the ASCell3912 consist of the following five pins:

"Transmit/Received data input/output" (DATA). A bi-directional serial data line, with states "H" (recessive, or weak pull-up) and "L" (dominant).

"Active "H" transmit data enable" (D\_EN)

"Transmit data clock input" (D CLK).

"Active "H" µC interrupt output " (RE\_INT).

"Active "H" µC wakeup output " (µC\_WAKEUP).

"μC clock output " (μC\_CLK).

#### 1.2.5.1 Instruction Set

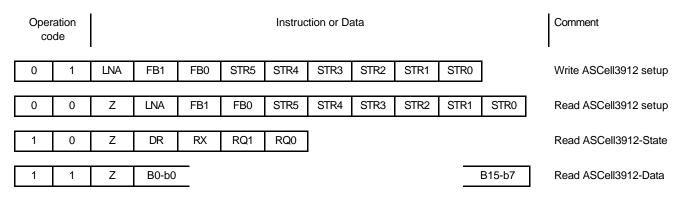

The following table shows the instruction set of the interface. The first two bits are the operation code, which determine the direction of the data transfer and which data is transferred.

Table 4: Overview of the instruction set.

Rev. A, February 2000 Page 7 of 14

#### 1.2.6 Timing Diagrams

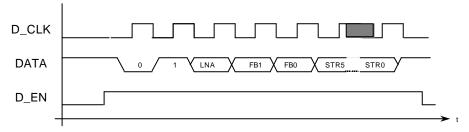

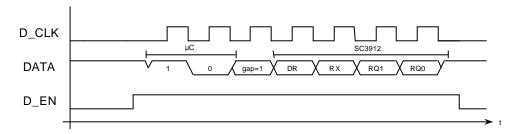

The following Figure 3 shows the timing for the write operation into the configuration register. First the opcode is transmitted and it is followed by 9 instruction bits.

Figure 3: Write timing for the configuration register..

The following Figure 4 shows the timing of a read operation from the status register. After writing the operation code to the ASCell3912, the ASCell3912 stays in high impedance state for one more clock cycle and starts transmission of the selected bit sequence after that period.

Figure 4: Read timing for status register.

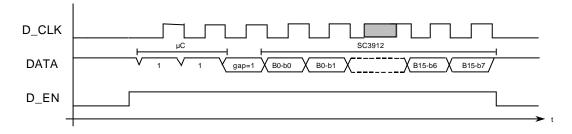

In the following Figure 5 shows read out of the received data. In the example `Bx-bz` stands for bit 'z' of Byte 'y', so B7-b5 depicts bit 5 of byte 7.

Figure 5: Read out timing for received data (16 Bytes).

#### 1.2.7 Interrupt and Wake-Up Pins

To provide the micro controller with time-critical information the receive/end transmission interrupt (RE\_INT) line is used. Figure 2 shows the timing of the RE\_INT and WAKE\_UP signals during the reception. A high pulse is issued on this line, when one of the both conditions appear:

- The reception of data is completed for the first time after a receiver wake-up.

- The transmission of data has stopped. This interrupt is necessary status oriented CMT for comfort orientated central locking functions (like window closing).

Rev. A, February 2000 Page 8 of 14

To distinguish between the two interrupt sources, the WAKE\_UP line is used, as listed in the following table.

| RE_INT | WAKE_UP | Interrupt source            |

|--------|---------|-----------------------------|

| 0→1    | 1       | Message received completely |

| 0→1    | 0       | Transmission stopped        |

Table 5: Interrupt sources and their meaning.

## 2 Electrical Characteristics

## Absolute Maximum Ratings (non operating)

| Symbol    | Parameter                                     | Min     | Max     | Units | Note  |

|-----------|-----------------------------------------------|---------|---------|-------|-------|

| VDD; AVDD | Positive supply voltage                       | -0.5    | 6       | V     |       |

| GND; AGND | Negative supply voltage                       | 0       | 0       | V     |       |

| Vin       | Voltage at every input pin                    | Gnd-0.5 | VCC+0.5 | V     |       |

| lin       | Input current into any pin except supply pins | -10     | 10      | mA    |       |

| ESD       | Electrostatic discharge                       |         | 1k      | V     | 1) 3) |

| Tstg      | Storage temperature                           | -55     | 125     | °C    |       |

| Tlead     | Lead temperature                              |         | 260     | °C    | 2)    |

<sup>1)</sup> Test according to MIL STD 883C, Method 3015.7: HBM: R=1.5 kΩ, C=100 pF, 5 positive pulses per pin against supply pins, 5 negative pulses per pin against supply pins [C2].

#### **Operating Conditions**

| Symbol              | Parameter                             | Conditions / Notes                                    | Min | Тур | Max | Units |

|---------------------|---------------------------------------|-------------------------------------------------------|-----|-----|-----|-------|

| VDD=AVDD            | Positive supply voltage               |                                                       | 2.7 |     | 5.5 | V     |

| GND=AGND            | Negative supply voltage               |                                                       | 0   | 0   | 0   | V     |

| TA                  | Operating temperature                 |                                                       | -40 |     | +85 | °C.   |

| IP <sub>run</sub>   | Supply current into VDDA and VDDD pin | Everything on                                         |     |     | 10  | mA    |

| IP <sub>idle</sub>  | Average supply current in idle mode.  |                                                       |     |     | 1.2 | mA    |

| IP <sub>sleep</sub> | Average supply current in sleep mode. |                                                       |     |     | 0,5 | μA    |

| P <sub>in,max</sub> | Maximum input power level             | Above this level cir-<br>cuit could be de-<br>stroyed |     | 30  |     | dBm   |

Rev. A, February 2000 Page 9 of 14

<sup>2) 260 °</sup>C for 10 sec (Reflow and Wave Soldering), 360 °C for 3 sec (Manual soldering).

<sup>3)</sup> All pins, pins XTAL+,XTAL-, RF+,RF-,LC+ and LC- have 500 V ESD protection

#### 2.3 Receiver Operation

TA = 23 °C, VDD, AVDD = 3.6 V, unless specified otherwise. Devive functional for TA = -40 to +85 °C.

| Symbol                             | Parameter                                                 | Conditions / Notes                                                                     | Min | Тур                           | Max            | Units             |

|------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------|-----|-------------------------------|----------------|-------------------|

| F <sub>C</sub>                     | Carrier Frequency                                         | Depends on different external crystals.                                                |     | 315.000<br>433.920<br>868.300 |                | MHz<br>MHz<br>MHz |

| R <sub>in</sub>                    | Input impedance                                           | Capacitive part t.b.d.                                                                 |     | 200~ 400                      |                | Ω                 |

| ? F                                | Nominal FSK frequency deviation                           | 315, 433.92, 868.3MHz                                                                  | 61  |                               | 69             | kHz               |

| F <sub>xosc</sub>                  | Crystal oscillator (XOSC) frequency                       | 315,000 MHz: max +/- 50ppm<br>433.920 MHz: max +/- 50ppm<br>868.300 MHz: max +/-25ppm  |     | 19,6875<br>13.5600<br>13.5672 |                | MHz<br>MHz<br>MHz |

| TF <sub>xosc</sub>                 | Crystal oscillator (XOSC) frequency tolerance             | 315,000 MHz: (-40~+85 °C),<br>433.920 MHz: (-40~+85 °C),<br>868.300 MHz: (-40~+85 °C). |     |                               | 50<br>50<br>25 | ppm<br>ppm<br>ppm |

| $D_{R,gross}$                      | Gross Data Rate                                           | Including protocol.                                                                    |     | 18.235                        |                | kbps              |

| RF <sub>Sens</sub> 1)              | Receiver sensitivity                                      | -10 °C <ta<+70 td="" °c<=""><td>-96</td><td>-100</td><td></td><td>dBm</td></ta<+70>    | -96 | -100                          |                | dBm               |

| RF <sub>SensT</sub>                | Temperature sensitivity reduction                         | -40 <ta<-10 or<br="" °c.="">+70&gt;TA&gt;+85 °C.</ta<-10>                              |     |                               | 4              | dB                |

| $RF_{Sens}F_{offim}$               | Receiver sensitivity reduction caused by frequency offset | @maximum receiver sensitivity reduction @ 44 kHz offset                                |     |                               | 7              | dB                |

| RF <sub>SensLNA</sub>              | Sensitivity reduction caused by LNA gain switching        |                                                                                        |     | 10                            |                | dB                |

| BI <sub>200KHz</sub> <sup>2)</sup> | Blocking immunity<br>200 kHz – 1 MHz                      | Without external filter.                                                               | 0   |                               |                | dB                |

| BI <sub>1MHz</sub> <sup>2)</sup>   | Blocking immunity<br>1-10 MHz                             | Without external filter                                                                | 21  |                               |                | dB                |

| BI <sub>10MHz</sub> <sup>2)</sup>  | Blocking immunity @ >10 MHz                               | Without external filter                                                                | 63  |                               |                | dB                |

| P <sub>LOfeed</sub>                | LO @ F <sub>C</sub> power available at LC+ and LC- nodes  |                                                                                        |     |                               | -28            | dBm               |

Standard Receive Quality (SRQ): Message reception successfully finished after <80 ms in 80% of all transmission trails.

## **Receiver Timing**

| Symbol            | Parameter                 | Conditions / Notes                                     | Min | Тур | Max | Units |

|-------------------|---------------------------|--------------------------------------------------------|-----|-----|-----|-------|

| $T_{Dni}$         | Time to received FSK data | Configured for fast response (receiver sleep time = 0) | 27  |     | 80  | ms    |

| $T_Dwi$           | Time to received FSK data | Using low idle duty cycle the (receiver sleep time >0) | 40  |     | 92  | ms    |

| T <sub>stop</sub> | RX switch off time        | Timeout for comfort functions                          |     | 30  |     | ms    |

Rev. A, February 2000 Page 10 of 14

<sup>2)</sup> CW blocking signal relative to applied useful signal with –94dBm power level and SRQ. Measured without frequency offset and at +25 °C

## 2.5 Digital Pin Characteristics

$T_{AMB}$  = 23 °C, VDD = 3.6 V, unless specified otherwise. GND is the 0 V reference.

| Symbol                                               | Parameter                                                                                 | Conditions    | Min     | Тур | Max  | Units |  |  |  |  |

|------------------------------------------------------|-------------------------------------------------------------------------------------------|---------------|---------|-----|------|-------|--|--|--|--|

| μC_CLK (լ                                            | μC_CLK (μC clock output)                                                                  |               |         |     |      |       |  |  |  |  |

| VOH                                                  | High level output voltage                                                                 | IOH =-1 mA    | VDD-0.5 | -   |      | V     |  |  |  |  |

| VOL                                                  | Low level output voltage                                                                  | IOL =1 mA     |         | -   | 0.3  | V     |  |  |  |  |

| tr                                                   | Rise time                                                                                 | CLoad = 10 pF |         | 20  |      | ns    |  |  |  |  |

| td                                                   | Fall time                                                                                 | CLoad = 10 pF |         | 20  |      | ns    |  |  |  |  |

| jcc                                                  | Cycle to cycle jitter                                                                     |               |         |     | +/-5 | %     |  |  |  |  |

| DATA(ser                                             | DATA(serial data input), D_EN (serial data enable input), D_CLK (serial data clock input) |               |         |     |      |       |  |  |  |  |

| VIH                                                  | High level input voltage                                                                  |               | VDD-0.5 | -   |      | V     |  |  |  |  |

| VIL                                                  | Low level input voltage                                                                   |               |         | -   | 0.3  | V     |  |  |  |  |

| IIH                                                  | High level input current                                                                  | VIH= VDD      |         |     | 1    | μΑ    |  |  |  |  |

| IIL                                                  | Low level input current                                                                   | VIL =0 V      | -1      |     |      | μΑ    |  |  |  |  |

| F <sub>D_CLK</sub>                                   | D_CLK frequency                                                                           |               | 3       |     |      | kHz   |  |  |  |  |

| RE_INT (interrupt output); WAKEUP (μC wakeup output) |                                                                                           |               |         |     |      |       |  |  |  |  |

| VOH                                                  | High level output voltage                                                                 | IOH = -1mA    | VDD-0.5 | -   |      | V     |  |  |  |  |

| VOL                                                  | Low level output voltage                                                                  | IOL = 1mA     |         | -   | 0.3  | V     |  |  |  |  |

## 3 Pin-out Information

Note: pin numbers have arbitrary ordering and numbering - will be defined during design

| Pin | Name   | Туре | Description                                             |

|-----|--------|------|---------------------------------------------------------|

| 1   | RF+    | I    | LNA input                                               |

| 2   | RF-    | I    | LNA input                                               |

| 3   | LC+    | I/O  | LNA tank                                                |

| 4   | LC-    | I/O  | LNA tank                                                |

| 5   | XTAL+  | I    | XTAL oscillator input                                   |

| 6   | XTAL-  | 0    | XTAL oscillator output                                  |

| 7   | AVDD   | Р    | Analog positive supply                                  |

| 8   | AGND   | Р    | Analog negative supply                                  |

| 9   | GMC    | I/O  | Base-Band Low Pass frequency set                        |

| 10  | RFGND  | I    | RF GND                                                  |

| 11  | DGND   | Р    | Digital negative supply                                 |

| 12  | TEST1  | I/O  | pin for test purposes                                   |

| 13  | TEST2  | I/O  | pin for test purposes                                   |

| 14  | uC_CLK | 0    | Clock output for micro controller                       |

| 15  | RE_INT | 0    | Interrupt at first received data block and receive end  |

| 16  | WAKEUP | 0    | Micro controller wake up; high during ongoing reception |

Rev. A, February 2000 Page 11 of 14

| Pin | Name  | Туре | Description                              |

|-----|-------|------|------------------------------------------|

| 17  | D_EN  | 0    | Enable data bus                          |

| 18  | D_CLK | 1    | Clock for serial interface               |

| 19  | DATA  | I/O  | Data Input / Output for serial interface |

| 20  | DVDD  | Р    | Digital positive supply                  |

## 4 Application Schematic

Figure 6: Basic application schematic of the ASCell3912.

Rev. A, February 2000 Page 12 of 14

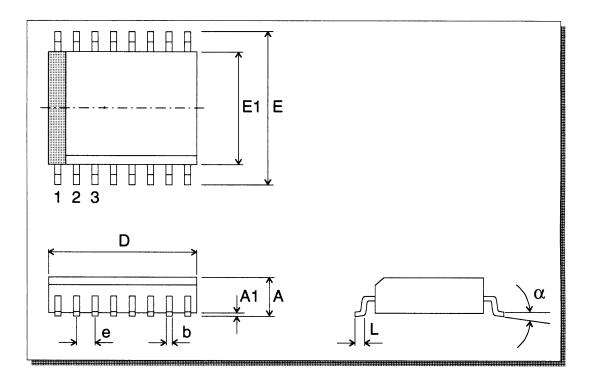

## 5 Package Information

Figure 7: Physical dimensions of TSSOP-20.

| Symbol | Common Dimensions |                  |                  |  |  |  |

|--------|-------------------|------------------|------------------|--|--|--|

|        | Minimal (mm/mil)  | Nominal (mm/mil) | Maximal (mm/mil) |  |  |  |

| А      | -                 | -                | 1.10/0.0433      |  |  |  |

| A1     | 0.05/0.002        | 0.10/0.004       | 0.15/0.006       |  |  |  |

| b      | 0.19/0.0075       | -                | 0.30/0.0118      |  |  |  |

| D      |                   |                  |                  |  |  |  |

| е      |                   | 0.65 BSC         |                  |  |  |  |

| E      | 6.25/0.246        | 6.40/0.252       | 6.50/0.256       |  |  |  |

| E1     | 4.30/0.169        | 4.40/0.173       | 4.50/0.177       |  |  |  |

| L      | 0.50/0.020        | 0.60/0.024       | 0.70/0.028       |  |  |  |

| ?      | 0°                | 4°               | 8°               |  |  |  |

ASCell's are functional and in-spec circuits, which are usually available as samples with documentation and demoboard. However they are intentionally to be used as a basis for ASIC derivatives. If an ASCell fits into a customer's application as it is, it will be immediately qualified and transfered to an ASSP to be ordered as a regular AS product.

Copyright © 2000, Austria Mikro Systeme International AG, Schloß Premstätten, 8141 Unterpremstätten, Austria. Telefon +43-(0)3136-500-0, Telefax +43-(0)3136-52501, E-Mail info@amsint.com

Rev. A, February 2000 Page 13 of 14

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing by the copyright holder. To the best of its knowledge, Austria Mikro Systeme International asserts that the information contained in this publication is accurate and correct.

Rev. A, February 2000 Page 14 of 14