# **OKI** Semiconductor

This version: Nov. 1997 Previous version: Mar. 1996

# MSM9005-xx

# DOT MATRIX LCD CONTROLLER WITH 8-DOT COMMON DRIVER AND 65-DOT SEGMENT DRIVER

#### **GENERAL DESCRIPTION**

The MSM9005-xx is a controller/driver which displays 13 alphanumerics and symbols (5x7 dots) and 65 arbitrators on a dot matrix LCD panel that has 8 common inputs and 65 segment inputs. Command and display data are written by 8-bit serial transfer.

A maximum of 256 types of alphanumerics and symbols can be displayed using an internal character display ROM. The character display ROM is reprogrammable. The general purpose code is -01.

## **FEATURES**

Logic power supply (V<sub>DD</sub>) : 2.5 to 5.5V

LCD bias power supply (V<sub>BI</sub>) : 4.0 to 8.0V

• LCD output resistance

Common driver (C1 to C8) :  $6 \text{ k}\Omega$ Segment driver (S1 to S65) :  $18 \text{ k}\Omega$

Display content

Number of display characters : 13 characters, 1 line

Arbitrator : 65 dots

Display control functions

Character blink : Characters all on or all off can be selected Arbitrator blink : 1-dot unit or 5-dot units can be selected

All off setting possible

• 5 interfaces with microcomputer, CS, SI, SO,  $C/\overline{D}$  and  $\overline{SHT}$  (6 interfaces if  $\overline{RST}$  is included)

• Internal character display ROM  $: 5 \times 7 \text{ dots} \times 256 \text{ types (reprogrammable)}$

• Internal oscillation circuit : External R, C

• Package:

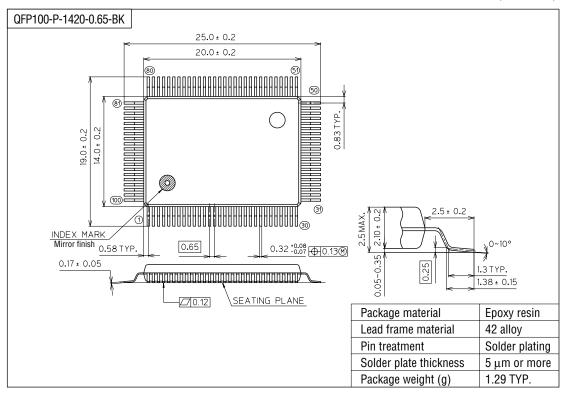

100-pin plastic QFP (QFP 100-P-1420-0.65-BK) (Product name: MSM9005-xxGS-BK)

xx indicates code number.

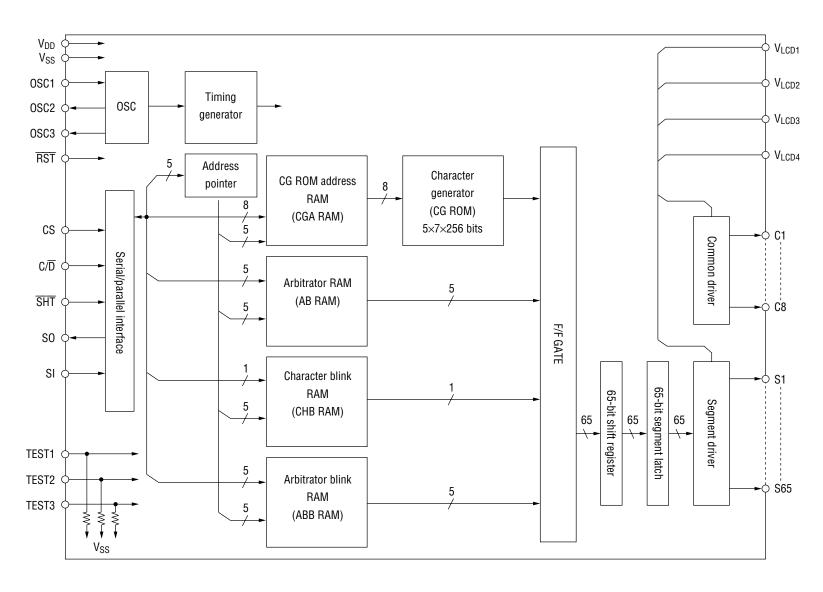

# **BLOCK DIAGRAM**

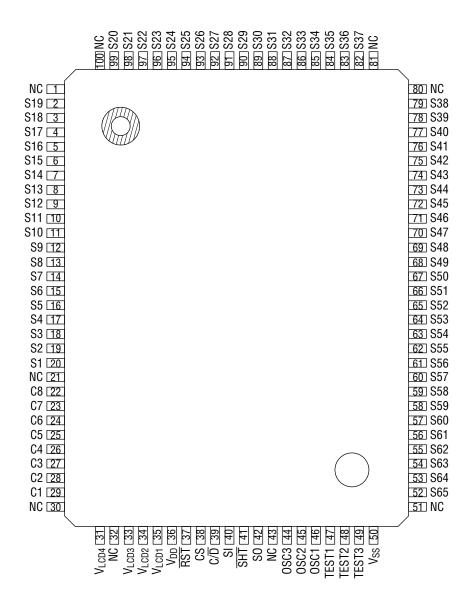

# **PIN CONFIGURATION (TOP VIEW)**

NC: No connection

100-Pin Plastic QFP

# **PIN DESCRIPTIONS**

| Pin                              | Symbol                  | Туре        | Connected to    | Description                                                                                                                                                                                                                                                                                                                            |

|----------------------------------|-------------------------|-------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2 to 20,<br>52 to 79<br>82 to 99 | S1 to S65               | 0           | LCD segment     | LCD segment outputs. Output resistance: ≤18 kΩ                                                                                                                                                                                                                                                                                         |

| 22 to 29                         | C1 to C8                | 0           | LCD common      | LCD common outputs. Output resistance: ≤6kΩ                                                                                                                                                                                                                                                                                            |

| 40                               | SI                      | I           | Microcontroller | Serial data input. Serial data is input through this pin in 8-bit units from the MSB side. For details on the configuration of input data, see "Command Configuration" and "Input Display Data Configuration".                                                                                                                         |

| 39                               | C/D                     | ı           | Microcontroller | Command/data select input. When this pin is at the "H" level, serial input data from SI is recognized as a command. When this pin is at the "L" level, serial input data from SI is recognized as display data.                                                                                                                        |

| 41                               | SHT                     | ı           | Microcontroller | Shift clock input. Data at SI and $C/\overline{D}$ pins are read synchronizing with the rising edge of this clock.  Display data is output to the SO pin synchronizing with the falling edge of this clock.                                                                                                                            |

| 42                               | \$0                     | I           | Microcontroller | Serial data output. This pin outputs display data. For details on the configuration of output data, see "Output Display Data Configuration". This pin can be set to high impedance by the SOE/D command.                                                                                                                               |

| 38                               | CS                      | ı           | Microcontroller | Chip select input. When this pin is at the "H" level, chip is selected, and command and display data can be transferred. When this pin is at the "L" level, SO output is set to high impedance, SHT input is set to the "H" level, and SI and C/D inputs are set to the "L" level, and command and display data transfer are disabled. |

| 37                               | RST                     | ı           | Microcontroller | Reset input. Setting this pin at the "L" level resets to initial status.                                                                                                                                                                                                                                                               |

| 47<br>48<br>49                   | TEST1<br>TEST2<br>TEST3 | ı           | _               | Test signal inputs. Set these pins to the same potential as $V_{SS}$ or unconnected. An error may occur by another setting.                                                                                                                                                                                                            |

| 46<br>45<br>44                   | 0SC1<br>0SC2<br>0SC3    | I<br>0<br>0 | _               | Pins for an 80 kHz RC oscillation circuit. Connect resistors and a capacitor as shown below.                                                                                                                                                                                                                                           |

| Pin                  | Symbol                                                                  | Туре | Connected to | Description                                                                                                                                                                                                                                                                                  |

|----------------------|-------------------------------------------------------------------------|------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36                   | $V_{DD}$                                                                |      |              | These are power pins. Set $V_{DD} = 2.5$ to 5.5V and $V_{SS} = 0$ V.                                                                                                                                                                                                                         |

| 50                   | V <sub>SS</sub>                                                         |      | _            |                                                                                                                                                                                                                                                                                              |

| 35<br>34<br>33<br>31 | V <sub>LCD1</sub> V <sub>LCD2</sub> V <sub>LCD3</sub> V <sub>LCD4</sub> | _    | _            | These are bias power pins for driving the LCD. Set the bias voltage as follows. $4\ V \leq V_{DD} - V_{LCD4} \leq 8\ V$ $V_{LCD1} = V_{DD} - \frac{1}{4}\ (V_{DD} - V_{LCD4})$ $V_{LCD2} = V_{DD} - \frac{2}{4}\ (V_{DD} - V_{LCD4})$ $V_{LCD3} = V_{DD} - \frac{3}{4}\ (V_{DD} - V_{LCD4})$ |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter            | Symbol            | Condition | Rating                                       | Unit |

|----------------------|-------------------|-----------|----------------------------------------------|------|

| Power Supply Voltage | V <sub>DD</sub>   | Ta=25°C   | -0.3 to +7.0                                 | V    |

| Bias Voltage         | V <sub>BI</sub>   | Ta=25°C   | V <sub>DD</sub> -10 to V <sub>DD</sub> +0.3  | V    |

| Innut Valtage        | VI                | Ta=25°C   | -0.3 to V <sub>DD</sub> +0.3                 | V    |

| Input Voltage        | V <sub>ILCD</sub> | Ta=25°C   | V <sub>BI</sub> -0.3 to V <sub>DD</sub> +0.3 | V    |

| Power Dissipation    | PD                | Ta=85°C   | 620                                          | mW   |

| Storage Temperature  | T <sub>STG</sub>  | _         | -55 to +150                                  | °C   |

#### RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol          | Condition | Range                                        | Unit |

|-----------------------|-----------------|-----------|----------------------------------------------|------|

| Power Supply Voltage  | V <sub>DD</sub> | *1        | 2.5 to 5.5                                   | V    |

| Bias Voltage          | V <sub>BI</sub> | *1, *2    | V <sub>DD</sub> -8.0 to V <sub>DD</sub> -4.0 | V    |

| Operating Frequency   | f <sub>op</sub> | _         | 60 to 110                                    | kHz  |

| Operating Temperature | T <sub>op</sub> | _         | -40 to +85                                   | °C   |

$$\begin{split} &V_{LCD1} \!\!=\!\! V_{DD} \!\!-\! \frac{1}{4} (V_{DD} \!\!-\!\! V_{BI}) \\ &V_{LCD2} \!\!=\!\! V_{DD} \!\!-\! \frac{2}{4} (V_{DD} \!\!-\!\! V_{BI}) \\ &V_{LCD3} \!\!=\!\! V_{DD} \!\!-\! \frac{3}{4} (V_{DD} \!\!-\!\! V_{BI}) \\ &V_{LCD4} \!\!=\!\! V_{DD} \!\!-\! \frac{4}{4} (V_{DD} \!\!-\!\! V_{BI}) \!\!=\!\! V_{BI} \end{split}$$

<sup>\*1:</sup> Voltage values are with respect to  $V_{SS}$ .

\*2: Add the following voltages to  $V_{LCD1}$ ,  $V_{LCD2}$ ,  $V_{LCD3}$  and  $V_{LCD4}$ , respectively.

# **ELECTRICAL CHARACTERISTICS**

DC Characteristics (1)

$(Ta=-40 \text{ to } +85^{\circ}\text{C}, V_{DD}=2.5 \text{ to } 4.5\text{V}, V_{BI}=(V_{DD}-8\text{V}) \text{ to } (V_{DD}-4\text{V}))$

|                             |                  | (1a=-40 to +0                                                                           | J 0, VDD=            | 2.3 10 4.0 | ov, vBI=(v         | טם–טע | ) 10 (VDD-4V))             |  |

|-----------------------------|------------------|-----------------------------------------------------------------------------------------|----------------------|------------|--------------------|-------|----------------------------|--|

| Parameter                   | Symbol           | Condition                                                                               | Min.                 | Тур.       | Max.               | Unit  | Applicable pin             |  |

| "H" Input Voltage           | V <sub>IH1</sub> | _                                                                                       | 0.8V <sub>DD</sub>   | _          | V <sub>DD</sub>    | V     | Input pins other than OSC1 |  |

| ii iiipat voitago           | V <sub>IH2</sub> | _                                                                                       | 0.8V <sub>DD</sub>   |            | V <sub>DD</sub>    | V     | 0SC1                       |  |

| "L" Input Voltage           | V <sub>IL1</sub> | _                                                                                       | 0.0                  | _          | 0.2V <sub>DD</sub> | V     | Input pins other than OSC1 |  |

|                             | V <sub>IL2</sub> | _                                                                                       | 0.0                  | _          | 0.2V <sub>DD</sub> | V     | OSC1                       |  |

| III III I a a a t O a a a t | I <sub>IH1</sub> | V <sub>IN</sub> =V <sub>DD</sub>                                                        | _                    | _          | 1                  | μА    | Input pins other           |  |

| "H" Input Current           | <b>.</b>         | 14 14 0.514                                                                             | _                    |            | 500                |       | than TEST                  |  |

|                             | I <sub>IH2</sub> | V <sub>DD</sub> , V <sub>IN</sub> =2.5V                                                 | 5                    |            | 500                | μΑ    | TEST                       |  |

| "L" Input Current           | I <sub>IL</sub>  | V <sub>IN</sub> =0V                                                                     | _                    | _          | -1                 | μΑ    | All input pins             |  |

| "H" Output Voltage          | V <sub>OH</sub>  | I <sub>OH</sub> =-0.5mA                                                                 | V <sub>DD</sub> -0.5 | _          | _                  | V     |                            |  |

| "L" Output Voltage          | V <sub>OL</sub>  | I <sub>OL</sub> =0.5mA                                                                  | _                    | _          | 0.5                | V     | S0                         |  |

| Output Off Leakage Current  |                  | $V_{IN}=V_{DD}$                                                                         | _                    | _          | 1                  | μΑ    | 30                         |  |

| Output On Leakage Gurrent   | I <sub>OFF</sub> | V <sub>IN</sub> =0V                                                                     | _                    | _          | -1                 | μΑ    |                            |  |

| OSC "H" Output Current      | I <sub>OH</sub>  | V <sub>OH</sub> =V <sub>DD</sub> -0.5V                                                  | _                    | _          | -0.15              | mA    | OSC2,                      |  |

| OSC "L" Output Current      | I <sub>OL</sub>  | V <sub>0L</sub> =0.5V                                                                   | 0.15                 | _          | _                  | mA    | OSC3                       |  |

| COM Output Resistance       | R <sub>C</sub>   | I <sub>0</sub> =+/-50μA                                                                 | _                    | _          | 6                  | kΩ    | C1 to C8                   |  |

| SEG Output Resistance       | Rs               | I <sub>0</sub> =+/-10μA                                                                 | _                    | _          | 18                 | kΩ    | S1 to S65                  |  |

| Supply Current              | I <sub>SS</sub>  | V <sub>DD</sub> =2.5V, V <sub>BI</sub> =V <sub>DD</sub> -8V,<br>f <sub>OSC</sub> =80kHz | _                    | _          | 0.2                | mA    | V <sub>SS</sub>            |  |

| σαμμην σαιτστιτ             | I <sub>BI</sub>  | (External resistor, capacitor) C=56pF, $R_S=10k\Omega$ , $R=66k\Omega$                  | _                    | _          | 50                 | μΑ    | V <sub>LCD4</sub>          |  |

# DC Characteristics (2)

(Ta=-40 to +85°C,  $V_{DD}$ =4.5 to 5.5V,  $V_{BI}$ =( $V_{DD}$ -8V) to ( $V_{DD}$ -4V))

| Parameter                  | Symbol           | `                                                                                       | Min.                 | Тур. | Max.               |    | Applicable pin             |

|----------------------------|------------------|-----------------------------------------------------------------------------------------|----------------------|------|--------------------|----|----------------------------|

| "H" Input Voltage          | V <sub>IH1</sub> | _                                                                                       | 0.8V <sub>DD</sub>   | _    | V <sub>DD</sub>    | V  | Input pins other than OSC1 |

|                            | V <sub>IH2</sub> | _                                                                                       | 0.8V <sub>DD</sub>   | _    | V <sub>DD</sub>    | V  | OSC1                       |

| "L" Input Voltage          | V <sub>IL1</sub> | _                                                                                       | 0.0                  | _    | 0.2V <sub>DD</sub> | V  | Input pins other than OSC1 |

|                            | V <sub>IL2</sub> | _                                                                                       | 0.0                  | _    | 0.2V <sub>DD</sub> | V  | OSC1                       |

| "H" Input Current          | I <sub>IH1</sub> | V <sub>IN</sub> =V <sub>DD</sub>                                                        | _                    | _    | 1                  | μА | Input pins other than TEST |

|                            | I <sub>IH2</sub> | V <sub>DD</sub> , V <sub>IN</sub> =2.5V                                                 | 5                    | _    | 1000               | μΑ | TEST                       |

| "L" Input Current          | I <sub>IL</sub>  | V <sub>IN</sub> =0V                                                                     | _                    | _    | -1                 | μΑ | All input pins             |

| "H" Output Voltage         | V <sub>OH</sub>  | I <sub>OH</sub> =-0.5mA                                                                 | V <sub>DD</sub> -0.5 |      | _                  | V  |                            |

| "L" Output Voltage         | V <sub>OL</sub>  | I <sub>OL</sub> =0.5mA                                                                  |                      |      | 0.5                | V  | S0                         |

| Output Off Leakage Current | 1                | $V_{IN}=V_{DD}$                                                                         |                      |      | 1                  | μΑ | 30                         |

| Output Off Leakage Guffein | loff             | V <sub>IN</sub> =0V                                                                     |                      |      | -1                 | μΑ |                            |

| OSC "H" Output Current     | I <sub>OH</sub>  | V <sub>OH</sub> =V <sub>DD</sub> -0.5V                                                  | _                    | _    | -0.15              | mA | OSC2,                      |

| OSC "L" Output Current     | I <sub>OL</sub>  | V <sub>0L</sub> =0.5V                                                                   | 0.15                 | _    | _                  | mA | OSC3                       |

| COM Output Resistance      | Rc               | I <sub>0</sub> =+/-50μA                                                                 | _                    | _    | 6                  | kΩ | C1 to C8                   |

| SEG Output Resistance      | Rs               | I <sub>0</sub> =+/-10μA                                                                 | _                    | _    | 18                 | kΩ | S1 to S65                  |

| Supply Current             | I <sub>SS</sub>  | V <sub>DD</sub> =5.5V, V <sub>BI</sub> =V <sub>DD</sub> -8V,<br>f <sub>OSC</sub> =80kHz | _                    | _    | 0.5                | mA | V <sub>SS</sub>            |

| Supply Current             | I <sub>BI</sub>  | (External resistor, capacitor)<br>C=56pF, $R_S$ =10k $\Omega$ ,<br>$R$ =66k $\Omega$    | _                    | _    | 50                 | μА | V <sub>LCD4</sub>          |

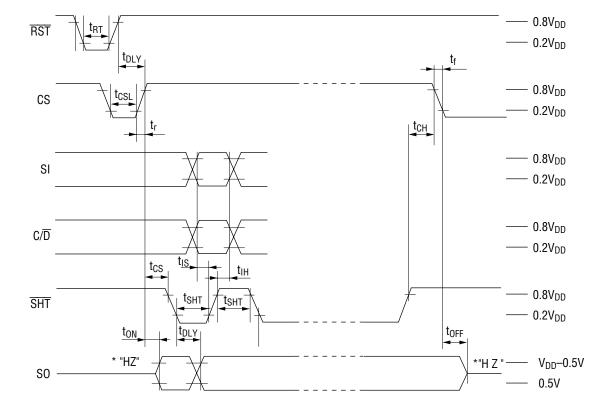

# **AC Characteristics**

$(Ta=-40 \text{ to } +85^{\circ}\text{C}, V_{DD}=2.5 \text{ to } 5.5\text{V}, V_{BI}=(V_{DD}-8\text{V}) \text{ to } (V_{DD}-4\text{V}))$

| Parameter                 | Symbol                         | Condition            | Min. | Тур. | Max. | Unit |

|---------------------------|--------------------------------|----------------------|------|------|------|------|

| CS Setup Time             | t <sub>CS</sub>                | _                    | 300  | _    | _    | ns   |

| CS Hold Time              | t <sub>CH</sub>                | _                    | 200  | _    | _    | ns   |

| CS "L" Time               | t <sub>CSL</sub>               | _                    | 500  | _    | _    | ns   |

| SO ON Delay Time          | t <sub>ON</sub>                | C <sub>L</sub> =45pF | _    | _    | 200  | ns   |

| SO OFF Delay Time         | toff                           | C <sub>L</sub> =45pF | _    | _    | 200  | ns   |

| SO Output Delay Time      | t <sub>DLY</sub>               | C <sub>L</sub> =45pF | 0    | _    | 200  | ns   |

| Input Setup Time          | t <sub>IS</sub>                | _                    | 200  | _    | _    | ns   |

| Input Hold Time           | t <sub>IH</sub>                | _                    | 200  | _    | _    | ns   |

| Input Rise, Fall Time     | t <sub>r</sub> /t <sub>f</sub> | All inputs           | _    | _    | 50   | ns   |

| RST Pulse Width           | t <sub>RT</sub>                | _                    | 5    | _    | _    | ns   |

| Wait Time After RST Pulse | t <sub>DLY</sub>               | _                    | 500  | _    | _    | ns   |

| SHT Frequency             | f <sub>SHT</sub>               | _                    | _    | _    | 2    | MHz  |

| SHT Pulse Width           | t <sub>SHT</sub>               | _                    | 200  | _    | _    | ns   |

\* "HZ": High impedance.

# FUNCTIONAL DESCRIPTION General Description of Block Diagram

#### 1. Address Pointer

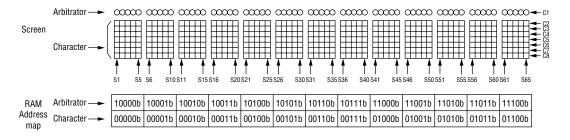

An address pointer is a 5-bit counter which assigns the write destination or read destination address of CGA RAM and AB RAM, and the write destination address of CHB RAM and ABB RAM. The value of the address pointer can be set by the LPA command. The value of the address pointer is automatically incremented by 1 after executing the AINC and CHB commands, or after transferring input display data.

#### 2. Character Generator Address RAM (CGA RAM)

The character generator address RAM stores 8-bit character codes of the character generator ROM. A maximum of thirteen 8-bit character codes can be stored.

#### 3. Arbitrator RAM (AB RAM)

The arbitrator RAM stores the lighting data of the arbitrator. Lighting data is stored in 5 dot units, and a maximum of 65 dots of lighting data can be stored.

#### 4. Character Blink RAM (CHB RAM)

The character blink RAM stores character blink data. A maximum of 13 characters of blink data can be stored.

#### 5. Arbitrator Blink RAM (ABB RAM)

The arbitrator blink RAM stores blink data of the arbitrator. Blink data is stored in 5 dot units, and a maximum of 65 dots of blink data can be stored.

#### 6. Character Generator ROM (CG ROM)

The character generator ROM generates character patterns with  $5 \times 7$  dots. This ROM can store a maximum of 256 types of characters, numerics, and symbols.

When an 8-bit character code of CG ROM is written to CGA RAM, character patterns with  $5 \times 7$  dots corresponding to 8-bit character code are displayed at the LCD display position corresponding to the CGA RAM address.

#### Relationship between display screen, LCD output and memory address

#### **Command Configuration**

|   | Comi     | mand                                | мѕв |    | In | put | da | ta |    | LSB | Comment                                                                                                                                         |

|---|----------|-------------------------------------|-----|----|----|-----|----|----|----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Mnemonic | Operation                           | D7  | D6 | D5 | D4  | D3 | D2 | D1 | D0  | Comment                                                                                                                                         |

| 1 | LPA      | Load Pointer<br>Address             | 1   | 1  | *  | A4  | А3 | A2 | A1 | A0  | Sets address pointer value A0, A1, A2, A3 A4: address pointer value (binary)                                                                    |

| 2 | DISP     | DISPlay on/off                      | 1   | 0  | 0  | *   | 1  | 0  | 0  | DI  | Sets on/off of LCD panel Panel is on when DI = "1" Panel is off when DI = "0"                                                                   |

| 3 | СНВ      | CHaracter Blink<br>on/off           | 0   | *  | *  | *   | 0  | 0  | СВ | *   | Sets blink in 5 dot units  Blink starts in 5 dot units when CB = "1"  Blink is cleared when CB = "0"                                            |

| 4 | ABBC 1/5 | ArBitrator Blink<br>Control 1/5 dot | 1   | 0  | 0  | 1   | 1  | 1  | 0  | ВС  | Sets writing method to arbitrator blink RAM Writing in 1 dot unit is enabled when BC = "1" Writing in 1 dot unit is disabled when BC = "0"      |

| 5 | ABB      | ArBitrator Blink                    | 1   | 0  | 0  | 0   | 1  | 1  | 0  | AB  | Sets start/stop of writing to arbitrator blink RAM Writing in 1 dot unit starts when AB = "1" Writing in 1 dot unit stops when AB = "0"         |

| 6 | BPC      | Blink Pattern<br>Control            | 1   | 0  | 0  | *   | 0  | 0  | 1  | ВР  | Sets blink pattern of characters  When BP = 1, all on $\leftrightarrow$ character blink  When BP = 0, all off $\leftrightarrow$ character blink |

| 7 | AINC     | Address<br>INCrement                | 1   | 0  | 0  | *   | 1  | *  | 1  | *   | Increments address pointer value by 1                                                                                                           |

| 8 | LOT      | Load OpTion                         | 1   | 0  | 1  | 1   | *  | *  | 11 | 10  | Sets additional function of AINC command                                                                                                        |

| 9 | SOE/D    | Serial Out<br>Enable/Disable        | 1   | 0  | 0  | *   | 0  | 1  | 1  | S   | Set SO pin SO pin is a CMOS output when S = "1" SO pin is in a high impedance state when S = "0"                                                |

<sup>\*:</sup> Don't care

The address pointer value is incremented by 1 when CG ROM code data, arbitrator display data and arbitrator blink data are input and when AINC and CHB commands are executed.

# **Input Display Data Configuration**

|   | Command                 | мѕв |    | In | put | da  | ta  |     | LSB | Comment                                                          |

|---|-------------------------|-----|----|----|-----|-----|-----|-----|-----|------------------------------------------------------------------|

|   |                         | D7  | D6 | D5 | D4  | D3  | D2  | D1  | D0  | Comment                                                          |

| 1 | CG ROM code data        | C7  | C6 | C5 | C4  | C3  | C2  | C1  | CO  | C0 to C7: CG ROM address                                         |

| 2 | Arbitrator display data | *   | *  | *  | AB4 | AB3 | AB2 | AB1 | AB0 | Relationship between AB0 to AB4 and segments pins is as follows. |

| 3 | Arbitrator blink data   | *   | *  | *  | AB4 | AB3 | AB2 | AB1 | AB0 | S5n+1 S5n+5                                                      |

# **Output Display Data Configuration**

|   | Command                 | мѕв Input data |    |    |      |       |      |        | LSB  | Comment                             |  |  |

|---|-------------------------|----------------|----|----|------|-------|------|--------|------|-------------------------------------|--|--|

|   |                         |                | D6 | D5 | D4   | D3    | D2   | D1     | D0   | Comment                             |  |  |

| 1 | CG ROM code data        | <b>C</b> 7     | C6 | C5 | C4   | C3    | C2   | C1     | C0   | C0 to C7: CG ROM address            |  |  |

|   |                         |                |    |    |      | I BU3 |      | 02 RD1 |      | Relationship between RD0 to RD4 and |  |  |

|   |                         |                | 0  | 0  | BD4  |       |      |        |      | segment pins is as follows.         |  |  |

| 2 | Arbitrator display data | 0              |    |    |      |       | BD2  |        | BDU  | S5n+1 S5n+5                         |  |  |

| - | Tribitator display data |                |    |    | דטוו | IIDO  | 1102 |        | INDO | ,                                   |  |  |

|   |                         |                |    |    |      |       |      |        |      | RD4 RD0                             |  |  |

n = 0 to 12

#### **How to Write Command and Display Data**

- Input a command and display data into the SI pin sequentially from MSB in 8-bit units (MSB first).

- Setting CS pin at "H" level enables transfer of a command and display data.

- Setting CS pin at a "L" level disables data transfer.

- As shown in the figure below, data is shifted at the rising edge of the shift clock that is input to the SHT pin. When 8 shift clocks are input, internal load signals are automatically generated and a command or display data is loaded. It is unnecessary to provide load signals externally.

- Loaded 8-bit data is recognized as a command if the  $C/\overline{D}$  pin is set at "H" level, and is recognized as display data if the  $C/\overline{D}$  pin is set at "L" level on the rising edge of the 8th shift clock input to the  $\overline{SHT}$  pin.

Write timing is shown below.

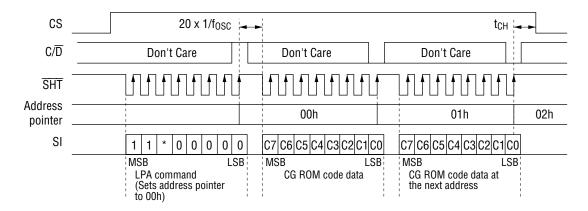

#### (Example) Writing CG ROM address data

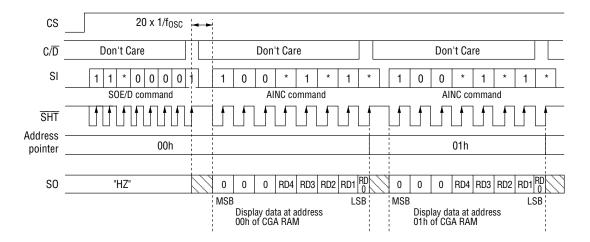

#### **How to Read Display Data**

- Display data is output sequentially from MSB in 8-bit units (MSB first).

- Setting S = "1" by the SOE/D command after setting the CS pin at "H" level enables the output of display data from the SO pin.

- Setting the CS pin at "L" level or setting S = "0" by the SOE/D command sets the SO pin to high impedance and disables output of display data.

- CGARAM or ABRAM data corresponding to the address pointer value is output.

- Display data is output from MSB on the falling edge of the shift clock that is input to the SHT pin, as shown in the figure below.

Read timing is shown below.

#### (Example) Reading by AINC command

#### **Reset Function**

Reset is enabled when the  $\overline{RST}$  pin is set at "L" level at such timing as at power-on, which initializes all functions and turns off the LCD panel.

The initial state after reset is as follows.

Data of each RAM............ All contents are held. (Contents are undefined when power is turned

on.)

Arbitrator blink ...... Writing in 5 dot units is set.

Character blink ...... Repeat of all display-on and character display is set.

Display on and

all display off ...... All display off mode is selected.

Common output...... All common outputs go to V<sub>DD</sub> level.

SO pin ...... High impedance state

### **Command Description**

1. Load pointer address command (LPA command)

This command is used to set the value of the address pointer. Execute this command before transferring other commands, CG ROM code data and arbitrator display data.

After this command is executed, setting the  $C/\overline{D}$  pin from "1" to "0" enables writing CG ROM code data to CG ROM address RAM (CGA RAM) and arbitrator display data to arbitrator RAM (ABRAM). After CG ROM code data or arbitrator display data is transferred, the address pointer is automatically incremented (+1), and CG ROM code data and arbitrator display data can be transferred continuously.

[How to transfer LPA command and CG ROM code data]

| LPA<br>command      | D8 D7 D6 D5 D4 D3 D2 D1  1 1 * 0 0 0 0 0 Specify address pointer value  *: Don't care (Example: Set address pointer value to 00H.)                                                                                                                                                                             |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CG ROM<br>code data | D8 D7 D6 D5 D4 D3 D2 D1  C7 C6 C5 C4 C3 C2 C1 C0  CG ROM code data is written to CGA RAM address 00H, and the character corresponding to the specified CG ROM code is displayed in segments 1 to 5.  After this data transfer is executed, the address pointer value becomes 01H.                              |

| CG ROM<br>code data | D8 D7 D6 D5 D4 D3 D2 D1  C7 C6 C5 C4 C3 C2 C1 C0  CG ROM code data is written to CGA RAM address 01H, and the character corresponding to the specified CG ROM code is displayed at segments 6 to 10.  After this data transfer is executed, the address pointer value becomes 02H.                             |

| CG ROM<br>code data | D8 D7 D6 D5 D4 D3 D2 D1  C7 C6 C5 C4 C3 C2 C1 C0  CG ROM code data is written to CGA RAM address 02H, and the character corresponding to the specified CG ROM code can be displayed at segments 11 to15.  After this data transfer is executed, the address pointer value becomes 03H.  (Repeats eight times.) |

| CG ROM<br>code data | D8 D7 D6 D5 D4 D3 D2 D1  C7 C6 C5 C4 C3 C2 C1 C0  CG ROM code data is written to CGA RAM address OBH, and the character corresponding to the specified CG ROM code can be displayed at segments 56 to 60.                                                                                                      |

becomes OCH.

After this data transfer is executed, the address pointer value

| CG ROM code data | D8 | D7 | D6<br>C5 | D5<br>C4 | D4<br>C3 | D3<br>C2 | D2<br>C1 | D1<br>C0 | CG ROM code data is written to CGA RAM address 0CH, and                                         |  |  |  |  |

|------------------|----|----|----------|----------|----------|----------|----------|----------|-------------------------------------------------------------------------------------------------|--|--|--|--|

|                  |    |    |          |          |          |          |          |          | the character corresponding to the specified CG ROM code can be displayed at segments 61 to 65. |  |  |  |  |

|                  |    |    |          |          |          |          |          |          | After this data transfer is executed, the address pointer value becomes ODH.                    |  |  |  |  |

| CG ROM           | D8 | D7 | D6       | D5       | D4       | D3       | D2       | D1       |                                                                                                 |  |  |  |  |

| code data        | C7 | C6 | C5       | C4       | C3       | C2       | C1       | CO       | CGA RAM address is only 00H to 0CH. <b>The address</b>                                          |  |  |  |  |

|                  |    |    |          |          |          |          |          |          | pointer value becomes 0DH. However, this CG                                                     |  |  |  |  |

|                  |    |    |          |          |          |          |          |          | ROM data is ignored.                                                                            |  |  |  |  |

[How to transfer LPA command and arbitrator display data]

| LPA                        | חס חק       |         |          |              |                                  |                                                                                                                                                                                                                                                                                                                                                                |

|----------------------------|-------------|---------|----------|--------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| command                    | D8 D7       | D6<br>* | D5       |              | D3 D2 D1<br>0 0 0                | Specify address pointer value                                                                                                                                                                                                                                                                                                                                  |

| Communa                    |             |         |          |              |                                  | (Example: Set address pointer value to 10H.)                                                                                                                                                                                                                                                                                                                   |

| Arbitrator                 | D8 D7       | D6      | D5       | D4 [         | D3 D2 D1                         | 1                                                                                                                                                                                                                                                                                                                                                              |

| display data               | * *         | *       | A4       | A3 /         | A2 A1 A0                         | Arbitrator display data is written to AB RAM address 10H,                                                                                                                                                                                                                                                                                                      |

|                            |             |         |          |              |                                  | and the specified arbitrator of segments 1 to 5 can be                                                                                                                                                                                                                                                                                                         |

|                            |             |         |          |              |                                  | displayed.                                                                                                                                                                                                                                                                                                                                                     |

|                            |             |         |          |              |                                  | After this data transfer is executed, the address pointer value becomes 11H.                                                                                                                                                                                                                                                                                   |

|                            | D0 D7       | De      | DE       | D4 F         | 20 00 01                         | becomes ith.                                                                                                                                                                                                                                                                                                                                                   |

| Arbitrator                 | D8 D7       | D6      | D5<br>A4 |              | D3 D2 D1<br>A2 A1 A0             | Arbitrator display data is written to AB RAM address 11H,                                                                                                                                                                                                                                                                                                      |

| display data               |             |         | A4       | AS F         | 12 AT AU                         | and the specified arbitrator of segments 6 to 10 can be                                                                                                                                                                                                                                                                                                        |

|                            |             |         |          |              |                                  | displayed.                                                                                                                                                                                                                                                                                                                                                     |

|                            |             |         |          |              |                                  | After this data transfer is executed, the address pointer value                                                                                                                                                                                                                                                                                                |

|                            |             |         |          |              |                                  | becomes 12H.                                                                                                                                                                                                                                                                                                                                                   |

| Arbitrator                 | D8 D7       | D6      | D5       | D4 [         | D3 D2 D1                         | 1                                                                                                                                                                                                                                                                                                                                                              |

| display data               | * *         | *       | A4       | A3 /         | A2 A1 A0                         | Arbitrator display data is written to AB RAM address 12H,                                                                                                                                                                                                                                                                                                      |

|                            |             |         |          |              |                                  | and the specified arbitrator of segments 11 to 15 can be                                                                                                                                                                                                                                                                                                       |

|                            |             |         | į        |              |                                  | displayed.                                                                                                                                                                                                                                                                                                                                                     |

|                            |             |         |          |              |                                  | After this data transfer is executed, the address pointer value becomes 13H.                                                                                                                                                                                                                                                                                   |

|                            |             |         | i        | (Rene        | eats eight tin                   |                                                                                                                                                                                                                                                                                                                                                                |

|                            |             |         |          | (Порс        | outo orgini tim                  | 100.)                                                                                                                                                                                                                                                                                                                                                          |

|                            |             |         | į        |              |                                  |                                                                                                                                                                                                                                                                                                                                                                |

| Arbitrator                 | D8 D7       | D6      | D5       | D4 [         | D3 D2 D1                         |                                                                                                                                                                                                                                                                                                                                                                |

| display data               | * *         | *       |          |              | 70 52 51                         |                                                                                                                                                                                                                                                                                                                                                                |

| uispiay uata               |             | 1 ^     | A4       | A3   A       | A2 A1 A0                         | Arbitrator display data is written to AB RAM address 1BH,                                                                                                                                                                                                                                                                                                      |

|                            |             |         | A4       | A3   A       | A2 A1 A0                         | Arbitrator display data is written to AB RAM address 1BH, and the specified arbitrator of segments 59 to 60 can be                                                                                                                                                                                                                                             |

|                            |             |         | A4       | A3   A       | A2 A1 A0                         |                                                                                                                                                                                                                                                                                                                                                                |

|                            |             | Î       | A4       | A3   A       | A2 A1 A0                         | and the specified arbitrator of segments 59 to 60 can be                                                                                                                                                                                                                                                                                                       |

|                            |             |         | A4       |              |                                  | and the specified arbitrator of segments 59 to 60 can be displayed.                                                                                                                                                                                                                                                                                            |

| Arbitrator                 | D8 D7       | D6      | D5       | D4 [         | D3 D2 D1                         | and the specified arbitrator of segments 59 to 60 can be displayed.  After this data transfer is executed, the address pointer value becomes 1CH.                                                                                                                                                                                                              |

| Arbitrator<br>display data | D8 D7       |         |          | D4 [         |                                  | and the specified arbitrator of segments 59 to 60 can be displayed.  After this data transfer is executed, the address pointer value becomes 1CH.  Arbitrator display data is written to AB RAM address 1CH,                                                                                                                                                   |

|                            | D8 D7       |         | D5       | D4 [         | D3 D2 D1                         | and the specified arbitrator of segments 59 to 60 can be displayed.  After this data transfer is executed, the address pointer value becomes 1CH.  Arbitrator display data is written to AB RAM address 1CH, and the specified arbitrator of segments 61 to 65 can be                                                                                          |

|                            | D8 D7       |         | D5       | D4 [         | D3 D2 D1                         | and the specified arbitrator of segments 59 to 60 can be displayed.  After this data transfer is executed, the address pointer value becomes 1CH.  Arbitrator display data is written to AB RAM address 1CH, and the specified arbitrator of segments 61 to 65 can be displayed.                                                                               |

|                            | D8 D7 * *   |         | D5       | D4 [         | D3 D2 D1                         | and the specified arbitrator of segments 59 to 60 can be displayed.  After this data transfer is executed, the address pointer value becomes 1CH.  Arbitrator display data is written to AB RAM address 1CH, and the specified arbitrator of segments 61 to 65 can be                                                                                          |

| display data               | D8 D7  * *  |         | D5       | D4 [<br>A3 / | D3 D2 D1                         | and the specified arbitrator of segments 59 to 60 can be displayed.  After this data transfer is executed, the address pointer value becomes 1CH.  Arbitrator display data is written to AB RAM address 1CH, and the specified arbitrator of segments 61 to 65 can be displayed.  After this data transfer is executed, the address pointer value              |

| display data  Arbitrator   | * *         | D6 *    | D5<br>A4 | D4           | D3 D2 D1<br>A2 A1 A0             | and the specified arbitrator of segments 59 to 60 can be displayed.  After this data transfer is executed, the address pointer value becomes 1CH.  Arbitrator display data is written to AB RAM address 1CH, and the specified arbitrator of segments 61 to 65 can be displayed.  After this data transfer is executed, the address pointer value              |

| display data               | * * * D8 D7 | D6 *    | D5<br>A4 | D4           | D3 D2 D1<br>A2 A1 A0<br>D3 D2 D1 | and the specified arbitrator of segments 59 to 60 can be displayed.  After this data transfer is executed, the address pointer value becomes 1CH.  Arbitrator display data is written to AB RAM address 1CH, and the specified arbitrator of segments 61 to 65 can be displayed.  After this data transfer is executed, the address pointer value becomes 1DH. |

<sup>\*:</sup> Don't care

### 2. Display on/off command (DISP command)

This command is used to select LCD panel display-on mode and display-off mode. Setting DI = "0" enters display-off mode. At this time, the output voltage of all segments and common output pins go to  $V_{DD}$  level and the LCD panel goes out. Setting DI = "1" enters display-on mode. At this time, the LCD panel restarts the status display before entering display-off mode.

#### [DISP command format]

| DISP    |       |       |     | D5 |   |   |   |    |                                       |

|---------|-------|-------|-----|----|---|---|---|----|---------------------------------------|

| command | 1     | 0     | 0   | *  | 1 | 0 | 0 | DI | Display-off mode is set when DI = "0" |

|         | *: Do | n't c | are |    |   | 1 |   |    | Display-on mode is set when DI = "1"  |

#### 3. Arbitrator Blink Control 1/5 command (ABBC 1/5 command)

This command is used to select the type of writing arbitrator blink data to the Arbitrator Blink RAM (ABB RAM). This command is used along with the Character Blink on/off command or with the Arbitrator Blink command, explained below.

Setting BC = "0" enables writing arbitrator blink data in 5-bit units using the CHB command. Setting BC = "1" enables writing arbitrator blink data in 1 bit unit using the ABB command.

#### [ABBC 1/5 command format]

| DISP    |   |   |   |   | D4 |   |   |    |                                         |

|---------|---|---|---|---|----|---|---|----|-----------------------------------------|

| command | 1 | 0 | 0 | 1 | 1  | 1 | 0 | ВС | BC = "0" enables writing in 5-bit unit. |

|         |   | l |   |   | ı  |   |   |    | BC = "1" enables writing in 1-bit unit. |

#### 4. Character Blink on/off command (CHB command)

This command is used to blink a character and arbitrator in 5-dot units. Blinking can be set for each address pointer value. This command is used with the ABBC 1/5 command, explained above.

If CB = "0" is set when the address pointer value is 00H to 0CH, "0" is written to Character Blink RAM (CHB RAM), and the blinking of a character displayed in the segments corresponding to the address pointer value stops. If CB = "1" is set, "1" is written to CHB RAM, and the character displayed in the segments corresponding to the address pointer value starts blinking.

If CB = "0" is set when the address pointer value is 10H to 1CH, "0" is written to the arbitrator blink RAM (ABB RAM) and the blinking of the arbitrator displayed in the segments corresponding to the address pointer value stops. If CB = "1" is set, "1" is written to the ABB RAM, and the arbitrator displayed in the segments corresponding to the address pointer value starts blinking.

Set the address pointer value by the LPA command before executing this command.

Transfer the LPA command, ABBC 1/5 command and CHB command as follows.

[How to transfer LPA command, ABBC 1/5 command and CHB command (character blink setting)]

| LPA<br>command | D8      | D7      | D6   | D5<br>0 | D4<br>0 | D3<br>0 | D2<br>0  | D1   | Specify the address pointer value. (Example: Set the address pointer value to 00H.)                                                                                                      |

|----------------|---------|---------|------|---------|---------|---------|----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHB            | D8<br>0 | D7 *    | D6 * | D5<br>* | D4<br>0 | D3<br>0 | D2<br>CB | D1 * | CB value is written to CHB RAM address 00H and the blinking of characters displayed in segments 1 to 5 is set.  After this command is executed, the address pointer value becomes 01H.   |

| CHB<br>command | 0       | *       | *    | *       | 0       | 0       | CB       | *    | CB value is written to CHB RAM address 01H, and the blinking of characters displayed in segments 6 to 10 is set. After this command is executed, the address pointer value becomes 02H.  |

| CHB<br>command | D8<br>0 | D7<br>* | D6 * | D5<br>* | D4<br>0 | D3<br>0 | D2<br>CB | D1 * | CB value is written to CHB RAM address 0BH and the blinking of characters displayed in segments 56 to 60 is set. After this command is executed, the address pointer value becomes 0CH.  |

| CHB<br>command | D8<br>0 | D7<br>* | D6 * | D5<br>* | D4<br>0 | D3<br>0 | D2<br>CB | D1 * | CB value is written to CHB RAM address 0CH, and the blinking of characters displayed in segments 61 to 65 is set. After this command is executed, the address pointer value becomes 0DH. |

| CHB<br>command | D8      | D7      | D6   | D5      | D4<br>0 | D3<br>0 | D2<br>CB | D1 * | CHB RAM address is only 00H to 0CH. The address                                                                                                                                          |

pointer value becomes 0DH. However, this CHB

command is ignored.

<sup>\*:</sup> Don't care

[How to transfer LPA command, ABBC 1/5 command and CHB command (arbitrator blink setting)]

| LPA            | D8 | D7         | D6       | D5      | D4         | D3         | D2         | D1         |                                                               |

|----------------|----|------------|----------|---------|------------|------------|------------|------------|---------------------------------------------------------------|

| command        | 1  | 1          | *        | 1       | 0          | 0          | 0          | 0          | Specify address pointer value                                 |

|                | DO | D.7        | DC       | D.F.    | D.4        | DO         | DO         | D.4        | (Example: Set address pointer value to 10H.)                  |

| ABBC1/5        | D8 | D7<br>0    | D6<br>0  | D5<br>1 | D4         | D3         | D2<br>0    | D1<br>0    | Set BC = "0" to enable writing in 5-dot units.                |

| command        | I  | U          | U        | ı       | ı          | ı          | U          | U          | Set BC = 0 to enable writing in 5-dot units.                  |

| СНВ            | D8 | D7         | D6       | D5      | D4         | D3         | D2         | D1         |                                                               |

| command        | 0  | *          | *        | *       | 0          | 0          | СВ         | *          | CB value is written to ABB RAM address 10H, and the           |

|                |    |            |          |         |            |            |            |            | blinking of arbitrator displayed in segments 1 to 5 is set.   |

|                |    |            |          |         |            |            |            |            | After this command is executed, the address pointer value     |

|                |    |            |          |         |            |            |            |            | becomes 11H.                                                  |

| СНВ            | D8 | D7         | D6       | D5      | D4         | D3         | D2         | D1         |                                                               |

| command        | 0  | *          | *        | *       | 0          | 0          | СВ         | *          | CB value is written to ABB RAM address 11H, and the           |

| 00111110110    |    |            |          |         |            |            |            |            | blinking of arbitrator displayed in segments 6 to 10 is set.  |

|                |    |            |          |         |            |            |            |            | After this command is executed, the address pointer value     |

|                |    |            |          |         | <br>       |            |            |            | becomes 12H.                                                  |

|                |    |            |          | i       | (Re        | neats      | s nine     | e time     | 28 )                                                          |

|                |    |            |          |         | ,          | pour       | , ,,,,,,   |            | ,                                                             |

|                |    |            |          |         |            |            |            |            |                                                               |

|                |    |            |          |         |            |            |            |            |                                                               |

| OUD            | D8 | D7         | D6       | D5      | D4         | D3         | D2         | D1         |                                                               |

| CHB<br>command | 0  | *          | *        | *       | 0          | 0          | CB         | *          | CB value is written to ABB RAM address 1BH, and the           |

| Commanu        |    |            |          |         |            |            | 0.2        |            | blinking of arbitrator displayed in segments 56 to 60 is set. |

|                |    |            |          |         |            |            |            |            | After this command is executed, the address pointer value     |

|                |    |            |          |         |            |            |            |            | becomes 1CH.                                                  |

|                |    | <b>5</b> - | <b>.</b> |         | <b>.</b> . | <b>D</b> - | <b>D</b> - | <b>5</b> · |                                                               |

| CHB            | D8 | D7<br>*    | D6<br>*  | D5<br>* | D4         | D3         | D2         | D1<br>*    | OD I I WAS ADD DAM II 400 IV                                  |

| command        | 0  |            | Û        | Ŷ       | 0          | 0          | СВ         |            | CB value is written to ABB RAM address 1CH and the            |

becomes 1DH.

| СНВ     | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

|---------|----|----|----|----|----|----|----|----|

| command | 0  | *  | *  | *  | 0  | 0  | СВ | *  |

ABB RAM address is only 10H to 1CH. The address pointer value becomes 1DH. However, this CHB command is ignored.

blinking of arbitrator displayed in segments 61 to 65 is set. After this command is executed, the address pointer value

<sup>\*:</sup> Don't care

#### 5. Arbitrator Blink command (ABB command)

This command is used to start writing arbitrator blink data to ABB RAM in 1-dot unit. This command is used with the ABB 1/5 command described above.

After setting AB = "1", setting the C/D pin from "1" to "0" enables writing arbitrator blink data to ABB RAM in 1-dot unit. After arbitrator blink data is transferred, the address pointer is automatically incremented by 1, and arbitrator blink data can be transferred continuously.

Set the address pointer value by the LPA command before executing this command. Transfer the ABBC 1/5 command, ABB command and arbitrator blink data as follows.

[How to transfer LPA command, ABBC 1/5 command, ABB command and arbitrator blink data]

| LPA                      | D8 D7 D6 D5 D4 D3 D2 D1                                                                                                                                                     |                                                                                                                                                                                                   |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| command                  | 1 1 * 0 0 0 0 0                                                                                                                                                             | Specify the address pointer value.                                                                                                                                                                |

|                          |                                                                                                                                                                             | (Example: Set the address pointer to 10H.)                                                                                                                                                        |

| ABBC1/5 command          | D8         D7         D6         D5         D4         D3         D2         D1           1         0         0         1         1         1         0         1           | Set BC = "1" to enable writing in 1-dot unit.                                                                                                                                                     |

| ABB<br>command           | D8         D7         D6         D5         D4         D3         D2         D1           1         0         0         0         1         1         0         1           | Set AB = "1" to start writing in 1-dot unit.                                                                                                                                                      |

| Arbitrator<br>blink data | D8         D7         D6         D5         D4         D3         D2         D1           *         *         *         AB4         AB3         AB2         AB1         AB0 | Arbitrator blink data is written to ABB RAM address 10H, and the arbitrator specified in segments 1 to 5 starts blinking. After this command is executed, the address pointer value becomes 11H.  |

| Arbitrator<br>blink data | D8 D7 D6 D5 D4 D3 D2 D1  * * * AB4 AB3 AB2 AB1 AB0  (Repeats nine time                                                                                                      | Arbitrator blink data is written to ABB RAM address 11H, and the arbitrator specified in segments 6 to 10 starts blinking. After this command is executed, the address pointer value becomes 12H. |

| Arbitrator<br>blink data | D8 D7 D6 D5 D4 D3 D2 D1  * * * AB4 AB3 AB2 AB1 AB0                                                                                                                          | Arbitrator blink data is written to ABB RAM address 1BH, and the arbitrator specified in segments 59 to 60 starts blinking.                                                                       |

becomes 1CH.

After this command is executed, the address pointer value

<sup>\*:</sup> Don't care

| Arbitrator<br>blink data | B D7 D6 D5 D4 D3 D2 D1  * * AB4 AB3 AB2 AB1 AB0 AB2 AB1 AB0  Arbitrator blink data is written to ABB RAM address 1CH, and the arbitrator specified in segment 61 to 65 starts blinking.  After this command is executed, the address pointer value |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arbitrator<br>blink data | becomes 1DH.  D8 D7 D6 D5 D4 D3 D2 D1  * * * AB4 AB3 AB2 AB1 AB0  ABB RAM address is only 10H to 1CH. The address pointer value becomes 1DH. However, this  ABB command is ignored.                                                                |

<sup>\*:</sup> Don't care

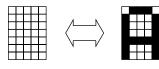

#### 6. Blink Pattern Control Command (BPC command)

This command is used to select the blink pattern of characters.

If BP = "1" is set, the display repeats all lighting off and character displays. If BP = "0" is set, the display repeats all light on and character displays.

This command cannot be set for each address pointer value. If this command is executed, 13 characters are set at the same blink pattern.

#### [BPC Command Format]

| D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

|----|----|----|----|----|----|----|----|

| 1  | 0  | 0  | *  | 0  | 0  | 1  | ВР |

\*: Don't care

When BP = "1"

When BP = "0"

#### 7. Address Increment Command (AINC Command)

This command is used to increment the address pointer value by +1. After this command is executed, the processing being set by the LOT command, described below, is performed on the RAM corresponding to the address pointer value before being incremented by +1.

#### [AINC Command Format]

| D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

|----|----|----|----|----|----|----|----|

| 1  | 0  | 0  | *  | 1  | *  | 1  | *  |

<sup>\*:</sup> Don't care

#### 8. Load Option Command (LOT Command)

This command is used to process the display corresponding to the address pointer value before being incremented by 1 when the AINC command is executed.

If I0 = "1" is set, all "0s" are written to CGA RAM and AB RAM each time the AINC command is executed. CG ROM code "00h" is displayed on the character display and the arbitrator goes out.

If I1 = "1" is set, all "0"s are written to CHB RAM and ABB RAM each time the AINC command is executed. Therefore character and arbitrator blinking is cleared.

I0 and I1 can be set independently. If I0 = "1" and I1 = "1" are set, "0" is written to all CG RAM, AB RAM, CHB RAM and ABB RAM.

#### [LOT Command Format]

|   |   | D6 |   |   |   |    |    |

|---|---|----|---|---|---|----|----|

| 1 | 0 | 1  | 1 | * | * | 11 | 10 |

<sup>\*:</sup> Don't care

9. Serial Out Enable/Disable Command (SOE/D Command) This command is used to select the output impedance of the SO pin. When S = "1" is selected, the SO pin becomes CMOS output and it outputs displays data. While S = "0" is selected, the SO pin becomes high impedance status.

[SOE/D Command Format]

| D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

|----|----|----|----|----|----|----|----|

| 1  | 0  | 0  | *  | 0  | 1  | 1  | S  |

<sup>\*:</sup> Don't care

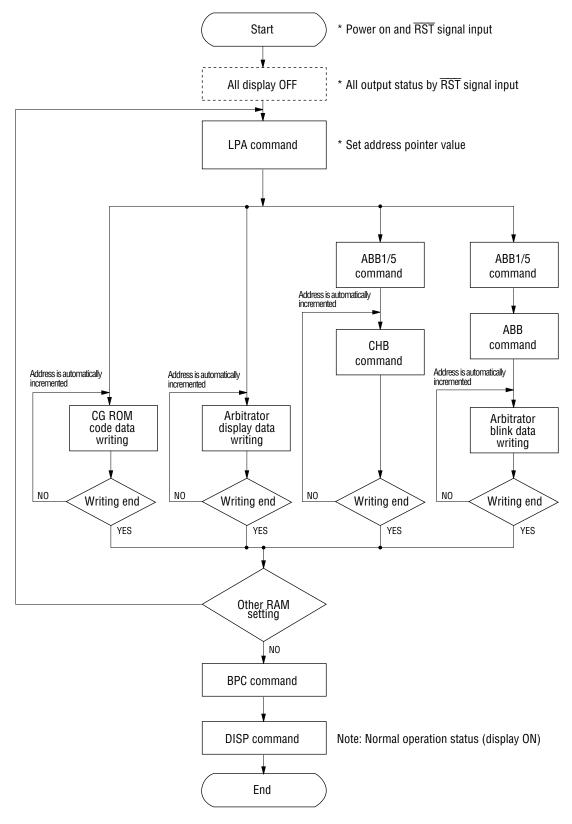

# **Initial Setting Operation Flow Chart**

# MSM9005-01 CG ROM Code

| MSB  |      |      |      |      |      |      |      |   |  |      |      |      |      |

|------|------|------|------|------|------|------|------|---|--|------|------|------|------|

| LSB  | 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 |   |  | 1100 | 1101 | 1110 | 1111 |

| 0000 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 0001 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 0010 |      |      |      |      |      |      |      | H |  |      |      |      |      |

| 0011 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 0100 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 0101 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 0110 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 0111 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 1000 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 1001 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 1010 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 1011 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 1100 |      |      |      |      |      |      |      |   |  |      |      |      |      |

| 1101 |      |      |      |      |      |      |      |   |  |      |      |      | ▓    |

| 1110 |      |      |      |      |      |      |      |   |  |      |      |      | 畿    |

| 1111 |      |      |      |      |      |      |      |   |  |      |      |      |      |

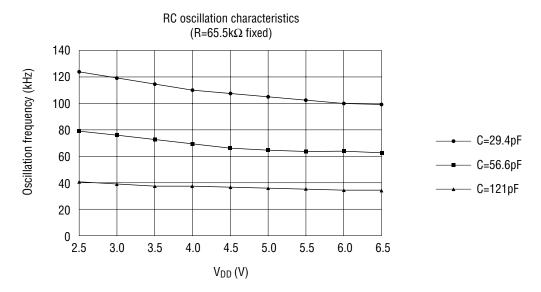

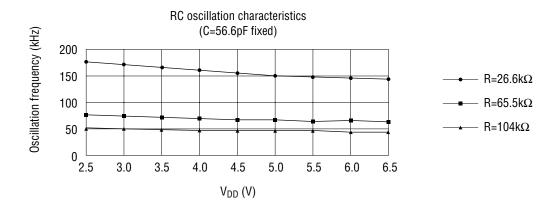

# **REFERENCE DATA**

#### **Oscillation Circuit Characteristics**

# **PACKAGE DIMENSIONS**

(Unit: mm)

Notes for Mounting the Surface Mount Type Package

The SOP, QFP, TSOP, SOJ, QFJ (PLCC), SHP and BGA are surface mount type packages, which are very susceptible to heat in reflow mounting and humidity absorbed in storage.

Therefore, before you perform reflow mounting, contact Oki's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).