## 128Kx16 SRAM/512Kx16 FLASH MODULE FEATURES

- Access Times of 35ns (SRAM) and 90ns (FLASH)

- Packaging

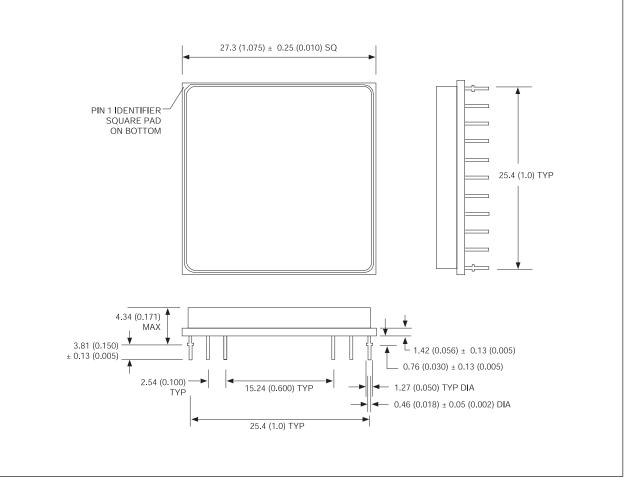

- 66 pin, PGA Type, 1.075" square HIP, Hermetic Ceramic HIP (Package 400)

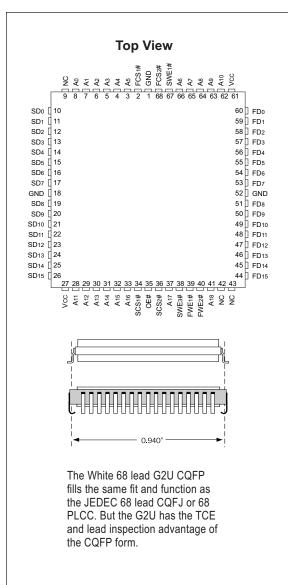

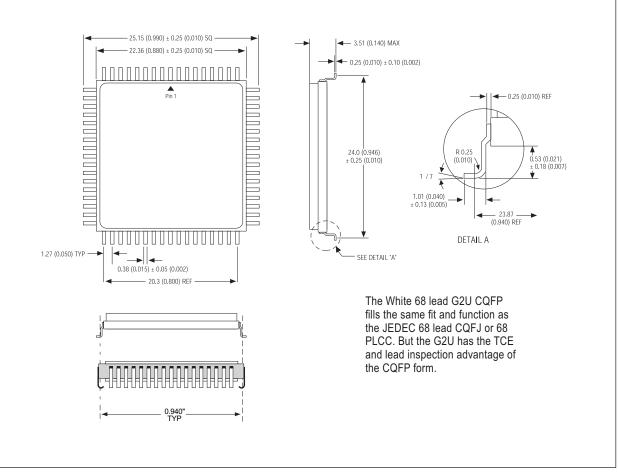

- 68 lead, Hermetic CQFP (G2U), 22.4mm (0.880") square (Package 510) 3.56mm (0.140") height. Designed to fit JEDEC 68 lead 0.990" CQFJ footprint (FIGURE 2)

- 128Kx16 SRAM

- 512Kx16 5V FLASH

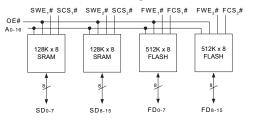

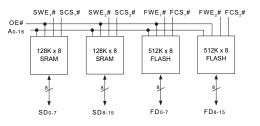

- Organized as 128Kx16 of SRAM and 512Kx16 of Flash Memory with separate Data Buses

- Both blocks of memory are User Configurable as 256Kx8

- Low Power CMOS

- Commercial, Industrial and Military Temperature Ranges

- TTL Compatible Inputs and Outputs

#### FIGURE1 – PIN CONFIGURATION FOR WSF2816-39H1X

|    | Top View |        |             |        |       |       |  |

|----|----------|--------|-------------|--------|-------|-------|--|

| 1  |          | 12     | 23          | 34     | 45    | 56    |  |

| 0  | SD8      | ⊖SWE2# | OSD15       | FD8 🔿  | Vcc〇  | FD15  |  |

| 0  | SD9      | OSCS2# | OSD14       | FD9 🔿  | FCS2# | FD14  |  |

| 0  | SD10     |        | ⊖SD13       | FD10 🔿 | FWE2# | FD13  |  |

| 0  | A13      | ⊖sd11  | ⊖SD12       | A6 🔿   | FD11  | FD12  |  |

| 0  | A14      | ()A10  | OE#         | A7 🔿   | A3    | A0 🔿  |  |

| 0  | A15      | ()A11  | <b>A</b> 17 | NC     | A4    | A1 () |  |

| 0  | A16      | ()A12  | ⊖SWE1#      | A8 🔾   | A5    | A2 🔿  |  |

| 0  | A18      | Vcc    | ⊖SD7        | A9 🔿   | FWE1# | FD7 🔿 |  |

| 0  | SD0      | OSCS1# | ⊖SD6        | FD0 🔿  | FCS1# | FD6   |  |

| 0  | SD1      | ONC    | ⊖SD5        | FD1 🔿  |       | FD5   |  |

| 0  | SD2      | ⊖SD3   | ⊖SD4        | FD2    | FD3   | FD4   |  |

| 11 |          | 22     | 33          | 44     | 55    | 66    |  |

- Built-in Decoupling Caps and Multiple Ground Pins for Low Noise Operation

- Weight:

WSF2816-39G2UX - 8 grams typical WSF2816-39H1X - 13 grams typical

#### FLASH MEMORY FEATURES

- 100,000 Erase/Program Cycles

- Sector Architecture

- 8 equal size sectors of 64K bytes each

- Any combination of sectors can be concurrently erased. Also supports full chip erase

- 5 Volt Programming; 5V ± 10% Supply

- Embedded Erase and Program Algorithms

- Hardware Write Protection

Note: For programming information refer to Flash Programming 4M5 Application Note.

| Pin Description      |                           |  |  |  |

|----------------------|---------------------------|--|--|--|

| FD <sub>0-15</sub>   | Flash Data Inputs/Outputs |  |  |  |

| SD0-15               | SRAM Data Inputs/Outputs  |  |  |  |

| A0-18                | Address Inputs            |  |  |  |

| SWE1-2#              | SRAM Write Enable         |  |  |  |

| SCS1-2#              | SRAM Chip Selects         |  |  |  |

| OE#                  | Output Enable             |  |  |  |

| Vcc                  | Power Supply              |  |  |  |

| GND                  | Ground                    |  |  |  |

| NC                   | Not Connected             |  |  |  |

| FWE <sub>1-2</sub> # | Flash Write Enable        |  |  |  |

| FCS <sub>1-2</sub> # | Flash Chip Select         |  |  |  |

#### Block Diagram

White Electronic Designs Corp. reserves the right to change products or specifications without notice.

1

### WHITE ELECTRONIC DESIGNS WSF2816-39XX

#### FIGURE 2 – PIN CONFIGURATION FOR WSF2816-39G2UX

#### **Pin Description**

| FD0-15               | Flash Data Inputs/Outputs |

|----------------------|---------------------------|

| SD0-15               | SRAM Data Inputs/Outputs  |

| A0-18                | Address Inputs            |

| SWE1-2#              | SRAM Write Enable         |

| SCS1-2#              | SRAM Chip Selects         |

| OE#                  | Output Enable             |

| Vcc                  | Power Supply              |

| GND                  | Ground                    |

| NC                   | Not Connected             |

| FWE <sub>1-2</sub> # | Flash Write Enable        |

| FCS1-2#              | Flash Chip Select         |

#### Block Diagram

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol | Min  | Max  | Unit |

|--------------------------------|--------|------|------|------|

| Operating Temperature          | TA     | -55  | +125 | °C   |

| Storage Temperature            | Tstg   | -65  | +150 | °C   |

| Signal Voltage Relative to GND | Vg     | -0.5 | 7.0  | V    |

| Junction Temperature           | TJ     |      | 150  | °C   |

| Supply Voltage                 | Vcc    | -0.5 | 7.0  | V    |

| Parameter                            |          |

|--------------------------------------|----------|

| Flash Data Retention                 | 20 years |

| Flash Endurance (write/erase cycles) | 100,000  |

NOTES: 1. Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter          | Symbol | Min  | Мах                   | Unit |

|--------------------|--------|------|-----------------------|------|

| Supply Voltage     | Vcc    | 4.5  | 5.5                   | V    |

| Input High Voltage | Vih    | 2.2  | V <sub>CC</sub> + 0.3 | V    |

| Input Low Voltage  | VIL    | -0.5 | +0.8                  | V    |

#### SRAM TRUTH TABLE

| SCS# | OE# | SWE# | Mode    | Data I/O | Power   |

|------|-----|------|---------|----------|---------|

| Н    | Х   | Х    | Standby | High Z   | Standby |

| L    | L   | Н    | Read    | Data Out | Active  |

| L    | Н   | Н    | Read    | High Z   | Active  |

| L    | Х   | L    | Write   | Data In  | Active  |

#### CAPACITANCE

T<sub>A</sub> = +25°C

| Test                     | Symbol | Condition                        | Max | Unit |

|--------------------------|--------|----------------------------------|-----|------|

| OE# Capacitance          | COE    | V <sub>IN</sub> = 0V, f = 1.0MHz | 50  | pF   |

| WE# Capacitance          | CWE    | V <sub>IN</sub> = 0V, f = 1.0MHz | 20  | pF   |

| CS# Capacitance          | Ccs    | V <sub>IN</sub> = 0V, f = 1.0MHz | 20  | pF   |

| Data I/O Capacitance     | Ci/o   | VIN = 0V, f = 1.0MHz             | 20  | pF   |

| Address Line Capacitance | CAD    | VIN = 0V, f = 1.0MHz             | 50  | pF   |

|                          |        |                                  |     |      |

This parameter is guaranteed by design but not tested.

#### DC CHARACTERISTICS

$V_{CC}$  = 5.0V,  $V_{SS}$  = 0V, -55°C  $\leq$  T<sub>A</sub>  $\leq$  +125°C

| Parameter                                                     | Symbol           | Conditions                                        | Min        | Max  | Unit |

|---------------------------------------------------------------|------------------|---------------------------------------------------|------------|------|------|

| Input Leakage Current                                         | ILI              | $V_{CC}$ = 5.5, $V_{IN}$ = GND to $V_{CC}$        |            | 10   | μA   |

| Output Leakage Current                                        | ILO              | SCS# = VIH, OE# = VIH, VOUT = GND to Vcc          |            | 10   | μA   |

| SRAM Operating Supply Current x 16 Mode                       | ICCx16           | SCS# = VIL, OE# = FCS# = VIH, f = 5MHz, Vcc = 5.5 |            | 325  | mA   |

| Standby Current                                               | Isb              | FCS# = SCS# = VIH, OE# = VIH, f = 5MHz, Vcc = 5.5 |            | 20   | mA   |

| SRAM Output Low Voltage                                       | Vol              | I <sub>OL</sub> = 8.0mA, V <sub>CC</sub> = 4.5    |            | 0.4  | V    |

| SRAM Output High Voltage                                      | Vон              | I <sub>OH</sub> = -4.0mA, V <sub>CC</sub> = 4.5   | 2.4        |      | V    |

| Flash V <sub>CC</sub> Active Current for Read (1)             | Icc1             | FCS# = VIL, OE# = SCS# = VIH                      |            | 120  | mA   |

| Flash V <sub>CC</sub> Active Current for Program or Erase (2) | Icc2             | FCS# = VIL, OE# = SCS# = VIH                      |            | 140  | mA   |

| Flash Output Low Voltage                                      | Vol              | I <sub>OL</sub> = 8.0mA, V <sub>CC</sub> = 4.5    |            | 0.45 | V    |

| Flash Output High Voltage                                     | V <sub>OH1</sub> | I <sub>OH</sub> = -2.5 mA, V <sub>CC</sub> = 4.5  | 0.85 x Vcc |      | V    |

| Flash Output High Voltage                                     | Vон2             | Іон = -100 µА, Vcc = 4.5                          | Vcc -0.4   |      | V    |

| Flash Low Vcc Lock Out Voltage                                | Vlko             |                                                   | 3.2        |      | V    |

NOTES:

1. The Icc current listed includes both the DC operating current and the frequency dependent component (@ 5 MHz).

The frequency component typically is less than 2mA/MHz, with OE# at VIH.

2. Icc active while Embedded Algorithm (program or erase) is in progress.

3. DC test conditions:  $V_{IL} = 0.3V$ ,  $V_{IH} = V_{CC} - 0.3V$

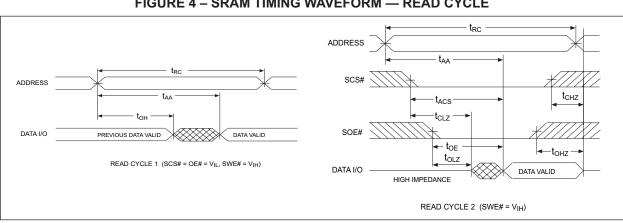

#### SRAM AC CHARACTERISTICS

$V_{CC} = 5.0V, -55^{\circ}C \le T_A \le +125^{\circ}C$

| Parameter                          | Complexed         | -35 |     | 11 14 |

|------------------------------------|-------------------|-----|-----|-------|

| Read Cycle                         | Symbol            | Min | Мах | Unit  |

| Read Cycle Time                    | trc               | 35  |     | ns    |

| Address Access Time                | taa               |     | 35  | ns    |

| Output Hold from Address Change    | tон               | 0   |     | ns    |

| Chip Select Access Time            | tacs              |     | 35  | ns    |

| Output Enable to Output Valid      | toe               |     | 20  | ns    |

| Chip Select to Output in Low Z     | tcLZ1             | 3   |     | ns    |

| Output Enable to Output in Low Z   | toLz <sup>1</sup> | 0   |     | ns    |

| Chip Disable to Output in High Z   | tcHz <sup>1</sup> |     | 20  | ns    |

| Output Disable to Output in High Z | tonz <sup>1</sup> |     | 20  | ns    |

1. This parameter is guaranteed by design but not tested.

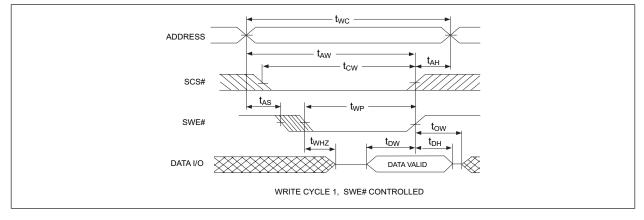

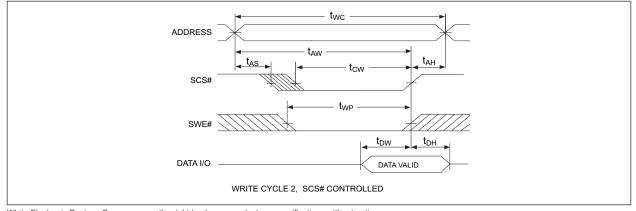

#### SRAM AC CHARACTERISTICS

$V_{CC} = 5.0V, -55^{\circ}C \le T_A \le +125^{\circ}C$

| Parameter                        | 0               | -3  | 11  |      |

|----------------------------------|-----------------|-----|-----|------|

| Write Cycle                      | Symbol          | Min | Max | Unit |

| Write Cycle Time                 | twc             | 35  |     | ns   |

| Chip Select to End of Write      | tcw             | 25  |     | ns   |

| Address Valid to End of Write    | taw             | 25  |     | ns   |

| Data Valid to End of Write       | tow             | 20  |     | ns   |

| Write Pulse Width                | twp             | 25  |     | ns   |

| Address Setup Time               | tas             | 0   |     | ns   |

| Address Hold Time                | tан             | 0   |     | ns   |

| Output Active from End of Write  | tow1            | 4   |     | ns   |

| Write Enable to Output in High Z | twHz1           |     | 20  | ns   |

| Data Hold from Write Time        | t <sub>DH</sub> | 0   |     | ns   |

1. This parameter is guaranteed by design but not tested.

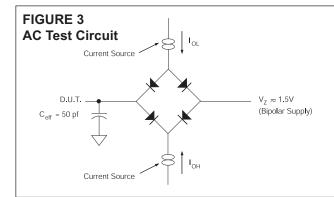

#### AC TEST CONDITIONS

| Parameter                        | Тур                                        | Unit |

|----------------------------------|--------------------------------------------|------|

| Input Pulse Levels               | V <sub>IL</sub> = 0, V <sub>IH</sub> = 3.0 | V    |

| Input Rise and Fall              | 5                                          | ns   |

| Input and Output Reference Level | 1.5                                        | V    |

| Output Timing Reference Level    | 1.5                                        | V    |

Notes: Vz is programmable from -2V to +7V.

IOL & IOH programmable from 0 to 16mA.

- Tester Impedance Z0 =  $75\Omega$ .

- Vz is typically the midpoint of VOH and VOL.

IOL & IOH are adjusted to simulate a typical resistive load circuit.

ATE tester includes jig capacitance.

#### FIGURE 4 – SRAM TIMING WAVEFORM — READ CYCLE

#### FIGURE 5 – SRAM WRITE CYCLE — SWE# CONTROLLED

#### FIGURE 6 – SRAM WRITE CYCLE — SCS# CONTROLLED

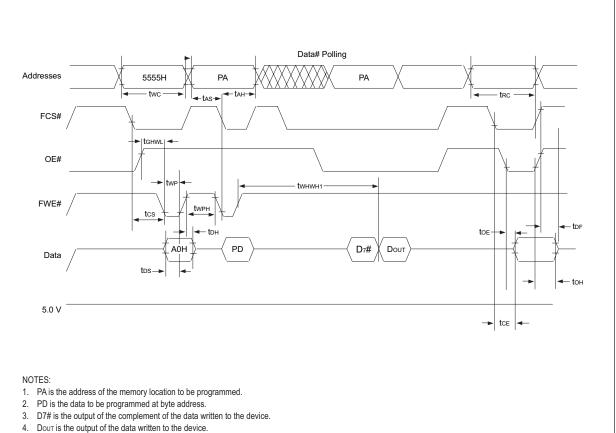

#### FLASH AC CHARACTERISTICS – WRITE/ERASE/PROGRAM OPERATIONS, FWE# CONTROLLED $V_{CC} = 5.0V - 55^{\circ}C < T_{A} < +125^{\circ}C$

| Parameter<br>Write Cycle Time              | Symbol |      | -90 |     |      |

|--------------------------------------------|--------|------|-----|-----|------|

|                                            |        |      | Min | Max | Unit |

|                                            | tavav  | twc  | 90  |     | ns   |

| Chip Select Setup Time                     | telwl  | tcs  | 0   |     | ns   |

| Write Enable Pulse Width                   | twlwh  | twp  | 45  |     | ns   |

| Address Setup Time                         | tavwl  | tas  | 0   |     | ns   |

| Data Setup Time                            | tovwн  | tos  | 45  |     | ns   |

| Data Hold Time                             | twhdx  | toн  | 0   |     | ns   |

| Address Hold Time                          | twlax  | tан  | 45  |     | ns   |

| Chip Select Hold Time                      | twhen  | tсн  | 0   |     | ns   |

| Write Enable Pulse Width High              | twhwL  | twpн | 20  |     | ns   |

| Duration of Byte Programming Operation (1) | twhwh1 |      |     | 300 | μs   |

| Sector Erase Time (2)                      | twhwh2 |      |     | 15  | sec  |

| Read Recovery Time Before Write            | tghwl  |      | 0   |     | μs   |

| Vcc Set-up Time                            |        | tvcs | 50  |     | μs   |

| Chip Programming Time                      |        |      |     | 11  | sec  |

| Output Enable Setup Time                   |        | toes | 0   |     | ns   |

| Output Enable Hold Time (1)                |        | tоен | 10  |     | ns   |

| Chip Erase Time                            |        |      |     | 64  | sec  |

NOTES:

1. Typical value for twhwh1 is 7µs.

2. Typical value for twhwh1 is 1sec.

3. Typical value for Chip Erase Time is 8sec.

4. For Toggle and Data# Polling.

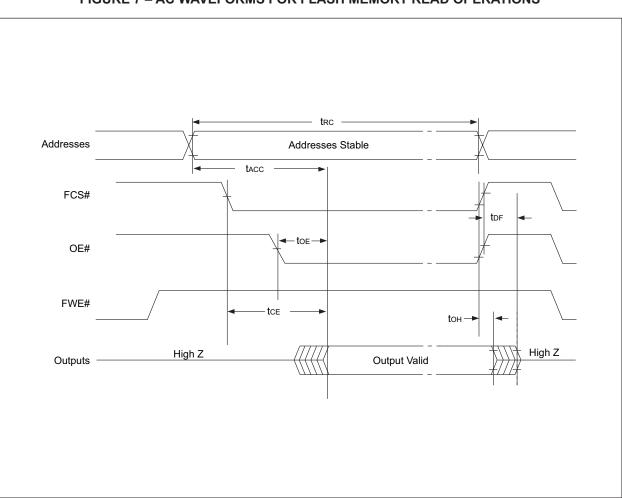

#### FLASH AC CHARACTERISTICS - READ ONLY OPERATIONS

$V_{CC} = 5.0V, -55^{\circ}C \le T_A \le +125^{\circ}C$

| Densmotor                                                       | Symbol        |       | -90 |     | 11.24 |

|-----------------------------------------------------------------|---------------|-------|-----|-----|-------|

| Parameter                                                       |               |       | Min | Мах | Unit  |

| Read Cycle Time                                                 | tavav         | trc   | 90  |     | ns    |

| Address Access Time                                             | tavqv         | tacc  |     | 90  | ns    |

| Chip Select Access Time                                         | telqv         | tce   |     | 90  | ns    |

| OE# to Output Valid                                             | tglqv         | toe   |     | 35  | ns    |

| Chip Select to Output High Z (1)                                | <b>t</b> EHQZ | tDF   |     | 20  | ns    |

| OE# High to Output High Z (1)                                   | tgнqz         | tDF . |     | 20  | ns    |

| Output Hold from Address, CS# or OE# Change, whichever is first | taxqx         | toн   | 0   |     | ns    |

1. Guaranteed by design, not tested.

### FLASH AC CHARACTERISTICS – WRITE/ERASE/PROGRAM OPERATIONS, FCS# CONTROLLED

| VCC = 5.UV, -55 C ≤ IA ≤ +125 C            |               |      |     |     |      |  |  |

|--------------------------------------------|---------------|------|-----|-----|------|--|--|

| Parameter                                  | Symbol        |      | -90 |     | 11   |  |  |

|                                            |               |      | Min | Max | Unit |  |  |

| Write Cycle Time                           | tavav         | twc  | 90  |     | ns   |  |  |

| FWE# Setup Time                            | twlel         | tws  | 0   |     | ns   |  |  |

| FCS# Pulse Width                           | teleн         | tcp  | 45  |     | ns   |  |  |

| Address Setup Time                         | tavel         | tas  | 0   |     | ns   |  |  |

| Data Setup Time                            | tdveн         | tos  | 45  |     | ns   |  |  |

| Data Hold Time                             | <b>t</b> EHDX | tон  | 0   |     | ns   |  |  |

| Address Hold Time                          | telax         | tан  | 45  |     | ns   |  |  |

| FWE# Hold From FWE# High                   | tенwн         | twн  | 0   |     | ns   |  |  |

| FCS# Pulse Width High                      | tehel         | tсрн | 20  |     | ns   |  |  |

| Duration Of Byte Programming Operation (1) | twhwh1        |      |     | 300 | μs   |  |  |

| Duration Of Erase Operation (2)            | twhwh2        |      |     | 15  | sec  |  |  |

| Read Recovery Before Write                 | tghel         |      | 0   |     | ns   |  |  |

| Chip Programming Time                      |               |      |     | 11  | sec  |  |  |

| Chip Erase Time (3)                        |               |      |     | 64  | sec  |  |  |

NOTES:

1. Typical value for  $t_{WHWH1}$  is 7µs.

2. Typical value for twHWH1 is 1sec.

3. Typical value for Chip Erase Time is 8sec.

## WHITE ELECTRONIC DESIGNS

#### FIGURE 7 – AC WAVEFORMS FOR FLASH MEMORY READ OPERATIONS

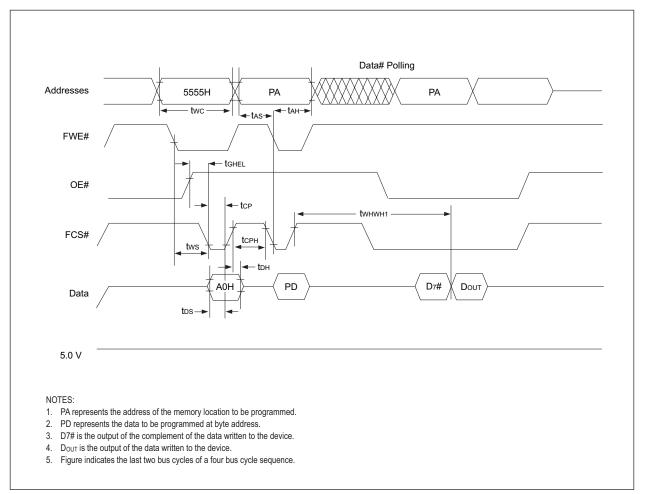

#### FIGURE 8 - WRITE/ERASE/PROGRAM OPERATION, FLASH MEMORY FWE# CONTROLLED

<sup>5.</sup> Figure indicates last two bus cycles of four bus cycle sequence.

WHITE ELECTRONIC DESIGNS

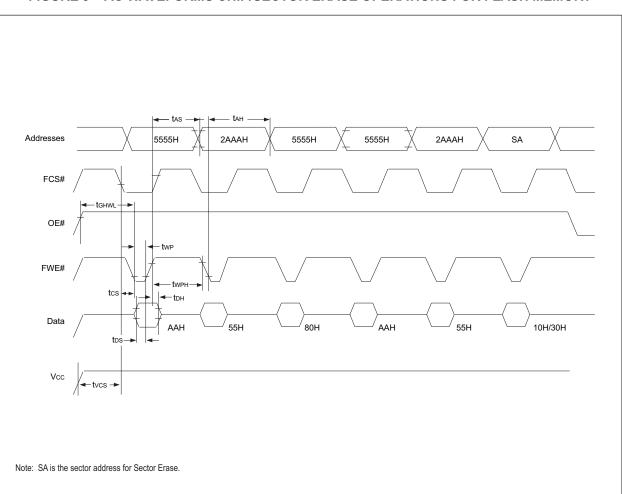

#### FIGURE 9 – AC WAVEFORMS CHIP/SECTOR ERASE OPERATIONS FOR FLASH MEMORY

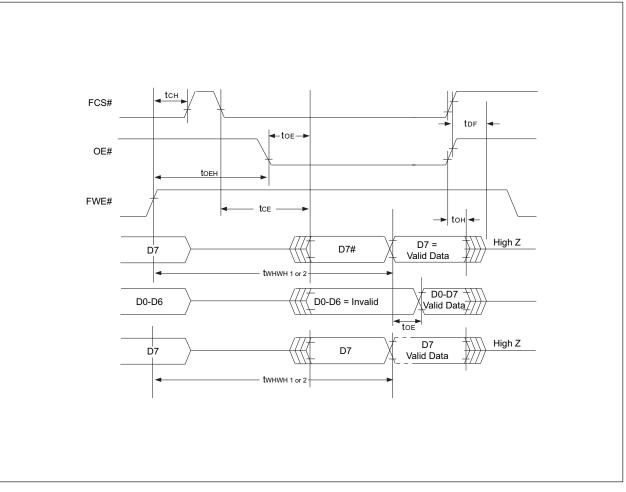

#### FIGURE 10 – AC WAVEFORMS FOR DATA# POLLING DURING EMBEDDED ALGORITHM OPERATIONS FOR FLASH MEMORY

11

#### FIGURE 11 – WRITE/ERASE/PROGRAM OPERATION FOR FLASH MEMORY, CS# CONTROLLED

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

# WHITE ELECTRONIC DESIGNS

ALL LINEAR DIMENSIONS ARE MILLIMETERS AND PARENTHETICALLY IN INCHES

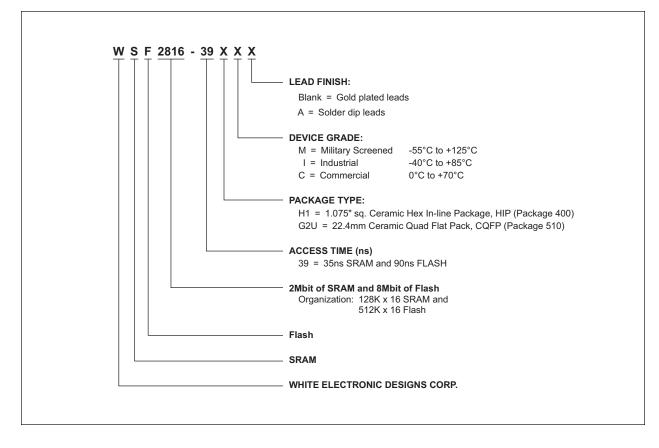

#### **ORDERING INFORMATION**