## M3V Series

## 9x14 mm, 3.3 Volt, HCMOS/TTL, VCXO

- HCMOS/TTL output to 160 MHz and excellent jitter (2.1 ps typ.) in a SMT package

- Phase-Locked Loops (PLL's), Clock Recovery, Reference Signal Tracking, Synthesizers, Frequency Modulation/Demodulation

$\mathbf{H}$   $\mathbf{H}$   $\mathbf{H}$

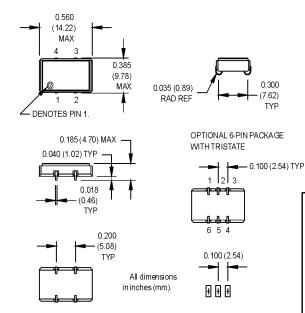

— 0.200 (5.08) - 0.050 (1.27) 0.346 (8.80)

SUGGESTED SOLDER PAD LAYOUT

Ħ

0.118 (3.00)

| FUNCTION            | 4 Pin<br>Pkg. | 6 Pin<br>Pkg. |

|---------------------|---------------|---------------|

| Control Voltage     | 1             | 1             |

| Tristate            |               | 2             |

| Circuit/Case Ground | 2             | 3             |

| Output              | 3             | 4             |

| N/C                 |               | 5             |

| +Vdd                | 4             | 6             |

|                           | PARAMETER                             | Symbol               | Min.                                                                                  | Тур.          | Max.                  | Units                  | Condition/Notes               |

|---------------------------|---------------------------------------|----------------------|---------------------------------------------------------------------------------------|---------------|-----------------------|------------------------|-------------------------------|

|                           | Frequency Range                       | F                    | 1.544                                                                                 |               | 160                   | MHz                    | See Note 1                    |

|                           | Operating Temperature                 | TA                   | (See Ordering Information)                                                            |               |                       |                        |                               |

|                           | Storage Temperature                   | Ts                   | -55                                                                                   |               | +125                  | °C                     |                               |

|                           | Frequency Stability                   | ∆ <b>F/F</b>         | (See Ordering Information)                                                            |               |                       |                        |                               |

|                           | Aging                                 |                      |                                                                                       |               |                       |                        |                               |

|                           | 1st Year                              |                      | -3/-5                                                                                 |               | +3/+5                 | ppm                    | < 52 MHz / ≥ 52 MHz           |

|                           | Thereafter (per year)                 |                      | -1/-2                                                                                 |               | +1/+2                 | ppm                    | < 52 MHz / ≥ 52 MHz           |

|                           | Pullability/APR                       |                      | (See Ordering Information)                                                            |               |                       |                        | Over control voltage          |

|                           | Control Voltage                       | Vc                   | 0.3                                                                                   | 1.65          | 3.0                   | ٧                      |                               |

|                           | Linearity                             |                      |                                                                                       |               | 10                    | %                      | Positive Monotonic Slope      |

| S                         | Modulation Bandwidth                  | fm                   | 10                                                                                    |               |                       | kHz                    |                               |

| tiol                      | Input Impedance                       | Zin                  | 50k                                                                                   |               |                       | Ohms                   |                               |

| ica                       | Input Voltage                         | Vdd                  | 3.135                                                                                 | 3.3           | 3.465                 | V                      |                               |

| ecit                      | Input Current                         | ldd                  |                                                                                       |               | 20                    |                        | 1.544 to 24 MHz               |

| Electrical Specifications |                                       |                      |                                                                                       |               | 55                    | mA                     | 24.001 to 96 MHz              |

|                           |                                       |                      |                                                                                       |               | 65                    | mA                     | 96.001 to 160 MHz             |

| ctri                      | Output Type                           |                      |                                                                                       |               |                       |                        | HCMOS/TTL                     |

| Ele                       | Load                                  |                      |                                                                                       |               |                       |                        | See Note 2                    |

|                           | 1.544 to 60 MHz                       |                      | 10 TTL or 50 pF                                                                       |               |                       |                        |                               |

|                           | 60.001 to 160 MHz                     |                      | 5 TTL or 30 pF                                                                        |               |                       |                        |                               |

|                           | Symmetry (Duty Cycle)                 |                      | (See Ordering Information)                                                            |               |                       |                        | See Note 3                    |

|                           | Logic "1" Level                       | Voh                  | 90% Vdd                                                                               |               |                       | V                      | HCMOS load                    |

|                           |                                       |                      | Vdd -0.5                                                                              |               |                       | V                      | TTL Load                      |

|                           | Logic "0" Level                       | Vol                  |                                                                                       |               | 10% Vdd               | V                      | HCMOS load                    |

|                           |                                       |                      |                                                                                       |               | 0.5                   | V                      | TTL load                      |

|                           | Rise/Fall Time                        | Tr/Tf                |                                                                                       | 3             | 10                    | ns                     | See Note 4                    |

|                           | Tristate Function                     |                      | Input Logic "1" or floating: output active Input Logic "0": output disables to high-Z |               |                       |                        |                               |

|                           | Start up Time                         |                      |                                                                                       | 4             |                       | ms                     |                               |

|                           | Phase Jitter @ 155.52 MHz             | φJ                   |                                                                                       | 3             | 5                     | ps RMS                 | Integrated 12 kHz - 20 MHz    |

|                           | Phase Noise (Typical)<br>@ 155.52 MHz | <b>10 H</b> z<br>-60 | <b>100 H</b> z<br>-90                                                                 | 1 kHz<br>-112 | <b>10 kHz</b><br>-123 | <b>100 kHz</b><br>-120 | Offset from carrier<br>dBc/Hz |

<sup>1.</sup> Frequencies above 70 MHz utilize a PLL design. Fundamental and PLL designs are available at other frequencies. Contact factory for availability.

MtronPTI reserves the right to make changes to the product(s) and service(s) described herein without notice. No liability is assumed as a result of their use or application.

<sup>\*</sup>Contact factory for availability. \*\*Other pull ranges available. Contact factory.

<sup>2.</sup> TTL load - see load circuit diagram #1. HCMOS load - see load circuit diagram #2.

3. Symmetry is measured at 1.4 V with TTL load, and at 50% Vdd with HCMOS load.

4. Rise/Fall times are measured between 0.5 V and 2.4 V with TTL load, and between 10% Vdd and 90% Vdd with HCMOS load.