SL1640C IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

T-77-09

# SL1640C & SL1641C

## **DOUBLE BALANCED MODULATORS**

The SL1640C and SL1641C are double balanced modulators intended for use in radio systems at frequencies up to 75MHz. The SL1640 has an integral output load resistor (Pin 5) together with an emitter follower output (Pin 6) whereas the SL1641 has a single output designed as a current drive to a tuned circuit.

# DECOUPLE F SL1640 7 SIGNAL INPUT CARRIER INPUT 3 SL1641 6 LOW IMP. OUTPUT DP8

Fig. 1 Pin connections (top view)

### **FEATURES**

- No External Bias Networks Needed

- Easy Interfacing

- Choice of Voltage or Current Outputs

#### **APPLICATIONS**

- Mixers In Radio Transceivers

- Phase Comparators

- Modulators

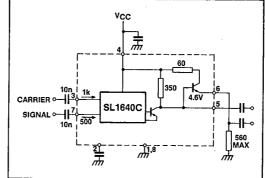

Fig. 2 Block diagram (SL1640C)

### **QUICK REFERENCE DATA**

Supply Voltage: 6V

Conversion Gain: 0dB

Maximum Inputs: 200mV rms

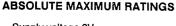

Fig. 3 Block diagram (SL1641C)

#### **ELECTRICAL CHARACTERISTICS**

# PLESSEY SEMICONDUCTORS T-77-09

Test conditions (unless otherwise stated): Supply voltage V<sub>cc</sub>: 6V Ambient temperature: -30°C to +85°C

| Characteristic              | Circuit            | Value |            |          | Units            | Conditions                                                                                                    |

|-----------------------------|--------------------|-------|------------|----------|------------------|---------------------------------------------------------------------------------------------------------------|

|                             |                    | Min.  | Тур.       | Max.     |                  |                                                                                                               |

| Supply current              | SL1640C<br>SL1641C |       | 12<br>10   | 18<br>15 | mA<br>mA         |                                                                                                               |

| Conversion gain             | SL1640C            | -3    | 0          | +3       | dB               |                                                                                                               |

| Conversion transconductance | SL1641C            | 1.7   | 2.5        | 3.5      | mmho             |                                                                                                               |

| Noise figure                | i '                | 1     | 10         |          | dB               |                                                                                                               |

| Carrier input impedance     |                    |       | 1          |          | kΩ               |                                                                                                               |

| Signal input impedance      | SL1640C<br>SL1641C |       | 500<br>1   |          | Ω<br>kΩ          |                                                                                                               |

| Maximum input voltage       | SL1640C<br>SL1641C |       | 210<br>250 |          | mV rms<br>mV rms |                                                                                                               |

| Signal leak<br>Carrier leak | SL1640C<br>SL1640C |       | -30<br>-30 |          | dB }             | Signal: 70mV rms, 1.75MHz Carrier: 100mV rms, 28.25 MHz Output: 30MHz                                         |

| Signal leak<br>Carrier leak | SL1641C<br>SL1641C |       | -18<br>-25 |          | dB }             | Signal: 70mV rms, 30MHz<br>Carrier: 100mV rms, 28.25 MHz<br>Output: 1.75MHz                                   |

| Intermodulation products    | SL1640C            |       | -45        |          | dB               | Signal1: 42.5mV rms, 1.75MHz<br>Signal2: 42.5mV rms, 2MHz<br>Carrier: 100mV rms, 28.25MHz<br>Output: 29.75MHz |

|                             | SL1641C            |       | -45        |          | dB               | Signal1: 42.5mV rms, 30MHz<br>Signal2: 42.5mV rms, 31MHz<br>Carrier:100mV rms, 28.25MHz<br>Output: 2.75MHz    |

#### **APPLICATION NOTES**

The SL1640C and SL1641C require input and output coupling capacitors which normally should be chosen to present a low reactance compared with the input and output impedances (see Electrical Characteristics). However, for minimum carrier leak at high frequencies the signal input should be driven from a low impedance source, in which case the signal input capacitor reactance should be comparable with the source impedance. Pin 2 must be decoupled to earth via a capacitor which presents the lowest possible impedance at both carrier and signal frequencies. The presence of these frequencies at Pin 2 would give rise to poor rejection figures and to distortion.

The output of the SL1641C is an open collector. If both sidebands are developed across the load its dynamic impedance must be less than 800 ohms. If only one sideband is significant this may be raised to 1600 ohms and it may be further raised if the maximum input swing of 200mV rms is not used. The DC resistance of the load should not exceed 800 ohms. If the circuit is connected to a +6V supply and the load impedance to +9V, the load may be increased to 1.8 kilohms at AC or DC. This, of course increases the gain of the

There are two outputs from the SL1640C; one is a voltage source of output impedance 350 ohms and 8pF and the other is the emitter of an emitter follower connected to the first output. The output on pin 6 requires a discrete load resistor of not less than 1500 ohms to ground. The emitter follower

output should not be used to drive capacitive loads as emitter followers act as detectors under such circumstances with resultant distortion and harmonic generation. Frequencyshaping components may be connected to the voltage output and the shaped signal taken from the emitter follower.

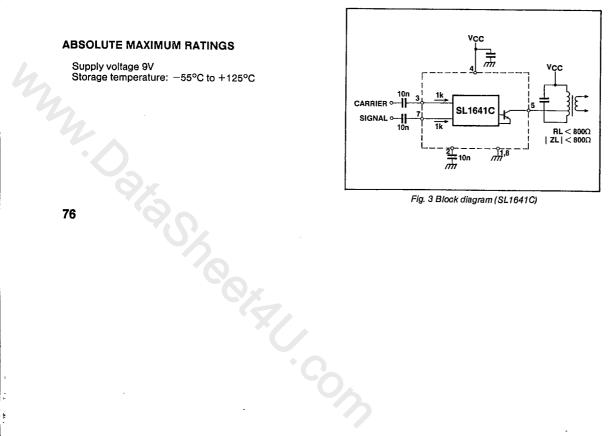

Fig. 4 Signal and carrier leak adjustment

Signal and carrier leak may be reduced by altering the bias on the carrier and signal input pins, as shown in Fig.4. With carrier but no signal R1 is adjusted for minimum carrier leak. A similar network is connected to the carrier input and with signal and carrier present, signal leak is minimised by means