SCI-PHY TO MULTIPHY ADAPTER CARD

# **APPS MULTI-PHY ADAPTER**

# SCI-PHY TO MULTI-PHY ADAPTER CARD

# REFERENCE DESIGN

# RELEASED ISSUE 1: FEBRUARY 1998

APPS MULTIPHY ADAPTER

PMC-Sierra,Inc.

REFERENCE DESIGN PMC-970438

ISSUE 1

PMC-970438

ISSUE 1

SCI-PHY TO MULTIPHY ADAPTER CARD

# **CONTENTS**

| 1  | FEAT  | FEATURES 1            |    |  |  |  |  |  |

|----|-------|-----------------------|----|--|--|--|--|--|

| 2  | APP   | LICATIONS             | 2  |  |  |  |  |  |

| 3  | REF   | REFERENCES3           |    |  |  |  |  |  |

| 4  | APP   | APPLICATION EXAMPLES  |    |  |  |  |  |  |

| 5  | BLO   | CK DIAGRAM            | 5  |  |  |  |  |  |

| 6  | DES   | CRIPTION              | 6  |  |  |  |  |  |

| 7  | CON   | NECTOR DESCRIPTIONS   | 7  |  |  |  |  |  |

| 8  | IMPL  | LEMENTATION           | 30 |  |  |  |  |  |

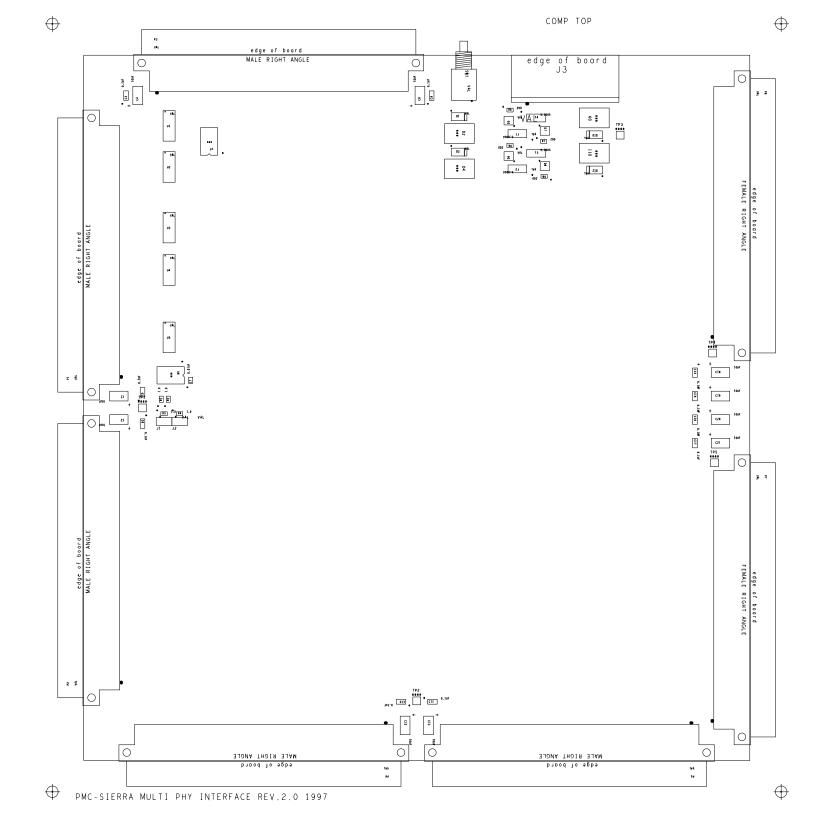

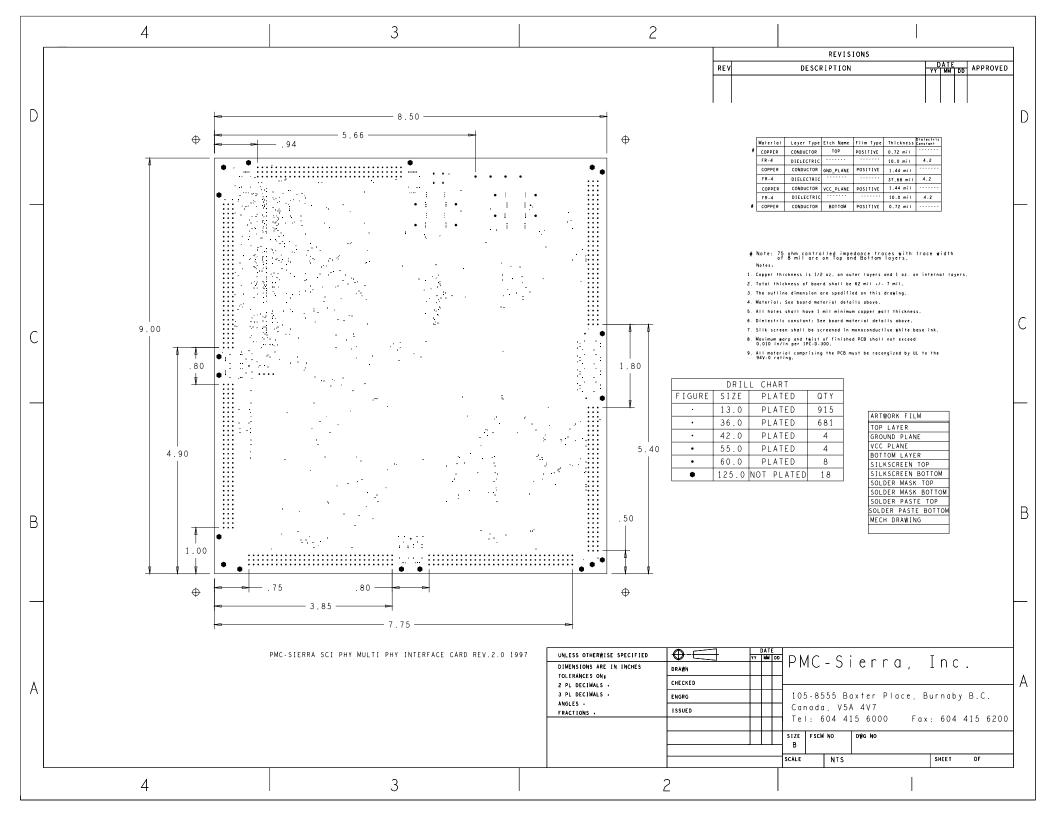

|    | 8.1   | ROOT DRAWING, SHEET 1 | 30 |  |  |  |  |  |

|    | 8.2   | SCIPHY_X, SHEET 2     | 30 |  |  |  |  |  |

|    | 8.3   | SCIPHY_Y, SHEET 3     | 30 |  |  |  |  |  |

|    | 8.4   | SWAN, SHEET 4         | 31 |  |  |  |  |  |

|    | 8.5   | MICRO_MUX, SHEET 5    | 31 |  |  |  |  |  |

|    | 8.6   | MULTIPHY _X, SHEET 6  | 33 |  |  |  |  |  |

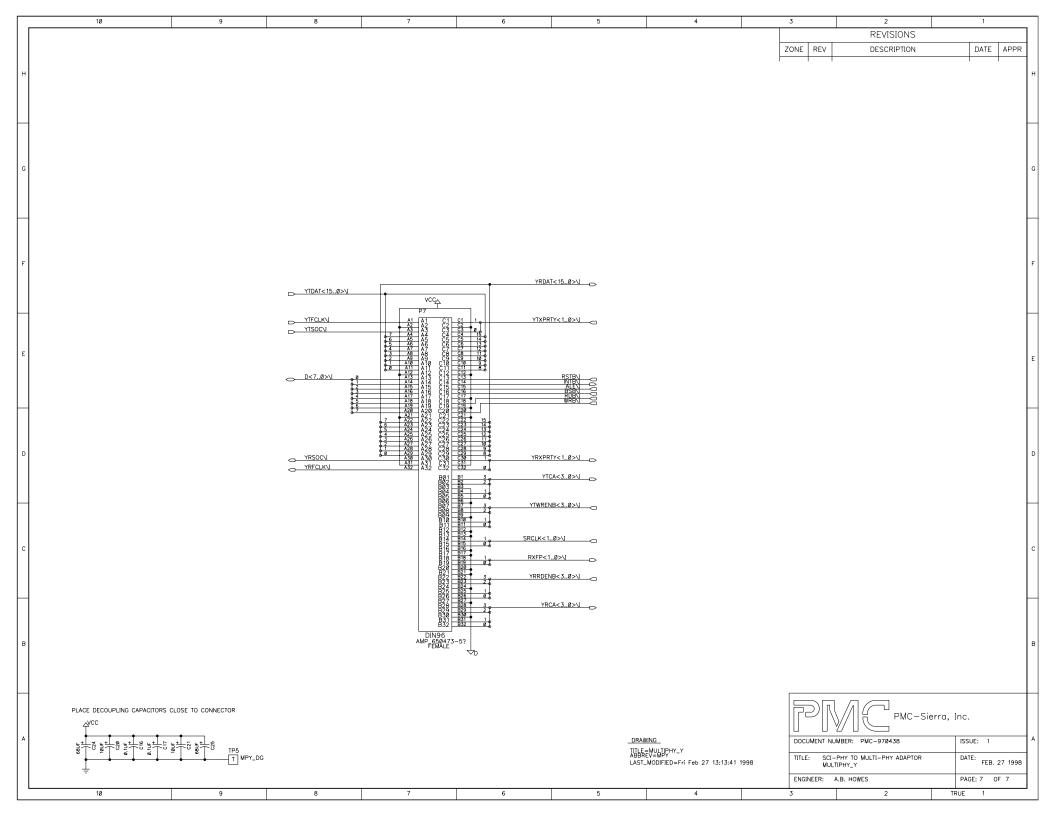

|    | 8.7   | MULTIPHY_Y, SHEET 7   | 33 |  |  |  |  |  |

| 9  | SCH   | SCHEMATICS3           |    |  |  |  |  |  |

| 10 | MAT   | MATERIAL LIST         |    |  |  |  |  |  |

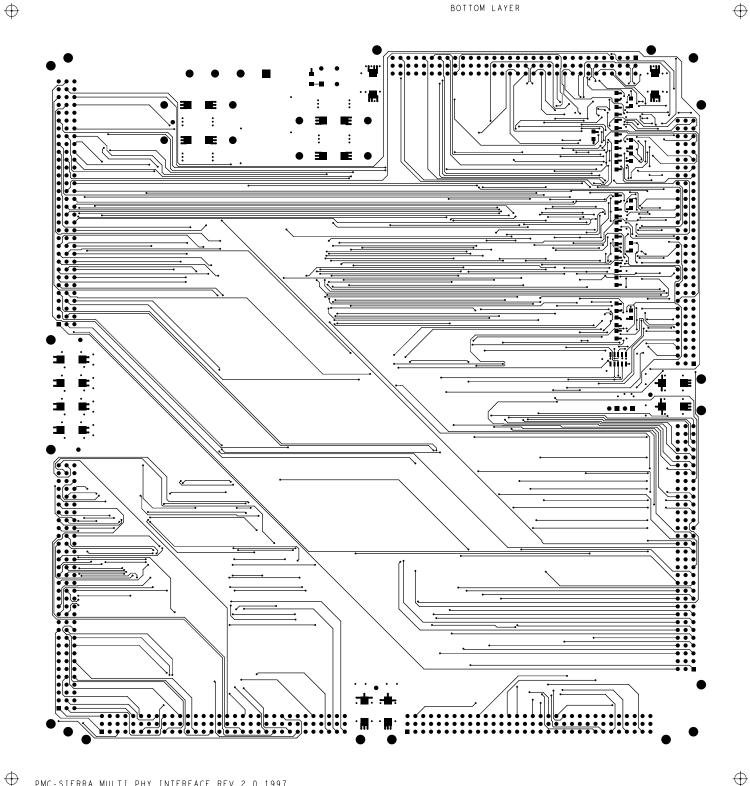

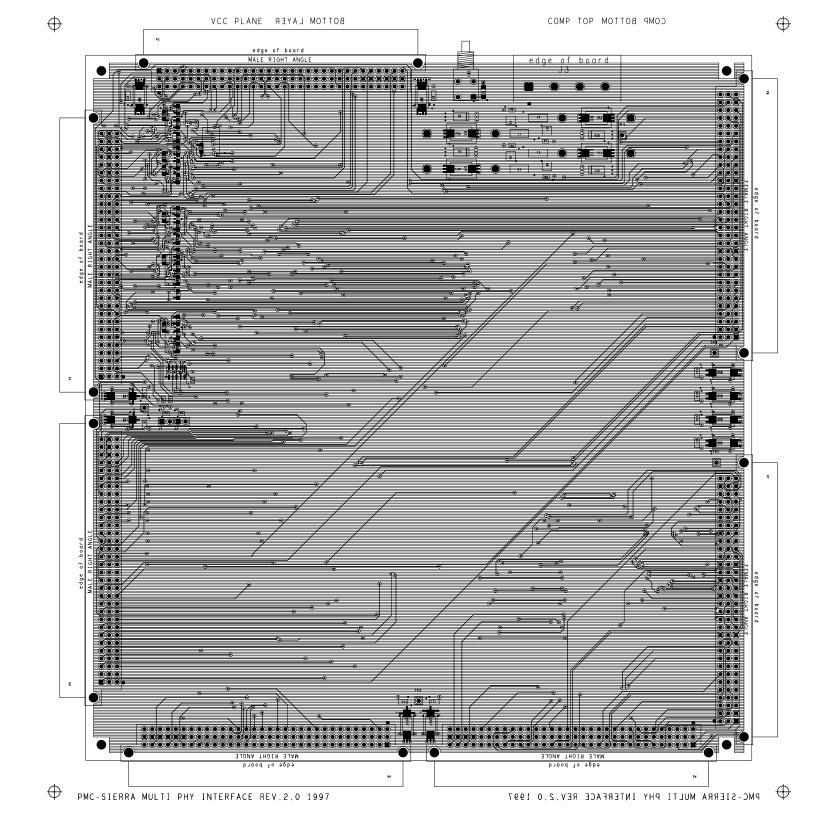

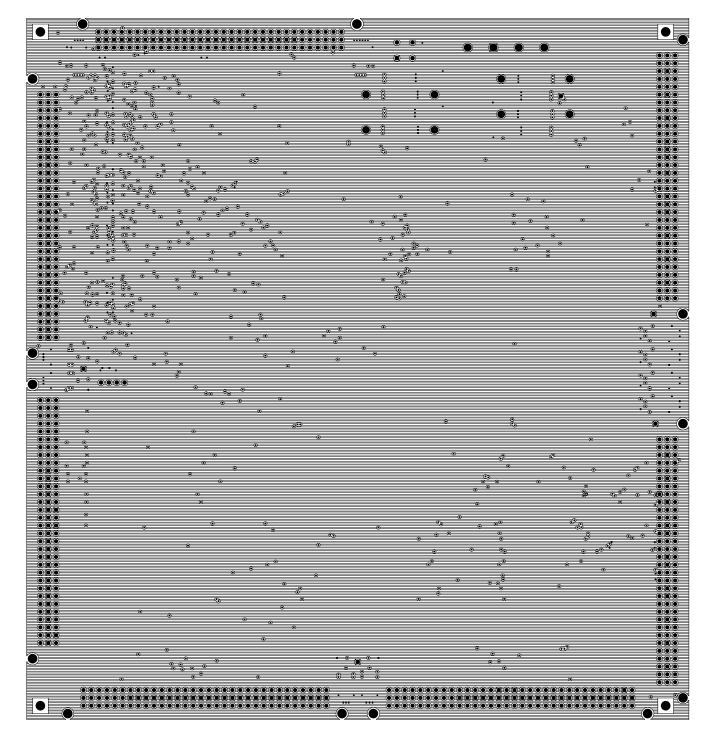

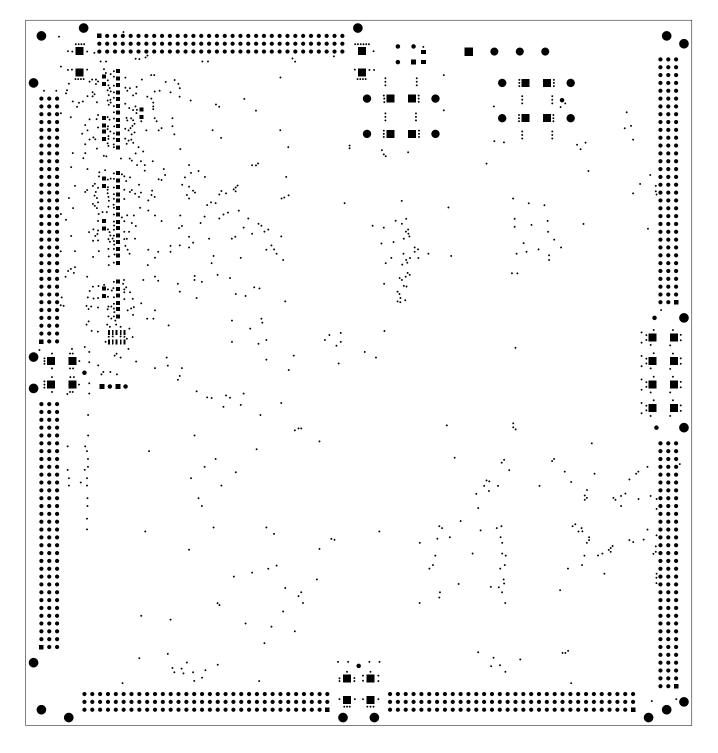

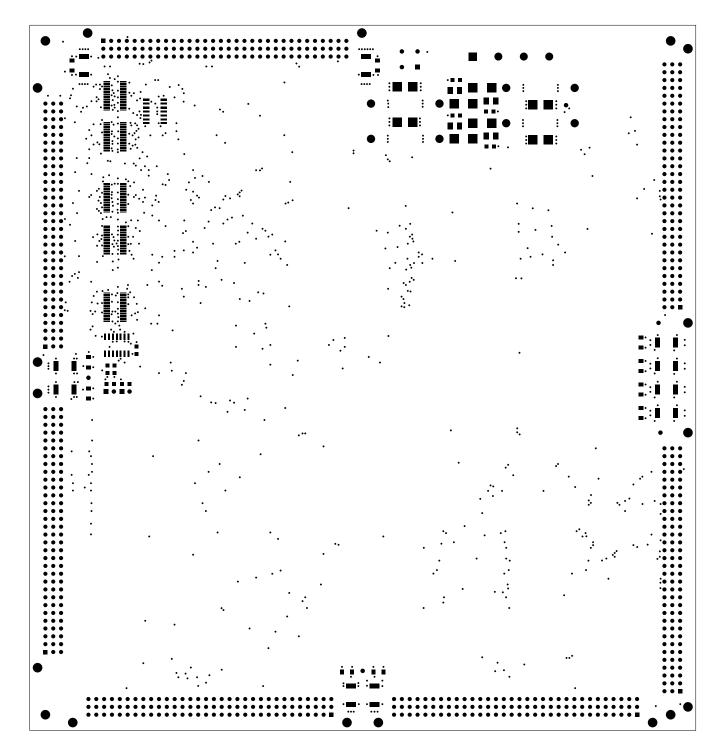

| 11 | I AYC | LAYOUT                |    |  |  |  |  |  |

SCI-PHY TO MULTIPHY ADAPTER CARD

# **LIST OF FIGURES**

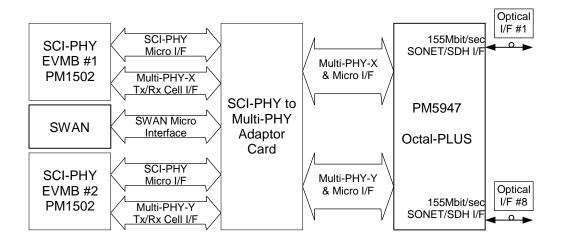

| FIGURE 1 | MULTI-PHY ADAPTER CARD CONNECTING TWO SCI-PH EVMBS AND A SWAN BOARD TO OCTAL-PLUS REFERENCE DESIGN. |    |

|----------|-----------------------------------------------------------------------------------------------------|----|

| FIGURE 2 | MICRO INTERFACE SELECTION ILIMPER POSITIONS                                                         | 32 |

PMC-970438

ISSUE 1

SCI-PHY TO MULTIPHY ADAPTER CARD

# **LIST OF TABLES**

| TABLE 1 | MULTI-PHY ADAPTER CARD CONNECTORS                   | 7  |

|---------|-----------------------------------------------------|----|

| TABLE 2 | SCI-PHY #1 AND SCI-PHY #2 MICRO INTERFACE CONNECTOR | 8  |

| TABLE 3 | SCI-PHY #1 MULTI-PHY INTERFACE CONNECTOR            | 10 |

| TABLE 4 | SCI-PHY #2 MULTI-PHY INTERFACE                      | 14 |

| TABLE 5 | SWAN CONNECTOR                                      | 17 |

| TABLE 6 | MULTI-PHY-X INTERFACE                               | 19 |

| TABLE 7 | MULTI-PHY-Y INTERFACE CONNECTOR                     | 24 |

| TABLE 8 | MICRO INTERFACE SELECTION JUMPER POSITIONS          | 32 |

| TABLE 9 | BILL OF MATERIAL                                    | 37 |

SCI-PHY TO MULTIPHY ADAPTER CARD

This page intentionally left blank

SCI-PHY TO MULTIPHY ADAPTER CARD

### 1 FEATURES

- Flexibility to select between ordinary microprocessor control or enhanced with system reference clock features.

- Direct SCI-PHY to multi-PHY connection.

REFERENCE DESIGN PMC-970438

SCI-PHY TO MULTIPHY ADAPTER CARD

# **2** APPLICATIONS

• Interconnect 2 SCI-PHY EVMB with dual multi-PHY ATM daughter board.

SCI-PHY TO MULTIPHY ADAPTER CARD

### 3 REFERENCES

- 1. PMC-Sierra Inc., Octal S/UNI-PLUS with Automatic Protection Switching Optical Reference Design, Issue 2, February 1998

- PMC-Sierra Inc., Saturn Compliant Interface for ATM Physical Layer Interconnect Evaluation Motherboard (SCI-PHY EVMB) Specification, Issue 3 June 1995

- 3. PMC-Sierra Inc., SWAN Timing and Micro Reference Design, Preliminary Issue 1, March 1997

SCI-PHY TO MULTIPHY ADAPTER CARD

# 4 APPLICATION EXAMPLES

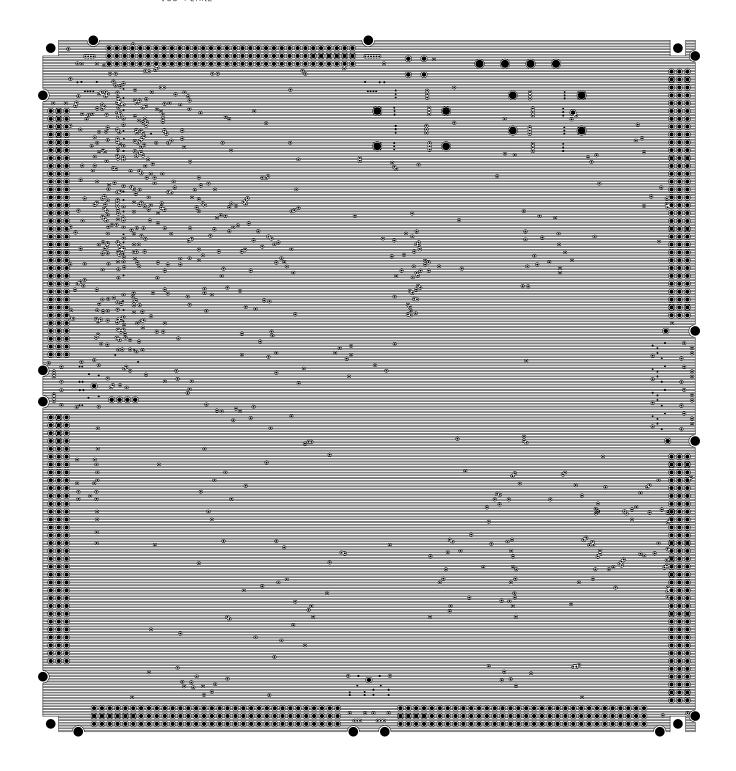

Figure 1 Multi-PHY adapter card connecting two SCI-PHY EVMBs and a SWAN board to Octal-PLUS Reference design.

The block diagram below is an example of how the SCI-PHY to Multi-PHY Adapter Card can be utilized to test the Octal PLUS reference design.

SCI-PHY TO MULTIPHY ADAPTER CARD

# 5 BLOCK DIAGRAM

ISSUE 1

SCI-PHY TO MULTIPHY ADAPTER CARD

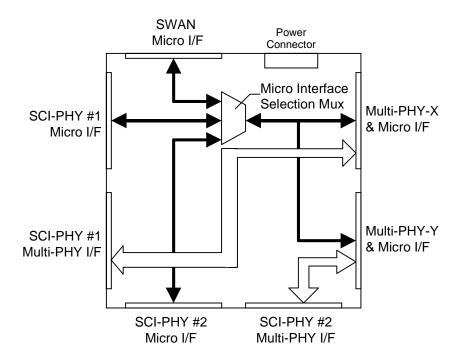

## 6 DESCRIPTION

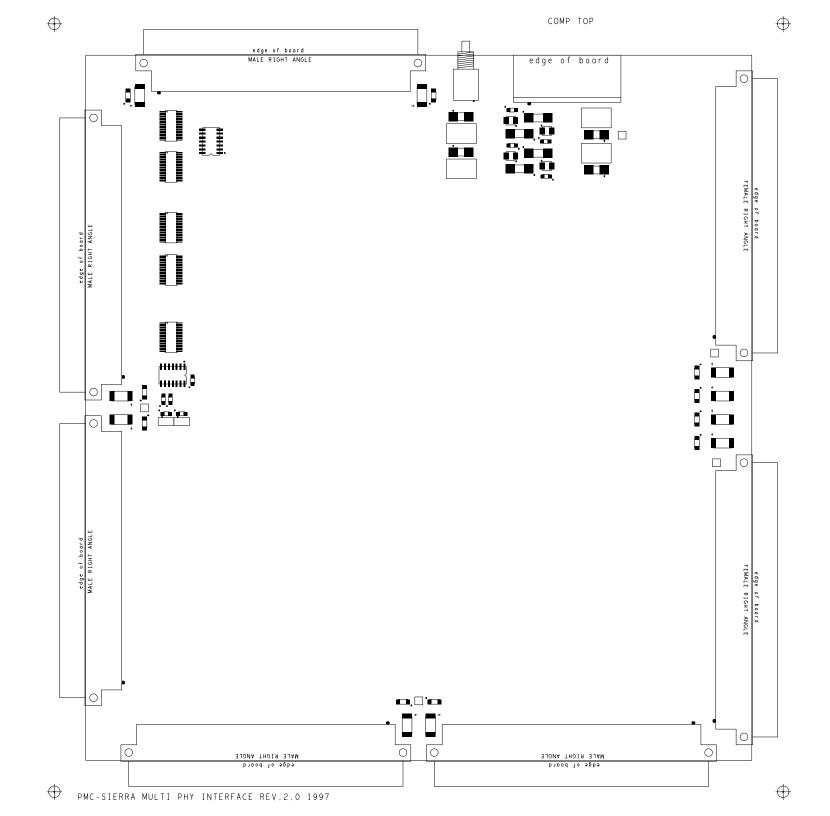

The Multi-PHY Adapter Card (MAC) facilitates the connection of two SCI-PHY EVMBs and a SWAN card to an ATM daughter card with two multi-PHY interfaces. Also, the MAC distributes power and microprocessor control to the SCI-PHY EVMBs, SWAN card and the multi-PHY interfaces.

The microprocessor access to the Multi-PHY-X and Multi-PHY-Y interfaces is multiplexed between the SWAN, SCI-PHY EVMB #1 or SCI-PHY EVMB #2 microprocessor. Selection between these microprocessor interfaces is made with jumpers.

The Multi-PHY-X Interface connects directly to the SCI-PHY #1 multi-PHY interface and the Multi-PHY-Y Interface connects directly to the SCI-PHY #2 multi-PHY interface

The Power Connection block allows connection to an external power supply and includes over-current protection. Therefore, power connections to the other MAC peripheral boards are not required.

SCI-PHY TO MULTIPHY ADAPTER CARD

# **7 CONNECTOR DESCRIPTIONS**

The adapter board contains the following connectors:

Table 1 Multi-PHY Adapter Card Connectors

| Connector                           | Description                                                                                                                      |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| SCI-PHY #1<br>Micro I/F             | 96 pin DIN female connector containing micro control signals from SCI-PHY #1 Micro Interface.                                    |

| SCI-PHY #1<br>Multi-PHY I/F         | 96 pin DIN female connector containing multi-PHY signals from SCI-PHY #1 Multi-PHY Interface.                                    |

| SCI-PHY #2<br>Micro I/F             | 96 pin DIN female connector containing micro control signals from SCI-PHY #2 Micro Interface.                                    |

| SCI-PHY #2<br>Multi-PHY I/F         | 96 pin DIN female connector containing multi-PHY signals from SCI-PHY #2 Multi-PHY Interface.                                    |

| SWAN<br>Interface                   | 96 pin DIN female connector containing micro control signals from SWAN Timing and Micro card.                                    |

| Micro &<br>Multi-PHY-X<br>Interface | 96 pin DIN male connector containing microprocessor address signals and multi-PHY signals to the Multi-PHY-X Interface.          |

| Micro &<br>Multi-PHY-Y<br>Interface | 96 pin DIN male connector containing microprocessor data and control signals and multi-PHY signals to the Multi-PHY-X Interface. |

SCI-PHY TO MULTIPHY ADAPTER CARD

The SCI-PHY EVMB connectors are exactly the same and are described in the table below.

Table 2 SCI-PHY #1 and SCI-PHY #2 Micro Interface Connector

| Pin Name                                                                     | Туре   | Pin#                                                 | Function                                                                                                                                                                           |

|------------------------------------------------------------------------------|--------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSB[0]<br>CSB[1]<br>CSB[2]<br>CSB[3]<br>CSB[4]<br>CSB[5]<br>CSB[6]<br>CSB[6] | Input  | A25<br>A26<br>A27<br>A28<br>A29<br>A30<br>A31<br>A32 | Chip Select. CSB[7:0] asserts low to enable reading from and writing to the micro interface of the Multi-PHY interface. CSB[7:0] routes through the Micro Interface Selection mux. |

| GND                                                                          | Power  | B1-<br>B25                                           | Ground                                                                                                                                                                             |

| VCC                                                                          | Power  | B26-<br>B32                                          | +5V Power                                                                                                                                                                          |

| RSTB                                                                         | Input  | C2                                                   | Reset. RSTB is an active low hardware reset that routes through the Micro Interface Selection mux.                                                                                 |

| WRB                                                                          | Input  | C3                                                   | Write Strobe. WRB is an active low write strobe that routes through the Micro Interface Selection mux.                                                                             |

| RDB                                                                          | Input  | C4                                                   | Read Enable. RDB is an active low read enable that routes through the Micro Interface Selection mux.                                                                               |

| ALE                                                                          | Input  | C5                                                   | Address Latch Enable. ALE is an active high address latch enable that routes through the Micro Interface Selection mux.                                                            |

| INTB                                                                         | Output | C6                                                   | Interrupt. INTB is an active low maskable hardware interrupt and routes through the Micro Interface Selection mux.                                                                 |

ISSUE 1

| Pin Name                                                     | Туре  | Pin #                                                | Function                                                                                                               |

|--------------------------------------------------------------|-------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| D[0] D[1] D[2] D[3] D[4] D[5] D[6] D[7]                      | I/O   | C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16  | Data Bus. D[7:0] is an eight bit microprocessor data bus that routes through the Micro Interface Selection mux.        |

| A[0]<br>A[1]<br>A[2]<br>A[3]<br>A[4]<br>A[5]<br>A[6]<br>A[7] | Input | C17<br>C18<br>C19<br>C20<br>C21<br>C22<br>C23<br>C24 | Address Bus. A[7:0] is an eight bit micro processor address bus that routes through the Micro Interface Selection mux. |

|                                                              | N/C   | A1-<br>A24,<br>C1,<br>C7,<br>C8,<br>C25-<br>C32      | Unconnected pins                                                                                                       |

SCI-PHY TO MULTIPHY ADAPTER CARD

The SCI-PHY EVMB #1 Multi-PHY interface is described in the table below. All signals connect directly to the Multi-PHY-X Interface.

Table 3 SCI-PHY #1 Multi-PHY Interface Connector

| Pin Name                                                                                                                                               | Туре   | Pin #                                                                                                        | Function                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDAT[0] TDAT[1] TDAT[2] TDAT[3] TDAT[4] TDAT[5] TDAT[6] TDAT[6] TDAT[7] TDAT[8] TDAT[9] TDAT[10] TDAT[11] TDAT[12] TDAT[13] TDAT[14] TDAT[15]          | Input  | A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15<br>A16          | Transmit Data. TDAT[15:0] transfers data to the Multi-PHY-X Interface. TDAT[7:0] corresponds to the least significant byte of the data word and TDAT[15:8] corresponds to the most significant byte of the data word. TDAT[15:0] is synchronous to the rising edge of TFCLK. TDAT[15:0] routes to the Multi-PHY-X Interface.        |

| RDAT[0] RDAT[1] RDAT[2] RDAT[3] RDAT[4] RDAT[5] RDAT[6] RDAT[6] RDAT[7] RDAT[8] RDAT[9] RDAT[10] RDAT[11] RDAT[11] RDAT[12] RDAT[13] RDAT[14] RDAT[15] | Output | A17<br>A18<br>A19<br>A20<br>A21<br>A22<br>A23<br>A24<br>A25<br>A26<br>A27<br>A28<br>A29<br>A30<br>A31<br>A32 | Receive Data. RDAT[15:0] transfers data from the Multi-PHY-X Interface. RDAT[7:0] corresponds to the least significant byte of the data word and RDAT[15:8] corresponds to the most significant byte of the data word. RDAT[15:0] is synchronous to the rising edge of RFCLK. RDAT[15:0] originates from the Multi-PHY-X Interface. |

ISSUE 1

| Pin Name                     | Туре   | Pin #                             | Function                                                                                                                                                                                                                                                                                          |

|------------------------------|--------|-----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                          | Power  | B1-<br>B23,<br>C2,<br>C16,<br>C18 | Ground                                                                                                                                                                                                                                                                                            |

| PWR +5V                      | Power  | B29 -<br>B32                      | +5V Power                                                                                                                                                                                                                                                                                         |

| TFCLK                        | Input  | C1                                | Transmit FIFO Clock. TFCLK synchronizes TDAT[15:0] to the Multi-PHY Interface. The Multi-PHY Interface updates TCAn and samples TWRENnB, TSOC, TXPRTY[1:0], and TDAT[15:0] on the rising edge of TFCLK. TFCLK routes to the Multi-PHY-X Interface.                                                |

| TSOC                         | Input  | C3                                | Transmit Start Of Cell. TSOC marks the start of cell on the TDAT bus. TSOC asserts when the first word of the cell structure is present on the TDAT bus. TSOC is synchronous to the rising edge of TFCLK and routes to the Multi-PHY-X Interface.                                                 |

| TXPRTY[0]<br>TXPRTY[1]       | Input  | C4<br>C5                          | Transmit Parity. TXPRTY[1:0] indicates the parity of the TDAT[15:0] bus. TXPRTY[1] is the parity calculation over the TDAT[15:8] bus. TXPRTY[0] is the parity calculation over the TDAT[7:0] bus. TXPRTY[1:0] is synchronous to the rising edge of TFCLK and routes to the Multi-PHY-X Interface. |

| TCA1<br>TCA2<br>TCA3<br>TCA4 | Output | C6<br>C7<br>C8<br>C9              | Transmit Cell Available. TCAn indicates when the nth channel of the Multi-PHY-X Interface can accept data. Four TCA inputs provide support for four channels. TCAn is synchronous to the rising edge of TFCLK and originates from the Multi-PHY-X Interface.                                      |

ISSUE 1

| Pin Name                                 | Туре   | Pin #                    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------|--------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TWREN1B<br>TWREN2B<br>TWREN3B<br>TWREN4B | Input  | C10<br>C11<br>C12<br>C13 | Transmit Write Enable. The active low TWRENnB initiates writes to the nth channel transmit FIFO of the Multi-PHY-X Interface. Data on TDAT[15:0] is written into the nth channel transmit FIFO when the nth Multi-PHY-X Interface channel samples an asserted TWRENnB on the rising edge of TFCLK. No data is written into the transmit FIFO when the nth Multi-PHY-X Interface channel samples a negated TWRENnB on the rising edge of TFCLK. TWRENnB routes to the Multi-PHY-X Interface. |

| RFCLK                                    | Input  | C17                      | Receive FIFO Clock. RFCLK synchronizes RDAT[15:0] from the Multi-PHY Interface. The Multi-PHY Interface samples RWRENnB and updates RCAn, RSOC, RXPRTY[1:0], and RDAT[15:0] on the rising edge of RFCLK. RFCLK routes to the Multi-PHY-X Interface.                                                                                                                                                                                                                                         |

| RSOC                                     | Output | C19                      | Receive Start Of Cell. RSOC marks the start of cell on the RDAT bus. RSOC asserts when the first word of the cell structure is present on the RDAT bus. RSOC is synchronous to the rising edge of RFCLK and originates from the Multi-PHY-X Interface.                                                                                                                                                                                                                                      |

| RXPRTY[0]<br>RXPRTY[1]                   | Output | C20<br>C21               | Receive Parity. RXPRTY[1:0] indicates the parity of the RDAT[15:0] bus. RXPRTY[1] is the parity calculation over the RDAT[15:8] bus. RXPRTY[0] is the parity calculation over the RDAT[7:0] bus. RXPRTY[1:0] is synchronous to the rising edge of RFCLK and originates from the Multi-PHY-X Interface.                                                                                                                                                                                      |

| RCA1<br>RCA2<br>RCA3<br>RCA4             | Output | C22<br>C23<br>C24<br>C25 | Receive Cell Available. RCAn indicates when the nth channel of the Multi-PHY-X Interface contains valid data. Four RCA inputs provide support for four channels. RCAn is synchronous to the rising edge of RFCLK and originates from the Multi-PHY-X Interface.                                                                                                                                                                                                                             |

ISSUE 1

SCI-PHY TO MULTIPHY ADAPTER CARD

| Pin Name                                 | Туре  | Pin#                                        | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|-------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRDEN1B<br>RRDEN2B<br>RRDEN3B<br>RRDEN4B | Input | C26<br>C27<br>C28<br>C29                    | Receive Read Enable. The active low RRDENnB initiates reads from the nth channel receive FIFO of the Multi-PHY-X Interface. Data is read from the nth Multi-PHY-X Interface channel receive FIFO and put on RDAT[15:0] when the nth Multi-PHY-X Interface channel samples an asserted RRDENnB on the rising edge of RFCLK. No data is read from the receive FIFO when the nth Multi-PHY-X Interface channel samples a negated RRDENnB on the rising edge of RFCLK. RRDENnB routes to the Multi-PHY-X Interface. |

|                                          | N/C   | B24-<br>B28,<br>C14,<br>C15,<br>C30-<br>C32 | Unconnected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

The SCI-PHY EVMB #2 Multi-PHY interface is described in the table below. All signals connect directly to the Multi-PHY-Y Interface.

SCI-PHY TO MULTIPHY ADAPTER CARD

# Table 4 SCI-PHY #2 Multi-PHY Interface

| Pin Name                                                                                                                                               | Туре   | Pin #                                                                                                        | Function                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TDAT[0] TDAT[1] TDAT[2] TDAT[3] TDAT[4] TDAT[5] TDAT[6] TDAT[6] TDAT[7] TDAT[8] TDAT[9] TDAT[10] TDAT[11] TDAT[12] TDAT[13] TDAT[14] TDAT[15]          | Input  | A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13<br>A14<br>A15<br>A16          | Transmit Data. TDAT[15:0] transfers data to the Multi-PHY-Y Interface. TDAT[7:0] corresponds to the least significant byte of the data word and TDAT[15:8] corresponds to the most significant byte of the data word. TDAT[15:0] is synchronous to the rising edge of TFCLK. TDAT[15:0] routes to the Multi-PHY-Y Interface.        |

| RDAT[0] RDAT[1] RDAT[2] RDAT[3] RDAT[4] RDAT[5] RDAT[6] RDAT[6] RDAT[7] RDAT[8] RDAT[9] RDAT[10] RDAT[11] RDAT[11] RDAT[12] RDAT[13] RDAT[14] RDAT[15] | Output | A17<br>A18<br>A19<br>A20<br>A21<br>A22<br>A23<br>A24<br>A25<br>A26<br>A27<br>A28<br>A29<br>A30<br>A31<br>A32 | Receive Data. RDAT[15:0] transfers data from the Multi-PHY-Y Interface. RDAT[7:0] corresponds to the least significant byte of the data word and RDAT[15:8] corresponds to the most significant byte of the data word. RDAT[15:0] is synchronous to the rising edge of RFCLK. RDAT[15:0] originates from the Multi-PHY-Y Interface. |

| GND                                                                                                                                                    | Power  | B1-<br>B23,<br>C2,<br>C16,<br>C18                                                                            | Ground                                                                                                                                                                                                                                                                                                                              |

ISSUE 1

| Pin Name                     | Туре   | Pin #                | Function                                                                                                                                                                                                                                                                                          |

|------------------------------|--------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PWR +5V                      | Power  | B29 -<br>B32         | +5V Power                                                                                                                                                                                                                                                                                         |

| TFCLK                        | Input  | C1                   | Transmit FIFO Clock. TFCLK synchronizes TDAT[15:0] to the Multi-PHY Interface. The Multi-PHY Interface updates TCAn and samples TWRENnB, TSOC, TXPRTY[1:0], and TDAT[15:0] on the rising edge of TFCLK. TFCLK routes to the Multi-PHY-Y Interface.                                                |

| TSOC                         | Input  | C3                   | Transmit Start Of Cell. TSOC marks the start of cell on the TDAT bus. TSOC asserts when the first word of the cell structure is present on the TDAT bus. TSOC is synchronous to the rising edge of TFCLK and routes to the Multi-PHY-Y Interface.                                                 |

| TXPRTY[0]<br>TXPRTY[1]       | Input  | C4<br>C5             | Transmit Parity. TXPRTY[1:0] indicates the parity of the TDAT[15:0] bus. TXPRTY[1] is the parity calculation over the TDAT[15:8] bus. TXPRTY[0] is the parity calculation over the TDAT[7:0] bus. TXPRTY[1:0] is synchronous to the rising edge of TFCLK and routes to the Multi-PHY-Y Interface. |

| TCA1<br>TCA2<br>TCA3<br>TCA4 | Output | C6<br>C7<br>C8<br>C9 | Transmit Cell Available. TCAn indicates when the nth channel of the Multi-PHY-Y Interface can accept data. Four TCA inputs provide support for four channels. TCAn is synchronous to the rising edge of TFCLK and originates from the Multi-PHY-Y Interface.                                      |

ISSUE 1

| Pin Name                                 | Туре   | Pin #                    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------|--------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TWREN1B<br>TWREN2B<br>TWREN3B<br>TWREN4B | Input  | C10<br>C11<br>C12<br>C13 | Transmit Write Enable. The active low TWRENnB initiates writes to the nth channel transmit FIFO of the Multi-PHY-Y Interface. Data on TDAT[15:0] is written into the nth channel transmit FIFO when the nth Multi-PHY-Y Interface channel samples an asserted TWRENnB on the rising edge of TFCLK. No data is written into the transmit FIFO when the nth Multi-PHY-Y Interface channel samples a negated TWRENnB on the rising edge of TFCLK. TWRENnB routes to the Multi-PHY-Y Interface. |

| RFCLK                                    | Input  | C17                      | Receive FIFO Clock. RFCLK synchronizes RDAT[15:0] from the Multi-PHY Interface. The Multi-PHY Interface samples RWRENnB and updates RCAn, RSOC, RXPRTY[1:0], and RDAT[15:0] on the rising edge of RFCLK. RFCLK routes to the Multi-PHY-Y Interface.                                                                                                                                                                                                                                         |

| RSOC                                     | Output | C19                      | Receive Start Of Cell. RSOC marks the start of cell on the RDAT bus. RSOC asserts when the first word of the cell structure is present on the RDAT bus. RSOC is synchronous to the rising edge of RFCLK and originates from the Multi-PHY-Y Interface.                                                                                                                                                                                                                                      |

| RXPRTY[0]<br>RXPRTY[1]                   | Output | C20<br>C21               | Receive Parity. RXPRTY[1:0] indicates the parity of the RDAT[15:0] bus. RXPRTY[1] is the parity calculation over the RDAT[15:8] bus. RXPRTY[0] is the parity calculation over the RDAT[7:0] bus. RXPRTY[1:0] is synchronous to the rising edge of RFCLK and originates from the Multi-PHY-Y Interface.                                                                                                                                                                                      |

| RCA1<br>RCA2<br>RCA3<br>RCA4             | Output | C22<br>C23<br>C24<br>C25 | Receive Cell Available. RCAn indicates when the nth channel of the Multi-PHY-Y Interface contains valid data. Four RCA inputs provide support for four channels. RCAn is synchronous to the rising edge of RFCLK and originates from the Multi-PHY-Y Interface.                                                                                                                                                                                                                             |

SCI-PHY TO MULTIPHY ADAPTER CARD

| Pin Name                                 | Туре  | Pin #                                       | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|-------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRDEN1B<br>RRDEN2B<br>RRDEN3B<br>RRDEN4B | Input | C26<br>C27<br>C28<br>C29                    | Receive Read Enable. The active low RRDENnB initiates reads from the nth channel receive FIFO of the Multi-PHY-Y Interface. Data is read from the nth Multi-PHY-Y Interface channel receive FIFO and put on RDAT[15:0] when the nth Multi-PHY-Y Interface channel samples an asserted RRDENnB on the rising edge of RFCLK. No data is read from the receive FIFO when the nth Multi-PHY-Y Interface channel samples a negated RRDENnB on the rising edge of RFCLK. RRDENnB routes to the Multi-PHY-Y Interface. |

|                                          | N/C   | B24-<br>B28,<br>C14,<br>C15,<br>C30-<br>C32 | Unconnected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

# Table 5 SWAN Connector

| Pin Name       | Туре   | Pin #    | Function                                                                                                                                                                                          |

|----------------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TXFP+<br>TXFP- | Output | A1<br>A2 | Transmit Frame Pulse. TXFP+/- is a differential signal pair used for system synchronization feedback. TXFP+/- is synchronous to SRCLK+/- and originates from the Multi-PHY-X Interface connector. |

| RALM           | Output | A4       | Receive Alarm. RALM indicates a Multi-PHY Interface channel has a loss of signal condition. RALM asserts high and originates from the Multi-PHY-X Interface connector.                            |

| RXFP+<br>RXFP- | Output | A6<br>A7 | Receive Frame Pulse. RXFP+/- is a differential signal pair used for system synchronization feedback. RXFP+/- is synchronous to SRCLK+/- and originates from the Multi-PHY-Y Interface connector.  |

ISSUE 1

| Pin Name                                                                     | Туре   | Pin #                                                | Function                                                                                                                                                                                    |

|------------------------------------------------------------------------------|--------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SRCLK+<br>SRCLK-                                                             | Input  | A14<br>A15                                           | System Reference Clock. SRCLK+/- is a differential system reference clock for the PHY channels of the Multi-PHY Interface. SRCLK+/- routes directly to the Multi-PHY-Y Interface connector. |

| CSB[0]<br>CSB[1]<br>CSB[2]<br>CSB[3]<br>CSB[4]<br>CSB[5]<br>CSB[6]<br>CSB[6] | Input  | A25<br>A26<br>A27<br>A28<br>A29<br>A30<br>A31<br>A32 | Chip Select. CSB[7:0] asserts low to enable reading from and writing to the micro interface of the Multi-PHY interface. CSB[7:0] routes through the Micro Interface Selection mux.          |

| GND                                                                          | Power  | B1-<br>B25                                           | Ground                                                                                                                                                                                      |

| VCC                                                                          | Power  | B26-<br>B32                                          | +5V Power                                                                                                                                                                                   |

| RSTB                                                                         | Input  | C2                                                   | Reset. RSTB is an active low hardware reset that routes through the Micro Interface Selection mux.                                                                                          |

| WRB                                                                          | Input  | C3                                                   | Write Strobe. WRB is an active low write strobe that routes through the Micro Interface Selection mux.                                                                                      |

| RDB                                                                          | Input  | C4                                                   | Read Enable. RDB is an active low read enable that routes through the Micro Interface Selection mux.                                                                                        |

| INTB                                                                         | Output | C6                                                   | Interrupt. INTB is an active low maskable hardware interrupt and routes through the Micro Interface Selection mux.                                                                          |

| D[0] D[1] D[2] D[3] D[4] D[5] D[6] D[7]                                      | I/O    | C9<br>C10<br>C11<br>C12<br>C13<br>C14<br>C15<br>C16  | Data Bus. D[7:0] is an eight bit microprocessor data bus that routes through the Micro Interface Selection mux.                                                                             |

SCI-PHY TO MULTIPHY ADAPTER CARD

| Pin Name                                                     | Туре  | Pin #                                                                                | Function                                                                                                               |

|--------------------------------------------------------------|-------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

| A[0]<br>A[1]<br>A[2]<br>A[3]<br>A[4]<br>A[5]<br>A[6]<br>A[7] | Input | C17<br>C18<br>C19<br>C20<br>C21<br>C22<br>C23<br>C24                                 | Address Bus. A[7:0] is an eight bit micro processor address bus that routes through the Micro Interface Selection mux. |

|                                                              | N/C   | A3,<br>A5,<br>A8-<br>A13,<br>A16-<br>A24,<br>C1,<br>C5,<br>C7,<br>C8,<br>C25-<br>C32 | Unconnected pins                                                                                                       |

# Table 6 Multi-PHY-X Interface

| Pin Name | Туре   | Pin# | Function                                                                                                                                                                                                                                                                                                                                     |

|----------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTFCLK   | Output | A1   | Multi-PHY-X FIFO Clock. XTFCLK synchronizes data transfer transactions to the Multi-PHY-X Interface. Clock rates up to 52 MHz are supported. The Multi-PHY-X Interface samples XTWRENB[3:0], XTSOC, XTXPRTY[1:0], XTDAT[15:0] and XRRDENB[3:0] on the rising edge of XTFCLK. XTFCLK originates from the SCI-PHY EVMB #1 Interface connector. |

ISSUE 1

| XTSOC                                                                                                                                                           | Output | A3                                                                                               | Multi-PHY-X Transmit Start Of Cell. XTSOC marks the start of cell on the XTDAT bus. XTSOC asserts high on the rising edge of XTFCLK when the first word of the data structure is present on the XTDAT bus. XTSOC originates from the SCI-PHY EVMB #1 Interface connector.                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XTXPRTY[0]<br>XTXPRTY[1]                                                                                                                                        | Output | C1<br>C3                                                                                         | Multi-PHY-X Transmit Parity. XTXPRTY[1:0] indicates the parity of the XTDAT[15:0] bus. The Multi-PHY-X Interface samples XTXPRTY[1:0] on the rising edge of XTFCLK. XTXPRTY[1] is the parity calculation over the XTDAT[15:8] bus. XTXPRTY[0] is the parity calculation over the XTDAT[7:0] bus. XTXPRTY[1:0] originates from the SCI-PHY EVMB #1 Interface connector.                              |

| XTDAT[0] XTDAT[1] XTDAT[2] XTDAT[3] XTDAT[4] XTDAT[5] XTDAT[6] XTDAT[6] XTDAT[8] XTDAT[8] XTDAT[10] XTDAT[10] XTDAT[11] XTDAT[12] XTDAT[13] XTDAT[14] XTDAT[15] | Output | A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>C11<br>C10<br>C9<br>C8<br>C7<br>C6<br>C5<br>C4 | Multi-PHY-X Transmit Data. XTDAT[15:0] transfers data to the corresponding Multi-PHY-X Interface channel on the rising edge of XTFCLK when one of XTWRENB[3:0] is asserted. XTDAT[7:0] corresponds to the least significant byte of the data word while XTDAT[15:8] corresponds to the most significant byte of the data word. XTDAT[15:0] originates from the SCI-PHY EVMB #1 Interface connector. |

| XTCA[0]<br>XTCA[1]<br>XTCA[2]<br>XTCA[3]                                                                                                                        | Input  | B5<br>B4<br>B2<br>B1                                                                             | Multi-PHY-X Transmit Cell Available. XTCA[n] indicates when the nth channel of the Multi-PHY-X Interface can accept data. Four XTCA inputs are provided to support four channels and the Multi-PHY-X Interface updates XTCAn on the rising edge of XTFCLK. XTCA[3:0] routes to the SCI-PHY EVMB #1 Interface connector.                                                                             |

ISSUE 1

| XTWRENB[0]<br>XTWRENB[1]<br>XTWRENB[2]<br>XTWRENB[3]                         | Output | B11<br>B10<br>B8<br>B7                               | Multi-PHY-X Transmit Write Enable. The active low XTWRENB[n] initiates writes to the nth channel transmit FIFO of the Multi-PHY-X Interface. Data on XTDAT[15:0] is written into the nth channel transmit FIFO when the nth Multi-PHY-X Interface channel samples an asserted XTWRENB[n] on the rising edge of XTFCLK. No data is written into the transmit FIFO when the nth Multi-PHY-X Interface channel samples a negated XTWRENB[n] on the rising edge of XFCLK. XTWRENB[3:0] originates from the SCI-PHY EVMB #1 Interface connector. |

|------------------------------------------------------------------------------|--------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[0]<br>A[1]<br>A[2]<br>A[3]<br>A[4]<br>A[5]<br>A[6]<br>A[7]                 | Output | A13<br>A14<br>A15<br>A16<br>A17<br>A18<br>A19<br>A20 | Address Bus. A[7:0] is an eight bit micro processor address bus that originates from the Micro Interface Selection mux.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CSB[0]<br>CSB[1]<br>CSB[2]<br>CSB[3]<br>CSB[4]<br>CSB[5]<br>CSB[6]<br>CSB[6] | Output | C13<br>C14<br>C15<br>C16<br>C17<br>C18<br>C19<br>C20 | Chip Select. CSB[7:0] asserts low to enable reading from and writing to the micro interface of the Multi-PHY interface. CSB[7:0] originates from the Micro Interface Selection mux.                                                                                                                                                                                                                                                                                                                                                         |

| TXFP+<br>(TXFP[1])<br>TXFP-<br>(TXFP[0])                                     | Input  | B15<br>B16                                           | Transmit Frame Pulse. The differential transmit frame pulse inputs provide the SWAN Micro and Timing card an 8KHz feedback signal for external clock synchronization. TXFP+/- routes directly to the SWAN Micro Interface connector.                                                                                                                                                                                                                                                                                                        |

| RALM                                                                         | Input  | B18                                                  | Receive Alarm. Receive Alarm indicates a loss of signal (LOS) condition has occurred at the PHY channel selected to provide the TXFP+/- signals. RALM routes directly to the SWAN Micro Interface connector.                                                                                                                                                                                                                                                                                                                                |

ISSUE 1

|                                                                                                                                                                          | 1      | 1                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XRFCLK                                                                                                                                                                   | Output | A32                                                                                                          | Multi-PHY-X Receive FIFO Clock. XRFCLK synchronizes data transfer transactions to the Multi-PHY-X Receive Interface. Clock rates up to 52 MHz are supported. The Multi-PHY-X Interface updates XRCA[3:0], XRSOC, XRXPRTY[1:0], XRDAT[15:0] and XTCA[3:0] on the rising edge of XRFCLK.                                                                                           |

| XRSOC                                                                                                                                                                    | Input  | A30                                                                                                          | Multi-PHY-X Receive Start Of Cell. XRSOC marks the start of cell on the XRDAT bus. XRSOC asserts high on the rising edge of XRFCLK when the first word of the data structure is present on the XRDAT bus. XRSOC routes to the SCI-PHY EVMB #1 Interface connector.                                                                                                               |

| XRXPRTY[0]<br>XRXPRTY[1]                                                                                                                                                 | Input  | C32<br>C30                                                                                                   | Multi-PHY-X Receive Parity. XRXPRTY[1:0] indicates the parity of the XRDAT[15:0] bus. XRXPRTY[1] is the parity calculation over the XRDAT[15:8] bus. XRXPRTY[0] is the parity calculation over the XRDAT[7:0] bus. XRXPRTY[1:0] routes to the SCI-PHY EVMB #1 Interface connector.                                                                                               |

| XRDAT[0] XRDAT[1] XRDAT[2] XRDAT[3] XRDAT[4] XRDAT[5] XRDAT[6] XRDAT[6] XRDAT[7] XRDAT[8] XRDAT[9] XRDAT[10] XRDAT[11] XRDAT[11] XRDAT[12] XRDAT[13] XRDAT[14] XRDAT[15] | Input  | A29<br>A28<br>A27<br>A26<br>A25<br>A24<br>A23<br>A22<br>C29<br>C28<br>C27<br>C26<br>C25<br>C24<br>C23<br>C22 | Multi-PHY-X Receive Data. XRDAT[15:0] transfers data from the Multi-PHY-X Interface channel on the rising edge of XRFCLK when one of XRRDENB[3:0] is asserted. XRDAT[7:0] corresponds to the least significant byte of the data word while XRDAT[15:8] corresponds to the most significant byte of the data word. XRDAT[15:0] routes to the SCI-PHY EVMB #1 Interface connector. |

PMC-Sierra,Inc.

REFERENCE DESIGN PMC-970438

ISSUE 1

| XRCA[0]<br>XRCA[1]<br>XRCA[2]<br>XRCA[3]             | Input  | B32<br>B31<br>B29<br>B28                                                      | Multi-PHY-X Receive Cell Available. XRCA[n] indicates when the nth channel of the Multi-PHY-X Interface contains valid data. Four XRCA inputs are provided to support four Multi-PHY-X channels. The nth Multi-PHY-X Interface channel asserts XRCA[n] when data can be read from its receive FIFO. The nth Multi-PHY-X Interface channel negates XRCA[n] when its receive FIFO is empty. XRCA[3:0] routes to the SCI-PHY EVMB #1 Interface connector.                                                                                                                                              |

|------------------------------------------------------|--------|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| XRRDENB[0]<br>XRRDENB[1]<br>XRRDENB[2]<br>XRRDENB[3] | Output | B26<br>B25<br>B23<br>B22                                                      | Multi-PHY-X Receive Write Enable. The active low XRRDENB[n] initiates reads from the nth channel receive FIFO of the Multi-PHY-X Interface. Data is read from the nth Multi-PHY-X Interface channel receive FIFO and put on XRDAT[15:0] when the nth Multi-PHY-X Interface channel samples an asserted XRRDENB[n] on the rising edge of XRFCLK. No data is read from the nth Multi-PHY-X Interface channel receive FIFO when the nth Multi-PHY-X Interface channel samples a negated XRRDENB[n] on the rising edge of XRFCLK. XRRDENB[3:0] originates from the SCI-PHY EVMB #1 Interface connector. |

| GND                                                  | Power  | B3<br>B6<br>B9<br>B12<br>B13<br>B14<br>B17<br>B19<br>B21<br>B24<br>B27<br>B30 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

ISSUE 1

SCI-PHY TO MULTIPHY ADAPTER CARD

| PWR +5V | Power | A2  | +5V Power |

|---------|-------|-----|-----------|

|         |       | A12 |           |

|         |       | A21 |           |

|         |       | A31 |           |

|         |       | C2  |           |

|         |       | C12 |           |

|         |       | C21 |           |

|         |       | C31 |           |

# Table 7 Multi-PHY-Y Interface Connector

| Pin Name                 | Туре   | Pin#     | Function                                                                                                                                                                                                                                                                                                                                                               |

|--------------------------|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| YTFCLK                   | Output | A1       | Multi-PHY-Y FIFO Clock. YTFCLK synchronizes data transfer transactions to the Multi-PHY-Y Interface. Clock rates up to 52 MHz are supported. The Multi-PHY-Y Interface samples YTWRENB[3:0], YTSOC, YTXPRTY[1:0] YTDAT[15:0] and YRRDENB[3:0] on the rising edge of YTFCLK. YTFCLK originates from the SCI-PHY EVMB #2 Interface connector.                            |

| YTSOC                    | Output | A3       | Multi-PHY-Y Transmit Start Of Cell. YTSOC marks the start of cell on the YTDAT bus. YTSOC asserts high on the rising edge of YTFCLK when the first word of the data structure is present on the YTDAT bus. YTSOC originates from the SCI-PHY EVMB #2 Interface connector.                                                                                              |

| YTXPRTY[0]<br>YTXPRTY[1] | Output | C3<br>C1 | Multi-PHY-Y Transmit Parity. YTXPRTY[1:0] indicates the parity of the YTDAT[15:0] bus. The Multi-PHY-Y Interface samples YTXPRTY[1:0] on the rising edge of YTFCLK. YTXPRTY[1] is the parity calculation over the YTDAT[15:8] bus. YTXPRTY[0] is the parity calculation over the YTDAT[7:0] bus. YTXPRTY[1:0] originates from the SCI-PHY EVMB #2 Interface connector. |

ISSUE 1

| YTDAT[0] YTDAT[1] YTDAT[2] YTDAT[3] YTDAT[4] YTDAT[5] YTDAT[6] YTDAT[7] YTDAT[8] YTDAT[9] YTDAT[10] YTDAT[11] YTDAT[12] YTDAT[13] YTDAT[14] YTDAT[15] | Output | A11<br>A10<br>A9<br>A8<br>A7<br>A6<br>A5<br>A4<br>C11<br>C10<br>C9<br>C8<br>C7<br>C6<br>C5<br>C4 | Multi-PHY-Y Transmit Data. YTDAT[15:0] transfers data to the corresponding Multi-PHY-Y Interface channel on the rising edge of YTFCLK when one of YTWRENB[3:0] is asserted. YTDAT[7:0] corresponds to the least significant byte of the data word while YTDAT[15:8] corresponds to the most significant byte of the data word. YTDAT[15:0] originates from the SCI-PHY EVMB #2 Interface connector.                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| YTCA[0]<br>YTCA[1]<br>YTCA[2]<br>YTCA[3]                                                                                                              | Input  | B5<br>B4<br>B2<br>B1                                                                             | Multi-PHY-Y Transmit Cell Available. YTCA[n] indicates when the nth channel of the Multi-PHY-Y Interface can accept data. Four YTCA inputs are provided to support four channels and the Multi-PHY-Y Interface updates YTCAn on the rising edge of YTFCLK. YTCA[3:0] routes to the SCI-PHY EVMB #2 Interface connector.                                                                                                                                                                                                                      |

| YTWRENB[0]<br>YTWRENB[1]<br>YTWRENB[2]<br>YTWRENB[3]                                                                                                  | Output | B11<br>B10<br>B8<br>B7                                                                           | Multi-PHY-Y Transmit Write Enable. The active low YTWRENB[n] initiates writes to the nth channel transmit FIFO of the Multi-PHY-Y Interface. Data on YTDAT[15:0] is written into the nth channel transmit FIFO when the nth Multi-PHY-Y Interface channel samples an asserted YTWRENB[n] on the rising edge of YTFCLK. No data is written into the transmit FIFO when the nth Multi-PHY-Y Interface channel samples a negated YTWRENB[n] on the rising edge of YTFCLK. YTWRENB[3:0] originates from the SCI-PHY EVMB #2 Interface connector. |

ISSUE 1

| D[0] D[1] D[2] D[3] D[4] D[5] D[6] D[7]      | Output | A13<br>A14<br>A15<br>A16<br>A17<br>A18<br>A19<br>A20 | Data Bus. D[7:0] is an eight bit microprocessor data bus that routes through the Micro Interface Selection mux.                                                                                              |

|----------------------------------------------|--------|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTB                                         | Output | C13                                                  | Reset. RSTB is an active low hardware reset that routes through the Micro Interface Selection mux.                                                                                                           |

| INTB                                         | Input  | C14                                                  | Interrupt. INTB is an active low maskable hardware interrupt and routes through the Micro Interface Selection mux.                                                                                           |

| ALE                                          | Output | C15                                                  | Address Latch Enable. ALE is an active high address latch enable that routes through the Micro Interface Selection mux.                                                                                      |

| BSB                                          | Output | C16                                                  | Board Select. BSB is an active low board select that enables microprocessor access to the Multi-PHY Interface. BSB originates from the Micro Interface Selection mux.                                        |

| RDB                                          | Output | C18                                                  | Read Enable. RDB is an active low read enable that routes through the Micro Interface Selection mux.                                                                                                         |

| WRB                                          | Output | C20                                                  | Write Strobe. WRB is an active low write strobe that routes through the Micro Interface Selection mux.                                                                                                       |

| SRCLK+<br>(SRCLK[1])<br>SRCLK-<br>(SRCLK[0]) | Output | B14<br>B15                                           | System Reference Clock. SRCLK+/- is a jitter free 19.44MHz differential system reference clock for the PHY channels of the Multi-PHY Interface. SRCLK+/- originates from the SWAN Micro Interface connector. |

| RXFP+<br>RXFP-                               | Input  | B18<br>B19                                           | Receive Frame Pulse. RXFP+/- is a differential signal pair used for system synchronization feedback. RXFP+/- is synchronous to SRCLK+/- and connects directly to the SWAN Micro Interface.                   |

ISSUE 1

| YRFCLK                                                                                                                                                | Output | A32                                                                                                          | Multi-PHY-Y Receive FIFO Clock. YRFCLK synchronizes data transfer transactions to the Multi-PHY-Y Interface. Clock rates up to 52 MHz are supported. The Multi-PHY-Y Interface updates YRCA[3:0], YRSOC, YRXPRTY[1:0], YRDAT[15:0] and YTCA[3:0] on the rising edge of YRFCLK. YRFCLK originates from the SCI-PHY EVMB #2 Interface connector.                                   |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| YRSOC                                                                                                                                                 | Input  | A30                                                                                                          | Multi-PHY-Y Receive Start Of Cell. YRSOC marks the start of cell on the YRDAT bus. YRSOC asserts high on the rising edge of YRFCLK when the first word of the data structure is present on the YRDAT bus. YRSOC routes to the SCI-PHY EVMB #2 Interface connector.                                                                                                               |

| YRXPRTY[0]<br>YRXPRTY[1]                                                                                                                              | Input  | C32<br>C30                                                                                                   | Multi-PHY-Y Receive Parity. YRXPRTY[1:0] indicates the parity of the YRDAT[15:0] bus. YRXPRTY[1] is the parity calculation over the YRDAT[15:8] bus. YRXPRTY[0] is the parity calculation over the YRDAT[7:0] bus. YRXPRTY[1:0] routes to the SCI-PHY EVMB #2 Interface connector.                                                                                               |

| YRDAT[0] YRDAT[1] YRDAT[2] YRDAT[3] YRDAT[4] YRDAT[5] YRDAT[6] YRDAT[7] YRDAT[8] YRDAT[9] YRDAT[10] YRDAT[11] YRDAT[12] YRDAT[12] YRDAT[14] YRDAT[15] | Input  | A29<br>A28<br>A27<br>A26<br>A25<br>A24<br>A23<br>A22<br>C29<br>C28<br>C27<br>C26<br>C25<br>C24<br>C23<br>C22 | Multi-PHY-Y Receive Data. YRDAT[15:0] transfers data from the Multi-PHY-Y Interface channel on the rising edge of YRFCLK when one of YRRDENB[3:0] is asserted. YRDAT[7:0] corresponds to the least significant byte of the data word while YRDAT[15:8] corresponds to the most significant byte of the data word. YRDAT[15:0] routes to the SCI-PHY EVMB #2 Interface connector. |

ISSUE 1

| YRCA[0]<br>YRCA[1]<br>YRCA[2]<br>YRCA[3]             | Input  | B32<br>B31<br>B29<br>B28                                               | Multi-PHY-Y Receive Cell Available. YRCA[n] indicates when the nth channel of the Multi-PHY-Y Interface contains valid data. Four YRCA inputs are provided to support four Multi-PHY-Y channels. The nth Multi-PHY-Y Interface channel asserts YRCA[n] when data can be read from its receive FIFO. The nth Multi-PHY-Y Interface channel negates YRCA[n] when its receive FIFO is empty. YRCA[3:0] routes to the SCI-PHY EVMB #2 Interface connector.                                                                                                                                             |

|------------------------------------------------------|--------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| YRRDENB[0]<br>YRRDENB[1]<br>YRRDENB[2]<br>YRRDENB[3] | Output | B26<br>B25<br>B23<br>B22                                               | Multi-PHY-Y Receive Write Enable. The active low YRRDENB[n] initiates reads from the nth channel receive FIFO of the Multi-PHY-Y Interface. Data is read from the nth Multi-PHY-Y Interface channel receive FIFO and put on YRDAT[15:0] when the nth Multi-PHY-Y Interface channel samples an asserted YRRDENB[n] on the rising edge of YRFCLK. No data is read from the nth Multi-PHY-Y Interface channel receive FIFO when the nth Multi-PHY-Y Interface channel samples a negated YRRDENB[n] on the rising edge of YFCLK. YRRDENB[3:0] originates from the SCI-PHY EVMB #2 Interface connector. |

| GND                                                  | Power  | B3<br>B6<br>B9<br>B13<br>B16<br>B17<br>B20<br>B21<br>B24<br>B27<br>B30 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

RELEASED

PMC-Sierra,Inc.

APPS MULTIPHY ADAPTER

REFERENCE DESIGN PMC-970438

ISSUE 1

| PWR +5V | Power | A2  | +5V Power |

|---------|-------|-----|-----------|

|         |       | A12 |           |

|         |       | A21 |           |

|         |       | A31 |           |

|         |       | C2  |           |

|         |       | C12 |           |

|         |       | C21 |           |

|         |       | C31 |           |

SCI-PHY TO MULTIPHY ADAPTER CARD

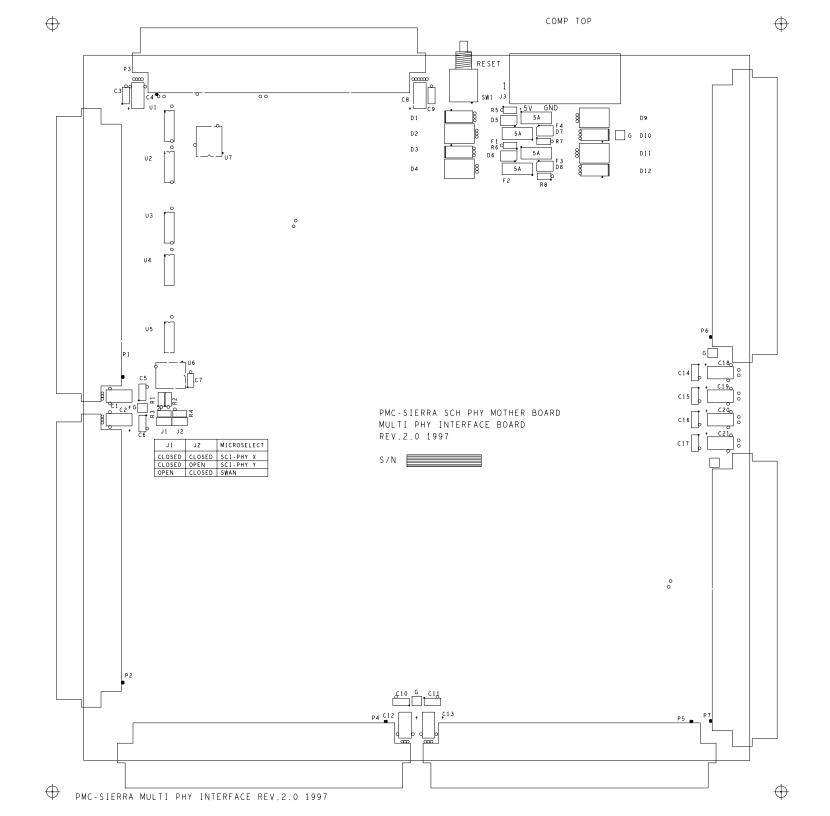

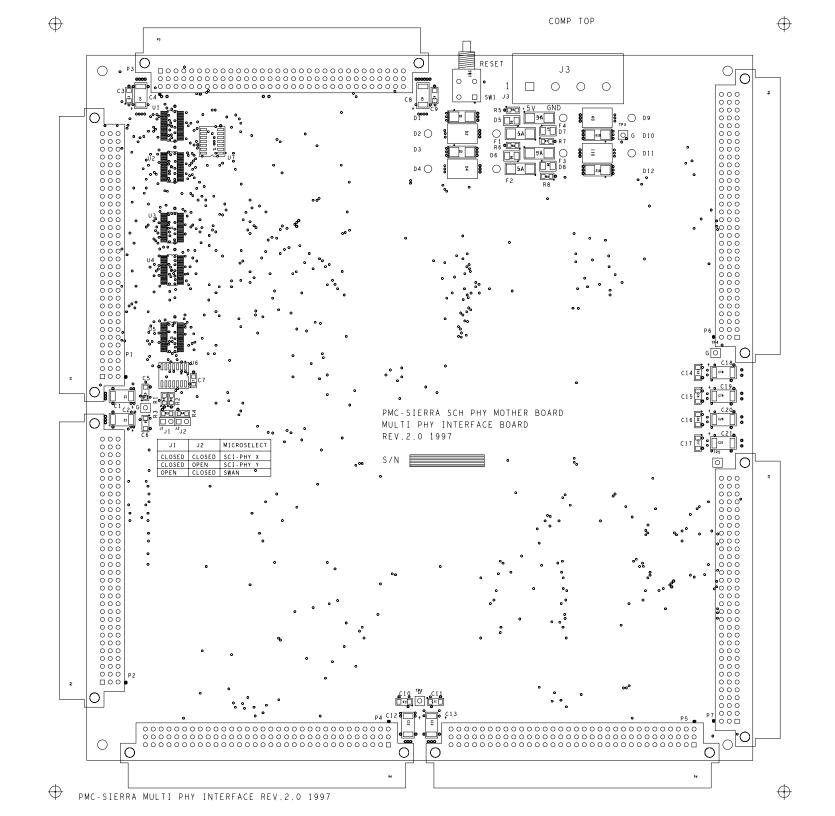

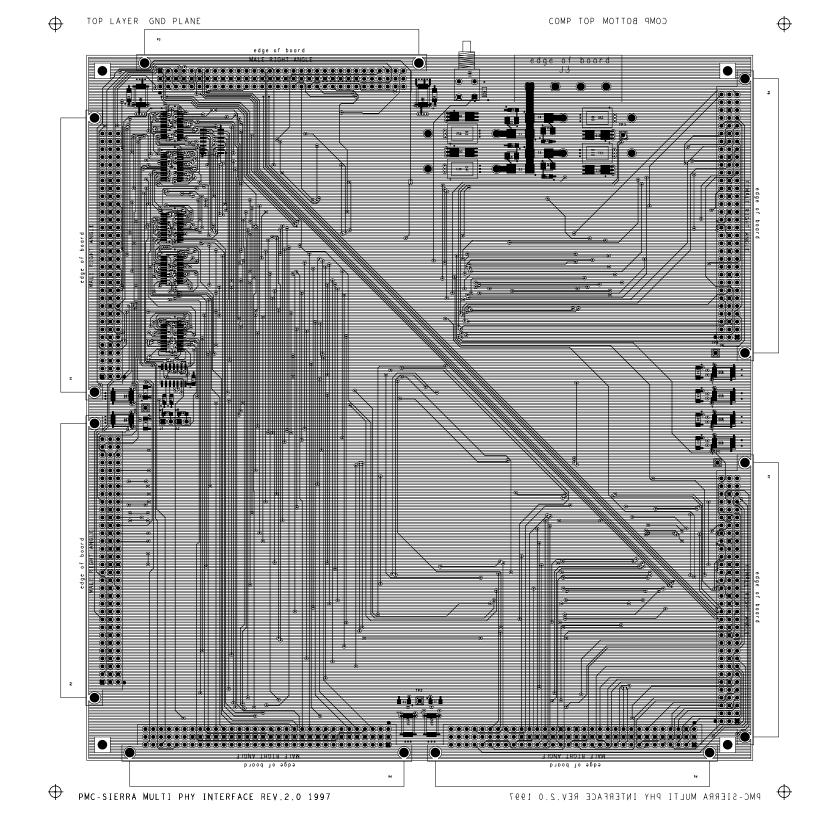

### 8 IMPLEMENTATION

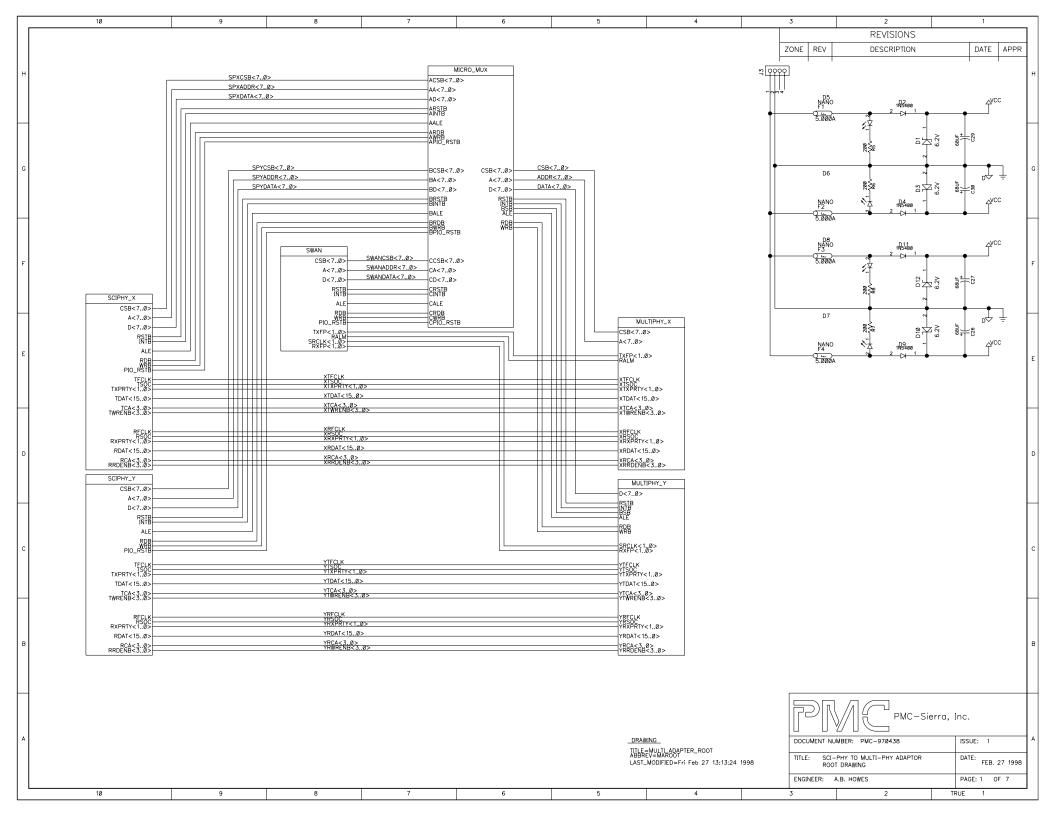

## 8.1 Root Drawing, Sheet 1

#### Function:

- 1. Provides an overview of the major functional blocks of the SCI-PHY to Multi-PHY Adapter board circuitry.

- 2. Illustrates the interconnecting data paths.

- 3. Shows power connection and protection.

## Implementation

This sheet interconnects the SCIPHY\_X, SCIPHY\_Y, SWAN, MICRO\_MUX, MULTIPHY\_X and MULTIPHY\_Y blocks. It also shows the power connections and related power circuitry.

+5V and GND power connections to the board are made via a screw-down type terminal block J3. The +5V routes through four identical networks that consist of a 5A fuse current protection, power indication LED with current limiting resistor, current feedback prevention diode, zener diode over-voltage protection and filtering capacitor.

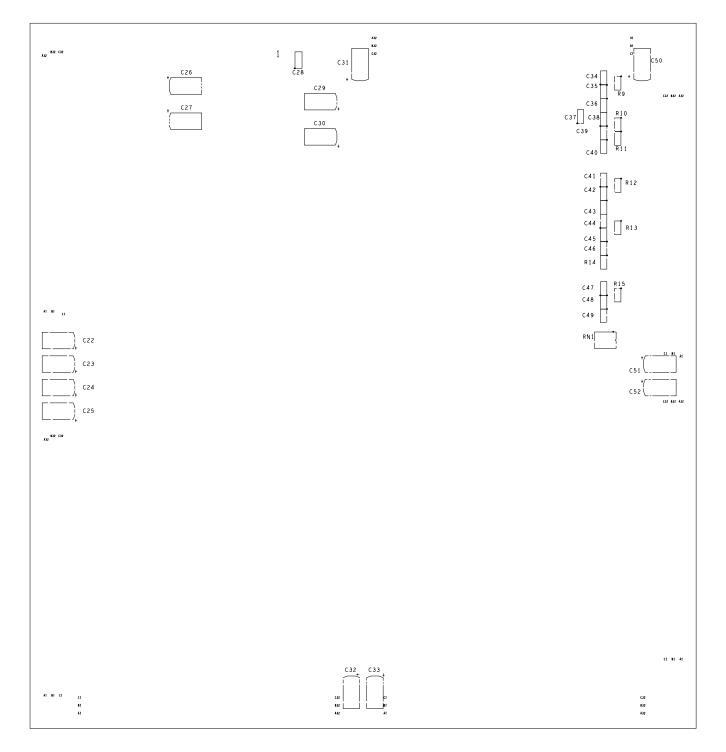

# 8.2 SCIPHY\_X, Sheet 2

#### Function:

1. Provides the electrical interface to the SCI-PHY #1 Evaluation Motherboard microprocessor interface and the SCI-PHY ATM cell interface.

#### Implementation:

This sheet shows two DIN-96 edge connectors. P1 provides the complete microprocessor interface which includes control signals, 8-bit data bus, 8-bit address bus and eight chip select signals. P2 provides the complete multi-PHY interface for the Multi-PHY-X Interface. This interface includes 16-bit data buses, parity, start-of-cell, cell available and read/write enable signals for the receive and transmit directions respectively. Power and ground connections are made in both connectors. Place the decoupling capacitors near to the connector for filtering VCC.

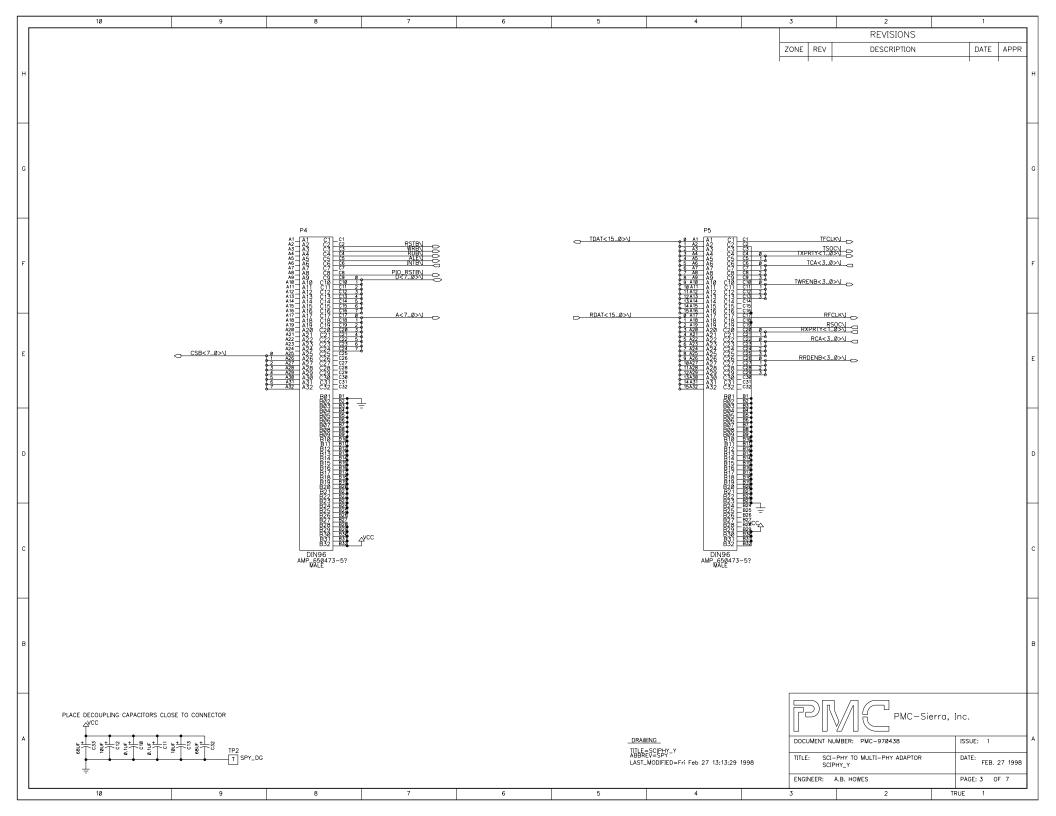

### 8.3 SCIPHY\_Y, Sheet 3

#### Function:

ISSUE 1

SCI-PHY TO MULTIPHY ADAPTER CARD

1. Provides the electrical interface to the SCI-PHY #2 Evaluation Motherboard microprocessor interface and the SCI-PHY ATM cell interface.

#### Implementation:

This sheet shows two DIN-96 edge connectors. P4 provides the complete microprocessor interface which includes control signals, 8-bit data bus, 8-bit address bus and eight chip select signals. P5 provides the complete multi-PHY interface for the Multi-PHY-Y Interface. This interface includes 16-bit data buses, parity, start-of-cell, cell available and read/write enable signals for the receive and transmit directions respectively. Power and ground connections are made in both connectors. Place the decoupling capacitors near to the connector for filtering VCC.

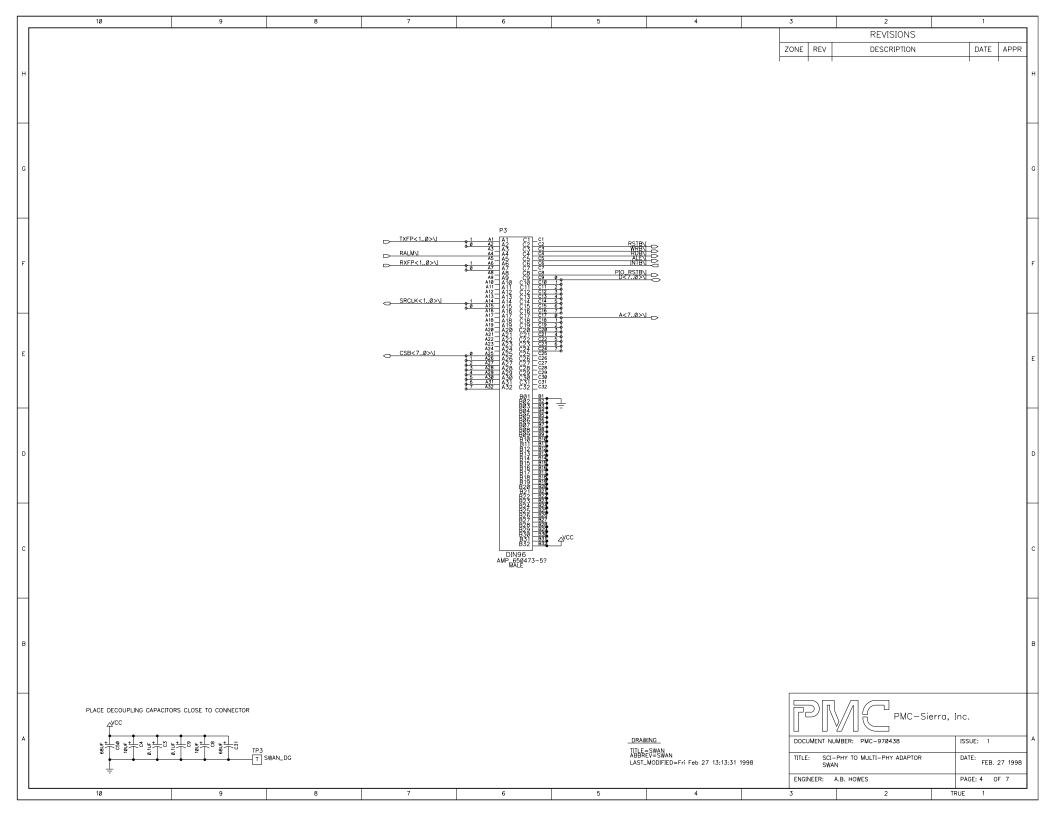

### 8.4 SWAN, Sheet 4

#### Function:

1. Provides the electrical interface to the SWAN Microprocessor and Reference Timing Card.

### Implementation:

This sheet shows one DIN-96 edge connector that provides a portion of the electrical connections to the SCI-PHY to Multi-PHY Adapter board. Connector P3 has the complete microprocessor interface which includes control signals, 8-bit data bus, 8-bit address bus and eight chip select signals. P3, also has the Transmit Frame Pulse (TXFP+/-), Receive Frame Pulse (RXFP+/-) and System Reference Clock (SRCLK+/) signals for the system reference clock card. Also, power and ground connections are made in connector P3. Place the decoupling capacitors near to the connector for filtering VCC.

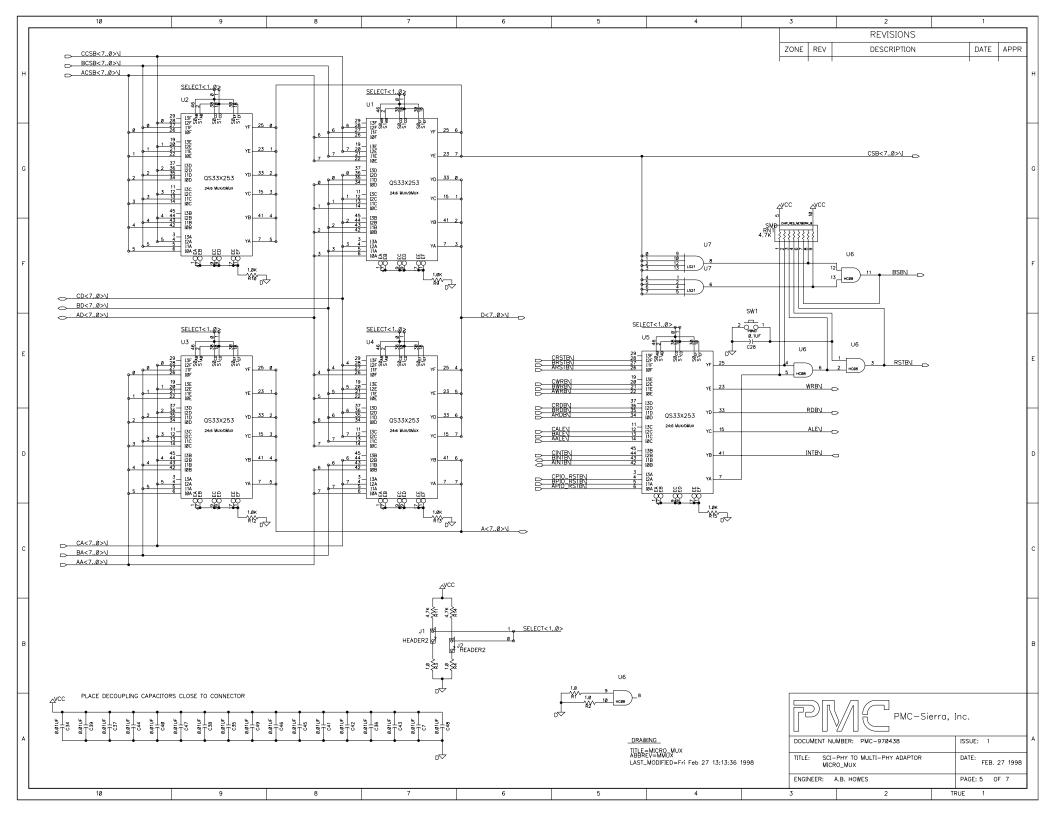

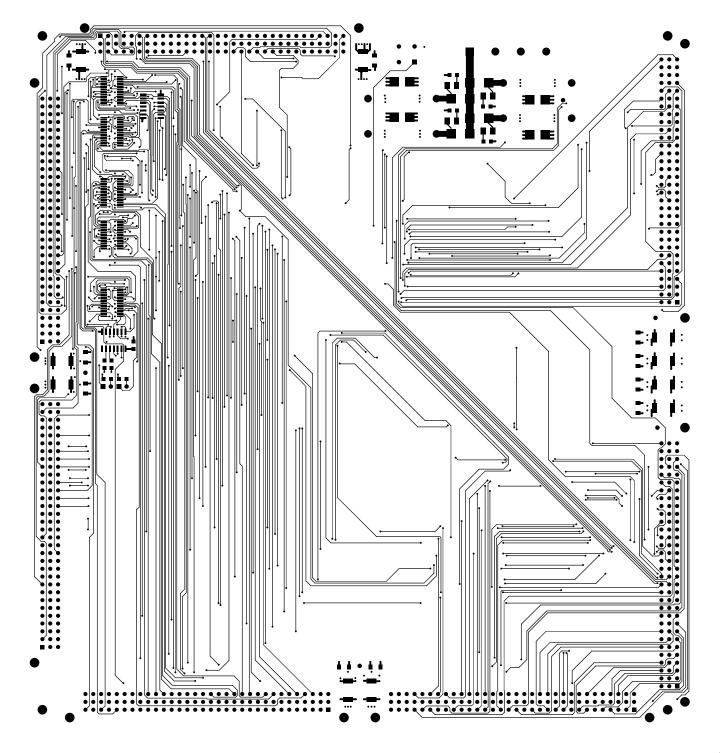

#### 8.5 MICRO\_MUX, Sheet 5

#### Function:

- Provides manual selection of the Multi-PHY Interface microprocessor control between either the SWAN microprocessor or the SCI-PHY EVMB #1 microprocessor.

- 2. Incorporates 3 sources of reset for the Multi-PHY Interface.

- Provides logic for the board select signal (BSB).

#### Implementation:

ISSUE 1

SCI-PHY TO MULTIPHY ADAPTER CARD

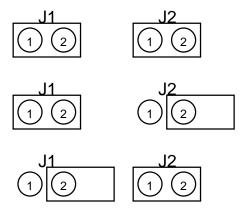

This sheet shows the multiplexing between the SCI-PHY #1, SCI-PHY #2 or the SWAN microprocessor signals U1, U2, U3 and U4 multiplex the microprocessor signals to the Multi-PHY Interface. Jumpers J1 and J2 correctly select which multiplex path is active. When the jumper is in place (closed), the SWAN microprocessor path is selected. When the jumper is removed (open), the SCI-PHY microprocessor path is selected.

Figure 2 Micro Interface Selection Jumper Positions

**Table 8** Micro Interface Selection Jumper Positions

| J1                | J2                | Description                                                                               |

|-------------------|-------------------|-------------------------------------------------------------------------------------------|

| Pin 1-2<br>Closed | Pin 1-2<br>Closed | Selects the SCI-PHY #1 Micro Interface to control the Multi-PHY Interface microprocessor. |

| Pin 1-2<br>Closed | Pin 1-2<br>Open   | Selects the SCI-PHY #2 Micro Interface to control the Multi-PHY Interface microprocessor. |

| Pin 1-2<br>Open   | Pin 1-2<br>Closed | Selects the SWAN Micro Interface to control the Multi-PHY Interface microprocessor.       |

An external hardware reset, an external software reset and a local hardware reset are the three sources for the Multi-PHY reset. The SCI-PHY #1, SCI-PHY #2 and the SWAN microprocessors provide the external reset signals dependent on the micro multiplexer selection. The normally open push button switch and capacitor C28 provide the local hardware reset. The two AND gates of U6 provide a logical OR function of these signals since they are active low.

4-input AND gates of U7 and the 2-input AND gate of U6 combine to assert BSB low when any of the CSB signals are asserted low.

SCI-PHY TO MULTIPHY ADAPTER CARD

The inputs of the unused gates of U6 are connected to ground (logic 0). Capacitors for decoupling power pins are also provided.

ISSUE 1

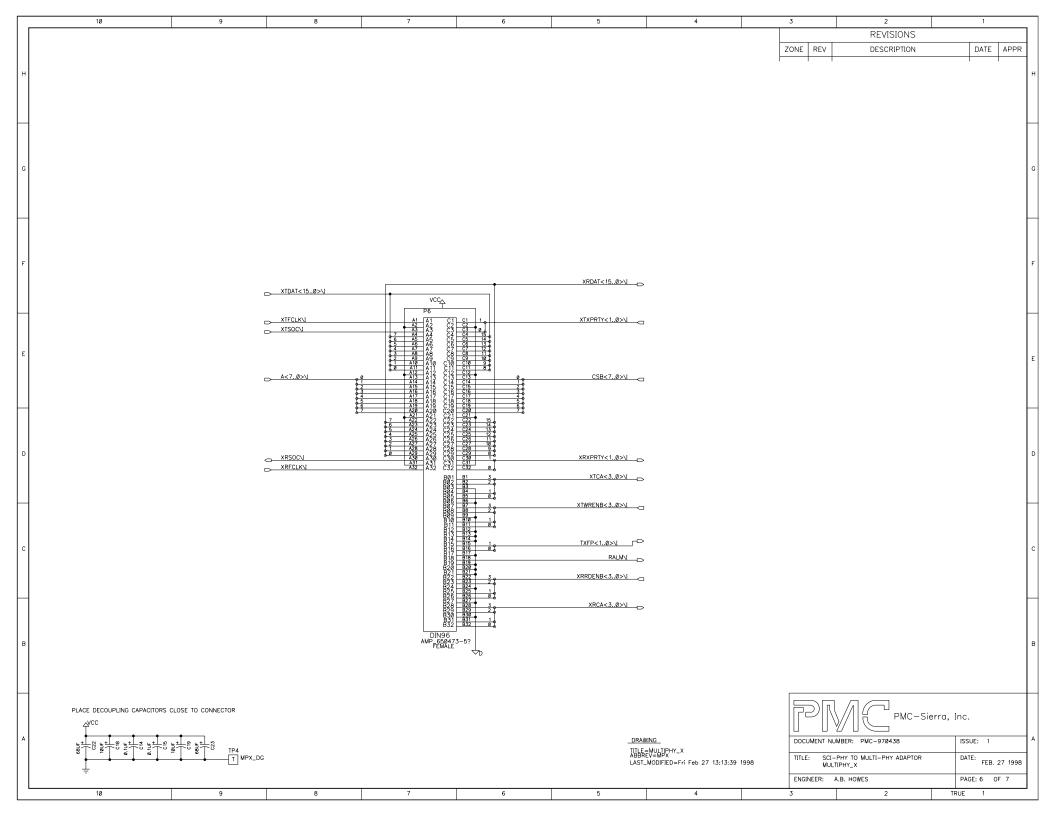

### 8.6 MULTIPHY \_X, Sheet 6

#### Function:

- Provides the electrical interface for the address bus of a microprocessor to Octal PLUS board.

- Provides the electrical interface for the Multi-PHY-X Interface of the Octal PLUS board.

- 3. Provides the external system reference clock feedback signal interface (TXFP+/-).

- 4. Provides VCC and GND connections to the Octal PLUS board.

### Implementation: