SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

# PM5342

# SPECTRA-155

# SUGGESTIONS FOR SPECTRA-155 PECL TERMINATIONS

## **APPLICATION NOTE**

#### **PREMINARY**

**ISSUE 1: SEPTEMBER 1997**

ISSUE 1

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

## **CONTENTS**

| 1    | SPECTRA-155 TO PMD AND REFERENCE OSCILLATOR TERMINATIONS | . 1 |

|------|----------------------------------------------------------|-----|

| 2    | SPECTRA-155 TXD TO PMD                                   | . 2 |

| 3    | DIFFERENTIAL REFERENCE OSCILLATOR                        |     |

|      | TERMINATIONS                                             | 3   |

| 4    | SINGLE TTL/CMOS OSCILLATOR DRIVING                       |     |

|      | BOTH RRCLK AND TRCLK                                     | 4   |

| 5    | INTERNAL SELECTION OF TRANSMIT TIMING                    |     |

|      | REFERENCE CLOCK                                          | 5   |

| RFFF | RENCES                                                   | 5   |

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

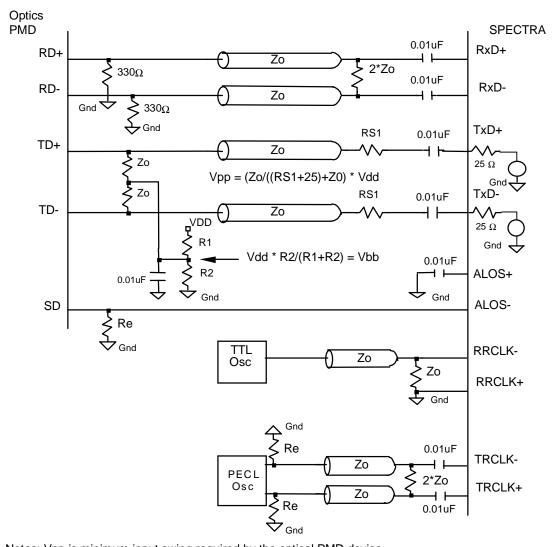

#### 1 SPECTRA-155 TO PMD AND REFERENCE OSCILLATOR TERMINATIONS

Notes: Vpp is minimum input swing required by the optical PMD device.

Vbb is the switching threshold of the PMD device (typically Vdd - 1.3 volts)

Vpp is Voh - Vol (typically 800 mVolts)

The value of Re is dependent on the signal trace characteristic impedence and the ECL or PECL supply voltage (-4.5 V,  $\pm$  5 V). Values in the range of 200-330 ohm are recommended

A single oscillator can be used to drive both RRCLK and TRCLK. Two interchangable options are shown for the supply of the TRCLK+/- and RRCLK+/- inputs.

APPLICATION NOTES

PMC-970938

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

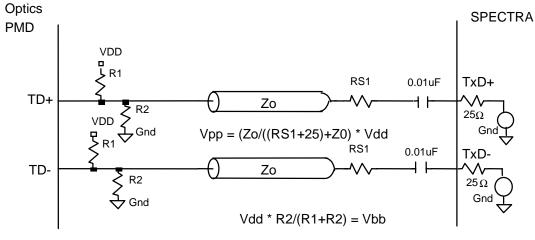

#### 2 SPECTRA-155 TXD TO PMD

The TxD outputs from the SPECTRA-155 may also use Thévenin termination resistors that provide the Vbb bias voltage rather than the resistor-divider shown above. While this circuit uses one less component (0.01 µF decoupling capacitor), it is more susceptible to common mode noise.

Zo= R1 \* R2/(R1+R2)

Notes: Vpp is minimum input swing required by the optical PMD device.

Vbb is the switching threshold of the PMD device (typically Vdd - 1.3 volts)

Vpp is Voh - Vol (typically 800 mVolts)

For Zo = 50 ohm; R1=67 ohm; R2 = 192.3 ohm

RS1=237 ohm

Resistor Tolerence ±5%.

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

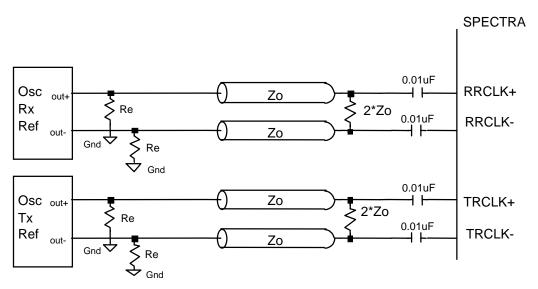

#### 3 DIFFERENTIAL REFERENCE OSCILLATOR TERMINATIONS

For optimum jitter performance on the transmit side and noise immunity on the receive side the reference clocks should be connected differentially as shown below.

The value of Re is dependent on the signal trace characteristic impedence and the ECL or PECL supply voltage (-4.5 V, + 5 V). Values in the range of 200-330 ohm are recommended

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

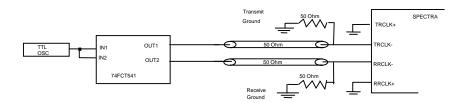

#### 4 SINGLE TTL/CMOS OSCILLATOR DRIVING BOTH RRCLK AND TRCLK

ISSUE 1

If a single TTL or CMOS oscillator is used to drive these inputs, the RRCLKand TRCLK- inputs can be used while RRCLK+ and TRCLK+ signals are connected to their respective grounds. The single clock signal must be properly terminated, however, it is not a good idea to connect the clock trace to either RRCLK- or TRCLK- and then run the trace to the other input and terminate at the far end. The transmit and receive planes should be isolated. therefore the potential differences between transmit and receive grounds will effect one of the reference clock inputs. For example, if the reference clock signal is run to the TRCLK input and then is terminated to the receive ground near the RRCLK input, the TRCLK input (which is referenced to the transmit ground) will require the clock swing to be large enough to accommodate the difference between grounds. Otherwise, the TRCLK input will be more sensitive to noise than the RRCLK input. A second problem may arise if the clock signal trace crosses the cuts in the ground plane (i.e. from transmit ground island to receive ground island). In that case the ground return current from the receive side cannot follow the signal trace back to the driver. Instead, it will seek an alternative path of least inductance. Consequently, this ground current will induce common-mode noise on signals nearby.

The solution is to run two separate reference clock signals and terminate them at each input<sup>1</sup>. The following diagram illustrates how to use a single TTL level oscillator to drive the RRCLK- & TRCLK- signals via a 74FCT541 buffer. The TRCLK+ and RRCLK+ signals are connected to their respective grounds.

The TTL oscillator should be placed as close to the buffer as possible as it is unterminated. The TTL oscillator is used to match the 74FCT541's TTL input level in order to avoid duty cycle distortion caused by differences in output levels and input switching thresholds.

<sup>&</sup>lt;sup>1</sup> A layout alternative could be to run a 50 ohm clock trace to the vicinity of the RRCLK- & TRCLK- inputs and then split into two 100 ohm traces. Each one of these two traces could then be connected to the RRCLK- or TRCLK- input and each terminated with 100 ohm to the receive or transmit analog ground respectively. However, this is not recommended because the resulting width of a 100 Ohm trace is very narrow (less than 3 mil). This width will be difficult for board manufacturers to fabricate accurately and reliably. Inaccuracy in the trace impedance will cause the signals to be improperly terminated.

ISSUE 1

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

#### 5 INTERNAL SELECTION OF TRANSMITTIMING REFERENCE CLOCK

A final option is to provide a reference clock input as shown in option 3 or 4 above and to program the SPECTRA-155 such that the source of the transmit reference clock is from the receive RRCLK+/- inputs. In order to select the RRCLK+/- inputs as the master timing reference for the transmit circuitry, the LTE bit in register 00H must be set to binary 1 and RBYP input must be set to high.

#### **REFERENCES**

- 1) PMC-Sierra, Inc., PM5342 SONET/SDH PAYLOAD EXTRACTOR/ALIGNER (SPECTRA-155) Data Sheet, Issue 1, Jan. 1995.

- 2) Ott, Henry W., "Noise Reduction Techniques in Electronic Systems", Second Edition, John Wiley & Sons.

- 3) Montrose, Mark I., "Printed Circuit Board Design Techniques for EMC Compliance", IEEE Press, 1995.

- 4) Graham, Martin and Johnson, Howard W., "High-Speed Digital Design: A Handbook of Black Magic", PRT Prentice-Hall Inc, 1993.

ISSUE 1

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

## **NOTES**

PLRLIMINARY 6

ISSUE 1

SONET/SDH PAYLOAD EXTRACTOR/ALIGNER

#### **CONTACTING PMC-SIERRA, INC.**

PMC-Sierra, Inc. 105-8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000

Fax: (604) 415-6200

Document Information: <a href="mailto:document@pmc-sierra.com">document@pmc-sierra.com</a>

Corporate Information: <a href="mailto:info@pmc-sierra.com">info@pmc-sierra.com</a>

Application Information: <a href="mailto:apps@pmc-sierra.com">apps@pmc-sierra.com</a>

http://www.pmc-sierra.com

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

© 1997 PMC-Sierra, Inc.

PMC-970938 (R1) Issue date: Septrmber 1997