REFERENCE DESIGN PMC-1981070 PMC-Sierra, Inc.

ISSUE 2

PM5357 S/UNI-622-POS

S/UNI-622-POS REFERENCE DESIGN

PM5357

## S/UNI-622-POS

## SATURN USER NETWORK INTERFACE (622-POS)

# **REFERENCE DESIGN**

PROPRIETARY AND CONFIDENTIAL PRELIMINARY ISSUE 2: FEBRUARY 2000

REFERENCE DESIGN PMC-1981070 PMC-Sierra, Inc.

PM5357 S/UNI-622-POS

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

## PUBLIC REVISION HISTORY

| lssue<br>No.                                                               | Issue<br>Date | Details of Change                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                                          | January       | Rev 2 to Rev 3 schematic change:                                                                                                                                                                                                                                                                                                                                              |

|                                                                            | 2000          | Removed the analog 8KHz t o77.76MHz PLL. The reference designations on the Issue 3 schematics match those on the Rev 1 PCB. At this time, there are no plans to build a PCB to Issue 3 schematics.                                                                                                                                                                            |

| 1.5                                                                        | August        | Rev 1 to Rev 2 schematic change to support uP cPCI:                                                                                                                                                                                                                                                                                                                           |

| 2000<br>Remove<br>cPCI I/F<br>internal<br>for S/UN<br>3.3V filte<br>ATM/Pa |               | Removed WAN clocking, removed local uP in lieu of the cPCI I/F, analog 8KHz to 77.76MHz PLL was added for internal testing, replaced 5V to 3.3V Linear regulator filter for S/UNI-622-POS analog power pins with RC passive 3.3V filters, add programmable FPGA for drop side ATM/Packets. Rev 1 PCB was fabricated to Rev 2 schematics. Issue 1.5 document was never issued. |

| 1                                                                          | Nov 1998      | Document created with Rev 1 Schematics. No PCB made<br>to Rev 1 Schematics. Only a paper design. Document<br>posted on intranet.                                                                                                                                                                                                                                              |

PMC-Sierra, Inc.

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

## **CONTENTS**

| 1 | INTRODUCTION 1              |                                                 |  |  |

|---|-----------------------------|-------------------------------------------------|--|--|

| 2 | S/UNI-622-POS BLOCK DIAGRAM |                                                 |  |  |

| 3 | APPLICATIONS                |                                                 |  |  |

|   | 3.1                         | ATM DROP SIDE LOOP-BACK 4                       |  |  |

|   | 3.2                         | ATM TRANSPARENT                                 |  |  |

|   | 3.3                         | POS SOURCE AND RECEIVE PACKETS                  |  |  |

|   | 3.4                         | POS TRANSPARENT 6                               |  |  |

|   | 3.5                         | REFERENCE PCB WITH OTHER PMC-SIERRA ATM CHIPS 7 |  |  |

|   | 3.6                         | USING THE REFERENCE BOARD WITH PACKET SWITCH 8  |  |  |

| 4 | REFERENCES9                 |                                                 |  |  |

| 5 | SYST                        | SYSTEM FUNCTIONAL DESCRIPTION                   |  |  |

| 6 | FUNCTIONAL DESCRIPTION1     |                                                 |  |  |

|   | 6.1                         | BLOCK DIAGRAM11                                 |  |  |

|   | 6.2                         | S/UNI-622-POS11                                 |  |  |

|   | 6.3                         | MICROPROCESSOR INTERFACE 13                     |  |  |

|   | 6.4                         | EXTERNAL CONNECTORS 13                          |  |  |

|   | 6.5                         | UTOPIA AND POS-PHY DROP SIDE INTERFACE          |  |  |

| 7 | IMPLEMENTATION DESCRIPTION  |                                                 |  |  |

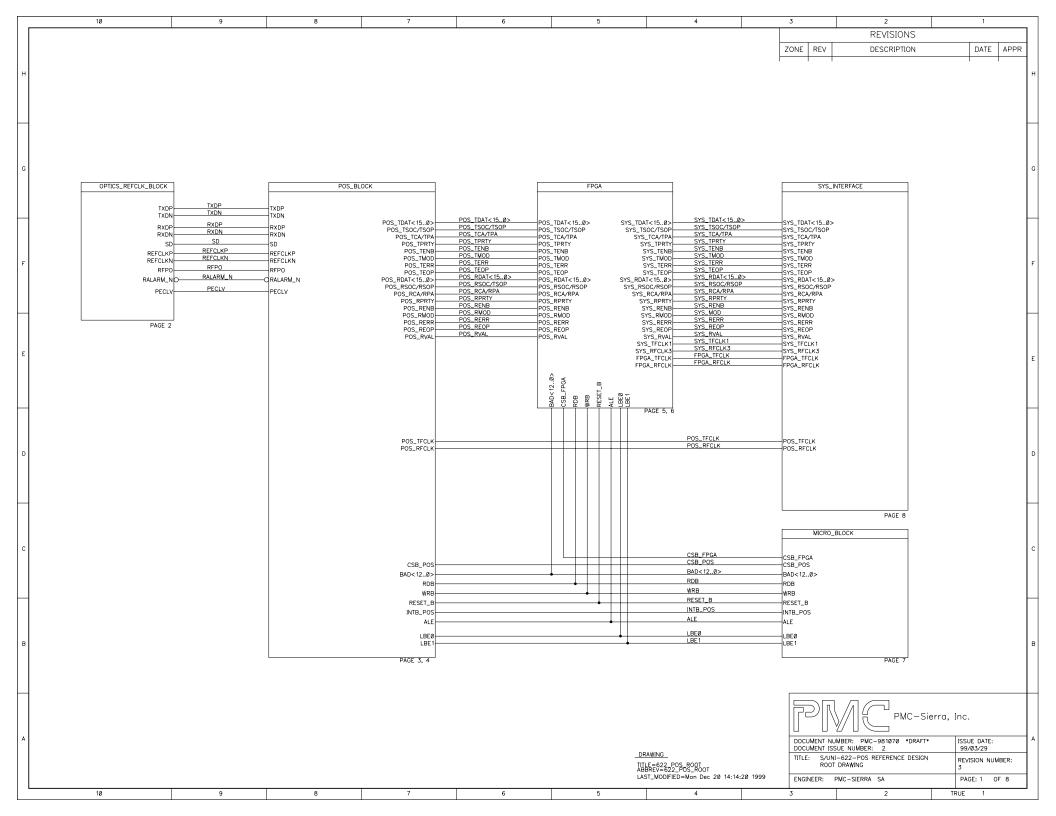

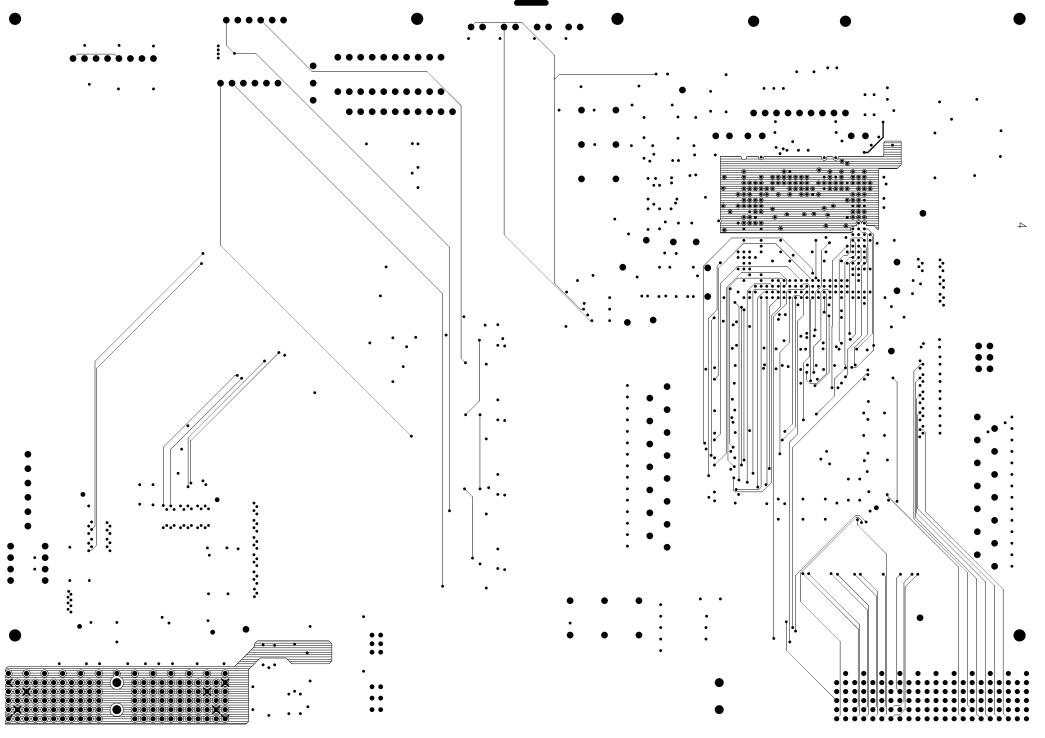

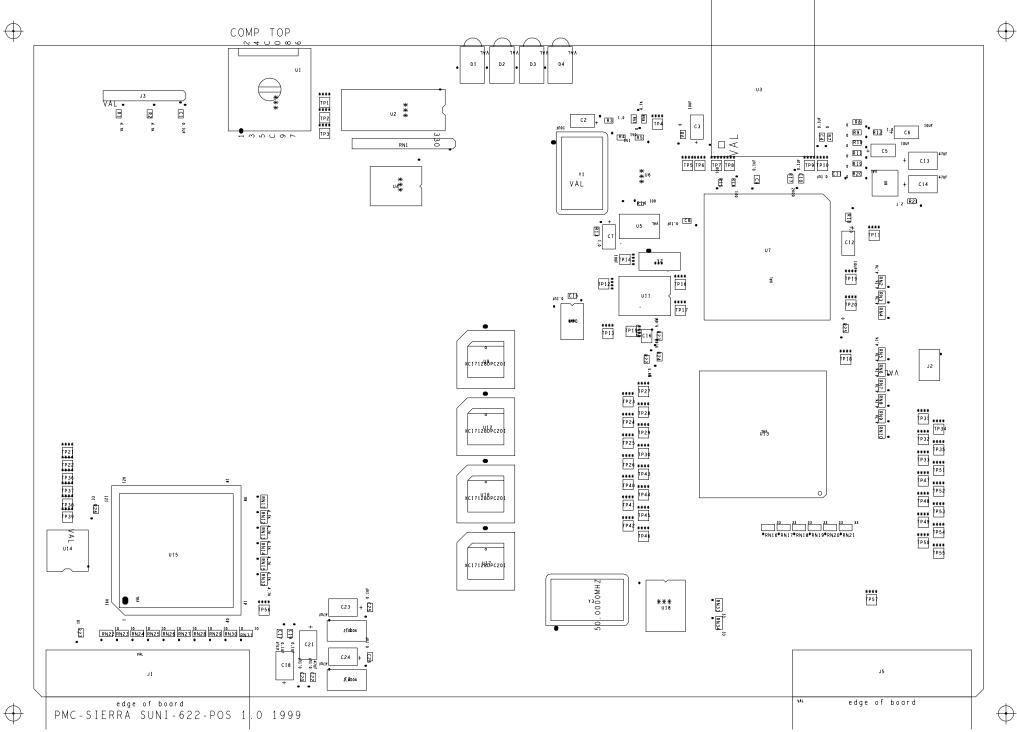

|   | 7.1                         | ROOT DRAWING, SHEET 1 15                        |  |  |

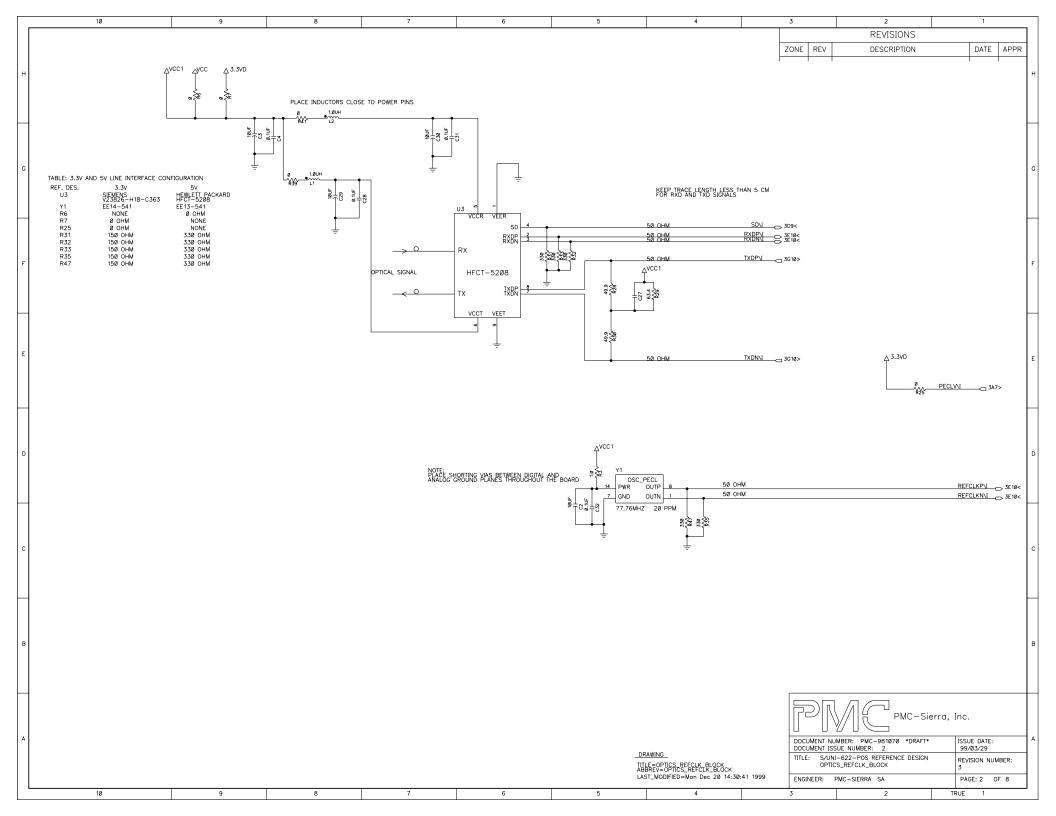

|   | 7.2                         | ODL AND 77.76 MHZ REFERENCE, SHEET 2 15         |  |  |

|   |                             | 7.2.1 622 MBIT/S OPTICAL INTERFACE 15           |  |  |

|   |                             | 7.2.2 77.7600 MHZ REFERENCE CLOCK CIRCUITRY 18  |  |  |

REFERENCE DESIGN PMC-1981070

8

9

| 070 |       | ISSUE 2                | S/UNI-622-POS REFERENCE DESIGN |

|-----|-------|------------------------|--------------------------------|

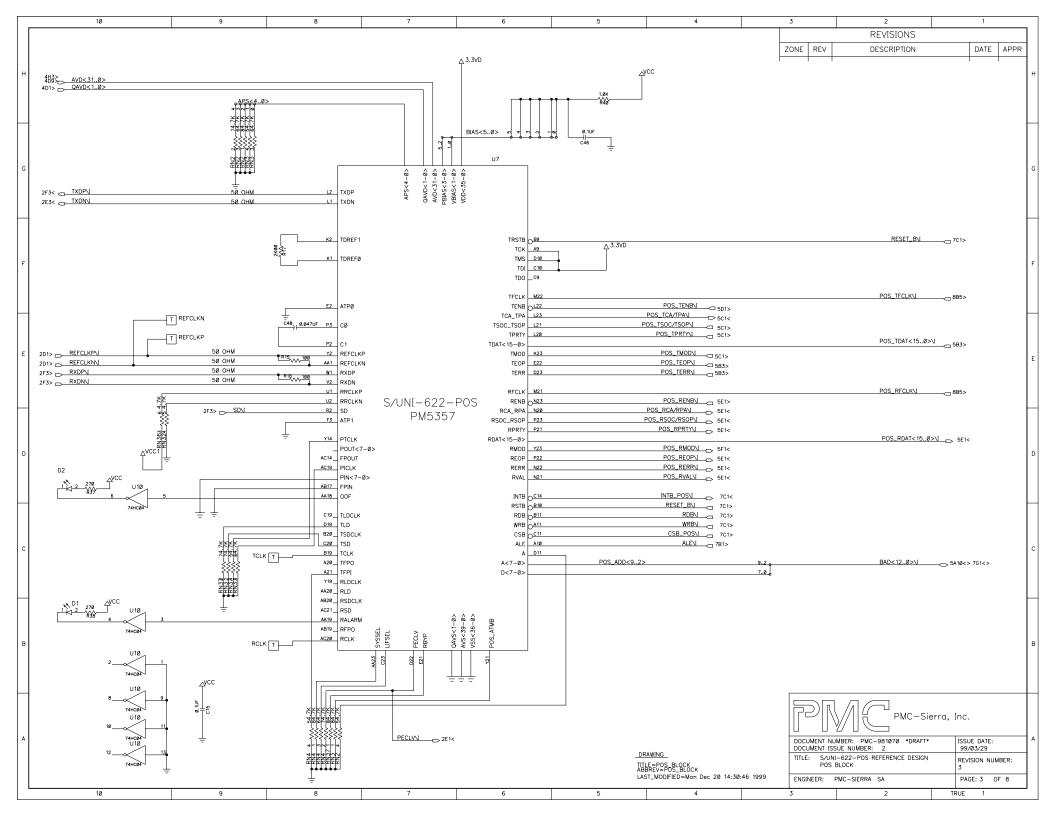

|     | 7.3   | POS_BLOCK, SHEET 3     |                                |

|     |       | 7.3.1 LOOP FILTER CAPA | ACITOR 24                      |

|     |       | 7.3.2 PULLUP AND PULL  | DOWN RESISTORS 24              |

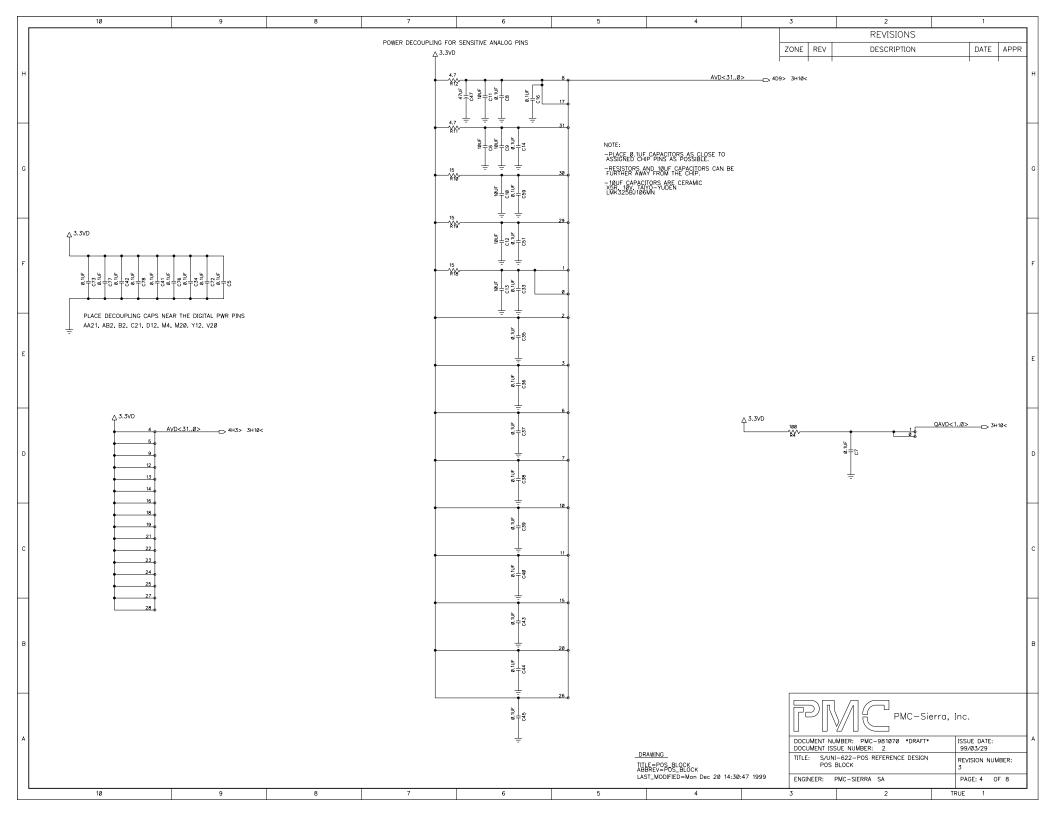

|     | 7.4   | POWER SUPPLY FILTER    | FOR THE PM5357 SHEET 4 25      |

|     |       | 7.4.1 PASSIVE RC LOW F | PASS POWER SUPPLY FILTER 25    |

|     |       | 7.4.2 LINEAR REGULATO  | OR FILTER METHOD 29            |

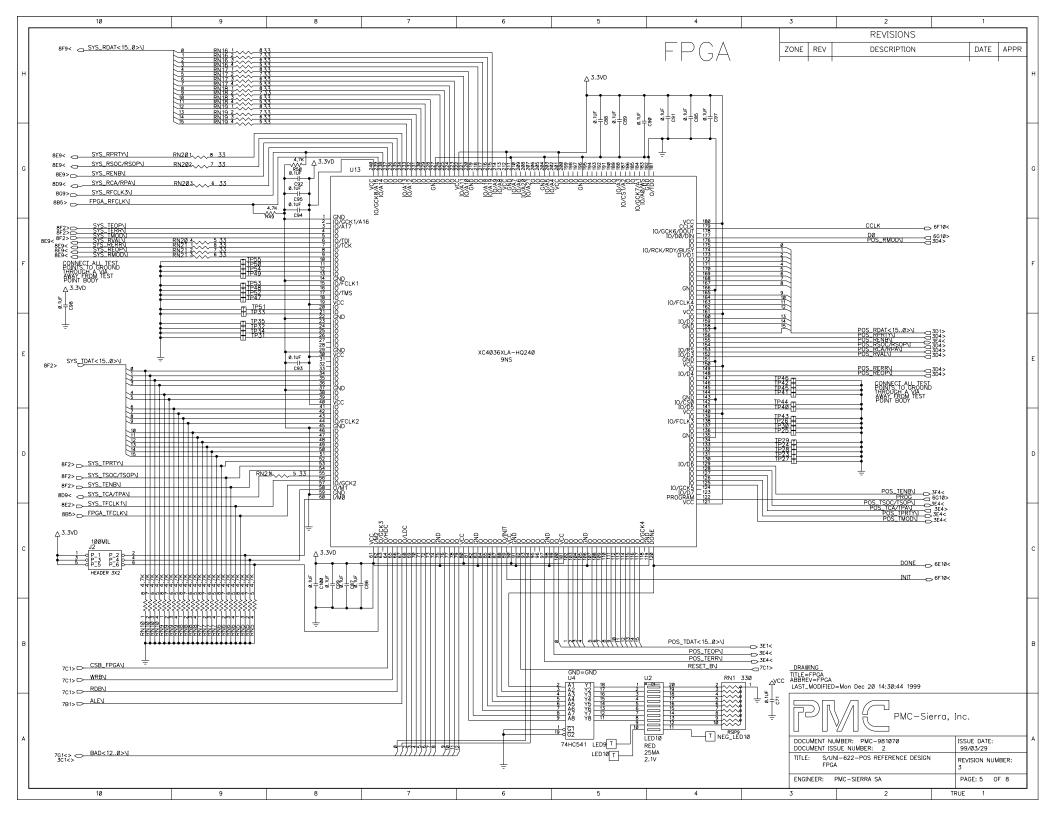

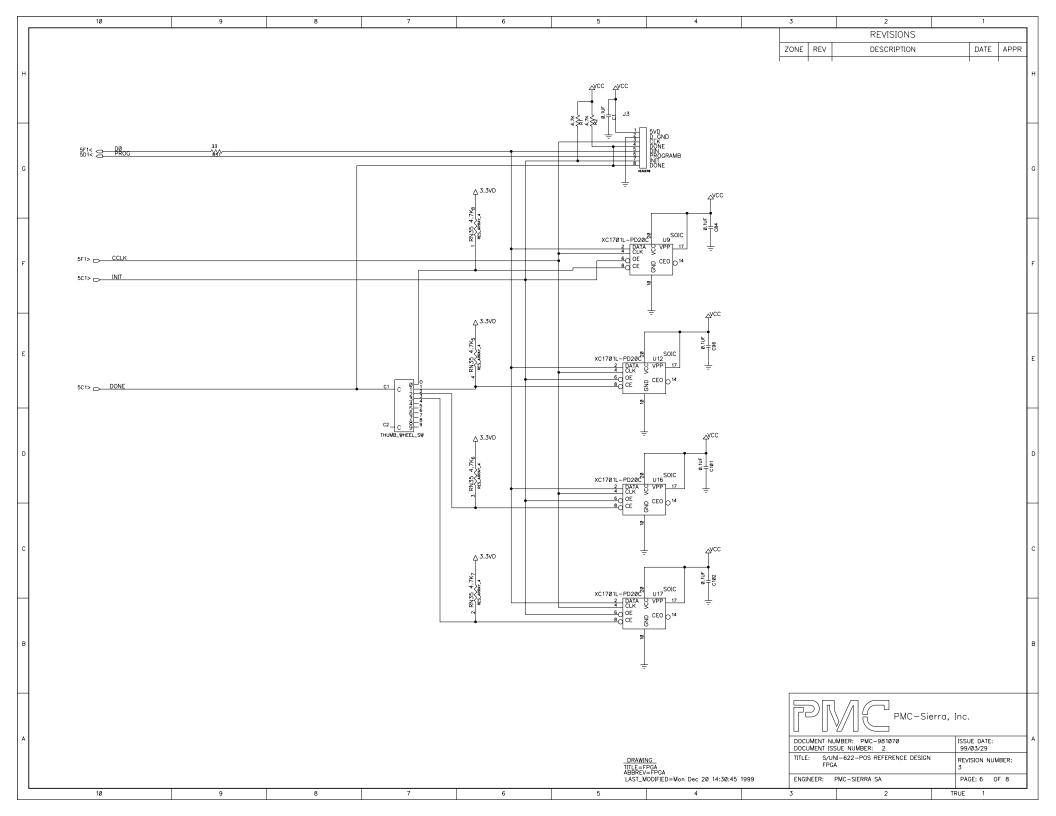

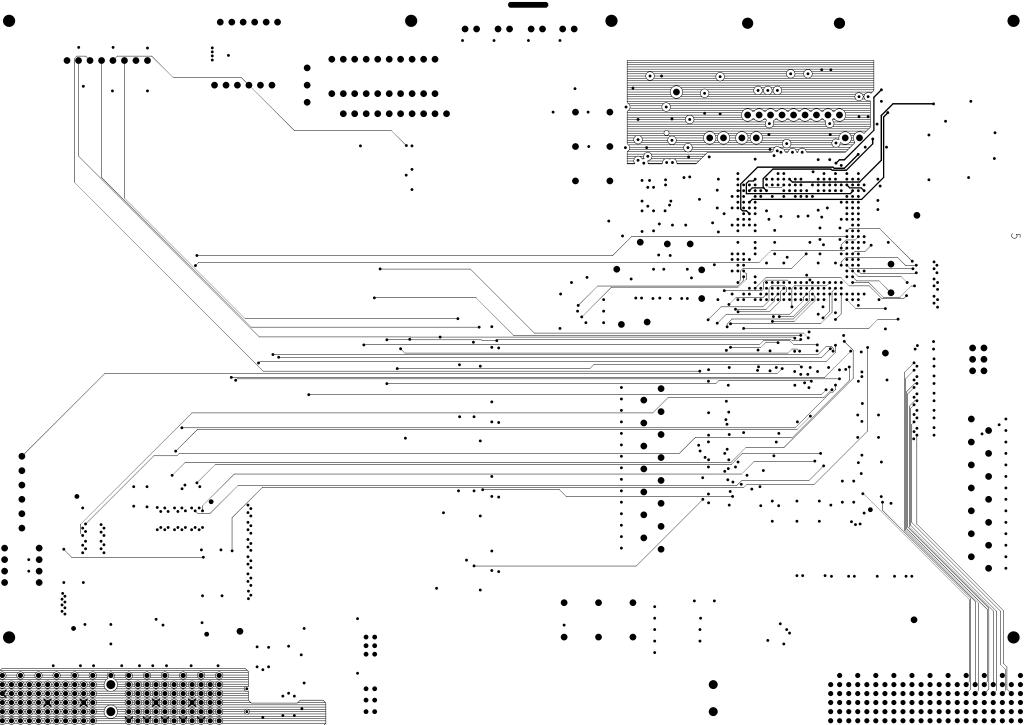

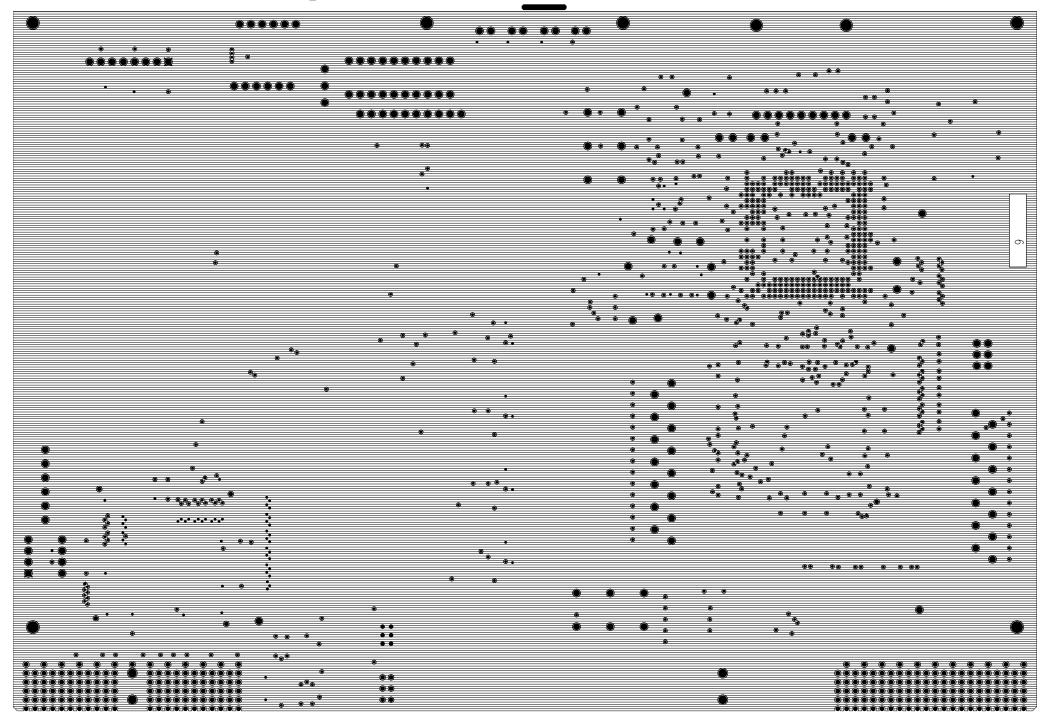

|     | 7.5   | FPGA, SHEET 5 AND 6    |                                |

|     | 7.6   | CPCI BUS INTERFACE SH  | IEET 7 31                      |

|     |       | 7.6.1 CPCI BACKPLANE   | CONNECTOR J1 32                |

|     |       | 7.6.2 PLX CPCI BRIDGE  | CHIP, PCI9050 32               |

|     |       | 7.6.3 SERIAL EEPROM    |                                |

|     |       | 7.6.4 POWER SUPPLY     |                                |

|     | 7.7   | SYS_INTERFACE, SHEET   | 8                              |

|     |       | 7.7.1 50MHZ UTOPIA OS  | CILLATOR                       |

|     |       | 7.7.2 J5 UTOPIA CONNE  | CTOR 34                        |

| 8   | SOFT  | WARE CONSIDERATIONS    |                                |

|     | 8.1   | PATH SIGNAL LABEL 'C2' |                                |

|     | 8.2   | SONET OR SDH CONFIGU   | JRING 38                       |

| 9   | PCB   | CONSIDERATIONS         |                                |

|     | 9.1   | PECL INTERFACE ISSUES  | 6                              |

|     | 9.2   | CLOCK AND DATA RECOV   | /ERY 42                        |

| 10  | APS ( | AUTOMATIC PROTECTION   | I SWITCHING) 43                |

|     | 10.1  | APS HARDWARE CONFIG    | SURATION: 43                   |

|     | 10.2  | APS SOFTWARE CONFIG    | URATION 44                     |

REFERENCE DESIGN PMC-1981070

| 81070 |      | ISSUE 2                          | S/UNI-622-POS REFERENCE DESIGN |

|-------|------|----------------------------------|--------------------------------|

| 11    | POW  | ER SUPPLY CONSIDERATIONS         |                                |

|       | 11.1 | POWER UP/DOWN CONSIDERATION      | IS 47                          |

|       | 11.2 | GROUNDING                        |                                |

|       | 11.3 | SYSTEM SIDE TRANSMISSION LINE    | TERMINATIONS 48                |

| 12    | TYPI | CAL JITTER MEASUREMENTS          |                                |

|       | 12.1 | INTRINSIC JITTER                 |                                |

|       | 12.2 | JITTER TOLERANCE                 |                                |

| 13    | OSCI | LLOSCOPE MEASUREMENTS            |                                |

|       | 13.1 | DIFFERENTIAL SCOPE PROBE         |                                |

|       | 13.2 | RFPO (RECEIVE FRAME PULSE OUT    | <u>-</u> ) 55                  |

|       | 13.3 | RXD+/- (RECEIVE DATA)            |                                |

|       | 13.4 | RCLK ( RECOVERED CLOCK)          |                                |

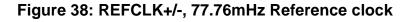

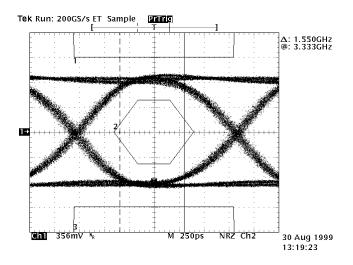

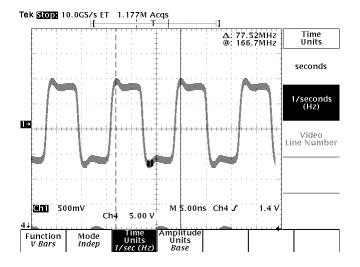

|       | 13.5 | REFCLK+/                         |                                |

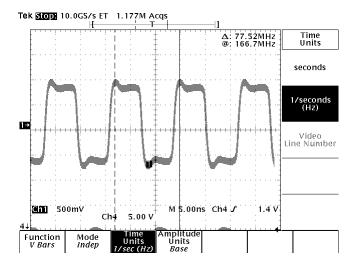

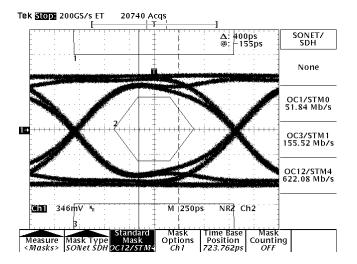

|       | 13.6 | RXD+/- EYE WITH OC-12 TEMPLATE   |                                |

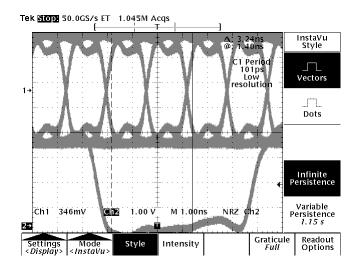

|       | 13.7 | TRANSMIT REFERENCE CLOCK, TCI    | _K 77.76MHZ 57                 |

|       | 13.8 | TXD+/- EYE WITH OC-12 TEMPLATE   |                                |

|       | 13.9 | DIFFERENTIAL TXD+/- WITH TCLK AS | S THE TRIGGER 59               |

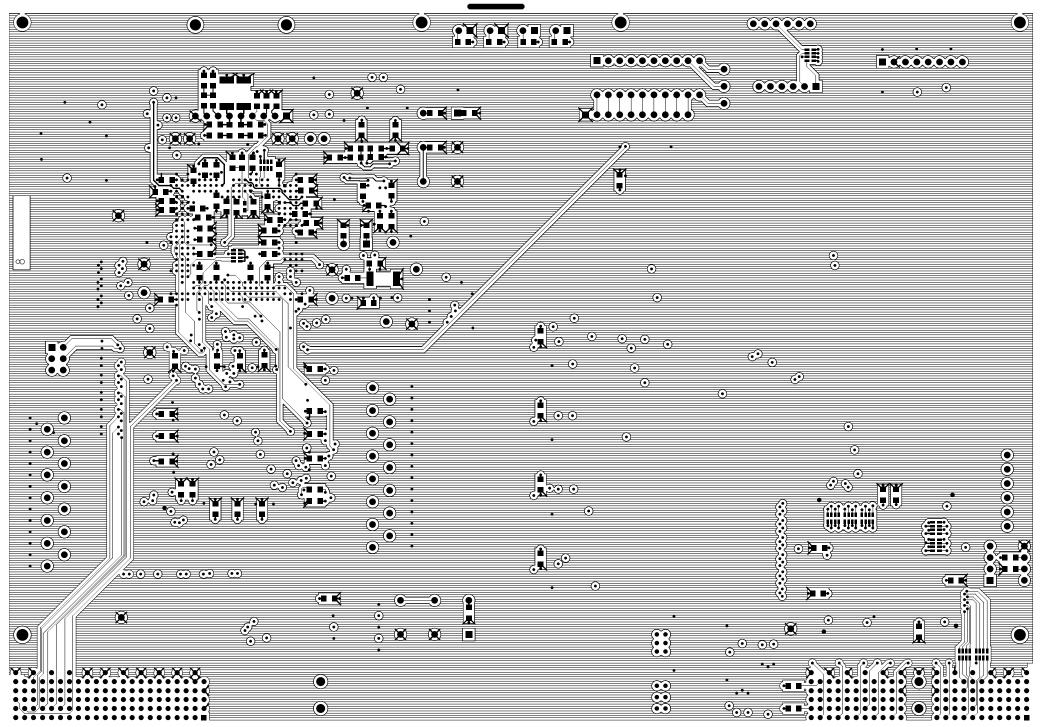

| 14    | SCHE | EMATICS REVISION 3               | 1                              |

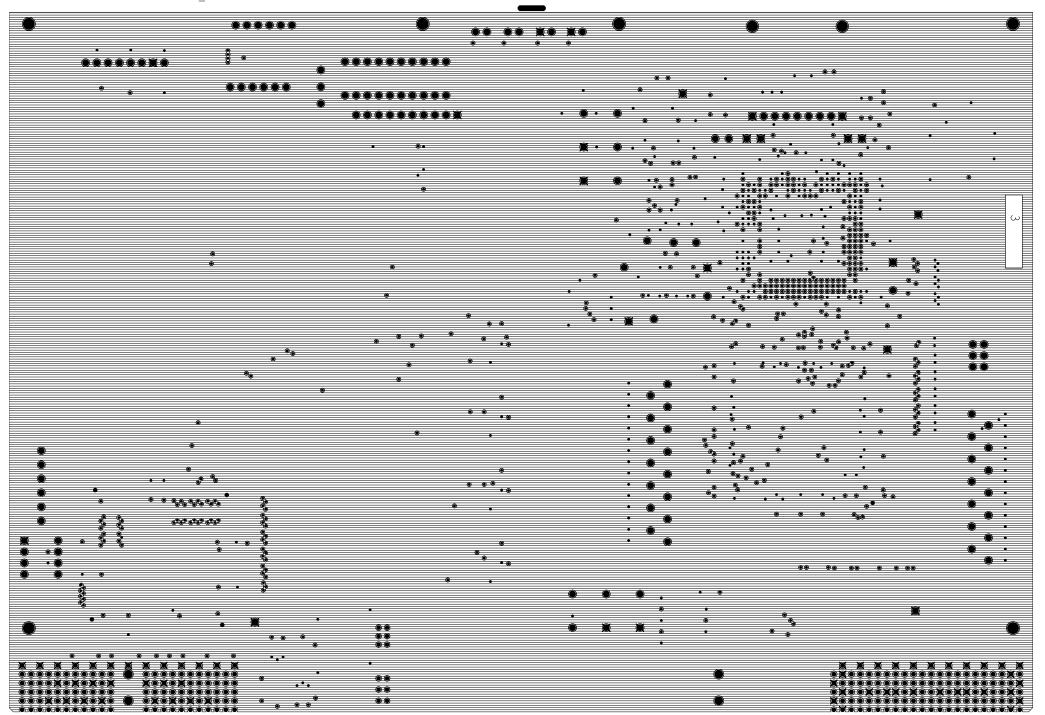

| 15    | PCB  | LAYOUT REVISION 1                | 1                              |

| 16    | REV  | 3 BOM (BILL OF MATERIALS)        | 1                              |

| 17    | FPGA | A ATM LOOPBACK SOURCE VHDL COE   | DE 1                           |

REFERENCE DESIGN PMC-1981070 PMC-Sierra, Inc.

PM5357 S/UNI-622-POS

ISSUE 2

## LIST OF FIGURES

| FIGURE 1: S/UNI-622POS CHIP 2                                     |

|-------------------------------------------------------------------|

| FIGURE 2: PICTURE OF S/UNI-622-POS REFERENCE DESIGN PCB           |

| FIGURE 3: S/UNI-622-POS BLOCK DIAGRAM                             |

| FIGURE 4: ATM DROP SIDE LOOP-BACK                                 |

| FIGURE 5: ATM TRANSPARENT 5                                       |

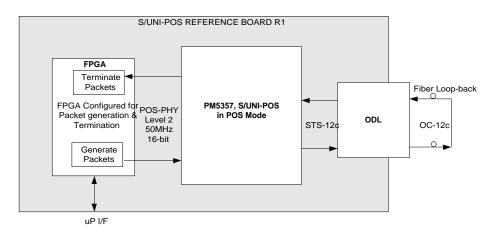

| FIGURE 6: PACKET GENERATION AND RECEIVING USING FPGA 6            |

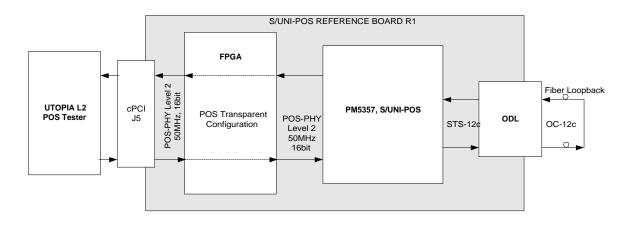

| FIGURE 7: POS TRANSPARENT TO BACKPLANE                            |

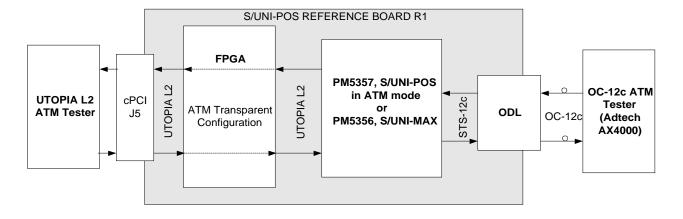

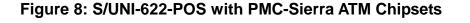

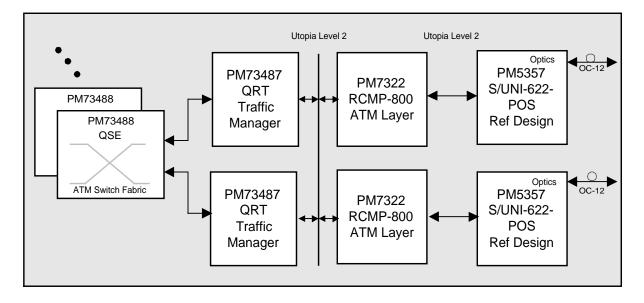

| FIGURE 8: S/UNI-622-POS WITH PMC-SIERRA ATM CHIPSETS 7            |

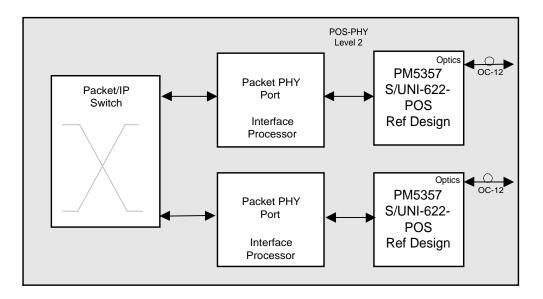

| FIGURE 9: S/UNI-622-POS REF DESIGN WITH POS LINK LAYER DEVICE 8   |

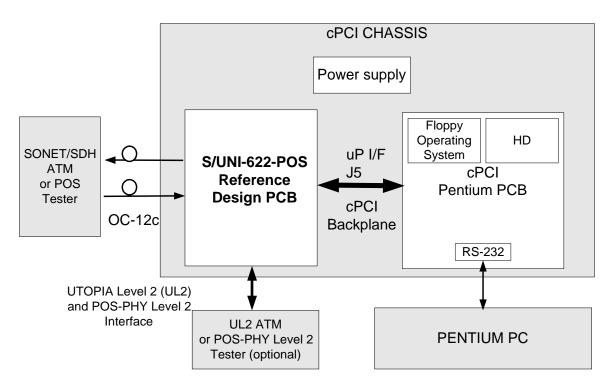

| FIGURE 10: SYSTEM LEVEL BLOCK DIAGRAM 10                          |

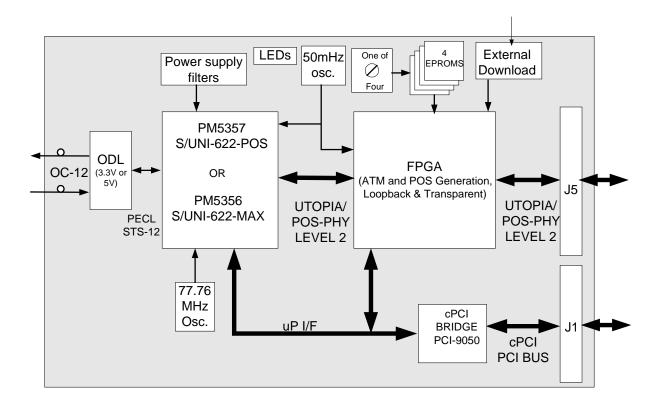

| FIGURE 11: REFERENCE DESIGN BLOCK DIAGRAM11                       |

| FIGURE 12: MICROPROCESSOR INTERFACE 13                            |

| FIGURE 13: ODL LINE INTERFACE TERMINATIONS 16                     |

| FIGURE 14: RXD+/- PCB LAYOUT 17                                   |

| FIGURE 15: 77.7600 MHZ REFERENCE OSCILLATOR 19                    |

| FIGURE 16: MIXING PECL 5V AND 3.3V ODL AND 77MHZ OSCILLATORS . 20 |

| FIGURE 17: PECL STS-12 VP-P 21                                    |

| FIGURE 18: PM5357 TXD+/- OPEN DRAIN CURRENT DRIVERS 22            |

| FIGURE 19: LOCATION OF TERMINATIONS OF TXD+/ 23                   |

| FIGURE 20: TANTALUM & X5R CERAMIC IMPEDANCE VS. FREQ 26           |

| FIGURE 21: PASSIVE RC ANALOG POWER SUPPLY FILTERING 27            |

| FIGURE 22: RC PASSIVE FILTER METHOD MECHANICAL DIAGRAM 28         |

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

| FIGURE 23: LINEAR REGULATOR POWER SUPPLY FILTER SCHEMATIC. 29 |

|---------------------------------------------------------------|

| FIGURE 24: LINEAR REGULATOR FILTER MECHANICAL LAYOUT          |

| FIGURE 25: EXTERNAL CLOCK AND DATA RECOVERY 42                |

| FIGURE 26: "1+1" APS USING PM5356 BUILT IN APS FUNCTION 46    |

| FIGURE 27: SYSTEM INTERFACE TERMINATIONS                      |

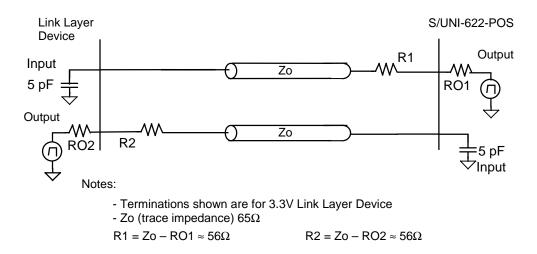

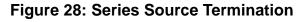

| FIGURE 28: SERIES SOURCE TERMINATION 50                       |

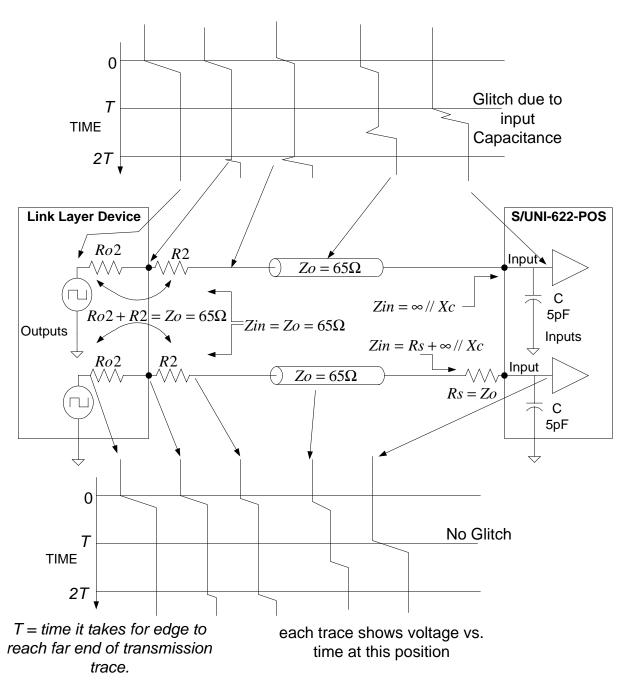

| FIGURE 29: JITTER TOLERANCE TEST SET-UP 52                    |

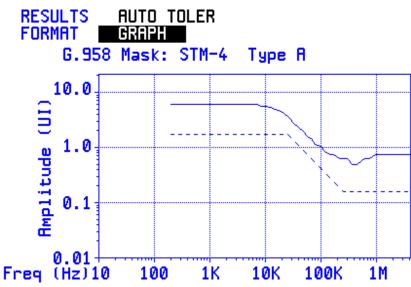

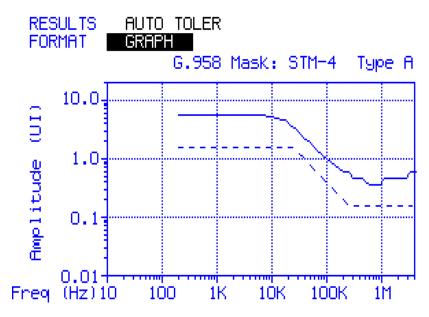

| FIGURE 30: JITTER TOLERANCE WITHOUT OPTICAL ATTENUATION 52    |

| FIGURE 31: JITTER TOLERANCE WITH OPTICAL ATTENUATION 53       |

| FIGURE 32: JITTER TOLERANCE WITH OPTICAL ATTENUATION 53       |

| FIGURE 33: DIFFERENTIAL SCOPE PROBE ANALYSIS                  |

| FIGURE 34: WHAT THE DIFFERENTIAL PROBE ACTUALLY SEES 54       |

| FIGURE 35: DIAGRAM RFPO (RECEIVE FRAME PULSE)                 |

| FIGURE 36: RXD+/- EYE (RECEIVE DATA) 55                       |

| FIGURE 37: RCLK (RECOVERED CLOCK) 56                          |

| FIGURE 38: REFCLK+/-, 77.76MHZ REFERENCE CLOCK                |

| FIGURE 39: RXD+/- EYE WITH OC-12 TEMPLATE                     |

| FIGURE 40: 77.7600 MHZ REFERENCE CLOCK 58                     |

| FIGURE 41: TXD+/- EYE WITH OC-12 TEMPLATE 58                  |

| FIGURE 42: DIFFERENTIAL TXD+/- WITH TCLK AS TRIGGER 59        |

REFERENCE DESIGN PMC-1981070 PMC-Sierra, Inc.

ISSUE 2

## LIST OF TABLES

| TABLE 1: PLX EPROM CONFIGURATION CODE                   | . 33 |

|---------------------------------------------------------|------|

| TABLE 2: J5 UTOPIA LEVEL 2 CONNECTOR                    | . 35 |

| TABLE 3: SONET VS. SDH CONFIGURATION                    | . 39 |

| TABLE 4: REFERENCE DESIGN PCB STACK UP                  | . 40 |

| TABLE 5: APS CONFIGURATION OF THE WORKING FRAMER        | . 43 |

| TABLE 6: APS HW CONFIGURATION OF THE PROTECTION FRAMER  | . 44 |

| TABLE 7: REGISTER SET-UP DURING NORMAL OPERATION        | . 45 |

| TABLE 8: REGISTER CONFIGURATION IN PROTECTION OPERATION | . 45 |

| TABLE 9: INTRINSIC JITTER CALIBRATION TESTS             | . 51 |

| TABLE 10: INTRINSIC JITTER TEST RESULTS WITH HP 717     | . 51 |

REFERENCE DESIGN PMC-1981070

**ISSUE 2**

S/UNI-622-POS REFERENCE DESIGN

## 1 INTRODUCTION

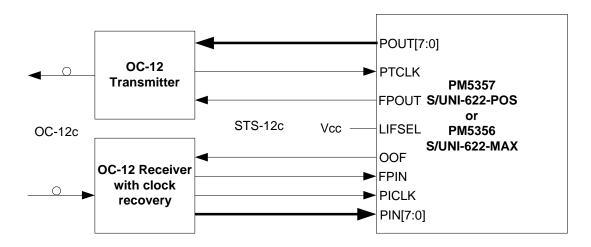

The PM5356 S/UNI-622-MAX performs ATM processing and the PM5357 S/UNI-622-POS performs both ATM processing and Packet Over SONET (POS). Both these devices have the same footprint and they are pin for pin compatible. Even though only reference to the PM5357 is made, this document relates to both the devices

The PM5357 S/UNI-622-POS standard product is a SATURN User Network Interface with SONET/SDH processing, ATM and Packet mapping functions at the STS-12c (STM-4-4c) 622.08 Mbit/s rate. This chip also features an integral CRU and CSU for clock/data recovery and generation. The S/UNI-622-POS is intended for use in equipment implementing Asynchronous Transfer Mode (ATM) User-Network Interface (UNI), ATM Network-Network Interfaces (NNI), and Packet Over SONET/SDH (POS) interfaces. The POS interface can be used to support several packet based protocols, including the Point-to-Point Protocol (PPP). The S/UNI-622-POS may find application at either end of switch-toswitch links or switch-to-terminal links, both in public network (WAN) and private network (LAN) situations.

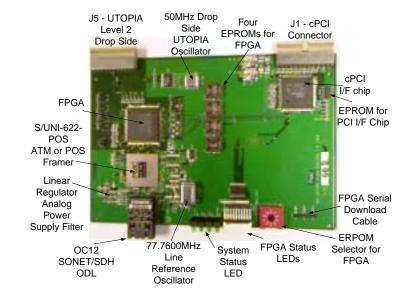

This S/UNI-622-POS reference design provides a physical interface implementation of a SONET/SDH line card for both ATM and POS applications. It provides one single-mode or multi-mode optical interface, 5V or 3.3 V, at OC-12c rate and a UTOPIA Level 2, 50MHz, 16-bit wide bus system side synchronous interface. The onboard programmable FPGA provides a simple means to manipulate ATM cells and POS packets.

The PM5357 S/UNI-622-POS features two drop side synchronous interfaces. For ATM applications, standard 50 MHz, 16 bit UTOPIA Level 2 and 100MHz, 8bit UTOPIA Level 3 interfaces are provided. For POS (Packet over SONET) designs, a SATURN compliant POS-PHY Level 2 and Level 3 interface is used. More on this interface is explained later in this document.

This POS Reference board implements a subset of the full capabilities of the S/UNI-622-POS and this board does not support APS.

Both the PM5357 and the PM5356 are packaged in a 304 pin Super Ball Grid Array (SBGA) as shown below.

For detailed information on these devices please refer to their respective data sheets. The terms cPCI and CompactPCI<sup>TM</sup> will be used interchangeably.

REFERENCE DESIGN PMC-1981070 PMC-Sierra, Inc.

PM5357 S/UNI-622-POS

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

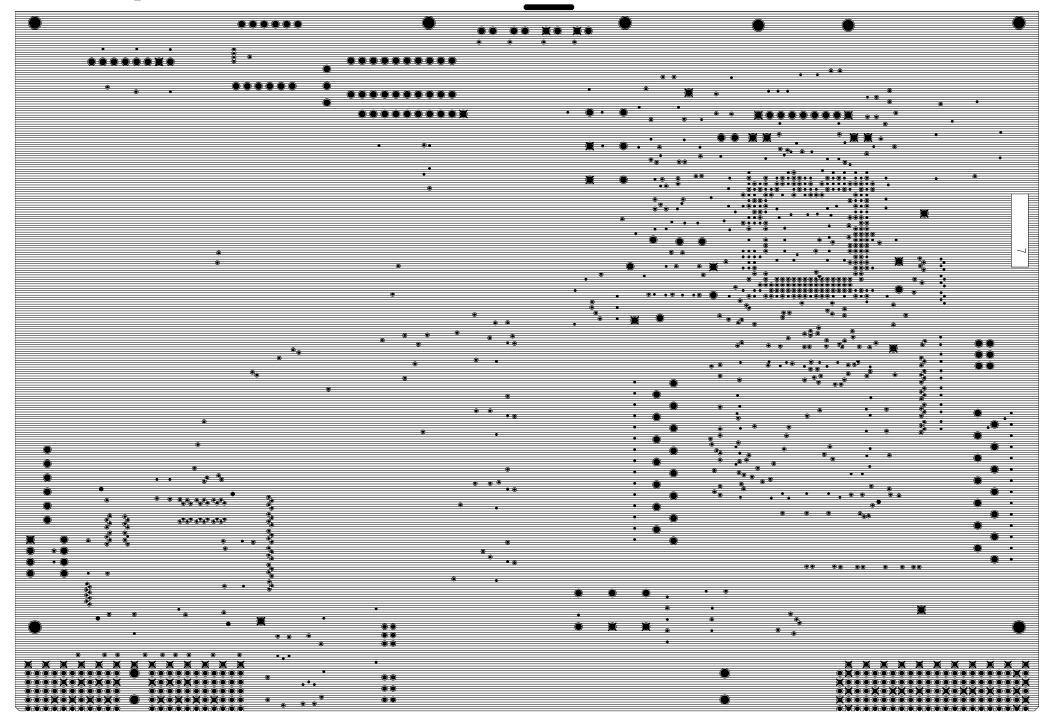

#### Figure 1: S/UNI-622POS Chip

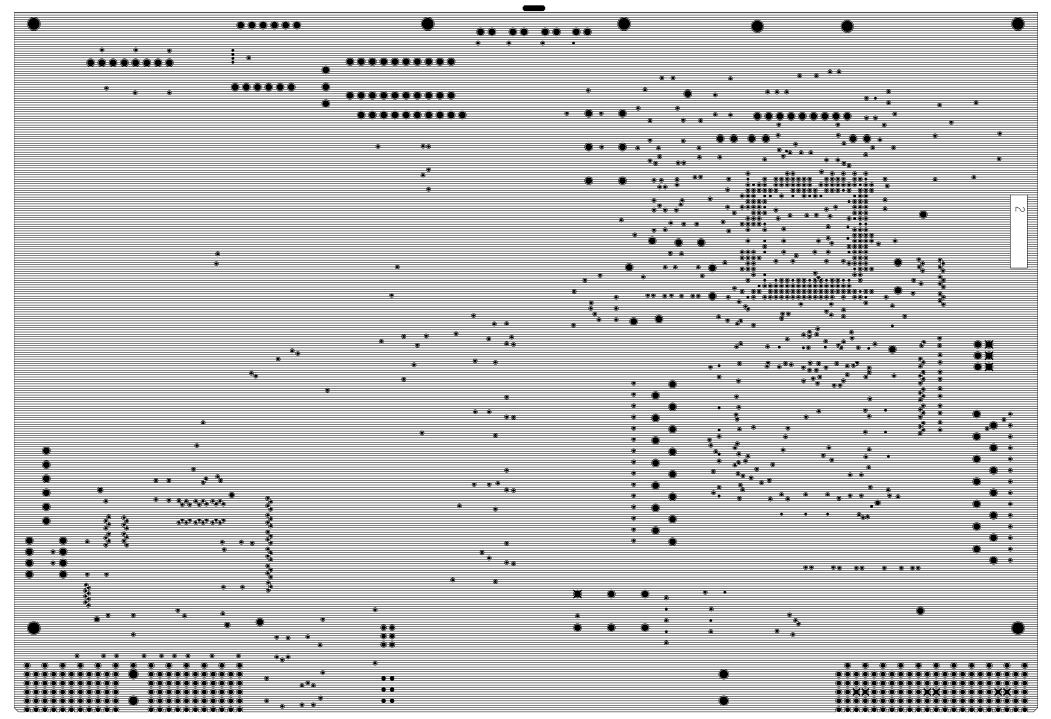

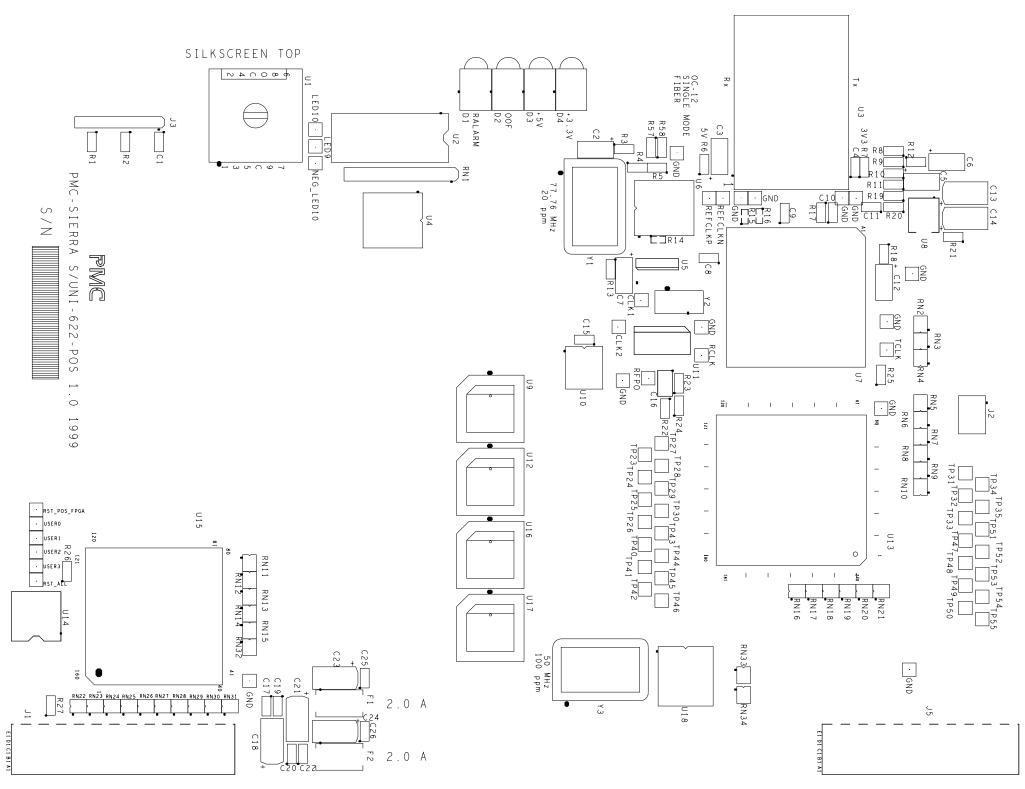

## Figure 2: Picture of S/UNI-622-POS Reference Design PCB

- Provides one single-mode or multi-mode OC-12c rate 622.08 Mbit/s SONET/SDH Physical Layer Port

- Provides a Utopia Level 2, 50 MHz, 16-bit ATM Single-PHY System Interface to the FPGA or cPCI J5.

- Provides a POS-PHY Level 2, 50 MHz, 16-bit Packet Over SONET/SDH Single-PHY System Interface to the FPGA or cPCI bus J5 connector.

REFERENCE DESIGN PMC-1981070

PM5357 S/UNI-622-POS

S/UNI-622-POS REFERENCE DESIGN

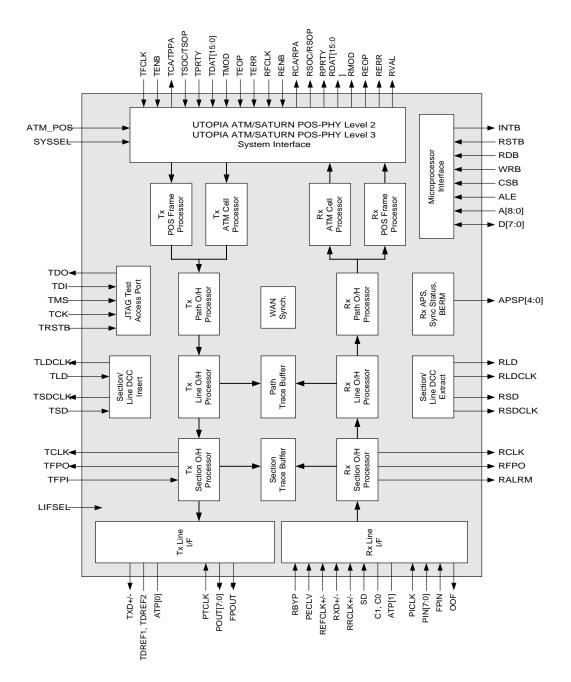

2 S/UNI-622-POS BLOCK DIAGRAM

### Figure 3: S/UNI-622-POS Block Diagram

**ISSUE 2**

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

## 3 APPLICATIONS

The S/UNI-622-POS reference design demonstrates the physical interface implementation for both ATM and POS applications. The list below shows the networking equipment that can incorporate the S/UNI-622-POS device:

- WAN and Edge ATM switches physical interfaces

- LAN switches and hubs physical interfaces

- Packet switches and hubs physical interfaces

The POS Reference Board can be used in four modes:

- Drop Side ATM Loop-Back

- ATM Transparent

- POS Generation/Receiving

- POS Transparent.

This S/UNI-622-POS reference PCB can be configured to demonstrate ATM drop side loopback, ATM transparent to the backplane, POS generation/receiving, and POS transparent to the backplane as described in more detail below.

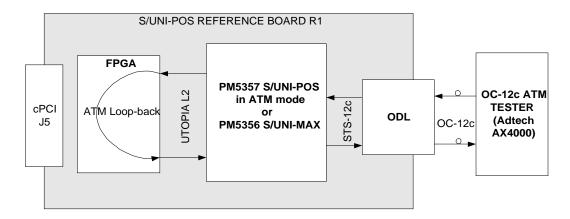

### 3.1 ATM Drop Side Loop-Back

In an ATM application, the S/UNI-622-POS reference design interfaces to one OC-12c rate SONET/SDH signal on the line side. On the drop side, the S/UNI-622-POS interfaces directly to an FPGA that can be programmed to do drop side loop-back as shown in figure 1 below. An external ATM/SONET tester must generate ATM cells within SONET OC-12c frames. The POS device must be programmed for ATM mode by strapping the POS\_ATMB pin (Y21) low. In addition, register 0x48, Transmit Path Signal Label, the SONET C2 byte, defaulted to 0x01, must be set to 0x13 to identify the payload to be ATM cells. The FPGA must be configured from the ATM Loop-back EPROM by selecting the correct EPROM via the dial up switch on the PCB before boot-up. The FPGA source VHDL code is enclosed in the Appendix at the end of this document.

PM5357 S/UNI-622-POS

REFERENCE DESIGN PMC-1981070

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

## Figure 4: ATM Drop Side Loop-Back

### 3.2 ATM Transparent

FPGA can also be configured to act like a transparent interface between the POS UTOPIA L2 and the cPCI J1 connector. The user can then connect a UTOPIA L2 compliant ATM Link layer device to the cPCI J1 connector and a SONET/ATM tester on the OC-12c side as shown in figure below.

Figure 5 below shows how the S/UNI-622-POS reference design can be used in a complete ATM switching design.

#### Figure 5: ATM Transparent

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

#### 3.3 POS Source and Receive Packets

The FPGA can be configured to generate packets and compare these packets when they are looped back as shown below. In a Packet Over SONET/SDH application using the PPP protocol, the S/UNI-622-POS reference design interfaces to an OC-12c rate SONET/SDH signal on the line side. On the drop side, the S/UNI-622-POS reference design interfaces directly with an FPGA programmed to act as a link layer processor using a 256 byte synchronous FIFO SATURN POS-PHY Level 2 interface over which packets are transferred.

### Figure 6: Packet generation and receiving using FPGA

#### 3.4 POS Transparent

The FPGA can be configured to be packet transparent while connected to an external stand-alone SATURN compliant, POS-PHY tester or a POS link layer device.

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

#### Figure 7: POS Transparent to backplane

## 3.5 Reference PCB with other PMC-Sierra ATM chips

This reference board can be potentially used within a larger system utilizing PMC-Sierra's ATM chip sets.

S/UNI-622-POS REFERENCE DESIGN

#### 3.6 Using the Reference board with Packet Switch

This reference board can also be potentially used within a larger system utilizing packet switch and link layer processors as shown below.

#### Figure 9: S/UNI-622-POS Ref Design with POS Link Layer Device

REFERENCE DESIGN PMC-1981070

**ISSUE 2**

S/UNI-622-POS REFERENCE DESIGN

#### 4 REFERENCES

- PMC-Sierra, Inc., PMC-980911 "PM5357 S/UNI-622-POS Data Sheet", Issue 3, Jan. 15, 1999

- PMC-Sierra, Inc., PMC-980589 "PM5356 S/UNI-622-MAX Data Sheet", Issue 4, Jan. 15, 1999

- Bell Communication Research SONET Transport Systems: Common Generic Criteria, GR-253-CORE, Issue 2, December 1995

- CompactPCI<sup>™</sup> specification, PICMG 2.0 R2.1, September 2, 1997.

- ATM Forum AF-PHY-0039.00, "UTOPIA Level 2, Version 1.0", June, 1995.

- ATM Forum STR-PHY-UL3-01.00, "UTOPIA Level 3", April, 1999

- PMC-Sierra's web site for this device, the IBIS models, BSDL file, and drivers can be found on PMC-Sierra's Internet Site.

- Digital High Speed Design, A Handbook of Black Magic, Prentice Hall PTR, by Howard W. Johnson, Martin Graham,

S/UNI-622-POS REFERENCE DESIGN

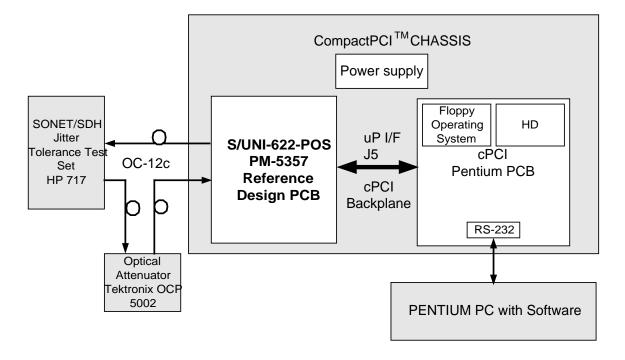

## 5 SYSTEM FUNCTIONAL DESCRIPTION

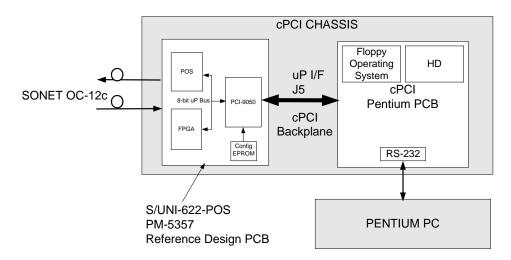

This Reference Design Board utilized a cPCI form factor hence it may only be tested within the cPCI environment. This system is composed of a cPCI chassis, the POS Reference PCB, Pentium PCI board with operating system SW, and an external Pentium PC with dumb terminal software. In addition an external SONET ATM and/or POS tester is required to generate and receive ATM or POS data to/from the S/UNI-622-POS framer.

### Figure 10: SYSTEM LEVEL BLOCK Diagram

ISSUE 2

#### 6 FUNCTIONAL DESCRIPTION

#### 6.1 BLOCK DIAGRAM

The figure below shows the major components on the reference design.

#### Figure 11: Reference Design Block Diagram

### 6.2 S/UNI-622-POS

The PM5357 S/UNI-622-POS and the PM5356 S/UNI-622-MAX are very similar devices. The PM5356 implements ATM framing and the PM5357 implements ATM and POS framing. These SATURN User Network Interfaces are monolithic integrated circuits that implement SONET/SDH processing, ATM mapping and Packet Over SONET/SDH mapping functions at the STS-12c/STM-4-4c, 622.08 Mbit/s rate.

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

The S/UNI-622-POS receives SONET/SDH streams using a bit serial interface, recovers the clock and data and processes section, line, and path overhead. The S/UNI-622-POS can also be configured for clock and data recovery and clock synthesis by-pass where it receives SONET/SDH frames via a byte-serial interface.

When used to implement an ATM UNI or NNI, the PM5357 S/UNI-622-POS and the PM5356 S/UNI-622-MAX frame to the ATM payload using cell delineation.

When used to implement packet transmission over a SONET/SDH link, the PM5357 S/UNI-622-POS, extracts Packet Over SONET/SDH (POS) frames from the SONET/SDH synchronous payload envelope.

The S/UNI-622-POS transmits SONET/SDH streams using a bit serial interface. This framer chip can also be configured for clock and data recovery and clock synthesis by-pass where it transmits the SONET/SDH frames via a byte-serial interface.

When used to implement an ATM UNI or NNI, ATM cells are written to an internal four cell FIFO using a 16-bit wide UTOPIA Level 2 (clocked up to 50 MHz) or an 8-bit wide Utopia Level 3 compatible (clocked up to 100 MHz) datapath interface. Idle/unassigned cells are automatically inserted when the internal FIFO contains less than one complete cell.

When used to implement a Packet over SONET/SDH link, the S/UNI-622-POS inserts POS frames into the SONET/SDH synchronous payload envelope. Packets to be transmitted are written into a 256-byte FIFO through a 16-bit SATURN POS-PHY Level 2 or Level 3 system side interface.

No line rate clocks are required directly by these chips, as they synthesize the transmit clock and recover the receive clock using a 77.76 MHz reference clock. These framers output serial differential PECL line data (TXD+/-).

The S/UNI-622-POS is configured, controlled and monitored via a generic 8-bit microprocessor bus interface. These devices also provides a standard 5 signal IEEE 1149.1 JTAG test port for boundary scan board test purposes.

Both these devices are implemented in low power, +3.3 Volt, CMOS technology. They have TTL compatible digital inputs and TTL/CMOS compatible digital outputs. High speed inputs and outputs support 3.3V and 5.0V compatible pseudo-ECL (PECL). Detailed information about the PM5357 S/UNI-622-POS is available in the data sheet PMC-980911 and the PM5356 in data sheet PMC-980589.

S/UNI-622-POS REFERENCE DESIGN

REFERENCE DESIGN PMC-1981070

#### 6.3 Microprocessor Interface

The S/UNI-622-POS chip and rest of the reference board is controlled through the cPCI interface connector J1. All read and writes to the S/UNI-622-POS chip and the FPGA are executed through this cPCI bus.

## Figure 12: Microprocessor Interface

At the physical level, the POS chip address and data bus is connected to the PLX chip (a PCI-9050 bus interface chip). The Address, A[10:2] and data bus, D[7:0], are multiplexed. The data bus is 8-bits wide (single byte) and the PLX chip must be programmed for this mode via it's external configuration EMPROM.

The local cPCI PCB  $\mu$ P should be running an operating system that allows the user to be able to access the PM5356/PM5357 registers.

## 6.4 External Connectors

The S/UNI-622-POS reference design contains two main back-plane connectors, J1 for the CompactPCI<sup>TM</sup> bus and J5 for the external UTOPIA/POS-PHY Level 2 drop-side.

J3, an 8-pin header is used to download the FPGA during code debugging from the PC to the reference board via a DLC4 Parallel Xchecker cable.

### 6.5 UTOPIA and POS-PHY drop side interface

For ATM applications, the PM5356/PM5357 and S/UNI-622-POS/MAX supports UTOPIA Level 2, Level 3 (UL2 and UL3) synchronous drop side interfaces.

S/UNI-622-POS REFERENCE DESIGN

For packet data (POS) applications the S/UNI-622-POS supports POS-PHY Level 2 and Level 3 bus interface.

On this PCB only the ATM Forum UTOPIA Level 2 (UL2) is supported at 50 MHz and 16 bits wide. The UL2 is used on many other PMC-Sierra ATM framers such as the S/UNI-LITE, S/UNI-ULTRA and S/UNI-622.

The UTOPIA Level 3 runs at 100MHz at 8-bits wide but is not supported on this PCB. For more information on these interfaces please consult the data sheets.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE 14

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

#### 7 IMPLEMENTATION DESCRIPTION

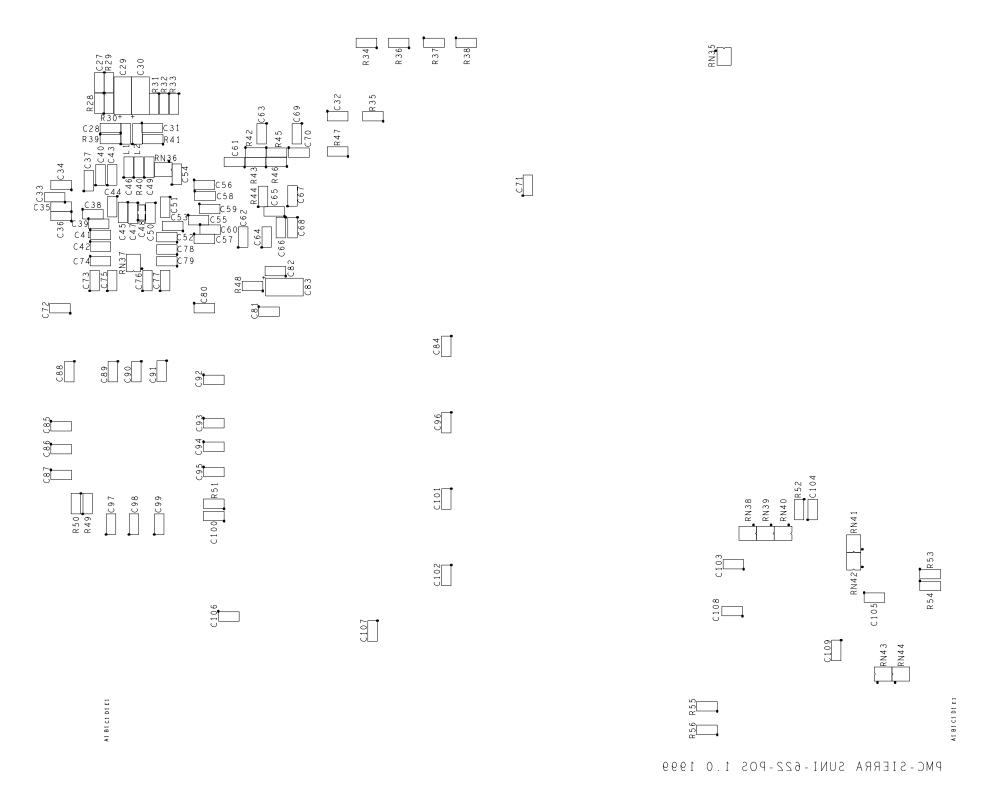

In this document, the S/UNI-622-POS schematics refer to the schematics titled "S/UNI-622-POS reference design".

The S/UNI-622-POS reference design schematics were captured using Cadence software, Concept Schematics Capture Tool.

#### 7.1 ROOT DRAWING, Sheet 1

This sheet provides an overview of the major functional blocks of the S/UNI-622-POS reference design. The schematic was designed in a hierarchical format. The interconnections between the OPTICS\_BLOCK, POS\_BLOCK, POS BLOCK POWER SUPPLY FILTERS, SYS\_INTERFACE, FPGA, FPGA EPROMs and PCI BUS Interface are labeled with a xxx\I.

#### 7.2 ODL and 77.76 MHz reference, Sheet 2

This page includes the OC-12, 622mHz Optical Interface and the 77.7600 MHz line side clock reference interface to the POS chip.

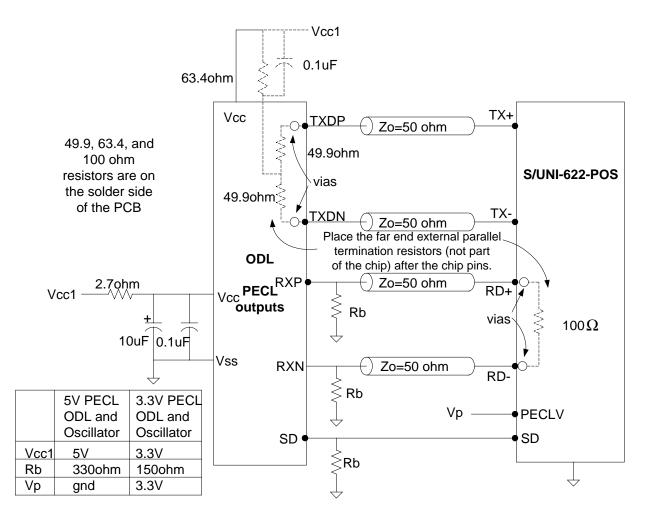

#### 7.2.1 622 Mbit/s Optical Interface

The ODL circuit consists of power supply filtering, ODL, TX and RX PECL terminations and SD connection.

The PECL signals run on 50 Ohm controlled impedance signal lines and are properly terminated at the ODL and at the S/UNI-622-POS device.

The S/UNI-622-POS device interfaces to one HP HFCT-5208 Single mode Fiber Transceivers. The HFCT-5208 transceivers are in a 1 x 9-pin package with a duplex SC receptacle. There are several manufacturers that market OC-12 ODL's including HP and Siemens in 5V and 3.3V options.

It's important that the oscillator is PECL and not the cheaper CMOS or TTL output type. Any jitter at the S/UNI-622-POS reference input may be seen at the TXD+/- data outputs and this translates into Optical output jitter. The 3.3V Connor Winfield EE14-541, 77.7600MHz Oscillator is specified at 10ps RMS output jitter and it's PECL outputs have rise/fall times of 550ps. The Connor Winfield 5V EH13-541 is specified at a much higher rise/fall times of 2.3ns max. Although no extensive tests were done with these two oscillators, no appreciable intrinsic jitter difference was noticed.

REFERENCE DESIGN PMC-1981070

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

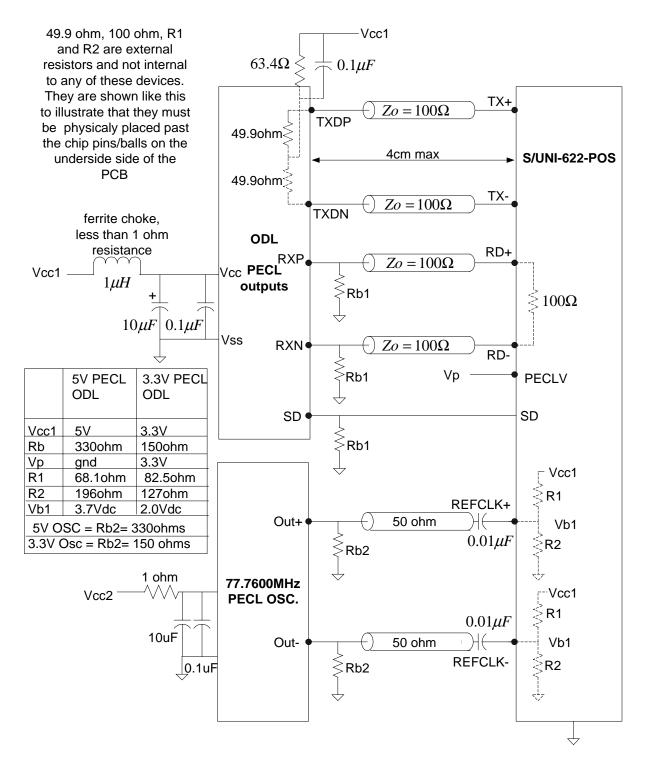

## Figure 13: ODL Line Interface Terminations

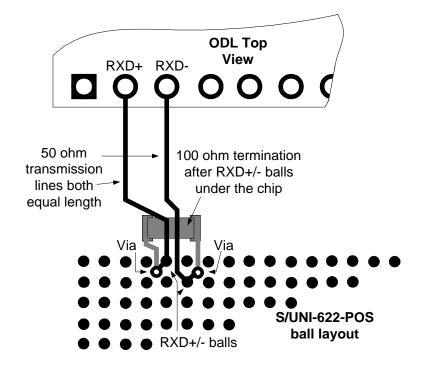

The S/UNI-622-POS reference design provides a single optical interface running at 622 Mbit/s OC-12c rate. The line interface consists of one single mode or multimode optical data link (ODL) and a termination scheme for the PECL signal into and out from the S/UNI-622-POS transmit, TXD+/- and receive, RXD+/- signal pairs. The suggested termination scheme for the PECL transmit and receive signals is shown in Figure 4 for 3.3V and 5V ODLs.

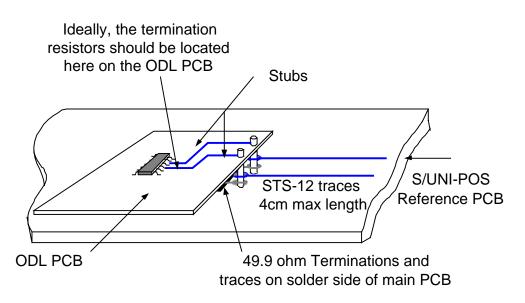

Notice in the schematic above, that the far end terminating resistors in dotted lines are placed after the chip (or ODL) pins so that transmission stubs are avoided and reflections are reduced. A suggested layout with the terminating 100 ohm resistor is shown below. Similarly the TXD+/- 49.9 ohm resistor termination circuit should be located on the solder side of the PCB and after the ODL pins.

PMC PMC-Sierra, Inc.

PM5357 S/UNI-622-POS

REFERENCE DESIGN PMC-1981070

**ISSUE 2**

S/UNI-622-POS REFERENCE DESIGN

### Figure 14: RXD+/- PCB layout

In normal operation, the S/UNI-622-POS performs clock and data recovery on the incoming serial stream. As an option, internal clock and data recovery may be bypassed by setting the RBYP pin high and providing an externally recovered receive clock on the RRCLK+/- pins. In this mode RXD+/- is sampled on the rising edge of RRCLK+/-. This reference design is intended to use the PM5356/PM5357 internal clock and data recovery only and provides a footprint fitting the HFCT-5208 type ODL with a 1x9 pin duplex SC receptacle only.

Optionally, a footprint and function compatible, Siemens 3.3V ODL can be used, PN# V23826-H18-C363. Comparable jitter performance was observed with the 5V and the 3.3V ODL.

In loss of signal condition, indicated by the SD (signal degrade) pin or a lack of data transitions for 80 consecutive bit periods, the S/UNI-622-POS will squelch the receive data and the clock recovery unit will switch to the reference clock (77.76MHz) to keep the recovered clock in range. This technique guarantees that the S/UNI-622-POS will generate a LOS indication when the ODL loses incoming light.

The ODL power supplies are filtered as recommended by the manufacturer. The TX and RX supplies are filtered with a 1 $\mu$ H series coil, a 10 $\mu$ F bulk Tantalum and a ceramic 0.1 $\mu$ F ceramic cap. However, if the power supply is 'noisy', greater than 100mVp-p, additional filtering may be required.

S/UNI-622-POS REFERENCE DESIGN

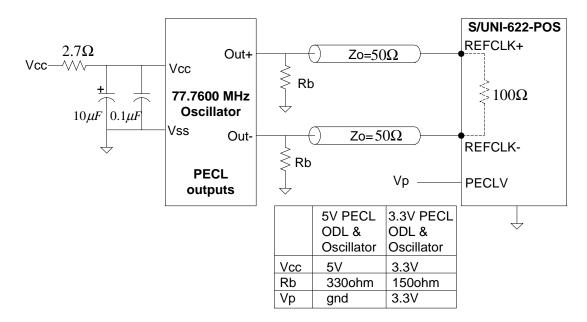

### 7.2.2 77.7600 MHz Reference Clock Circuitry

**ISSUE 2**

The SONET OC-12 line reference clock can be categorized into two classes of applications, WAN and LAN. The scope of this document only covers the LAN case.

For WAN applications, a WAN compliant clock must be employed. This type of reference basically must be Phase Lock Looped (Line Timed) to the WAN network and must have no phase hits during a switch-over if loss of network reference is lost and have a long hold over. To achieve such a stringent requirement, an external digital PLL with a VCXO could be utilized to synchronize to the recovered 77.76MHz clock, RCLK or 8KHz frame pulse, RFPO.

For LAN applications, a 77.76 MHz reference on this board consist of a PECL differential output, 77.76MHz oscillator. For LAN applications or edge switches, a 20ppm oscillator is adequate.

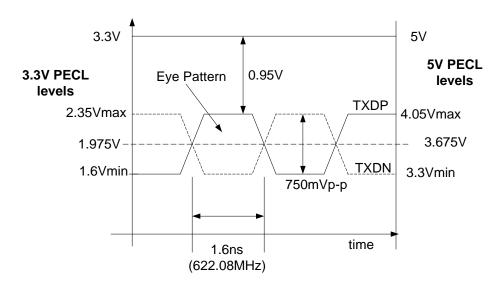

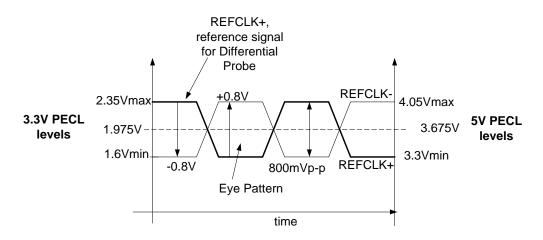

The PM5356 band PM5357 can accommodate either 5V or 3.3V PECL inputs. The PECLV pin selects which voltage range, 5V or 3.3V PECL, both the REFCLKP/N and RXD+/- pins will comply to. Both signals have to be either 3.3V or 5V PECL, depending on the PECLV pin. Both 3.3V and 5V PECL have a 0.8Vp-p swing but the 5V PECL is typically 3.2V to 4.1V. The 3.3V PECL is 1.6V to 2.4 V.

The PECLV pin on the framer programs both the ODL PECL I/F pins and the 77.76MHz Oscillator PECL inputs. Therefore, if the ODL is the same voltage as the Oscillator (both are either 3.3V or 5V type) then you can use the Oscillator circuit shown in Figure 15: 77.7600 MHz Reference Oscillator below. If the ODL and the oscillator are of different voltage, (ODL is 5V and Oscillator is 3.3V), then you must A.C. couple the oscillator with 0.01uF capacitors as shown in Figure 16: Mixing PECL 5V and 3.3V ODL and 77MHz Oscillators.

A single 100 ohm terminating resistor across the PECL signals is preferred over the two resistors per PECL trace method unless the signal is a.c. coupled as in Figure 16: Mixing PECL 5V and 3.3V ODL and 77MHz Oscillators. The single resistor method offers fewer components and because of component congestion near the 304 ball SBGA, it is easier to place one resistor than four. To avoid a transmission stub and reflections, place the terminating resistor(s) after the PCB trace contacts the chip pins (balls). In addition, keep the TXD+/- and RXD+/traces to less than 4cm and ensure each pair is of equal length.

REFERENCE DESIGN PMC-1981070

S/UNI-622-POS REFERENCE DESIGN

It is recommended that a low jitter oscillator be used to achieve the 0.10UIp-p (0.01UIrms) output Intrinsic Jitter. Low reference jitter is required because the clock synthesis unit (CSU) has to multiply the 77MHz reference by eight to generate the transmit 622Mhz. The jitter and noise is also multiplied.

Special attention must be given to ensure the Oscillator has a clean power supply since the output frequency will be modulated (jitter) by the DC voltage level or the AC noise. A RC type of voltage low pass filter is utilized to produce pole at 6Khz. A 2.7Ohm series resistor is used followed by  $10\mu$ F Tantalum capacitor and a  $0.1\mu$ F ceramic. The 2.7ohm resistor can't be too large because of DC IR loss. The  $10\mu$ F Tantalum eliminates low frequency noise. Ceramic capacitor is used for high frequency de-coupling since ceramic capacitors have a much better high frequency response than Tantalum.

The two PECL devices, ODL and the 77.76 PECL Reference Oscillator, can be of different voltage type, 5V or 3.3V. However it is preferable to strap the PECLV pin for the ODL's requirements because the SD signal is a DC signal and level shifting will require extra active components. You can AC couple (use  $0.01\mu$ F ceramic caps) and level shift the oscillator appropriately as shown below. Ensure that the 100 ohm resistor is placed after the chip pins instead of before the pins, otherwise a short stub may cause reflection problems.

It is not recommended to use a TTL oscillator and convert to PECL since this would introduce extraneous jitter.

REFERENCE DESIGN PMC-1981070

PM5357 S/UNI-622-POS

S/UNI-622-POS REFERENCE DESIGN

#### Figure 16: Mixing PECL 5V and 3.3V ODL and 77MHz Oscillators

**ISSUE 2**

S/UNI-622-POS REFERENCE DESIGN

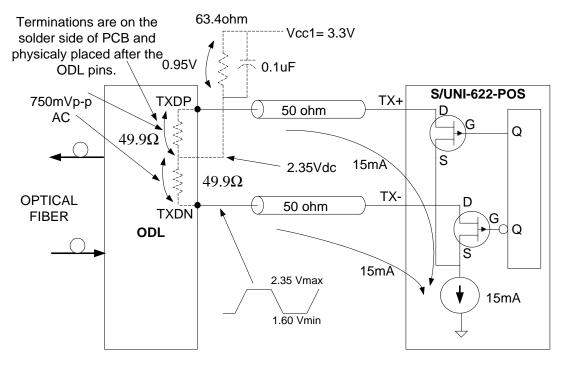

## 7.2.2.1 TXD+/- 15mA Current Drivers

The PM5357/PM5356 use CMOS open Drain 15mA current steered differential drivers as shown below. Since these TXD+/- drivers are not standard PECL BIPOLAR logic (Emitter Coupled Logic), with open emitter outputs, it is important to use exactly the circuit illustrated in "Figure 18: PM5357 TXD+/- Open Drain Current Drivers", to interface to the ODL.

At any one time, only one of the framer TXD outputs is sinking 15mA of current while the other one is off in a high impedance state. Here is an analysis of the TXD+/- drivers:

$$15mA \times 49.9\Omega = 750mVp - p$$

and

$$15mA \times 63.4\Omega = 0.951mVdc$$

Since 15mA always flows through the 63.4  $\Omega$  resistor, there will always be a DC drop of 0.951V across this resistor. An extra 0.1µF capacitor is added across the 63.4  $\Omega$  to make sure that this 2.35Vdc, an 'ac ground' voltage, has no ripple or noise. So the ac voltage at the ODL TXDP and TXDN inputs are as shown in figure below. The same calculations can be used for the 5V ODL with the same peak to peak voltage of 0.75 Vp-p but level shifted up and centered around 3.7V

Figure 17: PECL STS-12 Vp-p

It's critical that controlled PCB transmission line type traces be used for this highspeed 622.08 MHz signals with typical edge rates of 250ps. Even though the PMC-1981070

S/UNI-622-POS REFERENCE DESIGN

symbol rate is actually only half that speed, at 311.04 MHz, the 250ns edges must be treated like transmission line to achieve the desired jitter performance.

Because the terminations are outside the ODL and not inside the ODL package, there is a short stub on the ODL PCB. Ideally the terminating resistors should be located on the ODL PCB at the inputs to the driver as shown below.

Because of this stub, the ODL should not be farther than 4cm away from the S/UNI-622-POS. For longer traces, a PECL buffer is recommended on the TXD+/- signals and an ODL with integrated termination like the Siemens V23826-H18-C313 AC/DC option.

## Figure 18: PM5357 TXD+/- Open Drain Current Drivers

ISSUE 2

Ensure that the 49.90hm resistors are placed after the ODL pins to avoid having a stub in the PCB trace as shown in Figure 19: Location of Terminations of TXD+/-. The terminating impedance, two resistors in this case, must be placed at the farthest end of a transmission line.

PMC-Sierra, Inc.

S/UNI-622-POS REFERENCE DESIGN

## Figure 19: Location of Terminations of TXD+/-

## 7.3 POS\_BLOCK, Sheet 3

The POS\_BLOCK shows the PM5357 S/UNI-622-POS chip, all interface signals and power connections. If only ATM functionality is required, the PM5356 S/UNI-622-MAX may be soldered in the same footprint.

There are no Series resistors used to source terminate the UTOPIA/POS-PHY bus lines because the traces to the terminating device, the FPGA, are very short. However, if the traces were longer, one could use 51  $\Omega$  termination resistors combined with the output impedance of the UTOPIA/POS-PHY pads matches the impedance of the trace at 65 Ohms.

A 2K Ohm resistor is placed across the TDREF0 and TDREF1 pins. An LED displays line RX alarm status for the S/UNI-622-POS via a buffer 74HC04 chip. The RALRM output must be enabled in register 0x00E and 0x00F. RALRM out can be programmed to go high if there is alarms such as LAIS, PAIS, LRDI, PRDI, LOS< RDI, LOF, OOF, LOP, pointer AIS, LOPC, LCD, SFBER, and SDBER.

A 1K Ohm resistor is also placed in series with the power supply to limit the Vbias and Pbias current to prevent latch-up. A  $0.1\mu$ F is added to eliminate high frequency noise. A 100  $\Omega$  series resistor is also required to the QAVD biasing pins to prevent latchup.

PROPRIETARY AND CONFIDENTIAL TO PMC-SIERRA, INC., AND FOR ITS CUSTOMERS' INTERNAL USE 23

PRELIMINARY

REFERENCE DESIGN PMC-1981070

PMC-Sierra, Inc.

PM5357 S/UNI-622-POS

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

PECLV pin can be tied high or low with the resistor option, depending on whether 3.3V or 5V PECL interfaces are used for the 77.76 MHz clock reference and ODL.

The board has several test points such as RCLK and TCLK to facilitate debugging.

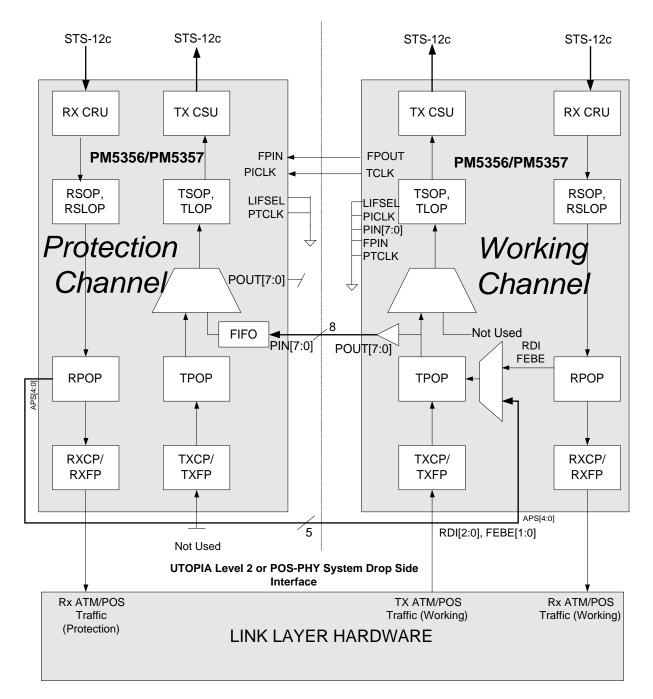

APS[4:0] pins are tied low through  $4.7K\Omega$  resistors. The APS pins provide a control bus between two S/UNI-622-POS devices to implement a 1+1 APS function. When using APS mode, line data is passed from one S/UNI-622-POS device to another using the FPIN, PIN[7:0], FPOUT, and POUT[7:0] pins. The APS function is not implemented in this reference design.

Care must be employed to ensure good PECL termination. In a far-end parallel termination scheme as employed on this case, usually the 100  $\Omega$  resistor should be placed after the chip pins otherwise the traces may be seen as stubs and reflections may occur. Reflections can cause poor jitter performance.

For more information on the PM5356 and PM5357 please refer to the data sheets.

#### 7.3.1 Loop Filter Capacitor

A 47nF capacitor is placed across the loop filter pins, C1 and C0 to ensure a stable recovered clock. To maintain jitter transfer peaking of less than 0.1db over the life of the product, the capacitor must be a stable 47nF +/-5%. The best practical choice is a Class 2 X7R SMT ceramic type which has low aging characteristics, and a +5% to -10% capacitance change over -40°C to +85°C temperature.

#### 7.3.2 Pullup and Pulldown Resistors

All unused CMOS inputs should be tied off high or low.

Unused PECL pins such as RRCLK+ and RRCLK- (or RRCLKP and RRCLKN respectively) should be tied to the opposite polarity. Failure to tie RRCLK+ and RRCLK- to complementary values will result in signal contention within the device which may cause problems with device operation.

When tying an input to ground, the pin may be connected directly to ground. When tying an input to 3.3V or 5V, a 4.7Kohm resistor should be used in order to prevent latch up during power up.

S/UNI-622-POS REFERENCE DESIGN

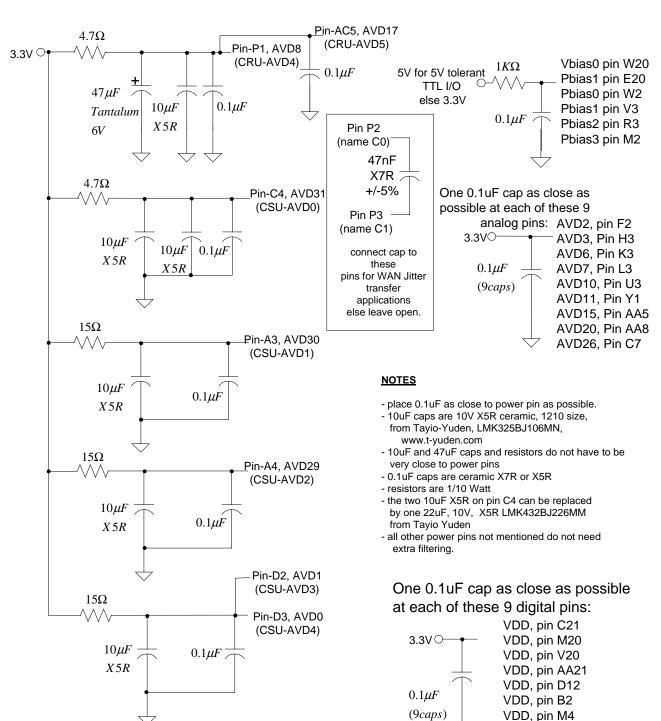

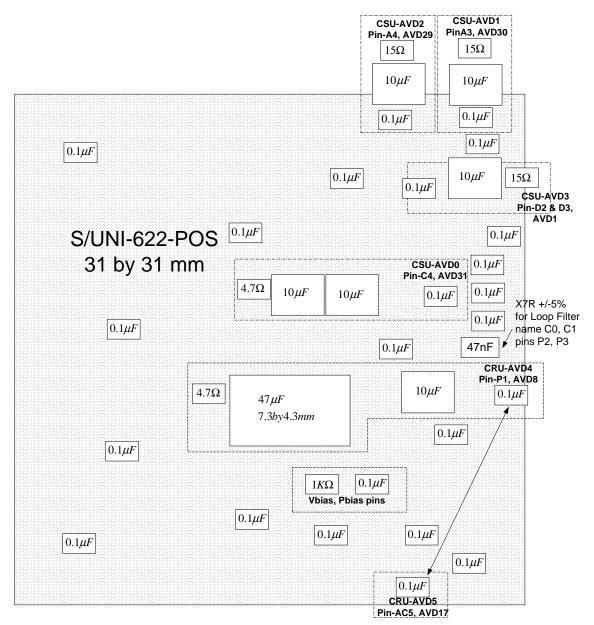

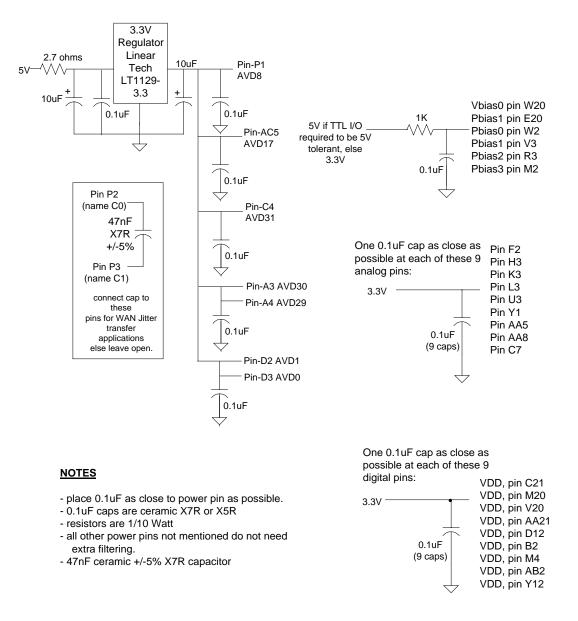

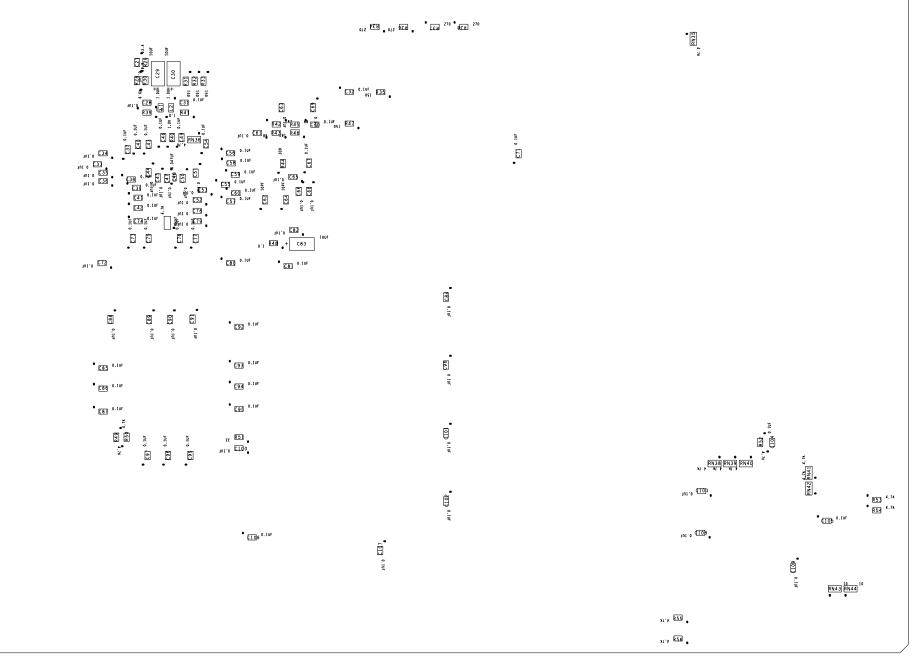

#### 7.4 Power Supply Filter for the PM5357 Sheet 4

**ISSUE 2**

This page shows how to clean up the power supply to the S/UNI-622-POS. Because this IC has mixed analog and digital circuits, care must be used to eliminate noise from affecting the critical analog sections. The analog power supply must be filtered as shown below.

In addition, 0.1µF ceramic capacitors are used to filter the digital supply.

These chips will function in either a 3.3V only system or a mixed 3.3V and 5V TTL UTOPIA bus environment. Typical power planes should be used in a multi layer board with sufficient filtering with high quality high frequency ceramic  $0.1\mu$ F caps on the digital rail and bulk filtered at the board connectors.

The S/UNI-622-POS performs clock and data recovery at a very high speed. Analog circuitry responsible for clock and data recovery must be free of noise to ensure reliable operation. Less sensitive analog power pins are grouped together and filtered with a single 0.1  $\mu$ F capacitor. The more sensitive analog power pins of the S/UNI-622-POS are de-coupled using a low pass RC filter method. If there is a lot of power supply noise, >100mVp-p in the 3.3V rail, and a 5V supply is available, then a linear regulator approach is recommended.

#### 7.4.1 Passive RC low pass power supply Filter

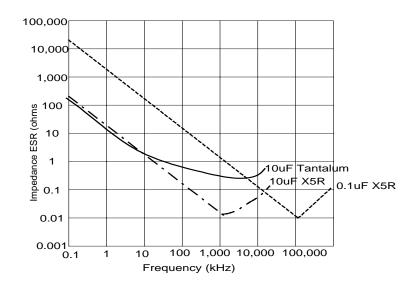

If there is no 5V rail available and the 3.3V supply is not very noisy (less than 100mVp-p at all frequencies), then this method is acceptable. Several capacitors may have to be paralleled to achieve the filtering across the desired frequency band. The  $10\mu$ F capacitors should be X5R ceramic type and not Tantalum. Also use a  $0.1\mu$ F X5R for high frequency noise reduction. The Issue 3 schematics use this passive filter method.

The X5R type capacitors have excellent low and high frequency response as seen in the graph below. The lower the impedance is, the better the capacitor for filtering. An excellent manufacturer of small size, non-polarized ceramic capacitors is Taiyo Yuden of 1930 North Thoreau, Drive, Suite 190, Schaumburg IL, 60173 USA, 1-80036-TAIYO. The X5R capacitors are similar to X7R except the high temperature spec is +85°C instead of 125°C for the X7R. These X5R ceramics are available up to  $10\mu$ F at 6.3 Volts.

| PRELIMINARY                     | PMC PMC-Sierra, Inc. | PM5357 S/UNI-622-POS           |

|---------------------------------|----------------------|--------------------------------|

| REFERENCE DESIGN<br>PMC-1981070 | ISSUE 2              | S/UNI-622-POS REFERENCE DESIGN |

|                                 |                      |                                |

Figure 20: Tantalum & X5R Ceramic Impedance vs. Freq.

PM5357 S/UNI-622-POS

REFERENCE DESIGN PMC-1981070

**ISSUE 2**

S/UNI-622-POS REFERENCE DESIGN

VDD, pin AB2 VDD, pin Y12

## Figure 21: Passive RC Analog Power Supply Filtering

| PRELIMINARY      | PMC PMC-Sierra, Inc. | PM5357 S/UNI-622-POS           |

|------------------|----------------------|--------------------------------|

| REFERENCE DESIGN |                      |                                |

| РМС-1981070      | ISSUE 2              | S/UNI-622-POS REFERENCE DESIGN |

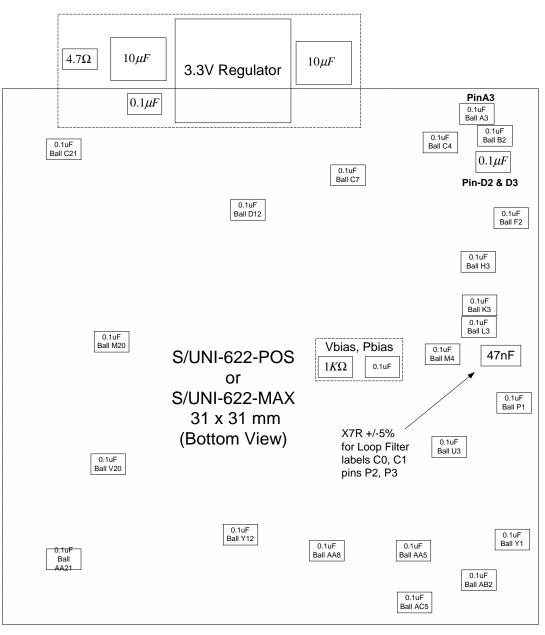

Figure below shows relative size of components and is not meant to show placement location since it's difficult to place components on the solder side of a BGA.

Figure 22: RC Passive Filter Method Mechanical Diagram

#### Parts Count

- 6 10uF 10V, X5R, 1210 (3.2 x 2.5 mm) size ceramic caps, LMK325BJ106MN

- 24 0.1uF, X7R, 0805 body (2 by 1.25mm)

- 1 47nF +/-5% ceramic X7R Class 2 capacitor

- 3 15 ohm R's, 1/10 W, 0805 body (2 by 1.25mm)

- 2 4.7 ohm Resistor, 1/10 W, 0805 body (2 by 1.25mm)

- 1 47uF Tantalum capacitor, 6.3V, SMT

Note: the resistors and the 10uF/ 47uF caps do not have to be close to the chip pins.

S/UNI-622-POS REFERENCE DESIGN

## 7.4.2 Linear Regulator Filter Method

If there is a 5V supply available, and the 3.3V supply has a lot of noise (>100mVp-p), then a better method to filter the analog supplies is with a "low drop-out voltage regulator" such as the LT1129-3.3 from Linear Technology. This regulator typically has about a 50db noise rejection up to about 500 kHz. Further noise attenuation is achieved with a front end the RC pre-filter (2.7 ohm + 10  $\mu$ F) and a high frequency 0.1 $\mu$ F ceramic at the input to the regulator. A 10  $\mu$ F Tantalum is required at the output for regulator stability.

| PRELIMINARY      | PMC-Sierra, Inc. | PM5357 S/UNI-622-POS           |

|------------------|------------------|--------------------------------|

| REFERENCE DESIGN |                  |                                |

| PMC-1981070      | ISSUE 2          | S/UNI-622-POS REFERENCE DESIGN |

Figure below shows relative size of components and is not meant to show placement location since it's difficult to place components on the solder side of a BGA.

# Figure 24: Linear Regulator Filter Mechanical Layout

#### Parts Count

- 2 10uF 10V, Tantalum, 6V

- 26 0.1uF, X7R, 0805 body (2 by 1.25mm)

- 1 47nF +/-5% ceramic X7R capacitor

- 1 2.7 ohm Resistor, 1/10 W, 0805 body (2 by 1.25mm)

- 1 1Kohm resistor

- 1 3.3VLinear Regulator, SOT-23

S/UNI-622-POS REFERENCE DESIGN

### 7.5 FPGA, Sheet 5 and 6

This reference board has a large general purpose Xilinx XC4000 series FPGA (XC4036XLA-HQ240-9NS), filtering, configuration EEPROMs (XC1701), external download header J3, and thumb-wheel switch selector the EPROMS.

The FPGA, U13, is used to interface to the S/UNI-622-POS drop side to give this board some ATM and packet functionality. We chose the largest and fastest device we could find so that we were not restricted during our development. Information on this device is available from Xilinx.

At the time of this document, only the ATM drop side loopback was implemented and debugged. The ATM loopback code for the FPGA is enclosed in this document. ATM transparent, POS generation and POS transparent may be available in the future.

Several pins were brought out into headers (TP's) just in case we wanted to use this device for a different function than originally envisioned. Although they are tied off to ground, provision was made so that the ground trace can be easily cut.

The FPGA has eight LEDs connected to the general purpose I/O pins so that code could be written to selectively light these depending on the FPGA performance at power up and real time status. At power up, all the LEDs are on and when the FPGA is downloaded correctly from the EPPROMS, only the first LED is left on.

A header, J2 is used to select how the FPGA is to be configured at power up. With all the jumpers installed, the FPGA is programmed via the J3 (on page 6), serial cable adapter from a PC development setup. This is only used at time of code debugging. With all the J6 jumpers removed, the FPGA is configured at power up from one of four serial EEPROMs located on page 6 of the schematics.

The serial EEPROMs, U9, U12, U17 and U17 can be used to configure the FPGA for ATM loopback, ATM transparent to the J5 backplane, Packet generation/receiving, and packet transparent. Depending on the thumb wheel selector switch, U1, one of four different functions can be jammed into the FPGA at power up. The XC1701L EEPROM devices contain 832,528 bits. 20 pin PLCC sockets are used to facilitate ease of changing these programmable devices.

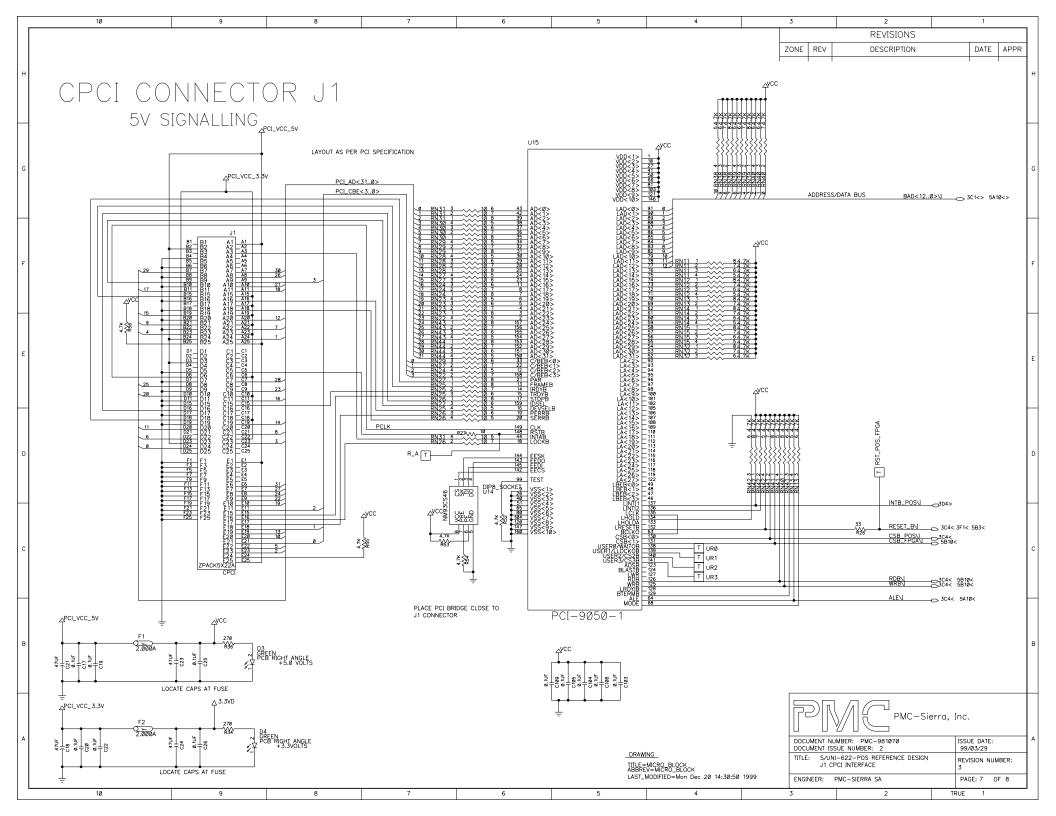

#### 7.6 cPCI BUS Interface Sheet 7

This page contains the CompactPCI<sup>™</sup> bus backplane interface circuitry. It consists of the cPCI connector J1, the PLX bridge chip PCI-9050-1, serial EEPROM, NM93CS46 and power supply.

S/UNI-622-POS REFERENCE DESIGN

## 7.6.1 cPCI Backplane Connector J1

**ISSUE 2**

The J1 cPCI connector details can be found in the CompactPCI<sup>™</sup> specification, PICMG 2.0 R2.1. All register accesses to the S/UNI-622-POS and FPGA are performed through connector. J1 can optionally supply 3.3V and 5V power to the board. Not all cPCI pins are used in this design. Please refer to the enclosed schematic for a detailed pin description.

### 7.6.2 PLX cPCI Bridge chip, PCI9050

The PCI 9050 provides a compact high performance PCI bus target (slave) interface for adapter boards. For more information on this device, please refer to the manufacturer's specification found on the PLX Technology web site. This device is programmed, via the external serial EEPROM, U14 at power up, for a multiplexed, 8 bit local data bus. The PLX chip allows the board to map several devices such as the S/UNI-622-POS and the FPGA to the cPCI bus.

The signals from the J1 connector to the PLX chip are tightly controlled and must adhere to the cPCI physical specification for proper operation. Ten ohm series terminating resistors are used to minimize reflection in all the signals.

Any unused inputs such as the unused LAD (address/data) pins are pulled up with 4.7K resistors.

Also, all tri-state outputs, such as RDB, are pulled up via a 4.7K resistor to prevent the bus from chattering during power up.

We added a couple of test points (RST\_POS\_FPGA, R\_A) isolated by 10 ohm resistors to allow us to reset each chip manually by grounding a node. This allowed us to reset each chip without resetting the whole system which takes a few minutes re-boot from disk.

The address/data bus is multiplexed and the lowest order address is A2. The PLX does 32 bit, 4 byte accesses to/from the framer/FPGA and the cPCI system Software selects the bottom byte only. Notice that the top three data bytes on the PLX are not connected to the bus.

#### 7.6.3 Serial EEPROM

The PLX chip, PCI9050, requires a configuration EEPROM during power up to configure itself. A serial device, U14, NM93CS46 contains the following code to configure the PLX for our system.

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

# Table 1: PLX EPROM Configuration Code

| EPROM  | Register | EEPROM |                                                                    |  |

|--------|----------|--------|--------------------------------------------------------------------|--|

| Offset | Offset   | Value  | Register Description                                               |  |

| 0      | PCI 02   | 9050   | Device ID                                                          |  |

| 2      | PCI 00   | 10B5   | Vendor ID                                                          |  |

| 4      | PCI 0A   | 0680   | Class code                                                         |  |

| 6      | PCI 08   | 0000   | Class code (revision is not loadable)                              |  |

| 8      | PCI 2E   | 5357   | Subsystem ID                                                       |  |

| A      | PCI 2C   | 11F8   | Subsystem Vendor ID                                                |  |

| С      | PCI 3E   | FFFF   | (Maximum Latency and Minimum Grant are not loadable.)              |  |

| E      | PCI 3C   | 01FF   | Interrupt Pin (Interrupt Line Routing is not loadable.)            |  |

| 10     | LOCAL 02 | 0FFF   | MSW of Range for PCI to Local Address Space 0 (1 MB)               |  |

| 12     | LOCAL 00 | FF00   | LSW of Range for PCI to Local Address Space 0 (1 MB)               |  |

| 14     | LOCAL 06 | 0FFF   | MSW of Range for PCI to Local Address Space 1                      |  |

| 16     | LOCAL 04 | F800   | LSW of Range for PCI to Local Address Space 1                      |  |

| 18     | LOCAL 0A | 0000   | MSW of Range for PCI to Local Address Space 2                      |  |

| 1A     | LOCAL 08 | 0000   | LSW of Range for PCI to Local Address Space 2                      |  |

| 1C     | LOCAL 0E | 0000   | MSW of Range for PCI to Local Address Space 3                      |  |

| 1E     | LOCAL 0C | 0000   | LSW of Range for PCI to Local Address Space 3                      |  |

| 20     | LOCAL 12 | 0FFF   | MSW of Range for PCI to Local Expansion ROM (62 KB)                |  |

| 22     | LOCAL 10 | 0000   | LSW of Range for PCI to Local Expansion ROM (62 KB)                |  |

| 24     | LOCAL 16 | 0000   | MSW of Local Base Address (Remap) for PCI to Local Address Space 0 |  |

| 26     | LOCAL 14 | 0001   | LSW of Local Base Address (Remap) for PCI to Local Address Space 0 |  |

| 28     | LOCAL 1A | 0000   | MSW of Local Base Address (Remap) for PCI to Local Address Space 1 |  |

| 2A     | LOCAL 18 | 1001   | LSW of Local Base Address (Remap) for PCI to Local Address Space 1 |  |

| 2C     | LOCAL 1E | 0000   | MSW of Local Base Address (Remap) for PCI to Local Address Space 2 |  |

| 2E     | LOCAL 1C | 0000   | LSW of Local Base Address (Remap) for PCI to Local Address Space 2 |  |

| 30     | LOCAL 22 | 0000   | MSW of Local Base Address (Remap) for PCI to Local Address Space 3 |  |

| 32     | LOCAL 20 | 0000   | LSW of Local Base Address (Remap) for PCI to Local Address Space 3 |  |

| 34     | LOCAL 26 | 0000   | MSW of Local Base Address (Remap) for PCI to Local Expansion ROM   |  |

| 36     | LOCAL 24 | 0000   | LSW of Local Base Address (Remap) for PCI to Local Expansion ROM   |  |

| 38     | LOCAL 2A | 5401   | MSW of Bus Region Descriptors for Local Address Space 0            |  |

| ЗA     | LOCAL 28 | 40C0   | LSW of Bus Region Descriptors for Local Address Space 0            |  |

| 3C     | LOCAL 2E | 0080   | MSW of Bus Region Descriptors for Local Address Space 1            |  |

| 3E     | LOCAL 2C | 0000   | LSW of Bus Region Descriptors for Local Address Space 1            |  |

| 40     | LOCAL 32 | 0080   | MSW of Bus Region Descriptors for Local Address Space 2            |  |

| 42     | LOCAL 30 | 0000   | LSW of Bus Region Descriptors for Local Address Space 2            |  |

| 44     | LOCAL 36 | 0080   | MSW of Bus Region Descriptors for Local Address Space 3            |  |

| 46     | LOCAL 34 | 0000   | LSW of Bus Region Descriptors for Local Address Space 3            |  |

| 48     | LOCAL 3A | 0000   | MSW of Bus Region Descriptors for Expansion ROM Space              |  |

| 4A     | LOCAL 38 | 0000   | LSW of Bus Region Descriptors for Expansion ROM Space              |  |

| 4C     | LOCAL 3E | 0000   | MSW of Chip Select (CS) 0 Base and Range Register                  |  |

| 4E     | LOCAL 3C | 1101   | LSW of Chip Select (CS) 0 Base and Range Register                  |  |

| 50     | LOCAL 42 | 0000   | MSW of Chip Select (CS) 1 Base and Range Register                  |  |

| 52     | LOCAL 40 | 1801   | LSW of Chip Select (CS) 1 Base and Range Register                  |  |

| 54     | LOCAL 46 | 0000   | MSW of Chip Select (CS) 2 Base and Range Register                  |  |

| 56     | LOCAL 44 | 0000   | LSW of Chip Select (CS) 2 Base and Range Register                  |  |

| 58     | LOCAL 4A | 0000   | MSW of Chip Select (CS) 3 Base and Range Register                  |  |

| 5A     | LOCAL 48 | 0000   | LSW of Chip Select (CS) 3 Base and Range Register                  |  |

| 5C     | LOCAL 4E | 0000   | MSW of Interrupt Control/Status Register                           |  |

| 5E     | LOCAL 4C | 0000   | LSW of Interrupt Control/Status Register                           |  |

| 60     | LOCAL 52 | 0002   | MSW of EEPROM Control and Miscellaneous Control Register           |  |

| 62     | LOCAL 50 | 4492   | LSW of EEPROM Control and Miscellaneous Control Register           |  |

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

## 7.6.4 Power Supply

The board is powered via the J1 connector from the system cPCI backplane. The 5V and the 3.3V rails are bulk filtered as they enter the board with  $47\mu$ F tantalum capacitors. These power rails are also fused with 2 Amp fuses to prevent the board from severe damage in case of a circuit failure. Because a fuse has a finite "on resistance/impedance", a second  $47\mu$ F is located on the other side of this fuse. An LED is provided for each supply to alert the user if the power is on.

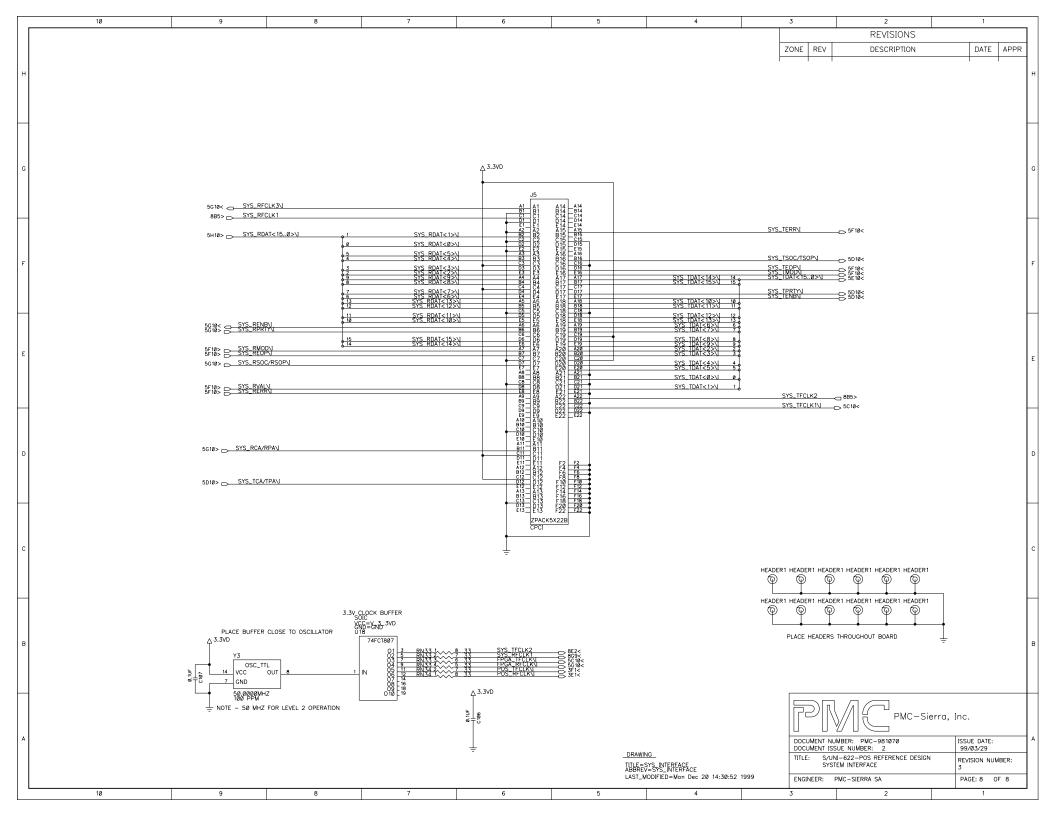

## 7.7 SYS\_INTERFACE, Sheet 8

The SYS\_INTERFACE block contains the J5 UTOPIA board connector and the UTOPIA bus clock oscillator.

### 7.7.1 50mHz UTOPIA Oscillator

A 50 MHz oscillator, 100ppm, is used for the POS-PHY Level 2 or Utopia Level interface rate. If there was a UTPOIA Level 3 provision, a 100 MHz crystal oscillator could have been used. The oscillator does not need any special power supply filter since jitter is not an issue like it is for the 77.7600MHz line side clock reference. However, because of the tight bus timing requirements, a buffer is used to provide low skewed clocks to the PM5357, the FPGA, and to the external J5 connector.

#### 7.7.2 J5 UTOPIA Connector

The J5 connector uses a PMC-Sierra Inc. proprietary pin out for the UTOPIA Level 2 bus as shown in Table 2: J5 UTOPIA Level 2 Connector.

The S/UNI-622-POS UTOPIA Level 2 interface is connected to the drop side J5 connector through the FPGA. The pin names shown below have the prefix "SYS\_" added on the signal names of the schematic.

PM5357 S/UNI-622-POS

REFERENCE DESIGN PMC-1981070

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

# Table 2: J5 UTOPIA Level 2 Connector

| Pin Name                                                                                   | Туре   | Pin<br>No.                                   | Function                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------|--------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RDAT[0]<br>RDAT[1]<br>RDAT[2]<br>RDAT[3]<br>RDAT[4]<br>RDAT[5]<br>RDAT[6]<br>RDAT[7]       | Output | D2<br>B2<br>E3<br>D3<br>B3<br>A3<br>E4<br>D4 | UTOPIA: Receive Cell Data Bus<br>For Utopia Level 2 this bus carries the ATM<br>cell octets that are read from the receive<br>FIFO. For Utopia Level 3 only RDAT[7:0]<br>are valid.                                                |

| RDAT[8]<br>RDAT[9]<br>RDAT[10]<br>RDAT[11]<br>RDAT[12]<br>RDAT[13]<br>RDAT[14]<br>RDAT[15] |        | B4<br>A4<br>E5<br>D5<br>B5<br>A5<br>E6<br>D6 | <u>POS-PHY: Receive Packet Data Bus</u><br>For POS-PHY Level 2 this bus carries<br>Packets that are read from the selected<br>receive FIFO. For POS-PHY Level 3, only<br>RDAT[7:0] are valid.                                      |

| RPRTY                                                                                      | Output | B6                                           | Receive bus parity. The receive parity signal indicates the parity of the RDAT bus.                                                                                                                                                |

| RENB                                                                                       | Input  | A6                                           | Receive Write Enable. The RENB signal is<br>an active low input which is used to initiate<br>reads from the receive FIFO.                                                                                                          |

| RCA<br>RPA                                                                                 | Output | B11<br>B11                                   | UTOPIA: Receive Direct Cell Available<br>This signal indicates an available cell.<br><u>POS-PHY: Direct Receive Packet Available.</u><br>For POS-PHY Level 2, this signal indicates<br>when data is available in the receive FIFO. |

|                                                                                            |        |                                              | For POS-PHY Level 3 this signal is not used<br>as RVAL signals valid data on the bus.                                                                                                                                              |

| RSOC                                                                                       | Output | D7                                           | <u>UTOPIA: Receive Start of Cell</u><br>This signal marks the start of cell on the<br>RDAT bus.                                                                                                                                    |

| RSOP                                                                                       |        | D7                                           | <u>POS-PHY: Receive Start of Packet</u><br>This signal marks the start of packet on the<br>RDAT bus.                                                                                                                               |

| RERR                                                                                       | Output | E8                                           | POS-PHY: Receive Error<br>This signal indicates that the current packet<br>has been aborted. This signal is ignored in<br>Utopia ATM modes.                                                                                        |

PMC-1981070

REFERENCE DESIGN

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

| Pin Name | Туре   | Pin<br>No. | Function                                                                                                                                                                                        |

|----------|--------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REOP     | Output | B7         | POS-PHY: Receive End of Packet<br>This signal marks the end of packet on the<br>RDAT bus. This signal is ignored in Utopia<br>ATM modes.                                                        |

| RMOD     | Output | B7         | RX modulo: Indicates number of bytes in the last RDAT bus transaction of a packet.                                                                                                              |

| RVAL     | Output | D8         | In POS mode, RAVL indicates signals<br>RDAT, RSOP, REOP, RMOD, RPRTY and<br>RERR are valid.                                                                                                     |

| RFCLK3   | Output | A1         | 50 MHz UTOPIA bus clock buffered by the FPGA and same time delay as the actual UTOPA signals.                                                                                                   |

| RFCLK1   | Output | C1         | 50 MHz UTOPIA bus clock straight from the oscillator buffer.                                                                                                                                    |

| TENB     | Input  | E17        | Utopia and POS-PHY:<br>Transmit Write Enable. The TENB signal is<br>an active low input which is used to initiate<br>writes to the transmit FIFO                                                |

| TCA      | Output | D12        | Utopia: Transmit cell available signal<br>This signal is used to indicate available cell<br>FIFO space by the PHY port.<br>POS-PHY: Direct Transmit Packet Available.                           |

| TPA      |        | D12        | This signal transitions to high when a programmable minimum number of free space is available in the transmit FIFO.                                                                             |

| TSOC     | Input  | B16        | Utopia: Transmit Start of Cell<br>The transmit start of cell signal marks the<br>start of cell on the TDAT bus.                                                                                 |

| TSOP     |        | B16        | <u>POS-PHY: Transmit Start of Packet</u><br>For POS-PHY Level 2 this signal indicates<br>the first word of a packet. In POS-PHY<br>Level 3 this signal indicates the first byte in<br>a packet. |

| TERR     | Input  | A15        | POS-PHY: Transmit Error<br>This signal indicates the current packet<br>must be aborted. This signal is ignored in<br>Utopia ATM mode                                                            |

| TEOP     | Input  | D16        | POS-PHY: Transmit End of Packet<br>This signal marks the end of a packet on the<br>TDAT bus. This signal is ignored in Utopia<br>ATM modes.                                                     |

REFERENCE DESIGN PMC-1981070

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

| Pin Name                                                                                                                                                                                      | Туре   | Pin<br>No.                                                                                                   | Function                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TMOD                                                                                                                                                                                          | Input  | E16                                                                                                          | POS-PHY: Transmit Word Modulo<br>For POS-PHY Level 2, this signal indicates<br>the size of the current word. For POS-PHY<br>Level 3 this signal is ignored. This signal is<br>ignored in Utopia ATM modes.                                                                                                                   |

| TPRTY                                                                                                                                                                                         | INPUT  | D17                                                                                                          | Transmit bus parity. The transmit parity signal indicates the parity of the TDAT bus.                                                                                                                                                                                                                                        |

| TDAT[0]<br>TDAT[1]<br>TDAT[2]<br>TDAT[3]<br>TDAT[4]<br>TDAT[5]<br>TDAT[6]<br>TDAT[6]<br>TDAT[7]<br>TDAT[8]<br>TDAT[9]<br>TDAT[10]<br>TDAT[11]<br>TDAT[12]<br>TDAT[13]<br>TDAT[14]<br>TDAT[15] | INPUT  | B21<br>D21<br>A20<br>B20<br>D20<br>E20<br>A19<br>B19<br>D19<br>E19<br>A18<br>B18<br>D18<br>E18<br>A17<br>B17 | Utopia: Transmit Cell Data Bus<br>This bus carries the ATM cell octets that are<br>written to the selected transmit FIFO.<br><u>POS-PHY:</u> Transmit Packet Data Bus<br>This data bus carries the POS packet octets<br>that are written to the selected transmit<br>FIFO. For POS-PHY Level 3, only<br>TDAT[0:7] are valid. |

| TFCLK2                                                                                                                                                                                        | Output | A1                                                                                                           | 50 MHz UTOPIA bus clock buffered by the FPGA and same time delay as the actual UTOPIA signals.                                                                                                                                                                                                                               |

| TFCLK1                                                                                                                                                                                        | Output | C1                                                                                                           | 50 MHz UTOPIA bus clock straight from the oscillator buffer.                                                                                                                                                                                                                                                                 |

| NC                                                                                                                                                                                            | NC     | D9                                                                                                           | Many No Connect Pins. See schematic                                                                                                                                                                                                                                                                                          |

| 3.3VDC                                                                                                                                                                                        | Power  | C3, C4                                                                                                       | 3.3V power supply                                                                                                                                                                                                                                                                                                            |

| GND                                                                                                                                                                                           | Power  | B1, D1                                                                                                       | Ground                                                                                                                                                                                                                                                                                                                       |

REFERENCE DESIGN PMC-1981070

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

## 8 SOFTWARE CONSIDERATIONS

#### 8.1 Path Signal Label 'C2'

Upon reset the S/UNI-622-POS/MAX register 0x48, Path Signal Label, SONET/SDH C2 byte, defaults to 0x01, which signifies an equipped unspecific payload. This device will stuff a 0x01 into the C2 byte in the SONE path overhead until it is changed. This register should be reprogrammed with the value 0x13 when in ATM mode or value 0xCF when in Packet over SONET (POS) mode so that the Path C2 byte will contain the correct payload type. The receiver should have a matching C2 byte so that a signal label mismatch (PSLM) alarm is not declared. If there is a path signal label mismatch the PSLMPAIS bit in register 0x0D will enable path AIS insertion. In this case all ones will be inserted into the receive SONET/SDH payload, the PM5356/PM5357 will not be able to acquire cell delineation and a PATH alarm will be declared.

Upon power up, register 0x54 should be programmed with the expected path signal label of 0x13 for ATM and 0xCF for Packet over SONET (POS).

#### 8.2 SONET or SDH Configuring

The SONET and SDH fiber standards for optical networking are very similar, with only minor differences in overhead processing. The main difference between the SONET and SDH standards lies in the handling of some of the overhead bytes. Other details, like framing, and data payload mappings are equivalent in SONET and SDH. By default, PMC's S/UNI-POS powers up in SONET mode. However, it can be configured to operate in SDH mode.

The bit error rate (BER) monitoring requirements are also slightly different between Bellcore GR-253-CORE (SONET) and ITU.707 (SDH) An application note, PMC-950820, explains in detail the different parameters for the RASE block.

The table below shows the various register settings to configure the POS for either SONET or SDH mode

ISSUE 2

S/UNI-622-POS REFERENCE DESIGN

# Table 3: SONET vs. SDH Configuration

| Register/bits                     | SONET | SDH |

|-----------------------------------|-------|-----|

| SDH_J0/Z0 (0x01) <sup>1</sup>     | 0     | Х   |

| ENSS (0x3D) <sup>2</sup>          | 0     | 1   |

| LEN16(Path, 0x28) <sup>3</sup>    | 0     | 1   |

| LEN16(Section, 0x50) <sup>3</sup> | 0     | 1   |

| S[1:0] (0x46) <sup>4</sup>        | 00    | 10  |

Notes:

- 1) SONET requires Z0 bytes to be set to the number corresponding to the STS-1 column number. SDH considers those bits as reserved.

- 2) SDH specification requires the detection of SS bits to be "10"

- 3) SONET uses 64 bytes message/SDH uses 16 bytes message

- 4) SS is undefined for SONET but must be set to "10" for SDH

REFERENCE DESIGN PMC-1981070

S/UNI-622-POS REFERENCE DESIGN

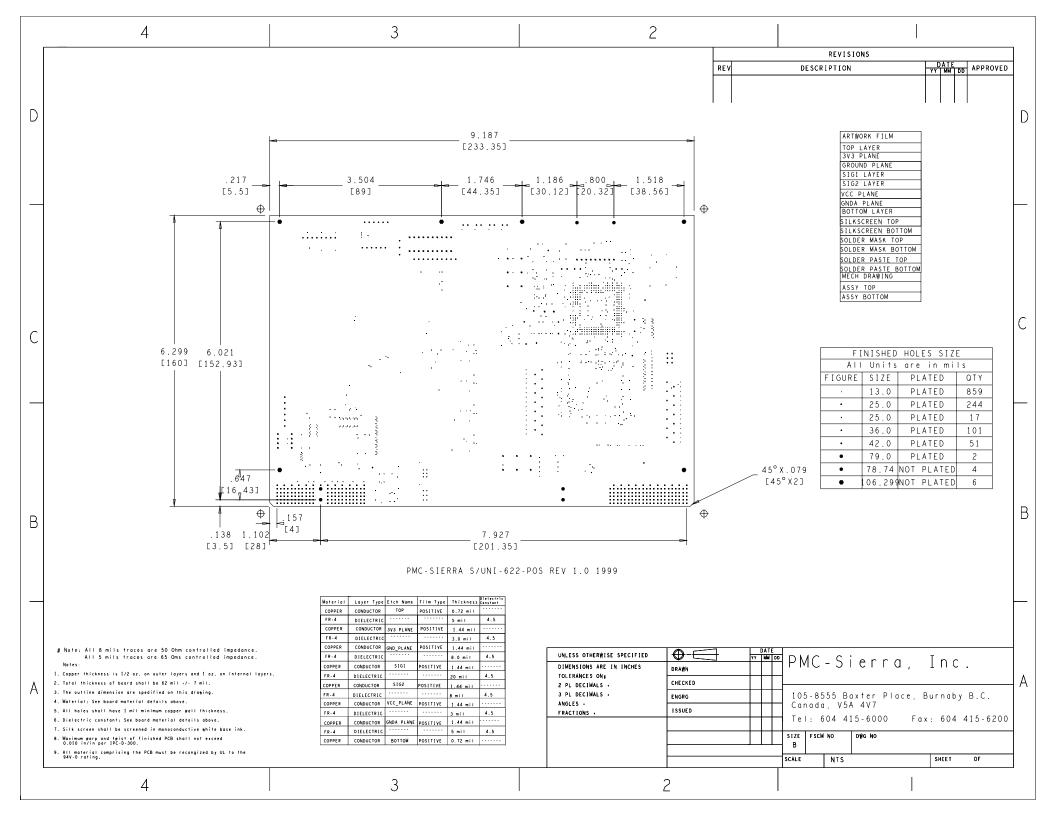

# 9 PCB CONSIDERATIONS

Because of the high speed 622MHz PECL differential drivers, and other fast edge signals such as the UTOPIA bus, this PCB requires careful layout. Typically the drivers for these have rise/fall times in excess of 1ns. High speed traces should be as short as possible, transmission lines are to be used where indicated and standard terminations must be incorporated to prevent signal reflections.

Standard FR-4 PCB material can be used for this application with as many layers as is required to derive the final board thickness, achieve enough layers for signal routing and attain the required trace impedance. Please refer to the first page of the artwork for more detail on the reference design PCB.

We chose the following stack up layers:

| Layer      | Location                          |

|------------|-----------------------------------|

| Тор        | Top Signal Layer , Component side |

| 3.3V PLANE | Power                             |

| GND_PLANE  | Ground                            |

| SIG1       | Signal Layer                      |

| SIG2       | Signal Layer                      |

| VCC_PLANE  | 5V Power Layer                    |

| GNDA_PLANE | Ground                            |

| воттом     | Bottom layer, Solder Side         |

#### Table 4: Reference Design PCB Stack Up

**ISSUE 2**

Although only one ground plane is required, two are used to attain the desired board thickness and correct trace impedance. A ground layer or a power plane can be used to achieve the desired signal transmission line trace impedance assuming there is adequate coupling between them.

The PECL 622MHz and 50 MHz traces are 50 ohms and they are 8 mil wide. The rest of the board is laid out with 5 mil and these are 65 ohm impedance.

| PRELIMINARY      | PMC PMC-Sierra, Inc. |

|------------------|----------------------|

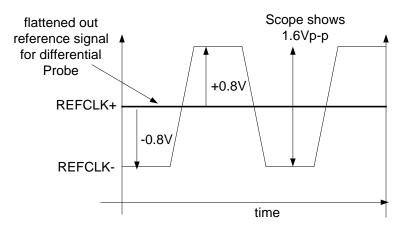

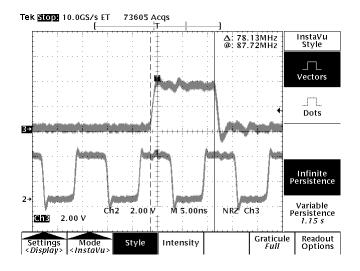

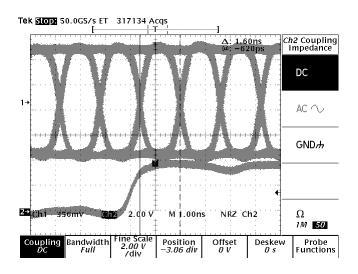

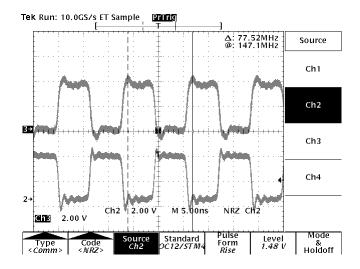

| REFERENCE DESIGN |                      |