# **PM73488**

# **QSE**

# **DATA SHEET Errata**

Released Issue 6: Feb. , 2002

## **Legal Information**

#### Copyright

© 2002 PMC-Sierra, Inc.

The information is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, you cannot reproduce any part of this document, in any form, without the express written consent of PMC-Sierra, Inc.

PMC-1980616 (P3)

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

QRT is a registered trademark of PMC-Sierra, Inc. PMC-Sierra is trademark of PMC-Sierra, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners.

#### **Patents**

The technology discussed is protected by one or more of the following Patents:

U.S. Patent No. 5,557,607; 5,570,348; 5,583,861; 6,151,301; 6,188,690B1

Relevant patent applications and other patents may also exist.

# **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: (604) 415-6000 Fax: (604) 415-6200

Document Information: document@pmc-sierra.com Corporate Information: info@pmc-sierra.com Technical Support: apps@pmc-sierra.com Web Site: <a href="http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

### **Revision History**

| Issue No. | Issue Date | Details of Change                                 |

|-----------|------------|---------------------------------------------------|

| 1         | Jan. 1999  | Creation of document                              |

| 2         | Apr. 1999  | Added errata items 1.1, 1.2, 1.4, 1.5             |

| 3         | June 1999  | Aligns with Issue 3 Production Release Data sheet |

| 4         | March 2000 | Reset timing signal is inverted in Figure 40.     |

| 5         | Sept. 2001 | Added patent award numbers                        |

| 6         | Feb. 2002  | Added errata items 2.5, 2.6 ,2.7 and 2.8          |

# **Table of Contents**

| Le | gal Inf                           | ormatio  | n                                            | 2  |

|----|-----------------------------------|----------|----------------------------------------------|----|

| Сс | ntacti                            | ng PMC   | S-Sierra                                     | 3  |

| Та | ble of                            | Content  | ts                                           | 4  |

| 1  | Intro                             | oduction | 1                                            | 5  |

|    | 1.1                               | Device   | e Identification                             | 5  |

|    | 1.2                               | Refere   | ences                                        | 5  |

| 2  | Doc                               | umenta   | ition Deficiency List                        | 6  |

|    | 2.1                               | Page     | 92                                           | 6  |

|    | 2.2                               | Page     | 109                                          | 6  |

|    | 2.3                               | Figure   | e 40. Inverted Reset Signal                  | 6  |

|    | 2.4                               | Page     | 2 - US Patents                               | 7  |

|    | 2.5                               | ESD S    | Specification                                | 7  |

|    | 2.6                               | Contra   | adictions on Cell Timing/Latency             | 7  |

|    | 2.7                               | CHIP_    | _MODE Register                               | 7  |

|    |                                   | 2.7.1    | Location                                     | 7  |

|    |                                   | 2.7.2    | Original Wording                             | 7  |

|    |                                   | 2.7.3    | Replacement Wording                          | 8  |

|    | 2.8                               | Typos    | on Ball Number of RAM_ADD(16) and RAM_PARITY | 9  |

| 3  | Device Functional Deficiency List |          | 10                                           |    |

|    | 3.1                               | Short    | Tag Feature Restriction                      | 10 |

#### 1 Introduction

In this document:

- Section 2 lists documentation errors found in Issue 3 of the QSE Data Sheet (PMC-1980616).

- Section3 lists the known functional errata for Revision B of the PM73488 QSE.

#### 1.1 Device Identification

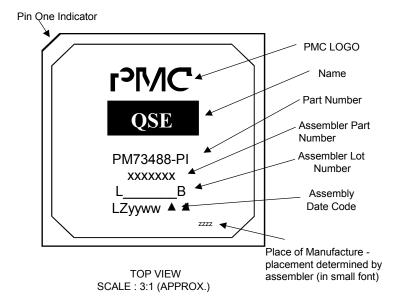

The information contained in Section 2 relates to Revision B of the PM73488 QSE only. The device revision code is marked at the end of the Wafer Batch Code on the face of the device.

Figure 1 PM73488 QSE Branding Format

#### 1.2 References

• Issue 3 of the QSE Data Sheet (PMC-1980616).

## 2 Documentation Deficiency List

This section lists the known documentation deficiencies for Issue 3 of the QSE Data Sheet (PMC-1980616) as of the publication date of this document.

For each *specific* deficiency, the location of the passage in question, the deficient text, and the replacement text are described. New text is shown in bold. Deleted text is shown as underlined.

For more *general* issues, a description of the nature of the error is given, along with a passage that correctly describes the concept or device function. Please report any documentation deficiencies not covered in this errata to PMC-Sierra.

#### 2.1 Page 92

Add to GANG DEAD ACK register description:

For example, if the gang size is 8, and 4 out of the 8 ports are dead/disabled, then a GANG\_DEAD\_NACK is returned if a cell is sent to any of the 4 dead ports, even though the whole gang (of 8) is not dead/disabled

#### 2.2 Page 109

Add to GANG DEAD NACK description:

For example, if the gang size is 8, and 4 out of the 8 ports are dead/disabled, then a GANG\_DEAD\_NACK is returned if a cell is sent to any of the 4 dead ports, even though the whole gang (of 8) is not dead/disabled.

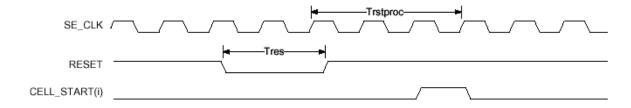

## 2.3 Figure 40. Inverted Reset Signal

The RESET signal shown in figure 40 of the data sheet (below) is defined as being asserted during the time period (Tres). Since the RESET pin on the QSE is defined as active high, the RESET signal in figure 40 is incorrect and should be inverted.

Figure 40 (Data sheet Issue 3). Reset Timing

#### 2.4 Page 2 - US Patents

The PM73488 is protected by the following patents:

US patent 5,557,607

US patent 5,570,348

US patent 5,583,861

US patent 6,151,301

US patent 6,188,690B1

#### 2.5 ESD Specification

There is no ESD specification in Table 22 (Absolute Maximum Ratings) under Section 7, Physical Characteristic, in the current QSE data sheet.

The qualification data indicates that the QSE meets ±500 V ESD.

### 2.6 Contradictions on Cell Timing/Latency

There are contradictions on cell timing and latency specification between Sections 3.9 and 4.2.2 in the QSE data sheet.

Section 3.9 Cell/Timing Latency mentions that in aggregate mode 1 the latency is 13 clock cycles. Section 4.2.2 Relation Between Local CELL\_START and Data Out of the QSE mentions that "The switch latency is 8 clocks from the local CELL\_START signal for all unicast gang modes, except for unicast gang mode = 0, in which case the switch latency is 11 clocks."

Section 3.9 is correct, and Section 4.2.2 is in error.

## 2.7 CHIP\_MODE Register

There is a typo in the bit description of the CHIP\_MODE register. The bit 1 is shown as Reserved in one place and as SWITCH\_MODE in another place. In fact, the bit 1 in this register should be a reserved bit defaulted to '0'. Therefore, the SWITCH\_MODE description should be ignored.

#### 2.7.1 Location

The bit 1 (SWITCH\_MODE) bit description is in the CHIP\_MODE register under Section 9.3.2 of the QSE data sheet.

#### 2.7.2 Original Wording

| Field (Bits)           | Description                                                                                                                      |

|------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| ENABLE_STAT_PIN<br>(7) | Enable StatOut and CtrlIn pin functionality StatOut behaves like No Data In, and Ctrl In behaves like No Data Out.               |

| PARITY_CHECK           | 1 Parity checks on cell header disabled.                                                                                         |

| (6)                    | 0 Normal operation.                                                                                                              |

| /NO_DATA_OUT           | Current value at the /NO_DATA_OUT pin.                                                                                           |

| (5)                    |                                                                                                                                  |

| /NO_DATA_IN<br>(4)     | Current value at the /NO_DATA_IN pin.                                                                                            |

| MULTICAST_MODE         | 1 External RAM present.                                                                                                          |

| (3)                    | 0 No external RAM.                                                                                                               |

| CHIP_HARDWARE_RESET    | Writing a one to this bit will put the chip is in hardware reset (except the                                                     |

| (2)                    | processor interface, which remains untouched).                                                                                   |

|                        | Writing a zero to this bit will take the chip out of hardware reset.                                                             |

|                        | Upon pin-reset, this bit comes up as a one. A zero must be explicitly written to this bit before the chip can function normally. |

| SWITCH_MODE            | 1 Double switch mode.                                                                                                            |

| (1)                    | 0 Single switch mode.                                                                                                            |

| Reserved               | Write with a 0 to maintain future software compatibility.                                                                        |

| (1:0)                  |                                                                                                                                  |

# 2.7.3 Replacement Wording

| Field (Bits)           | Description                                                                                                        |

|------------------------|--------------------------------------------------------------------------------------------------------------------|

| ENABLE_STAT_PIN<br>(7) | Enable StatOut and CtrlIn pin functionality StatOut behaves like No Data In, and Ctrl In behaves like No Data Out. |

| PARITY_CHECK           | 1 Parity checks on cell header disabled.                                                                           |

| (6)                    | 0 Normal operation.                                                                                                |

| /NO_DATA_OUT           | Current value at the /NO_DATA_OUT pin.                                                                             |

| (5)                    |                                                                                                                    |

| /NO_DATA_IN<br>(4)     | Current value at the /NO_DATA_IN pin.                                                                              |

| MULTICAST_MODE         | 1 External RAM present.                                                                                            |

| (3)                    | 0 No external RAM.                                                                                                 |

| CHIP_HARDWARE_RESET    | 1 Writing a one to this bit will put the chip is in hardware reset (except the                                     |

| (2)                    | processor interface, which remains untouched).                                                                     |

|                        | Writing a zero to this bit will take the chip out of hardware reset.                                               |

|                | Upon pin-reset, this bit comes up as a one. A zero must be explicitly written to this bit before the chip can function normally. |

|----------------|----------------------------------------------------------------------------------------------------------------------------------|

| Reserved (1:0) | Write with a 0 to maintain future software compatibility.                                                                        |

## 2.8 Typos on Ball Number of RAM\_ADD(16) and RAM\_PARITY

There are typos on ball number of RAM\_ADD(16) and RAM\_PARITY pins in Table 17 in the QSE data sheet.

Table 17 in Section 6.4.2 shows that the ball number for the RAM\_ADD(16) pin is F18 and for the RAM\_PARITY pin is F19. This is not correct.

The correct ball number for RAM\_ADD(16) pin is F19 and for the RAM\_PARITY pin is F18 as shown in Table 14 in Section 6.2 and in Table 15 in Section 6.3.

# 3 Device Functional Deficiency List

This section lists the known functional deficiencies for Revision B of the QSE as of the publication date of this document. For each deficiency, the known workaround and the operating constraints, with and without the workaround, are also described.

Please report any functional deficiencies not covered in this errata to PMC-Sierra.

#### 3.1 Short Tag Feature Restriction

This does not apply to cases when the QRT is used in conjunction with the QSE. Short Tags should only be used when the QSE is used with a device other than the QRT.

In the case where the QSE is used with a device other than the QRT, the SHORT\_TAG\_ENABLE (pg. 97 in 9.3.7 Extended Chip mode) can only be used if Unicast Gang Mode (9.3.25 on pg. 105) is NOT 0.

Proprietary and Confidential to PMC-Sierra, Inc., and for its Customers' Internal Use Document ID: PMC-1981490, Issue 6

#### **Notes**