**ISSUE 3**

PMC-2001646

Digital Correction Signal Processor

# **PM7800**

# **PALADIN-10**

# **Digital Correction Signal Processor**

# **Data Sheet**

PROPRIETARY AND CONFIDENTIAL

Released

Issue 3: July, 2001

Digital Correction Signal Processor

# **PUBLIC REVISION HISTORY**

ISSUE 3

| Issue No. | Issue Date    | ECN<br>Number | Details of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------|---------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Issue 1   | January, 2001 | N/A           | Document created.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Issue 2   | March, 2001   | N/A           | Modified voltage tolerances for VDD and VDDI.  Modified CPUMODE2 connection (tied to VDD rather than GND).  Minor editorial changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Issue 3   | July, 2001    | N/A           | <ul> <li>Removed I2C references throughout to reflect the fact that I2C is not supported.</li> <li>Changed Figure 3-1 on page 7: changed GND to VSS and VCC to VDD to match labels used in pin descriptions.</li> <li>Text edits in Section 5.1 on page 16.</li> <li>Modified procedure for Programming the WAIT_N Register (Section 5.1.2 on page 23).</li> <li>Inserted text and diagram regarding relative timing of SPI inputs in Section 5.3 on page 26.</li> <li>Added section (Section 5.4.2 on page 31) describing bug affecting Power_Attenuator_Delay and Power_Correction_Delay circuits. Modified Figure 5-25 on page 33 to reflect this issue.</li> <li>Revision number incremented to 1; i.e., rev_code changed to 178000CD. Affects Section 5.6 on page 34 and Table 6-3 on page 41.</li> <li>Changed VT+ and VT- values to 2.2V min and 0.8V max, respectively, in DC Characteristics. Also, changed VTH to 0.87V typ.</li> <li>IIH text edit in Table 8-1 on page 51.</li> <li>added IDDOP (VDDI) and IDDOP (VDDO) in DC Characteristics.</li> <li>Changed notes at start of AC Timing.</li> <li>Removed Relative Timing Diagrams and table for serial interface in AC Timing.</li> <li>Changed min/max loading from 0/40pF to 15/30pF on toe, tdp, toz, and trp, in Table 9-2 on page 54; toe, in Table 9-3 on page 55; and toe, top, and toz in Table 9-7 on page 59.</li> </ul> |

Digital Correction Signal Processor

# **CONTENTS**

| Lis | t of Ta           | ables                                                                                                                                                                                       | iii                              |

|-----|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Lis | t of Fi           | gures                                                                                                                                                                                       | iv                               |

| 1   | 1.1<br>1.2<br>1.3 | duction Definitions PALADIN Technologies PALADIN-10 1.3.1 System Diagram 1.3.2 Signal Flow PM7800 DCSP 1.4.1 Features 1.4.2 Interfaces 1.4.3 Applications 1.4.4 References                  | 1<br>2<br>3<br>4<br>4<br>4       |

| 2   | Block             | k Diagram                                                                                                                                                                                   | 6                                |

| 3   | Pin D             | Diagram                                                                                                                                                                                     | 6                                |

| 4   | Pin D             | Description                                                                                                                                                                                 | 8                                |

| 5   | 5.1               | tional Description  CPU Interface  5.1.1 Functional Timing  5.1.2 Programming the WAIT_N Register  Data Interfaces  5.2.1 VREF Interface and FIFO  5.2.2 VOBS Interface  5.2.3 VD Interface | 16<br>18<br>23<br>24<br>24<br>25 |

|     | 5.3               | 5.2.4 Dual-Clock System 5.2.5 Single-Clock System Serial Interface 5.3.1 Serial Operation Hop Generation 5.4.1 Power and Carrier Values and Hop                                             | 25                               |

|     |                   | 5.4.2 Bug that affects Power_Attenuator_Delay and Power_Correction_Delay .  GPIO Pins                                                                                                       | 31 32 33                         |

| 6   | 6.1               | JTAG Test Access Port  Features Full Scan RAMBIST                                                                                                                                           | 36                               |

ISSUE 3 Digital Correction Signal Processor

|    | 6.3  | OE_N Pin                              | 38 |

|----|------|---------------------------------------|----|

|    | 6.4  | JTAG Boundary Scan, IEEE 1149.1       |    |

|    |      | 6.4.1 TAP Controller                  |    |

|    |      | 6.4.2 Registers                       |    |

|    |      |                                       |    |

|    |      |                                       |    |

|    |      |                                       |    |

|    |      | · · · · · · · · · · · · · · · · · · · |    |

|    |      | 6.4.4 Boundary Scan Cells             |    |

|    |      |                                       |    |

| 7  | A 1  |                                       |    |

| 7  | Absc | olute Maximum Ratings                 |    |

| 8  | DC 0 | Characteristics                       | 51 |

| 9  | AC 7 | Timing                                | 53 |

|    | 9.1  | RESET_N                               |    |

|    | 9.2  | CPU Interface                         |    |

|    | 9.3  | VREF, VOBS, VD Interfaces             |    |

|    |      | 9.3.1 Dual-Clock System               |    |

|    |      | <del>-</del>                          |    |

|    | 9.4  | Serial Interface                      |    |

|    |      |                                       |    |

|    | 9.5  | <del>_</del>                          |    |

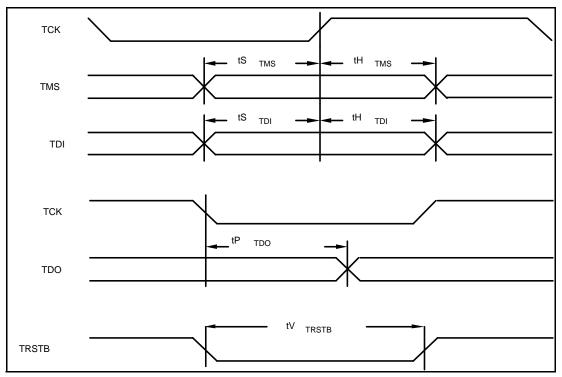

|    | 9.6  | JTAG Interface                        | 60 |

| 10 | Ther | rmal                                  | 61 |

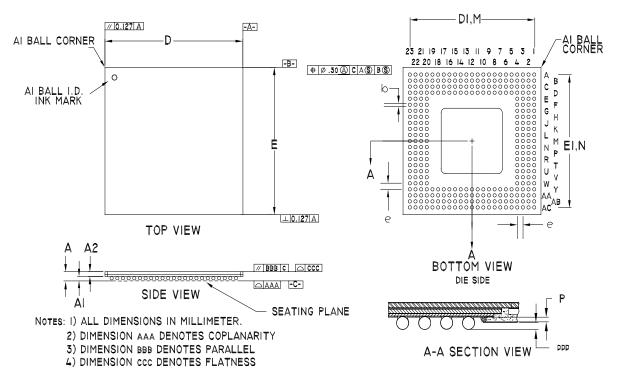

| 11 | Med  | Phanical                              | 62 |

PM7800 PALADIN-10

PMC-2001646

ISSUE 3

Digital Correction Signal Processor

# **LIST OF TABLES**

| Table 1-1 | Definitions                                          | 1  |

|-----------|------------------------------------------------------|----|

| Table 4-1 | Pin Description and Cell Types                       | 8  |

| Table 5-1 | Connection to C54xx Processor                        |    |

| Table 5-2 | Functional Timing for WAIT_N                         | 23 |

| Table 5-3 | Programming the WAIT_N Register                      | 23 |

| Table 6-1 | Full-Scan Interface                                  | 36 |

| Table 6-2 | Instruction Register                                 | 41 |

| Table 6-3 | Identification Register                              | 41 |

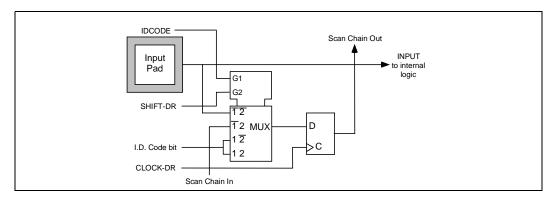

| Table 6-4 | Input Observation Cell (IN_CELL)                     | 47 |

| Table 7-1 | Absolute Maximum Ratings                             | 50 |

| Table 8-1 | D.C.Characteristics                                  | 51 |

| Table 9-1 | RESET_N                                              | 53 |

| Table 9-2 | CPU Interface - DCLK Timing                          | 54 |

| Table 9-3 | CPU Interface - CPUCLK Timing                        | 55 |

| Table 9-4 | Dual-Clock System timing                             | 56 |

| Table 9-5 | Single-Clock System timing                           |    |

| Table 9-6 | AC Timing for Serial Inputs (SCLK, SCS_N, SD, HOP_N) |    |

| Table 9-7 | GPIO                                                 |    |

| Table 9-8 | JTAG Interface                                       |    |

|           |                                                      |    |

Release Digital Correction Signal Processor Data Sheet

PMC-2001646

ISSUE 3

Digital Correction Signal Processor

# **LIST OF FIGURES**

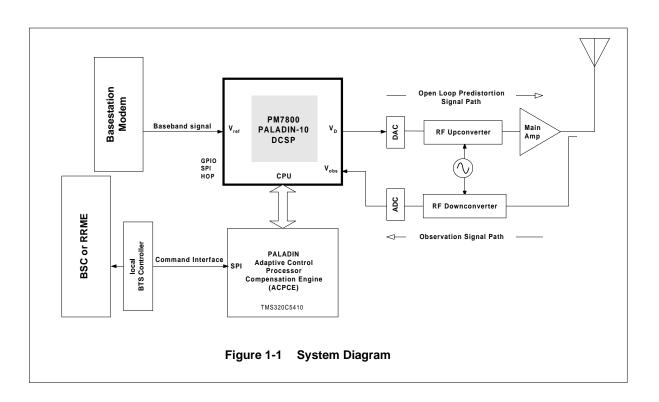

| Figure 1-1  | System Diagram                                                               | 3  |

|-------------|------------------------------------------------------------------------------|----|

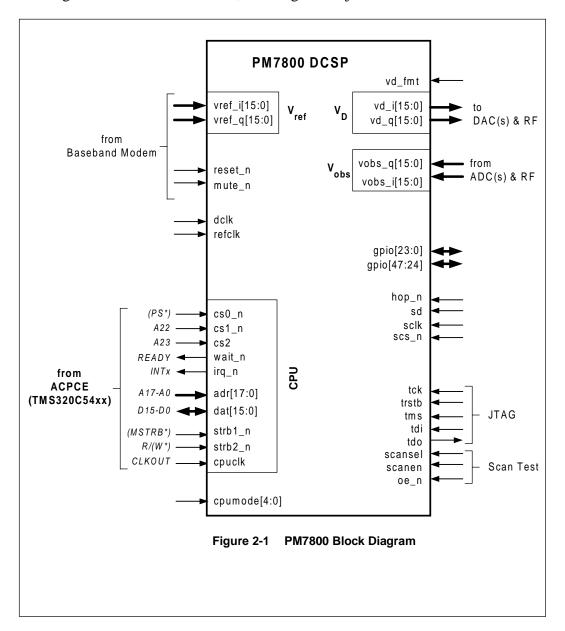

| Figure 2-1  | PM7800 Block Diagram                                                         |    |

| Figure 3-1  | Pin Diagram (Bottom View)                                                    | 7  |

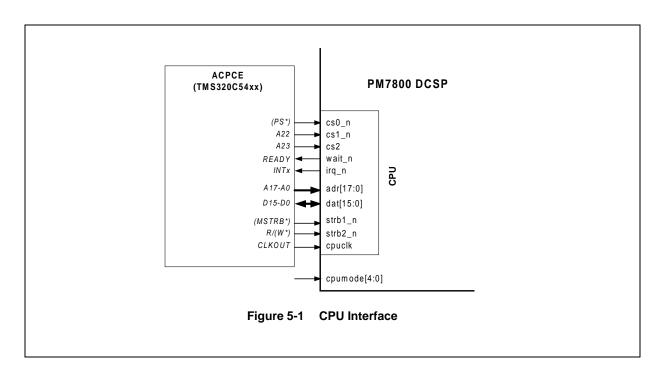

| Figure 5-1  | CPU Interface                                                                | 16 |

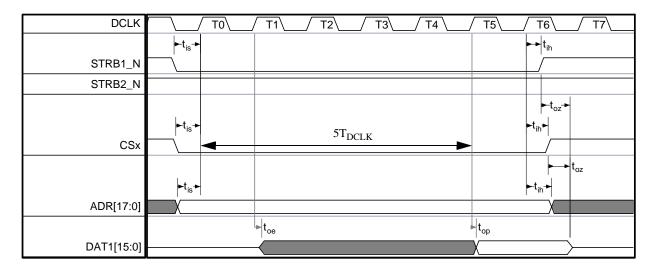

| Figure 5-2  | Read Cycle (CPUMODE0 = 0)                                                    | 19 |

| Figure 5-3  | Read Cycle (CPUMODE0 = 1)                                                    |    |

| Figure 5-4  | Back-to-Back Read Cycles (CPUMODE0 = 0)                                      |    |

| Figure 5-5  | Back-to-Back Read Cycles (CPUMODE0 = 1)                                      | 20 |

| Figure 5-6  | Back-to-Back Write Cycles (CPUMODE0 = 0)                                     | 21 |

| Figure 5-7  | Back-to-Back Write Cycles (CPUMODE0 = 1)                                     | 21 |

| Figure 5-8  | WAIT_N Timing - Reads (CPUMODE0 = 0)                                         | 22 |

| Figure 5-9  | WAIT_N Timing - Reads (CPUMODE0 = 1)                                         | 22 |

| Figure 5-10 | WAIT_N Timing - Writes (CPUMODE0 = 0)                                        | 22 |

| Figure 5-11 | WAIT_N Timing - Writes (CPUMODE0 = 1)                                        | 23 |

| Figure 5-12 | Data Interfaces                                                              |    |

| Figure 5-13 | Dual-Clock System timing                                                     |    |

| Figure 5-14 | Single-Clock System timing                                                   | 26 |

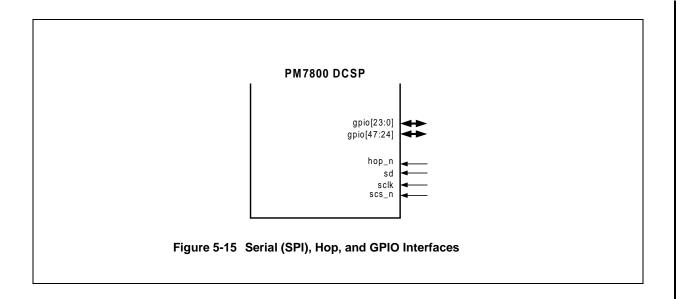

| Figure 5-15 | Serial (SPI), Hop, and GPIO Interfaces                                       |    |

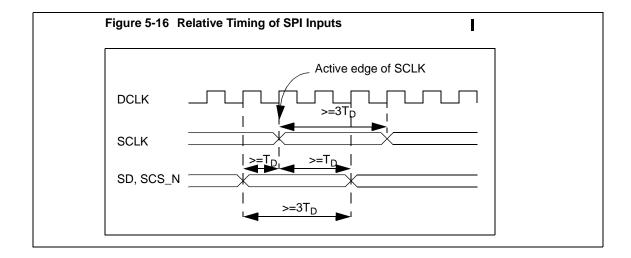

| Figure 5-16 | Relative Timing of SPI Inputs                                                | 27 |

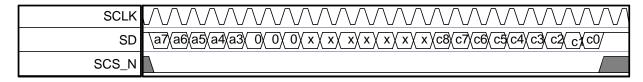

| Figure 5-17 | SPI carrier_stream (spi_clock_polarity = 0, falling edge of SCLK is active)  | 28 |

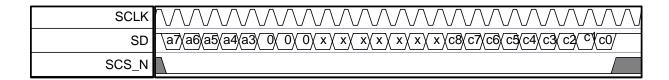

| Figure 5-18 | SPI carrier_stream (spi_clock_polarity = 1, rising edge of SCLK is active) . |    |

| Figure 5-19 | SPI power_stream (spi_clock_polarity = 0, falling edge of SCLK is active).   | 28 |

| Figure 5-20 | SPI power_stream (spi_clock_polarity = 1, rising edge of SCLK is active) .   | 28 |

| Figure 5-21 | SPI word_stream (spi_clock_polarity = 0, falling edge of SCLK is active) .   | 29 |

| Figure 5-22 | SPI word_stream (spi_clock_polarity = 1, rising edge of SCLK is active)      | 29 |

| Figure 5-23 | SPI hop_stream (spi_clock_polarity = 0, falling edge of SCLK is active)      | 29 |

| Figure 5-24 | SPI hop_stream (spi_clock_polarity = 1, rising edge of SCLK is active)       | 30 |

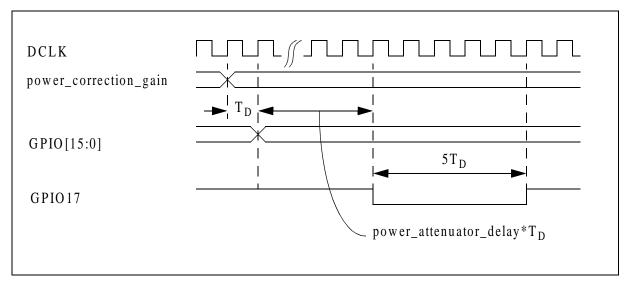

| Figure 5-25 | Power Attenuator Outputs - shown with active-low pulse on GPIO17             | 33 |

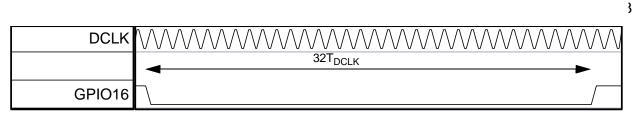

| Figure 5-26 | Watchdog Timer Output                                                        | 33 |

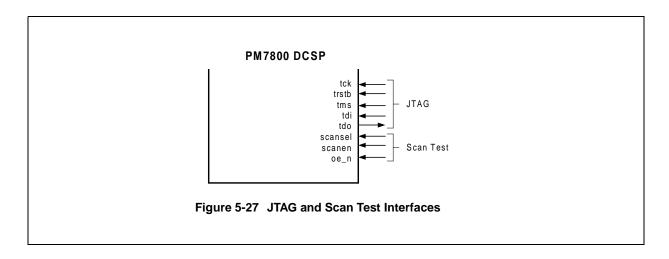

| Figure 5-27 | JTAG and Scan Test Interfaces                                                | 34 |

| Figure 6-1  | Boundary-Scan Architecture                                                   | 38 |

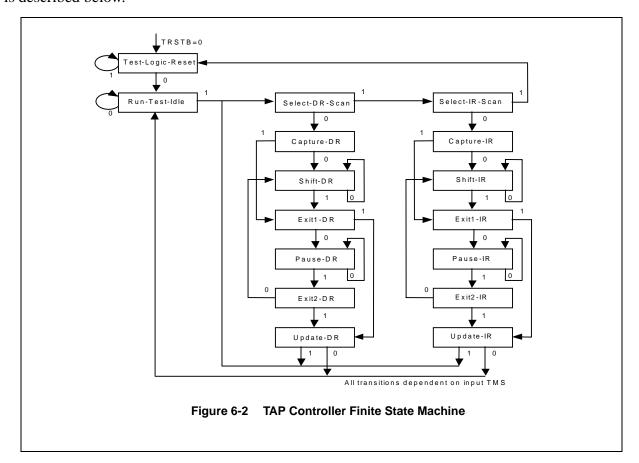

| Figure 6-2  | TAP Controller Finite State Machine                                          | 39 |

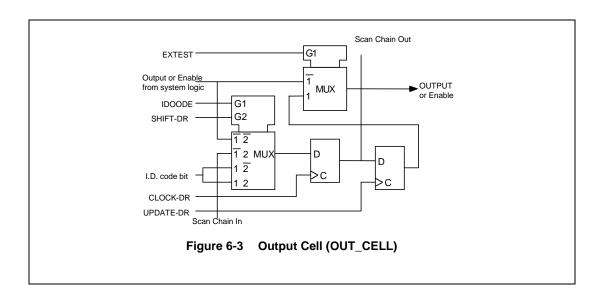

| Figure 6-3  | Output Cell (OUT_CELL)                                                       | 48 |

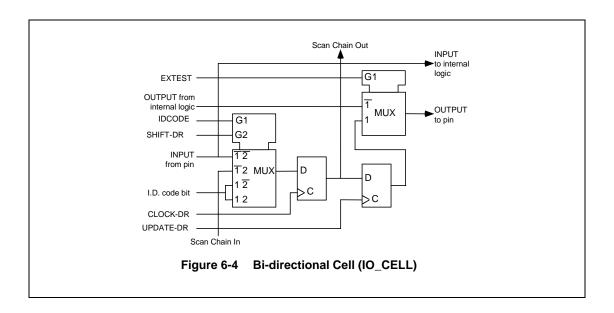

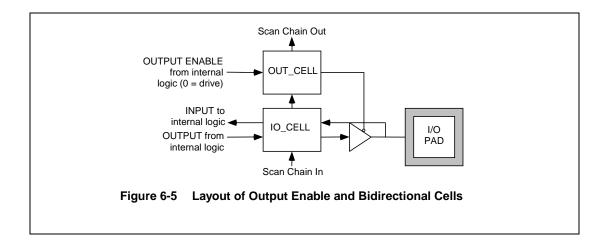

| Figure 6-4  | Bi-directional Cell (IO_CELL)                                                | 48 |

| Figure 6-5  | Layout of Output Enable and Bidirectional Cells                              | 49 |

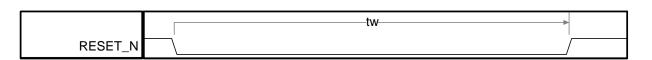

| Figure 9-1  | RESET_N                                                                      |    |

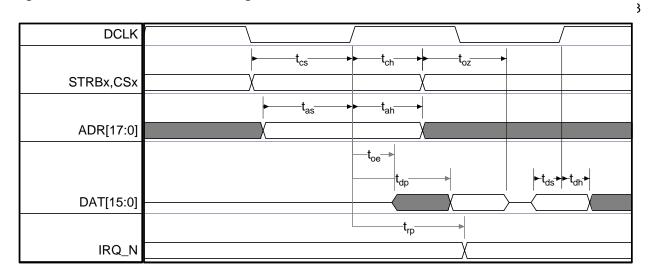

| Figure 9-2  | CPU Interface - DCLK Timing                                                  | 54 |

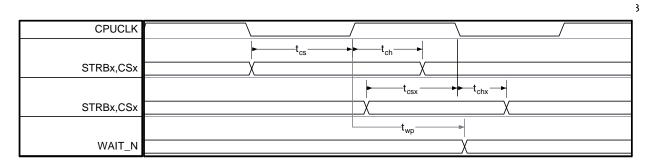

| Figure 9-3  | CPU Interface - CPUCLK Timing                                                | 55 |

| Figure 9-4  | Dual-Clock System timing                                                     | 56 |

| Figure 9-5  | Single-Clock System timing                                                   | 57 |

| Figure 9-6  | AC Timing for Serial Inputs (SCLK, SCS_N, SD, HOP_N)                         | 58 |

| Figure 9-7  | GPIO                                                                         | 59 |

|             |                                                                              |    |

Release Digital Correction Signal Processor Data Sheet

PM7800 PALADIN-10

| Data Sneet  |                |                                    |

|-------------|----------------|------------------------------------|

| PMC-2001646 | ISSUE 3        | Digital Correction Signal Processo |

| Figure 9-8  | JTAG Interface | 60                                 |

Release Digital Correction Signal Processor Data Sheet PMC-Sierra, Inc.

PM7800 PALADIN-10

PMC-2001646

ISSUE 3

Digital Correction Signal Processor

Digital Correction Signal Processor

# 1 Introduction

This document describes the features, functionality, and physical characteristics of the PM7800 Digital Correction Signal Processor, which forms part of the PALADIN-10 system.

# 1.1 Definitions

The following table defines the terms and abbreviations used in this data sheet.

ISSUE 3

**Definitions** Table 1-1

| Abbreviation | Definition                                                                                             |  |  |  |

|--------------|--------------------------------------------------------------------------------------------------------|--|--|--|

| ACPCE        | Adaptive Control Processing Compensation Engine                                                        |  |  |  |

| ADC          | Analog to Digital Converter                                                                            |  |  |  |

| AQM          | Analog Quadrature Modulator                                                                            |  |  |  |

| BGA          | Super Ball Grid Array, the type of package used by this chip                                           |  |  |  |

| BIST         | Built-In Self-Test                                                                                     |  |  |  |

| BTS          | Base Transceiver Station (Node B in WCDMA)                                                             |  |  |  |

| CMOS         | Complementary Metal Oxide Semiconductor                                                                |  |  |  |

| CPU          | Central Processing Unit - in this context, the CPU is the ACPCE and the terms are used interchangeably |  |  |  |

| DAC          | Digital to Analog Converter                                                                            |  |  |  |

| DCSP         | Digital Correction Signal Processor                                                                    |  |  |  |

| DQM          | Digital Quadrature Modulator                                                                           |  |  |  |

| DSP          | Digital-Signal Processor                                                                               |  |  |  |

| EDGE         | Enhanced Data Rates for GSM Evolution - 3rd generation GSM (Global System for Mobile Communications)   |  |  |  |

| FIFO         | First-In, First-Out - a queuing mechanism                                                              |  |  |  |

| GPIO         | General-Purpose Input-Output pin                                                                       |  |  |  |

| GSM          | Global System for Mobile Communications                                                                |  |  |  |

| NC           | No Connect, indicates an unused pin                                                                    |  |  |  |

| RAM          | Random-Access Memory                                                                                   |  |  |  |

| RRME         | Radio Resource Management Entity                                                                       |  |  |  |

| WCDMA        | Wideband Code Division Multiple Access                                                                 |  |  |  |

Digital Correction Signal Processor

# 1.2 PALADIN Technologies

PALADIN is a family of distortion elimination chip technologies that enables the development of higher performance, higher efficiency 2G and 3G base stations that utilize fewer and less expensive components. Based on proprietary Digital Signal Processing (DSP) architectures and techniques, PALADIN products feature:

- Digital Adaptive Predistortion for wideband amplifier linearization;

- Digital Correction for Analog Quadrature Modulation (AQM) distortion; and

- Constant-Gain Mode to facilitate operation at higher efficiency.

ISSUE 3

Emerging 3G wireless services require high capacity radio networks to deliver the high volume multi-media data traffic that is central to the new "wireless internet" paradigm. High spectral efficiency, the ability to maximize the data-carrying capacity of a limited amount of licensed spectrum, will be key to the success of 3G radio networks. However, spectral efficiency is fundamentally limited by distortion in the analog transmitter and power amplifier components of the Base Transceiver Station (BTS).

PALADIN products eliminate distortion in the transmitter chain and power amplifier using fully digital methods, permitting designers to replace many expensive and difficult to manufacture analog IF and RF sub-systems, components which are often required to control distortion and aggregate signals in many existing BTS designs.

In particular, PALADIN can transform an inexpensive, simple, narrow-band Class AB power amplifier into a wide-band, multi-carrier capable, high efficiency, digitally controlled amplifier unit which can replace the expensive, low efficiency, feedforward-based multi-carrier power amplifiers (MCPA) commonly used in many current 3G BTS designs. Furthermore, PALADIN opens the door to the development of new BTS architectures that could feature "standard sockets" for multiple air interfaces, multiple transmitter/amplifier "hot swap" redundancy, multiple amplifier efficiency management, and smart antenna transceivers.

## **1.3 PALADIN-10**

PALADIN-10 is a wideband transceiver linearizer and distortion elimination chip solution for multi-carrier high power radio transmitter applications. Based on high speed digital signal processing (DSP), PALADIN-10 provides digital adaptive predistortion and preconditioning for complex modulation signals with instantaneous bandwidths up to 10MHz. PALADIN-10 consists of (1) the PM7800 Digital Correction Signal Processor (DCSP) chip and (2) the Adaptive Control Processor Compensation Engine (APCE) running on an industry-standard programmable DSP<sup>1</sup>.

ISSUE 3

PMC-2001646

Digital Correction Signal Processor

# 1.3.1 System Diagram

Figure 1-1 shows a simplified system diagram of PALADIN-10 operating in the transmitter chain of a typical multi-carrier base transceiver subsystem (BTS).

The PM7800 DCSP chip, also called the PALADIN predistortion kernel, is responsible for all the real-time operations on the complex modulation baseband signal, from the base station modem, that predistort and precondition it such that the modified signal at the main or power amplifier (PA) will cancel out the distortions due to non-linearities in the PA and transmitter chain. The PM7800 DCSP chip supports all 3G and 2G air interfaces, including WCDMA, cdma2000 and IS-95, and GSM/EDGE. The PM7800 DCSP chip is the very high speed "hardware" digital signal processor component of the PALADIN-10 system.

The PALADIN ACPCE, also called the PALADIN predistortion firmware, is responsible for carrying out all the nonreal-time complex computations necessary to generate predictive parameters used inside the PM7800 DCSP. The PALADIN ACPCE is also responsible for control functions and acts as the Master, taking commands from the base station controller (BSC) or some radio resource management entity (RRME) and controlling the operation and functioning of the PM7800 DCSP chip. The ACPCE runs on an external programmable DSP processor chip (TMS320C5410), also referred to as the CPU. The ACPCE is fully software upgradeable via a

PM7800 PALADIN-10

PMC-2001646

Digital Correction Signal Processor

serial interface from the BSC or RRME. The current version of the ACPCE supports the WCDMA air interface standard only. Versions supporting the other 2G and 3G air standards will be provided as software updates. The PALADIN-10 ACPCE is the highly complex adaptive "software" digital signal processor component of the PALADIN-10 system.

## 1.3.2 Signal Flow

The signal flow through the PALADIN-10 system is as follows:

ISSUE 3

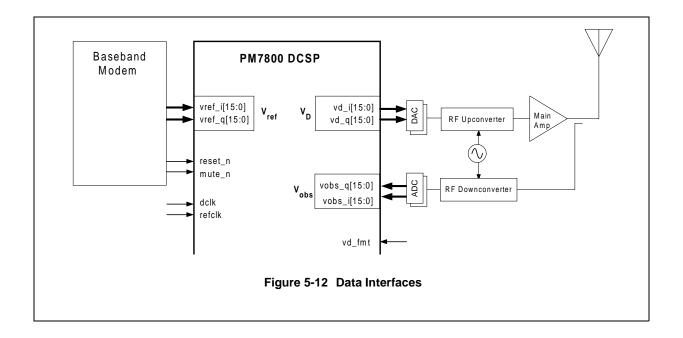

In the forward direction, the composite (digitally combined single or multi-carrier complex baseband) signal from the base station modem enters the PM7800 through the  $V_{ref}$  port, where it is interpolated to the correct rate, predistorted by the Digital Correction Signal (DCSP) Processor core using parameters provided by the Adaptive Control Processor Compensation Engine (ACPCE), and exits through the  $V_D$  port. The predistorted signal output at the  $V_D$  port is converted to analog, up-converted, amplified, and applied to the antenna. This is called the open-loop predistortion signal path, which is sometimes referred to as the transmit path or upconversion path.

In the reverse direction, a small portion of the amplified signal is downconverted, re-sampled and re-digitized, and enters the PM7800 through the  $V_{\rm obs}$  port. This is called the observation or sampling signal path, and is sometimes referred to as the downconversion path. The PM7800 concurrently captures the baseband signal ( $V_{\rm ref}$ ) and observed signal ( $V_{\rm obs}$ ) for analysis by the Adaptive Control Processor Compensation Engine (running on a TMS320C5410 DSP). The CPU analyzes the captured data to monitor system performance, and adjusts the internal parameters of the PM7800 DCSP accordingly.

### 1.4 PM7800 DCSP

The PM7800 DCSP chip is the very high speed "hardware" digital signal processor component of the PALADIN-10 system. The remainder of this document describes the PM7800 DCSP chip only.

The ACPCE is described in a companion document: PMC-2002272, "PALADIN-10/PALADIN-15 ACPCE Firmware User Manual."

### 1.4.1 Features

- predistortion kernel for linearization of power-amplifiers in wireless base-stations

- up to 80MHz data-rate

- interpolated up-conversion (1:N, where 1<=N<=10) of baseband input to the data-rate

- generic 16-bit microprocessor bus interface for configuration, control, and monitoring

- SPI serial interface for update of power and carrier values

- 48 general-purpose IO pins, eight of which are edge-triggered interrupt sources

- standard five-signal IEEE 1149.1 JTAG test port for boundary scan board test purposes

- low-power 1.8V CMOS core logic with 3.3V CMOS/TTL compatible digital inputs and digital outputs

- Industrial temperature range (-40C to +85C)

Digital Correction Signal Processor

### 1.4.2 Interfaces

The major interfaces to the PM7800 DCSP include:

• Baseband interface to the base station modem (V<sub>ref</sub>)

ISSUE 3

- Digital IF or Digital Baseband interface to DAC(s) and RF Upconverter (V<sub>D</sub>)

- Digital IF or Digital Baseband interface from ADC(s) and RF Downconverter (V<sub>obs</sub>)

- GPIO and Serial (SPI) interface for auxiliary monitor and control

- CPU interface to ACPCE processor (external C54xx DSP)

Note: The command interface to the BSC or RRME is through an SPI (serial) interface on the CPU (TMS320C5410). The command interface is separately detailed in the companion document: PMC-2002272, "PALADIN-10/PALADIN-15 ACPCE Firmware User Manual."

## 1.4.3 Applications

- WCDMA Base Transceiver Subsystems (BTS)

- CDMA2000 BTS (requires firmware upgrade)

- GSM/TDMA/EDGE BTS (requires firmware upgrade)

# 1.4.4 References

- 1. TMS320VC5410 Fixed-Point Digital Signal Processor (Texas Instruments)

- 2. Section 8: Synchronous Serial Peripheral Interface, M68HC11 Reference Manual (Motorola)

- 3. PMC-2002272, "PALADIN-10/PALADIN-15 ACPCE Firmware User Manual."

Digital Correction Signal Processor

# 2 Block Diagram

A block diagram of the PM7800 DCSP, showing the major interfaces is shown below as:

ISSUE 3

# 3 Pin Diagram

The PM7800 is packaged in a 304-pin SBGA with a body size of 31mm x 31mm. The following pin diagram shows the pinout from the ball-side of the package. Note that, for readability, the aspect ratio of the diagram has been changed.

VDD

ISSUE 3 Digital Correction Signal Processor PMC-2001646

VSS SCS\_N က VREF\_I9 HOP\_N VDD VDD VDD VDD SD VDDI 2 VDD VSS 70BS\_Q6 VSS œ 0 VDDI 12 VSS 14 ADR12 15 VDD 9 | TCK VSS ADR 5 ADR 8 Pin Diagram (Bottom View) TDI 18 VDD VSS 19 VD\_02 20 00\_dv VDD VDD VDD VDD 21 VD\_04 80 VSS VSS NC Figure : VDDI VDD 23 VDD VSS VSS VSS VSS VSS

<del>۲</del>

ISSUE 3

PMC-2001646

Digital Correction Signal Processor

# 4 Pin Description

#### **Pin Description and Cell Types** Table 4-1

| Pin Name         | Туре               | Pin#                                                                                                                                              | Default | Functional Description                                                                                                                                                                                                                                                                                                         |  |

|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPU Interface (4 | CPU Interface (47) |                                                                                                                                                   |         |                                                                                                                                                                                                                                                                                                                                |  |

| STRB1_N          | I                  | AB12                                                                                                                                              | Hi-Z    | This signal is either used as an access strobe or as a write strobe, depending on the setting of the CPUMODE0 pin. If the CPUMODE0 pin is connected to VSS, this signal is treated as an access strobe, if the CPUMODE0 pin is connected to VDD, then this strobe is treated as a WRITE_N strobe.                              |  |

| STRB2_N          | I                  | AA12                                                                                                                                              | Hi-Z    | This signal is either used as an Read/Write_N cycle type indication or as a read strobe, depending on the setting of the CPUMODE0 pin. If the CPUMODE0 pin is connected to VSS, this signal is treated as an Read/Write_N indication, if the CPUMODE0 pin is connected to VDD, then this strobe is treated as a READ_N strobe. |  |

| CS0_N            | 1                  | AB13                                                                                                                                              | Hi-Z    | This signal is an active-low chip select. All three chip selects must be asserted for the chip to be accessed.                                                                                                                                                                                                                 |  |

| CS1_N            | I                  | AA13                                                                                                                                              | Hi-Z    | This signal is an active-low chip select. All three chip selects must be asserted for the chip to be accessed.                                                                                                                                                                                                                 |  |

| CS2              | I                  | Y13                                                                                                                                               | Hi-Z    | This signal is an active-high chip select. All three chip selects must be asserted for the chip to be accessed.                                                                                                                                                                                                                |  |

| ADR[17:0]        | I                  | Y14,<br>AA14,<br>AB14,<br>AA15,<br>AC15,<br>Y16,<br>AA16,<br>AB16,<br>Y17,<br>AA17,<br>AB17,<br>AC17,<br>AA18,<br>AB18,<br>AB19,<br>AA19,<br>AC20 | Hi-Z    | This is the eighteen-bit word-address bus. The bus addresses 256k 16-bit words (512Kbytes) in the PM7800.                                                                                                                                                                                                                      |  |

ISSUE 3

Digital Correction Signal Processor

| Pin Name          | Туре                 | Pin#                                                                                                          | Default        | Functional Description                                                                                                                                                                                                                                                               |

|-------------------|----------------------|---------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAT[15:0]         | IO                   | AB6,<br>Y7,<br>AA7,<br>AB7,<br>AC7,<br>Y8,<br>AA8,<br>AB9,<br>Y10,<br>AA10,<br>AB10,<br>AC10,<br>Y11,<br>AA11 | Hi-Z           | This is the 16-bit data bus.                                                                                                                                                                                                                                                         |

| WAIT_N            | 0                    | AC11                                                                                                          | Output<br>High | This is the external wait signal, required when DCLK on the PM7800 is slow. This output has programmable timing. See <i>Programming the WAIT_N Register</i> section 5.1.2.                                                                                                           |

| IRQ_N             | 0                    | AB11                                                                                                          | Output<br>High | This is an active-low interrupt request pin.                                                                                                                                                                                                                                         |

| CPUCLK            | I                    | AC13                                                                                                          | Hi-Z           | CPU Clock Input. This is a Schmitt-trigger input.                                                                                                                                                                                                                                    |

| CPUMODE0          | I                    | Y3                                                                                                            | Hi-Z           | This pin configures the strobe-signalling mode of the PM7800. When this pin is connected to VSS, access strobe and R/W# indication signalling is used. When this pin is connected to VDD, read strobe and write strobe signaling is used. See <i>CPU Interface</i> section 5.1.      |

| CPUMODE1          | I                    | AA4                                                                                                           | Hi-Z           | If this pin is connected to VDD, the WAIT circuit deactivates the internal version of the CPU write strobe for a programmable number of CPUCLK cycles. See CPU Interface section 5.1.                                                                                                |

| CPUMODE2          | I                    | AB4                                                                                                           | Hi-Z           | This input is reserved and must be connected to VDD.                                                                                                                                                                                                                                 |

| CPUMODE3          | I                    | AA20                                                                                                          | Hi-Z           | This pin, when connected to VDD, selects a mode of operation that can be used to support processors, e.g. ARM, that require the read strobe to be sampled on the falling edge of CPUCLK and the write strobe to be sampled on the rising edge. See <i>CPU Interface</i> section 5.1. |

| CPUMODE4          | I                    | Y21                                                                                                           | Hi-Z           | This pin, when connected to VDD, enables additional delay on the WAIT_N output to provide more hold time. See CPU Interface section 5.1.                                                                                                                                             |

| Data Interfaces ( | Data Interfaces (98) |                                                                                                               |                |                                                                                                                                                                                                                                                                                      |

| DCLK              | 1                    | N23                                                                                                           | Hi-Z           | Data clock. This is a Schmitt-trigger input.                                                                                                                                                                                                                                         |

| REFCLK            | I                    | L1                                                                                                            | Hi-Z           | VREF clock. This is a Schmitt-trigger input. VREF is synchronous to this clock in 2-clock systems.                                                                                                                                                                                   |

ISSUE 3

Digital Correction Signal Processor

| Pin Name     | Туре | Pin #                                                                                                                       | Default | Functional Description                                                                                                                     |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|

| VREF_I[15:0] | Ю    | G1,<br>G2,<br>G3,<br>G4,<br>H2,<br>H3,<br>H4,<br>J1, J2,<br>J3,<br>K2,<br>K3,<br>K4,<br>L2,<br>L3, L4                       | Hi-Z    | In normal modes, this bus is the I-channel of the baseband input signal. In scan test mode, this bus is an output used for SCANOUT[31:16]. |

| VREF_Q[15:0] | Ю    | M2,<br>M3,<br>N1,<br>N2,<br>N3,<br>N4,<br>P1,<br>P2,<br>P3,<br>P4,<br>R1,<br>R2,<br>T2,<br>T3,<br>T4, U1                    | Hi-Z    | In normal modes, this bus is the Q-channel of baseband input signal. In scan test mode, this bus is an output used for SCANOUT[15:0].      |

| VOBS_I[15:0] | I    | A11,<br>B11,<br>C11,<br>D11,<br>B12,<br>C12,<br>A13,<br>B13,<br>C13,<br>D13,<br>A14,<br>B14,<br>C14,<br>D14,<br>B15,<br>C15 | Hi-Z    | Input: I-channel of observed signal from power amplifier.                                                                                  |

ISSUE 3

Digital Correction Signal Processor

| Pin Name        | Туре | Pin #                                                                                                                       | Default | Functional Description                                                                                                                  |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------|

| VOBS_Q[15:0]    | I    | B5,<br>B6,<br>C6,<br>A7,<br>B7,<br>C7,<br>D7,<br>B8,<br>C8,<br>D8,<br>A9,<br>B9,<br>C9,<br>A10,<br>B10,<br>C10              | Hi-Z    | Input: Q-channel of observed signal from power amplifier.                                                                               |

| VD_I[15:0]      | Ю    | G23,<br>G22,<br>G21,<br>H22,<br>H21,<br>H20,<br>J23,<br>J22,<br>J21,<br>K22,<br>K21,<br>K20,<br>L23,<br>L22,<br>L21,<br>L20 | Hi-Z    | In normal modes, this bus is the I-channel of output signal to the DAC. In scan test mode, this bus is an input used for SCANIN[31:16]. |

| VD_Q[15:0]      | Ю    | N21,<br>N20,<br>P22,<br>P21,<br>P20,<br>R22,<br>R21,<br>T22,<br>T21,<br>T20,<br>U23,<br>U22,<br>U21,<br>U20,<br>V22,<br>W23 | Hi-Z    | In normal modes, this bus is the Q-channel of output signal to the DAC. In scan test mode, this bus is an input used for SCANIN[15:0].  |

| Serial Port (4) |      |                                                                                                                             |         |                                                                                                                                         |

| SD              | I    | W4                                                                                                                          | Hi-Z    | Serial Data input for the serial port. If unused, this pin must be connected to VSS.                                                    |

| SCLK            | I    | U2                                                                                                                          | Hi-Z    | Clock input for the serial port - Schmitt trigger. If unused, this pin must be connected to VSS.                                        |

ISSUE 3

Digital Correction Signal Processor

| Pin Name         | Туре         | Pin# | Default             | Functional Description                                                                                                                                                                 |

|------------------|--------------|------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCS_N            | I            | U3   | Hi-Z                | Chip Select for the serial port. This is a Schmitt-trigger input. If unused, this pin must be connected to VSS.                                                                        |

| HOP_N            | I            | U4   | Hi-Z                | This input can be used to activate the new carrier and power values. This is a Schmitt-trigger input.  If unused, this pin must be connected to VSS.                                   |

| JTAG and other   | test pins (8 | 3)   | •                   |                                                                                                                                                                                        |

| TCK              | 1            | D16  | Hi-Z                | JTAG clock. In normal operation, this pin must be connected to VSS.                                                                                                                    |

| TRSTB            | I            | C16  | Hi-Z pulled<br>high | JTAG reset signal - active low. This is a Schmitt-trigger input with internal pull-up resistor. In normal mode (non-JTAG) this pin must be connected to RESET_N.                       |

| TMS              | I            | B16  | Hi-Z pulled<br>high | JTAG test mode select input with internal pull-up resistor. In normal operation, this pin must be driven high or left unconnected.                                                     |

| TDI              | 1            | C17  | Hi-Z pulled<br>high | JTAG test data input with internal pull-up resistor. In normal operation, this pin must be driven high or left unconnected.                                                            |

| TDO              | 0            | B18  | Hi-Z                | Tri-state output for JTAG test data. This is the only pin unaffected by OE_N.                                                                                                          |

| SCANSEL          | 1            | A17  | Hi-Z                | Scan MUX select. When high, this signal selects Scan test mode. This pin must be connected to VSS in normal operation.                                                                 |

| SCANEN           | I            | B17  | Hi-Z                | When high, this signal enables the Scan chain. This pin must be connected to VSS in normal operation.                                                                                  |

| OE_N             | I            | A19  | Hi-Z pulled<br>low  | Forces all pins except TDO to high impedance. This is a Schmitt-trigger input with internal pull-down resistor.  In normal operation, this pin must be driven low or left unconnected. |

| Miscellaneous (5 | 50)          |      |                     |                                                                                                                                                                                        |

| RESET_N          | I            | F3   | Hi-Z pulled<br>high | System reset signal - active low. This is a Schmitt-trigger input with internal pull-up resistor.                                                                                      |

| MUTE_N           | I            | AA23 | Hi-Z pulled<br>high | Mute input - active-low. When low, this signal forces VD to zero. This is a Schmitt-trigger input with internal pull-up resistor.                                                      |

| VD_FMT           | I            | C20  | Hi-Z                | Configuration pin that sets the data format of the VD_I and VD_Q outputs: 0 -> offset-binary 1 -> 2s-complement.                                                                       |

ISSUE 3

Digital Correction Signal Processor

| Pin Name         | Туре | Pin#                                                                                                                       | Default | Functional Description                                                                                   |

|------------------|------|----------------------------------------------------------------------------------------------------------------------------|---------|----------------------------------------------------------------------------------------------------------|

| GPIO[47:32]      | Ю    | W22,<br>Y23,<br>Y22,<br>Y19,<br>AB20,<br>AC21,<br>AA6,<br>Y5,<br>AA5,<br>AC4,<br>AC3,<br>AC1,<br>Y1,<br>Y2,<br>W1          | Hi-Z    | General-purpose IO pins.                                                                                 |

| GPIO[31:28]      | Ю    | W2,<br>W3,<br>V2,<br>F2                                                                                                    | Hi-Z    | General-purpose IO pins with rising-edge interrupt capability (see Interrupt_Enable2 register).          |

| GPIO[27:24]      | Ю    | E2,<br>E3,<br>D1,<br>E4                                                                                                    | Hi-Z    | General-purpose IO pins with falling-edge interrupt capability (see Interrupt_Enable2 register).         |

| GPIO[23:18]      | Ю    | D2,<br>C1,<br>D3,<br>A3,<br>C4,<br>D5                                                                                      | Hi-Z    | General-purpose IO pins.                                                                                 |

| GPIO[17]         | Ю    | B4                                                                                                                         | Hi-Z    | General-purpose IO pins or Power_Attenuator_Pulse output (see GPIO_Secondary_Function_Select registers). |

| GPIO[16]         | Ю    | C5                                                                                                                         | Hi-Z    | General-purpose IO pins or Watchdog_Timer_Output (see GPIO_Secondary_Function_Select registers).         |

| GPIO[15:0]       | Ю    | A4,<br>D17,<br>C18,<br>A20,<br>C19,<br>B20,<br>A21,<br>D19,<br>C23,<br>D22,<br>E22,<br>D23,<br>E23,<br>F21,<br>G20,<br>F22 | Hi-Z    | General-purpose IO pins or Power_Attenuator_Output[15:0] (see GPIO_Secondary_Function_Select registers). |

| Power Supply (84 | )    |                                                                                                                            |         |                                                                                                          |

ISSUE 3

Digital Correction Signal Processor

| Pin Name | Туре | Pin# | Default | Functional Description |

|----------|------|------|---------|------------------------|

| VSS      | Р    | A2   |         | Ground supply.         |

|          |      | A6   |         |                        |

|          |      | A8   |         |                        |

|          |      | A12  |         |                        |

|          |      | A16  |         |                        |

|          |      | A18  |         |                        |

|          |      | A22  |         |                        |

|          |      | B1   |         |                        |

|          |      | B3   |         |                        |

|          |      | B21  |         |                        |

|          |      | B23  |         |                        |

|          |      | C2   |         |                        |

|          |      | C22  |         |                        |

|          |      | F1   |         |                        |

|          |      | F23  |         |                        |

|          |      | H1   |         |                        |

|          |      | H23  |         |                        |

|          |      | M1   |         |                        |

|          |      | M23  |         |                        |

|          |      | T1   |         |                        |

|          |      | T23  |         |                        |

|          |      | V1   |         |                        |

|          |      | V23  |         |                        |

|          |      | AA2  |         |                        |

|          |      | AA22 |         |                        |

|          |      | AB1  |         |                        |

|          |      | AB3  |         |                        |

|          | AB21 |      |         |                        |

|          |      | AB23 |         |                        |

|          |      | AC2  |         |                        |

|          |      | AC6  |         |                        |

|          |      | AC8  |         |                        |

|          |      | AC12 |         |                        |

|          |      | AC16 |         |                        |

|          |      | AC18 |         |                        |

|          |      | AC22 |         |                        |

ISSUE 3

Digital Correction Signal Processor

| Pin Name | Туре | Pin #                                                                                                                                | Default | Functional Description    |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------|

| VDD      | P    | A1 A23 B2 B22 C3 C21 D4 D6 D9 D12 D15 D18 D20 F4 F20 J4 J20 M4 M20 R4 R20 V4 V20 Y4 Y6 Y9 Y12 Y15 Y18 Y20 AA3 AA21 AB2 AB22 AC1 AC23 |         | 3.3V IO voltage supply.   |

| VDDI     | Р    | E20,<br>K23,<br>R23,<br>W20,<br>AC19,<br>AC14<br>AC9,<br>AC5,<br>V3,<br>R3,<br>K1,<br>E1,<br>A5,<br>D10,<br>A15,<br>B19              |         | 1.8V Core voltage supply. |

ISSUE 3

PMC-2001646

Digital Correction Signal Processor

# 5 Functional Description

## 5.1 CPU Interface

The CPU interface is designed to "look" like the interface to a slow asynchronous SRAM device, with some added functionality to reduce glue logic. The CPU interface is primarily designed for a TI TMS320C54xx General Purpose DSP processor, but some flexibility is provided to support other processors.

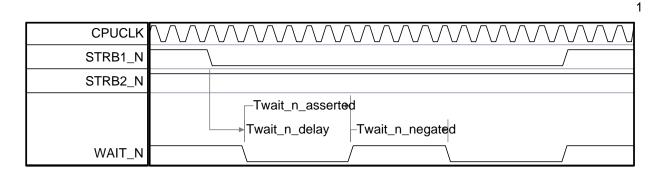

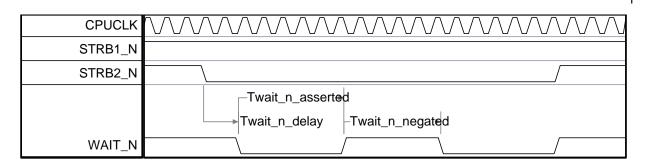

Internally, the CPU access cycle is synchronized to the DCLK to allow a simultaneous CPU write to, and data path read from, the same memory location - this is to provide fail-safe operation of the internal dual-port RAM. This requirement significantly slows down the access speed of the CPU interface, especially at EDGE sample clock rates in the 13MHz range. The slow access speed can result in a longer access time than what can be generated by the internal wait-state machine of the processor when the processor is fast and DCLK is slow. To generate longer CPU access cycles, a wait signal (WAIT\_N) is generated by the PM7800. The WAIT\_N signal is generated by the wait circuit which is clocked by CPUCLK.

The PM7800 needs to detect cycle-to-cycle transitions on the CPU bus. Detecting the cycle-tocycle change is complicated because the cycle-inactive indication (deassertion of the strobes) between cycles can be short for write-to-write cycles, and short or non-existent for read-to-read cycle transitions. To simplify the design and stay within synchronous design practices, cycle-to-

PM7800 PALADIN-10

ISSUE 3

PMC-2001646

Digital Correction Signal Processor

cycle transition-detection is achieved by the direct approach of sampling the control signal(s) inactive, or by the indirect approach of sampling the control strobes a programmable number of clock cycles after the WAIT N signal is deasserted - if the strobes are still active, then the start of another cycle is assumed.

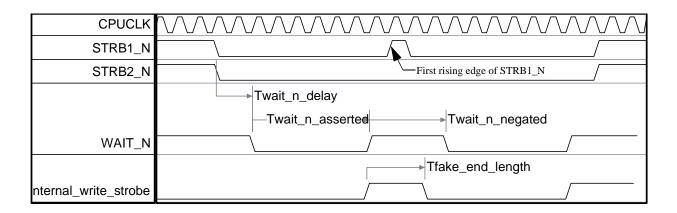

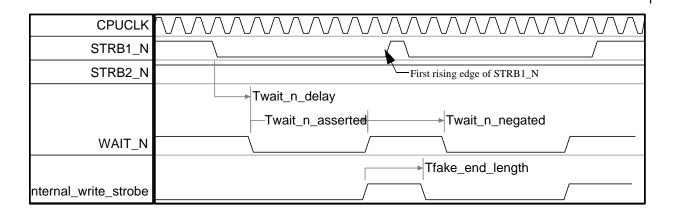

The operation of the wait circuit - clocked by CPUCLK - is as follows: sample control strobes active, assert WAIT N for Assert Wait Cycles (register 0x0 0010 bits 6:0) CPUCLK's, negate WAIT\_N for Negate\_Wait\_Cycles (register 0x0\_0010 bits 11:8) CPUCLK's, then sample control strobes again. Another cycle has started if the control strobes are still active. The TI processor's internal wait-state circuit continues to count while WAIT N is asserted. This results in the waitstate circuitry re-aligning itself with the TI cycle at each transition since the TI cycle will end as soon as it detects WAIT\_N negated. Other processors' internal wait-state circuits may halt while WAIT N is asserted: in this case, the Assert Wait Cycles and Negate Wait Cycles registers must be programmed so that they match the length of the processor accesses.

To further support the case where the de-assertion period of the strobe signal between back-to-back writes is too short to be reliably detected by DCLK, the PM7800 must be programmed to temporarily deassert its internal version of the write strobe: CPUMODE1, when tied to VDD, selects this operation. The Fake End Length register (register 0x0 0010 bits 15:12) sets the duration, in CPUCLK's, for which the write strobe is deasserted.

The C54xx interface has an access strobe (either I/O or memory), an area indication (either DS# or PS# for data or program memory or IS# for I/O space select), a R/W# indication, a data bus and an address bus. To support C54xx processors, STRB1\_N and STRB2\_N must be connected to the access strobe and R/W# indicator respectively, and CPUMODE0 must be tied to VSS. Processors with read and write strobes can be supported by tying CPUMODE0 to VDD, and connecting the write strobe to STRB1 N and the read strobe to STRB2 N.

The CPUMODE2 pin is reserved and should be tied to VDD.

The CPUMODE3 pin, when tied to VDD, selects a mode of operation that can be used to support processors, e.g. ARM, that require the read strobe to be sampled on the falling edge of CPUCLK and the write strobe to be sampled on the rising edge.

The PM7800 can be configured to provide additional hold time from CPUCLK before negating WAIT N - this may be required to support processors, e.g. ARM, that require longer hold times on WAIT N. CPUMODE4, when tied to VDD, selects additional hold time.

ISSUE 3 PMC-2001646

Digital Correction Signal Processor

The following table describes how to connect the PM7800 to a C5410 processor.

Table 5-1 **Connection to C54xx Processor**

| Signal<br>(PM7800) | Connect To<br>(TMS320C5410) | Description                                                                                                                                       |

|--------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| MSTRB#             | STRB1_N                     | This signal is the active-low program memory access strobe.                                                                                       |

| R/W#               | STRB2_N                     | This signal is the Read/Write# cycle type indication.                                                                                             |

| PS#                | CS0_N.                      | This signal is the program space access strobe.                                                                                                   |

| A22 -> A21         | CS1_N, and<br>CS2.          | Two of the upper address bits can be connected to the two other chip select inputs to provide basic address decoding of the program memory space. |

| READY              | WAIT_N                      | When the WAIT_N signal is asserted low, the TI chip extends the current cycle until the WAIT_N signal negated to a high state.                    |

| INTx               | IRQ_N                       | INTx. is one of the four interrupt inputs.                                                                                                        |

| A[17:00]           | ADR[17:00]                  | The TI bus is word addressed, as is the PM7800.                                                                                                   |

| D[15:00]           | DAT[15:00]                  | Data is connected straight across.                                                                                                                |

| CLKOUT             | CPUCLK                      | The master clock output for the TI processor.  Maximum CPU clock frequency 125 MHz.                                                               |

| CPUMODE0           | 0                           | The CPU signalling style is access strobe and read/write# indication.                                                                             |

| CPUMODE1           | 1                           | The WAIT circuit forces the internal version of the CPU write strobe inactive for a programmable number of CPUCLK cycles.                         |

| CPUMODE2           | 1                           | Reserved.                                                                                                                                         |

| CPUMODE3           | 0                           | All inputs sampled on rising edge of CPUCLK.                                                                                                      |

| CPUMODE4           | 0                           | No additional delay on WAIT_N.                                                                                                                    |

# **5.1.1 Functional Timing**

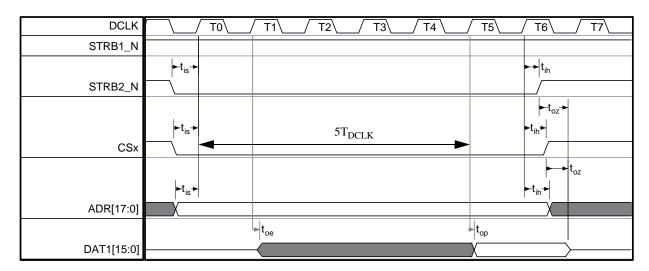

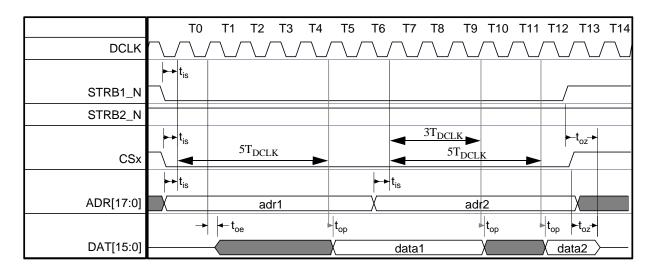

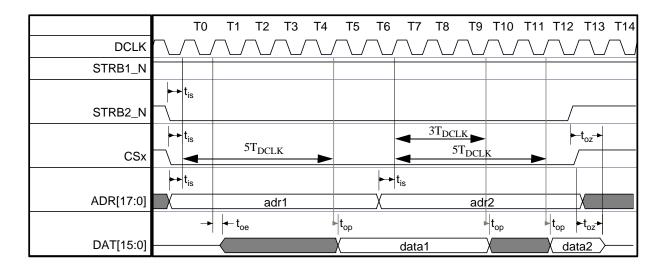

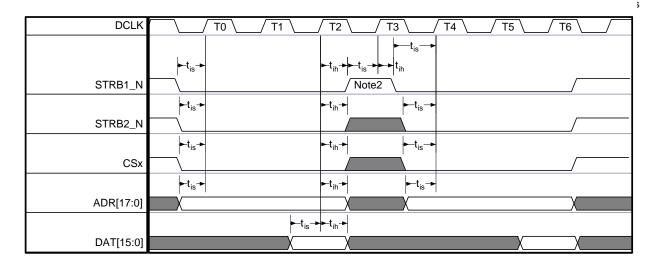

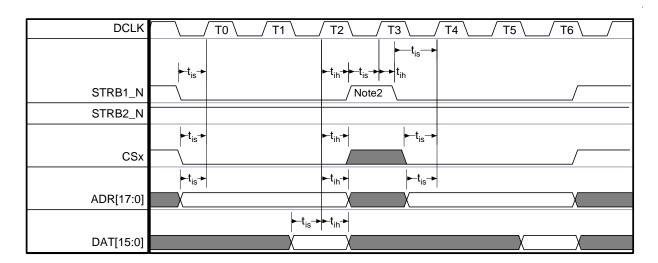

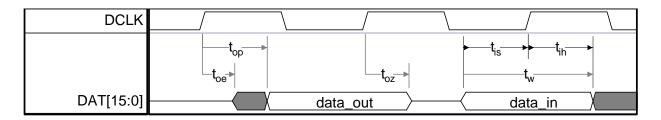

The following timing diagrams give functional timing for the CPU interface. Because this interface is asynchronous to DCLK, AC timing parameters  $(t_{is}, t_{ih}, t_{oe}, t_{op}, t_{oz}, t_{w})$  are shown here for clarity but are defined in AC Timing section 9.

ISSUE 3 PMC-2001646

Digital Correction Signal Processor

Figure 5-2 Read Cycle (CPUMODE0 = 0)

Figure 5-3 Read Cycle (CPUMODE0 = 1)

Digital Correction Signal Processor

Figure 5-4 Back-to-Back Read Cycles (CPUMODE0 = 0)

ISSUE 3

Figure 5-5 Back-to-Back Read Cycles (CPUMODE0 = 1)

Digital Correction Signal Processor

Figure 5-6 Back-to-Back Write Cycles (CPUMODE0 = 0)

Figure 5-7 Back-to-Back Write Cycles (CPUMODE0 = 1)

## Note:

- 1. The system designer need not worry about violating  $t_{is}$  and  $t_{ih}$  all inputs are treated as asynchronous signals. Setup and hold times are specified here to identify the clock edge on which the signal is sampled.

- 2. If deassertion of the strobe cannot be detected by DCLK, CPUMODE1 must be tied to VDD to program the PM7800 to temporarily deactivate the internal write strobe See *Functional Description* section 5. .

Digital Correction Signal Processor

Figure 5-8 WAIT\_N Timing - Reads (CPUMODE0 = 0)

Figure 5-9 WAIT\_N Timing - Reads (CPUMODE0 = 1)

Figure 5-10 WAIT\_N Timing - Writes (CPUMODE0 = 0)

Digital Correction Signal Processor

Figure 5-11 WAIT\_N Timing - Writes (CPUMODE0 = 1)

Table 5-2 Functional Timing for WAIT\_N

| Parameter                    | min                                               | Description                                       |

|------------------------------|---------------------------------------------------|---------------------------------------------------|

| T <sub>wait_n_delay</sub>    | 2T <sub>CPUCLK</sub>                              | STRBx to WAIT_N delay                             |

| T <sub>wait_n_asserted</sub> | (Assert_Wait_Cycles[6:0] + 1)T <sub>CPUCLK</sub>  | WAIT_N pulse width                                |

| T <sub>wait_n_negated</sub>  | (Negate_Wait_Cycles[3:0] + 1) T <sub>CPUCLK</sub> | WAIT_N negated width                              |

| T <sub>fake_end_length</sub> | (Fake_End_Length[3:0] + 1) T <sub>CPUCLK</sub>    | Internal fake_end length for back-to-back writes. |

# 5.1.2 Programming the WAIT\_N Register

The following are guidelines for programming the WAIT\_N register:

Table 5-3 Programming the WAIT\_N Register

| Formula                                                                                                                                                                        | Comment                                                                                                                                                      |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Assert_Wait_Cycles = round-up {6Tdclk /Tcpuclk -1}                                                                                                                             | Must satisfy PM7800 read-access time of 6 dclk periods                                                                                                       |

| Negate_Wait_Cycles = round-up {3 + 32 / T <sub>cpuclk</sub> }                                                                                                                  | Must be long enough to allow the C54 to end the current cycle, and to flush the cycle_active out of the cpuclk synchronizers.                                |

| internal_c54_wait > <b>Negate_Wait_Cycles</b> where internal_c54_wait is the number of wait cycles programmed in the C54xx processor.                                          | The C54 must be programmed such that it will not start another cycle before WAIT_N can be reasserted.                                                        |

| $\label{eq:fake_end_length} \begin{split} &\textbf{Fake\_End\_Length} = round-up\{max\{[(T_{delk} + 2ns)  /  T_{cpuclk}  -  1]: \\ &[1.5 + 32  /  T_{cpuclk}]\}\} \end{split}$ | Must be long enough for the PM7800 to sample its internal fake_wait_inactive with dclk.                                                                      |

|                                                                                                                                                                                | Must also be long enough that fake_wait_inactive is held until past the rising edge of STRB1_N (shown in Figure 5-10 on page 22 and Figure 5-11 on page 23). |

ISSUE 3

PMC-2001646

Digital Correction Signal Processor

### 5.2 Data Interfaces

## 5.2.1 VREF Interface and FIFO

The VREF interface is used to input the reference signal in either offset-binary or two's-complement notation. In the case of offset-binary format, the VREF\_Data\_Format bit in the Mode register must be set to zero to instruct the PM7800 to convert the data to two's-complement format which is used throughout the chip. There are three modes of operation for the VREF interface:

- 1. VREF is clocked in by REFCLK and upsampled to the rate of the PM7800 clock, DCLK, where f<sub>DCLK</sub> = N \* f<sub>REFCLK</sub>. In this case, a FIFO is used to handle the skew between REFCLK and DCLK, and to provide a steady supply of data to the interpolator. Set the Bypass FIFO and Interpolator Bypass bits to zero (default) in this case.

- 2. VREF is clocked in by REFCLK which is at the same rate as the PM7800 clock, DCLK, that is, f<sub>DCLK</sub> = f<sub>REFCLK</sub>. In this case, a FIFO is used to handle the skew between REFCLK and DCLK. The interpolator can be bypassed to reduce latency. Set the Bypass\_FIFO bit to zero (default) and the Interpolator\_Bypass bit to one in this case.

- 3. VREF is at the same rate as and synchronous to DCLK. In this case, the FIFO and interpolator can be bypassed to reduce system latency by setting the Bypass\_FIFO and Interpolator\_Bypass bits to one in the Mode register. The REFCLK input is ignored and should be connected to VSS.

ISSUE 3

PMC-2001646

Digital Correction Signal Processor

### **5.2.2 VOBS Interface**

The VOBS interface is used to input the observed signal from the ADC in either offset-binary or two's-complement notation. In the case of offset-binary format, the VOBS\_Data\_Format bit in the Mode register must be set to zero to instruct the PM7800 to convert the data to two's-complement format.

### **5.2.3 VD Interface**

The VD interface is used to output the predistorted signal to the DAC in either offset-binary or two's-complement notation. The VD\_FMT pin selects offset-binary format when low, and two's-complement format when high.

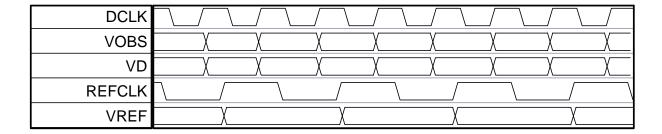

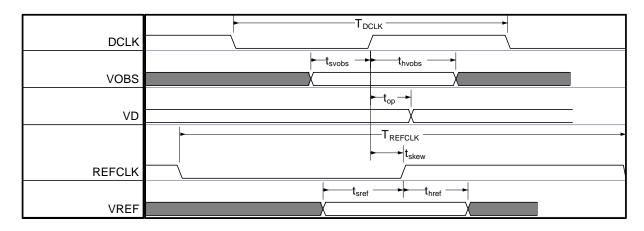

## 5.2.4 Dual-Clock System

Use the dual-clock system when VREF is synchronous to REFCLK (usually when VREF is upsampled internally to the DCLK rate).  $T_{REFCLK}$  must be an exact integer multiple of  $T_{DCLK}$ , i.e.  $T_{REFCLK} = nT_{DCLK}$ , where n = 1,2,...,10. REFCLK must be created from DCLK. In this case, a FIFO and interpolator are used to upsample VREF to the DCLK rate. REFCLK must be created from DCLK such that there is no varying phase shift that may cause under-run or over-run, i.e. skew may exist between DCLK and REFCLK, but this skew must not vary over time by more than one DCLK period.

Figure 5-13 Dual-Clock System timing

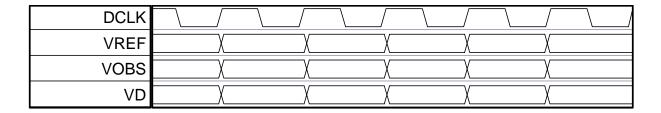

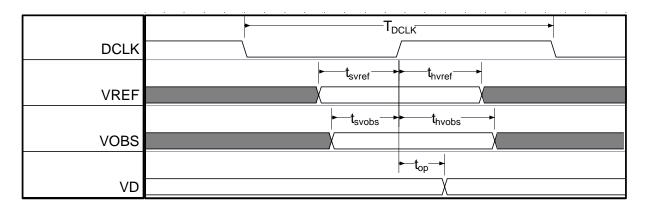

# **5.2.5** Single-Clock System

Use the single-clock system when all signals are synchronous to DCLK and the data-rate of VREF is the same as the output data-rate of VD. In this case, connect the REFCLK pin to VSS, and bypass the FIFO and interpolator to reduce latency through the chip.

PMC-2001646 ISSUE 3 Digital Correction Signal Processor

Figure 5-14 Single-Clock System timing

### 5.3 Serial Interface

The serial interface is used to input the next\_power, next\_carrier values, hop\_stream command, and general-purpose serial\_word register. Also included in this interface is the HOP\_N pin which can be used to delay the effect of the hop\_stream to a more precise time.

The PM7800 supports the SPI specification included in the M68HC11 Reference Manual (section 8). Only the modes where CPHA = 1 is supported. CPOL may be 0 or 1, and the spi\_clock\_polarity bit of the serial\_mode register ( $0x0_013$  bit 2) is used to select the active clock edge. The PM7800 does not have a data output pin (MISO). The PM7800's SCS\_N pin is equivalent to the /SS pin, and it can be tied to ground to reduce system pin requirements.

A transfer can be reset by deactivating SCS\_N. If SCS\_N is tied low (always active) then another method must be used to reset the state machine. One way is to disable the serial interface by writing a zero to the serial\_interface\_enable bit in the Serial\_Mode register. Another way is to set reg\_serial\_address[4:0] = 00000b (this is the default setting) and stream twenty-four 1's into the serial port: at some stage during the stream of 1's, the idle state will be reached and the interface

Digital Correction Signal Processor

will be held waiting for the first 0 of the address. Note that if the transfer is aborted after some data has been sent, that data will already be shifted into the respective data register.

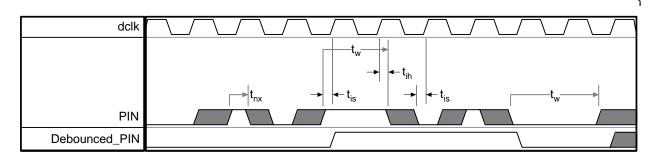

ISSUE 3

Relative timing of the SPI input signals is shown in Figure 5-16. Note that SCLK, SD, SCS\_N can be asynchronous to DCLK: Figure 5-16 shows timing for the inputs relative to the DCLK edges on which they are detected. Notes:

- SCLK, SD, SCS\_N are debounced using DCLK, therefore they must be present for two consecutive DCLK edges to be properly detected. It is recommended that the minimum pulse-width be 3 T<sub>DCLK</sub>, i.e. T<sub>SCLK</sub> >= 6T<sub>DCLK</sub>.

- SD and SCS\_N are sampled by DCLK on the active edge of SCLK. Therefore, because of the asynchronous relationship, it is recommended that SD and SCS\_N be valid for one DCLK either side of the active SCLK edge.

## **5.3.1 Serial Operation**

All signal pins in the serial interface are synchronized to dclk and debounced to reject glitches shorter than a dclk period - see *AC Timing*. There are four serial streams recognized by this interface:

- 1. carrier stream consists of three bytes as follows:

- five address bits corresponding to reg\_serial\_address[4:0]

- two bits = 00b, that indicate a carrier\_stream

- a r/w bit that must be zero

- seven don't-care bits

Digital Correction Signal Processor

• nine bits of the next carrier value - in the order of msb to lsb

ISSUE 3

Figure 5-17 SPI carrier\_stream (spi\_clock\_polarity = 0, falling edge of SCLK is active)

Figure 5-18 SPI carrier\_stream (spi\_clock\_polarity = 1, rising edge of SCLK is active)

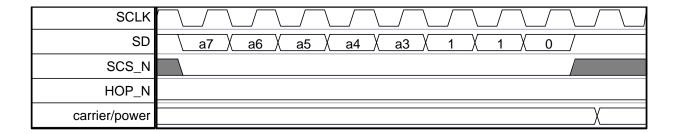

- 2. power\_stream consists of two bytes as follows:

- five address bits corresponding to reg\_serial\_address[4:0]

- two bits = 01b, that indicate a power\_stream

- a r/w bit that must be zero

- eight bits of the next\_power value in the order of msb to lsb

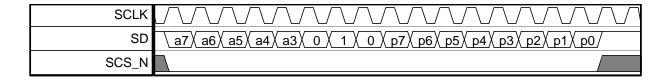

Figure 5-19 SPI power\_stream (spi\_clock\_polarity = 0, falling edge of SCLK is active)

Figure 5-20 SPI power\_stream (spi\_clock\_polarity = 1, rising edge of SCLK is active)

| SCLK  |                                                                                                                |

|-------|----------------------------------------------------------------------------------------------------------------|

| SD    | \ a7\(\) a6\(\) a5\(\) a4\(\) a3\(\) 0\(\) 1\(\) 0\(\) p7\(\) p6\(\) p5\(\) p4\(\) p3\(\) p2\(\) p1\(\) p0\(\) |

| SCS_N |                                                                                                                |

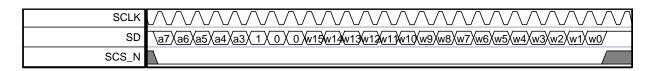

3. word\_stream consists of three bytes as follows:

PMC-2001646 ISSUE 3

Digital Correction Signal Processor

- five address bits corresponding to reg\_serial\_address[4:0]

- two bits = 10b, that indicate a word\_stream

- a r/w bit that must be zero

- sixteen bits of the serial\_word value in the order of msb to lsb

Figure 5-21 SPI word\_stream (spi\_clock\_polarity = 0, falling edge of SCLK is active)

Figure 5-22 SPI word\_stream (spi\_clock\_polarity = 1, rising edge of SCLK is active)

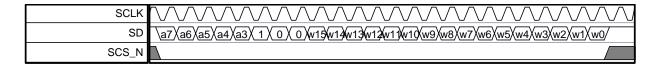

- 4. hop\_stream consists of one byte as follows:

- five address bits corresponding to reg\_serial\_address[4:0]

- two bits = 11b, that indicate a hop\_stream

- a r/w bit that must be zero

Figure 5-23 SPI hop\_stream (spi\_clock\_polarity = 0, falling edge of SCLK is active)

Figure 5-23 shows how HOP N can be used to delay the new carrier/power values.

Digital Correction Signal Processor

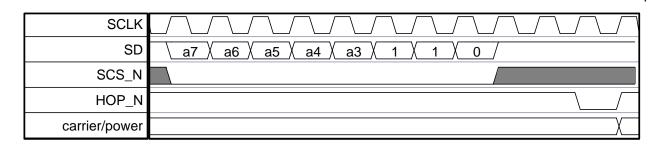

Figure 5-24 SPI hop\_stream (spi\_clock\_polarity = 1, rising edge of SCLK is active)

ISSUE 3

Figure 5-24 shows a case where HOP\_N is tied active so that the new carrier/power values take effect immediately after the Hop\_Stream.

### 5.4 Hop Generation

The hop\_state\_machine generates the Hop pulse that propagates throughout the chip and activates the new carrier and power values. The Hop pulse is generated upon a write to the Hop bit in the Control register, or on the later of HOP\_N and a Hop\_Stream. There are three methods of operation:

- 1. The Hop bit in the Control register controls the activation point.

The CPU writes to the next\_carrier and/or next\_power registers, then writes 1 to the Hop bit in the Control register.