# 64K x 72-bit Entry NETWORK PACKET SEARCH ENGINE

DATA BRIEFING

## **FEATURES SUMMARY**

- 64K DATA ENTRIES IN 72-BIT MODE

- TABLE MAY BE PARTITIONED INTO UP TO EIGHT (8) OCTANTS (Data entry width in each octant is configurable as 36, 72, 144, or 288 bits.)

- UP TO 100 MILLION SUSTAINED SEARCHES PER SECOND IN 72-BIT and 144-BIT CONFIGURATIONS

- UP TO 50 MILLION SEARCHES PER SECOND IN 36-BIT and 288-BIT CONFIGURATIONS

- SEARCHES ANY SUB-FIELD IN A SINGLE CYCLE

- OFFERS BIT-BY-BIT and GLOBAL MASKING

- SYNCHRONOUS, PIPELINED OPERATION

- UP TO 31 SEARCH ENGINES CASCADABLE WITHOUT PERFORMANCE DEGRADATION

- WHEN CASCADED, THE DATABASE ENTRIES CAN SCALE FROM 496K TO 3968K DEPENDING ON THE WIDTH OF THE ENTRY

- GLUELESS INTERFACE TO INDUSTRY-STANDARD SRAMS

- SIMPLE HARDWARE INSTRUCTION INTERFACE

- IEEE 1149.1 TEST ACCESS PORT

- OPERATING SUPPLY VOLTAGES INCLUDE:

$V_{DD}$  (Operating Core Supply Voltage) = 1.5V for 66 and 83MSPS; 1.65V for 100MSPS  $V_{DDQ}$  (Operating Supply Voltage for I/O) = 2.5 or 3.3V

■ 388 PBGA, 35mm x 35mm

Figure 1. 388-ball PBGA Package

April 2002 1/7

#### DESCRIPTION

### Overview

ST Microelectronics, Inc.'s M7040N Search Engine incorporates patent-pending Associative Processing Technology™ (APT) and is designed to be a high-performance, pipelined, synchronous, 64K-entry network database search engine. The M7040N database entry size can be 72 bits, 144 bits, or 288 bits. In the 72-bit entry mode, the size of the database is 64K entries. In the 144-bit mode, the size of the database is 32K entries, and in the 288-bit mode, the size of the database is 16K entries. The M7040N is configurable to support multiple databases with different entry sizes. The 36-bit entry table can be implemented using the Global Mask Registers (GMRs) building-database size of 128K entries with a single device.

#### **Performance**

The Search Engine can sustain 100 million transactions per second when the database is programmed or configured as 72 or 144 bits. When the database is programmed to have an entry size of 36 or 288 bits, the Search Engine will perform at 50 million transactions per second. STM's M7040N can be used to accelerate network protocols such as Longest-prefix Match (CIDR), ARP, MPLS, and other Layer 2, 3, and 4 protocols.

## **Applications**

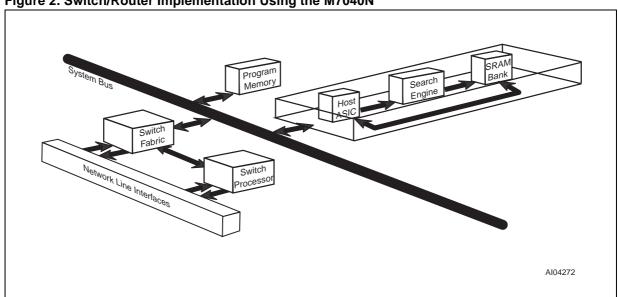

This high-speed, high-capacity Search Engine can be deployed in a variety of networking and communications applications. The performance and features of the M7040N make it attractive in applications such as Enterprise LAN switches and routers and broadband switching and/or routing equipment supporting multiple data rates at OC-48 and beyond. The Search Engine is designed to be scalable in order to support network database sizes to 3968K entries specifically for environments that require large network policy databases. Figure 4, page 5 shows the block diagram for the M7040N device.

**Table 1. Product Range**

| Part Number   | Operating<br>Supply Voltage | Operating I/O<br>Voltage | Speed  | Temperature Range |  |  |  |  |

|---------------|-----------------------------|--------------------------|--------|-------------------|--|--|--|--|

| M7040N-100ZA1 | 1.65V                       | 2.5 or 3.3V              | 100MHz | Commercial        |  |  |  |  |

| M7040N-083ZA1 | 1.5V                        | 2.5 or 3.3V              | 83MHz  | Commercial        |  |  |  |  |

| M7040N-066ZA1 | 1.5V                        | 2.5 or 3.3V              | 66MHz  | Commercial        |  |  |  |  |

Figure 2. Switch/Router Implementation Using the M7040N

2/7

**Table 2. Signal Names**

| Symbol                 | Type <sup>(1)</sup> | Description                     |  |  |  |  |  |  |  |  |  |  |

|------------------------|---------------------|---------------------------------|--|--|--|--|--|--|--|--|--|--|

| Clocks and Reset       |                     |                                 |  |  |  |  |  |  |  |  |  |  |

| CLK_MODE               | I                   | Clock Mode                      |  |  |  |  |  |  |  |  |  |  |

| CLK2X_CLK1X            | I                   | Master Clock                    |  |  |  |  |  |  |  |  |  |  |

| PHS_L                  | I                   | Phase                           |  |  |  |  |  |  |  |  |  |  |

| TEST_CO <sup>(2)</sup> | I                   | Test Output (ST Use Only)       |  |  |  |  |  |  |  |  |  |  |

| TEST                   | I                   | Test Input (ST Use Only)        |  |  |  |  |  |  |  |  |  |  |

| TEST_FM                | I                   | Test Input (ST Use Only)        |  |  |  |  |  |  |  |  |  |  |

| RST_L                  | 1                   | Reset                           |  |  |  |  |  |  |  |  |  |  |

| TEST_PB <sup>(3)</sup> | I                   | Test Input (ST Use Only)        |  |  |  |  |  |  |  |  |  |  |

| CFG_L                  | I                   | Configuration                   |  |  |  |  |  |  |  |  |  |  |

| C                      | ommand              | and DQ Bus                      |  |  |  |  |  |  |  |  |  |  |

| CMD[10:0]              | 1                   | Command Bus                     |  |  |  |  |  |  |  |  |  |  |

| CMDV                   | 1                   | Command Valid                   |  |  |  |  |  |  |  |  |  |  |

| DQ[71:0]               | I/O                 | Address/Data Bus                |  |  |  |  |  |  |  |  |  |  |

| ACK <sup>(4)</sup>     | Т                   | READ Acknowledge                |  |  |  |  |  |  |  |  |  |  |

| EOT <sup>(4)</sup>     | Т                   | End of Transfer                 |  |  |  |  |  |  |  |  |  |  |

| SSF                    | Т                   | SEARCH Successful Flag          |  |  |  |  |  |  |  |  |  |  |

| SSV                    | Т                   | SEARCH Successful Flag<br>Valid |  |  |  |  |  |  |  |  |  |  |

| MULTI_HIT              | 0                   | Multiple Hit Flag               |  |  |  |  |  |  |  |  |  |  |

| HIGH_SPEED             | I                   | 100MHz Indicator                |  |  |  |  |  |  |  |  |  |  |

| CLKTUNE[3:0]           | I                   | PLL Tuner                       |  |  |  |  |  |  |  |  |  |  |

| SRAM Interface        |          |                                                             |  |  |  |  |  |  |  |  |  |

|-----------------------|----------|-------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| SADR[23:0]            | Т        | SRAM Address                                                |  |  |  |  |  |  |  |  |  |

| CE_L                  | Т        | SRAM Chip Enable                                            |  |  |  |  |  |  |  |  |  |

| WE_L                  | Т        | SRAM Write Enable                                           |  |  |  |  |  |  |  |  |  |

| OE_L                  | Т        | SRAM Output Enable                                          |  |  |  |  |  |  |  |  |  |

| ALE_L                 | Т        | Address Latch Enable                                        |  |  |  |  |  |  |  |  |  |

|                       | Cascade  | Interface                                                   |  |  |  |  |  |  |  |  |  |

| LHI[6:0]              | 1        | Local Hit In                                                |  |  |  |  |  |  |  |  |  |

| LHO[1:0]              | 0        | Local Hit Out                                               |  |  |  |  |  |  |  |  |  |

| BHI[2:0]              | I        | Block Hit In                                                |  |  |  |  |  |  |  |  |  |

| BHO[2:0]              | 0        | Block Hit Out                                               |  |  |  |  |  |  |  |  |  |

| FULI[6:0]             | I        | Full In                                                     |  |  |  |  |  |  |  |  |  |

| FULO[1:0]             | 0        | Full Out                                                    |  |  |  |  |  |  |  |  |  |

| FULL                  | 0        | Full Flag                                                   |  |  |  |  |  |  |  |  |  |

| Device Identification |          |                                                             |  |  |  |  |  |  |  |  |  |

| ID[4:0]               | 1        | Device Identification                                       |  |  |  |  |  |  |  |  |  |

|                       | Sup      | plies                                                       |  |  |  |  |  |  |  |  |  |

| V <sub>DD</sub>       | n/a      | Chip Core Supply (1.5V for 66 and 83MSPS; 1.65 for 100MSPS) |  |  |  |  |  |  |  |  |  |

| V <sub>DDQ</sub>      | n/a      | Chip I/O Supply (2.5 or 3.3V)                               |  |  |  |  |  |  |  |  |  |

|                       | Test Acc | cess Port                                                   |  |  |  |  |  |  |  |  |  |

| TDI                   | I        | Test Access Port's Test<br>Data In                          |  |  |  |  |  |  |  |  |  |

| тск                   | ı        | Test Access Port's Test<br>Clock                            |  |  |  |  |  |  |  |  |  |

| TDO                   | Т        | Test Access Port's Test<br>Data Out                         |  |  |  |  |  |  |  |  |  |

| TMS                   | I        | Test Access Port's Test<br>Mode Select                      |  |  |  |  |  |  |  |  |  |

| TRST_L                | l        | Test Access Port's Reset                                    |  |  |  |  |  |  |  |  |  |

Note: 1. Signal types are: I = Input only; I/O = Input or Output; O = Output; and T = Tristate

See DESCRIPTIONS FOR CONNECTION DIAGRAM (Figure 3, page 9), page 152 for individual connection details.

In the previous versions of this specification, this signal was called, "CLK\_OUT."

In previous versions of this specification, this signal was called, "PLL\_BYPASS."

ACK and EOT Signals require a weak, external pull-down resistor of 47 KΩ or 100 KΩ.

Figure 3. Connections

|    | 1                | 2                | 3                | 4                | 5               | 6                | 7               | 8                | 9                | 10               | 11              | 12               | 13               | 14              | 15               | 16              | 17               | 18              | 19               | 20              | 21               | 22               | 23              | 24               | 25               | 26               | 1  |

|----|------------------|------------------|------------------|------------------|-----------------|------------------|-----------------|------------------|------------------|------------------|-----------------|------------------|------------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|-----------------|------------------|------------------|-----------------|------------------|------------------|------------------|----|

| Α  | CLK<br>TUNE3     | DQ71             | V <sub>DDQ</sub> | DQ67             | DQ63            | V <sub>DDQ</sub> | DQ57            | DQ53             | DQ51             | DQ43             | DQ41            | DQ37             | DQ35             | DQ31            | V <sub>DDQ</sub> | DQ25            | DQ21             | DQ17            | V <sub>DDQ</sub> | DQ9             | DQ5              | DQ3              | TEST_<br>FM     | V <sub>DDQ</sub> | HIGH_<br>SPEED   | CLK<br>TUNE0     | A  |

| В  | TDI              | v <sub>ss</sub>  | DQ69             | DQ65             | DQ61            | DQ59             | DQ55            | V <sub>DDQ</sub> | DQ47             | DQ45             | DQ39            | V <sub>DDQ</sub> | DQ33             | DQ29            | DQ27             | DQ23            | V <sub>DDQ</sub> | DQ15            | DQ11             | DQ7             | V <sub>DDQ</sub> | DQ1              | TEST_<br>PB     | CFG_L            | V <sub>SS</sub>  | SADR<br>0        | В  |

| С  | TCK              | TMS              | V <sub>DD</sub>  | V <sub>DD</sub>  | v <sub>DD</sub> | V <sub>DD</sub>  | V <sub>DD</sub> | NC8              | DQ49             | V <sub>DDQ</sub> | v <sub>DD</sub> | v <sub>DD</sub>  | V <sub>DD</sub>  | V <sub>DD</sub> | V <sub>DD</sub>  | v <sub>DD</sub> | DQ19             | DQ13            | NC7              | V <sub>DD</sub> | V <sub>DD</sub>  | v <sub>DD</sub>  | V <sub>DD</sub> | V <sub>DD</sub>  | SADR<br>1        | V <sub>DDQ</sub> | С  |

| D  | TRST_<br>L       | TDO              | V <sub>DD</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>DD</sub> | v <sub>DD</sub>  | V <sub>DD</sub>  | V <sub>DD</sub> | $V_{DD}$         | v <sub>DD</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | SADR<br>3        | SADR<br>2        | D  |

| Е  | ID0              | V <sub>DDQ</sub> | V <sub>DD</sub>  | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | V <sub>DD</sub>  | SADR<br>5        | SADR<br>4        | Ε  |

| F  | ID1              | ID2              | V <sub>DD</sub>  | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | V <sub>DD</sub>  | SADR<br>6        | V <sub>DDQ</sub> | F  |

| G  | ID3              | ID4              | $v_{DD}$         | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | v <sub>DD</sub>  | SADR<br>8        | SADR<br>7        | G  |

| Н  | LHI0             | LHI1             | NC1              | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | NC6              | V <sub>DDQ</sub> | SADR<br>9        | Н  |

| J  | LHI2             | LHI3             | V <sub>DDQ</sub> | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | SADR<br>11       | SADR<br>12       | SADR<br>10       | J  |

| K  | LHI6             | LHI4             | LHI5             | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | SADR<br>13       | V <sub>DDQ</sub> | SADR<br>14       | К  |

| L  | LHO0             | LHO1             | V <sub>DD</sub>  | V <sub>DD</sub>  |                 |                  |                 |                  |                  |                  | V <sub>SS</sub> | V <sub>SS</sub>  | v <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> |                  |                 |                  |                 |                  |                  | v <sub>DD</sub> | V <sub>DD</sub>  | SADR<br>15       | SADR<br>16       | L  |

| М  | V <sub>DDQ</sub> | BHI0             | V <sub>DD</sub>  | v <sub>DD</sub>  |                 |                  |                 |                  |                  |                  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> |                  |                 |                  |                 |                  |                  | v <sub>DD</sub> | V <sub>DD</sub>  | V <sub>DDQ</sub> | SADR<br>17       | М  |

| Ν  | BHI1             | BHI2             | V <sub>DD</sub>  | v <sub>DD</sub>  |                 |                  |                 |                  |                  |                  | V <sub>SS</sub> | V <sub>SS</sub>  | v <sub>ss</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> |                  |                 |                  |                 |                  |                  | v <sub>DD</sub> | V <sub>DD</sub>  | SADR<br>19       | SADR<br>18       | N  |

| Р  | BHO0             | MULTI_<br>HIT    | V <sub>DD</sub>  | V <sub>DD</sub>  |                 |                  |                 |                  |                  |                  | V <sub>SS</sub> | V <sub>SS</sub>  | v <sub>ss</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> |                  |                 |                  |                 |                  |                  | v <sub>DD</sub> | v <sub>DD</sub>  | SADR<br>21       | SADR<br>20       | Р  |

| R  | V <sub>DDQ</sub> | BHO1             | $V_{DD}$         | V <sub>DD</sub>  |                 |                  |                 |                  |                  |                  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | v <sub>SS</sub> |                  |                 |                  |                 |                  |                  | V <sub>DD</sub> | V <sub>DD</sub>  | SADR<br>22       | V <sub>DDQ</sub> | R  |

| Т  | BHO2             | V <sub>SS</sub>  | V <sub>DD</sub>  | V <sub>DD</sub>  |                 |                  |                 |                  |                  |                  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> |                  |                 |                  |                 |                  |                  | V <sub>DD</sub> | V <sub>DD</sub>  | CLK_<br>MODE     | SADR<br>23       | Т  |

| U  | FULI0            | V <sub>DDQ</sub> | FULI1            | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | OE_L             | PHS_L            | CLK1x/<br>CLK2x  | U  |

| ٧  | FULI2            | FULI3            | FULI4            | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | CE_L             | V <sub>DDQ</sub> | WE_L             | V  |

| W  | V <sub>DDQ</sub> | FULI5            | NC2              | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | NC5              | CMDV             | ALE_L            | w  |

| Υ  | FULI6            | FULO0            | v <sub>DD</sub>  | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | V <sub>DD</sub>  | CMD1             | CMD0             | Y  |

| AA | FULO1            | V <sub>DDQ</sub> | v <sub>DD</sub>  | V <sub>SS</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | V <sub>DD</sub>  | CMD3             | CMD2             | AΑ |

| AB | FULL             | ACK              | V <sub>DD</sub>  | v <sub>ss</sub>  |                 |                  |                 |                  |                  |                  |                 |                  |                  |                 |                  |                 |                  |                 |                  |                 |                  |                  | V <sub>SS</sub> | v <sub>DD</sub>  | CMD5             | CMD4             | AE |

| AC | V <sub>SS</sub>  | EOT              | V <sub>DD</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub>  | v <sub>DD</sub> | V <sub>DD</sub>  | V <sub>DD</sub>  | V <sub>DD</sub> | V <sub>DD</sub>  | v <sub>DD</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>SS</sub>  | V <sub>SS</sub>  | V <sub>SS</sub> | V <sub>DD</sub>  | CMD6             | V <sub>DDQ</sub> | AC |

| AD | RST_L            | V <sub>DDQ</sub> | v <sub>DD</sub>  | V <sub>DD</sub>  | V <sub>DD</sub> | V <sub>DD</sub>  | V <sub>DD</sub> | NC3              | V <sub>DDQ</sub> | DQ46             | V <sub>DD</sub> | v <sub>DD</sub>  | v <sub>DD</sub>  | v <sub>DD</sub> | v <sub>DD</sub>  | V <sub>DD</sub> | DQ20             | DQ16            | NC4              | V <sub>DD</sub> | V <sub>DD</sub>  | V <sub>DD</sub>  | v <sub>DD</sub> | v <sub>DD</sub>  | CMD8             | CMD7             | ΑC |

| ΑE | TEST             | V <sub>SS</sub>  | DQ70             | V <sub>DDQ</sub> | DQ64            | DQ60             | DQ58            | DQ54             | DQ50             | DQ44             | DQ42            | DQ38             | V <sub>DDQ</sub> | DQ32            | DQ28             | DQ26            | V <sub>DDQ</sub> | DQ18            | DQ12             | DQ10            | DQ6              | V <sub>DDQ</sub> | DQ0             | V <sub>DDQ</sub> | V <sub>SS</sub>  | CLK<br>TUNE1     | AE |

| AF | TEST_<br>CO      | CLK<br>TUNE2     | DQ68             | DQ66             | DQ62            | V <sub>DDQ</sub> | DQ56            | DQ52             | DQ48             | V <sub>DDQ</sub> | DQ40            | DQ36             | DQ34             | DQ30            | V <sub>DDQ</sub> | DQ24            | DQ22             | DQ14            | V <sub>DDQ</sub> | DQ8             | DQ4              | DQ2              | SSV             | SSF              | CMD10            | CMD9             | AF |

|    | 1                | 2                | 3                | 4                | 5               | 6                | 7               | 8                | 9                | 10               | 11              | 12               | 13               | 14              | 15               | 16              | 17               | 18              | 19               | 20              | 21               | 22               | 23              | 24               | 25               | 26               |    |

Note: This diagram is TOP VIEW perspective (view through package).

4/7

Figure 4. M7040N Block Diagram PHS\_L -CLK1X\_CLK2X — Comparand Registers[15:0] Global Mask Registers [15:0] RST\_L ─► Information and Command Register CLK\_MODE -Burst Read Register Burst Write Register Next Free Address Register Search Successful Index Registers [7:0] Compare/PIO Data (All registers are 72-bit-wide) TAP - TAP Controller DQ [71:0] Compare/PIO Data Configurable as SADR [23:0] 128K x 36 64K x 72 CMD [10:0] -32K x 144 OE\_L Command Pipeline Address Decode Priority Encode CMDV 16K x 288 Decode Match Logic and and PIO Access Data Array ACK SRAM WE\_L Control EOT -Configurable as 128K x 36 CE\_L 64K x 72 32K x 144 ALE\_L ID [4:0] 16K x 288 Mask Array Full Logic FULL [6:0] -FULL LHI [6:0] -LHO [1:0]

BHI [2:0] -

FULO [1:0]

Arbitration

Logic

BHO [2:0]

SSF

SSV

AI04645

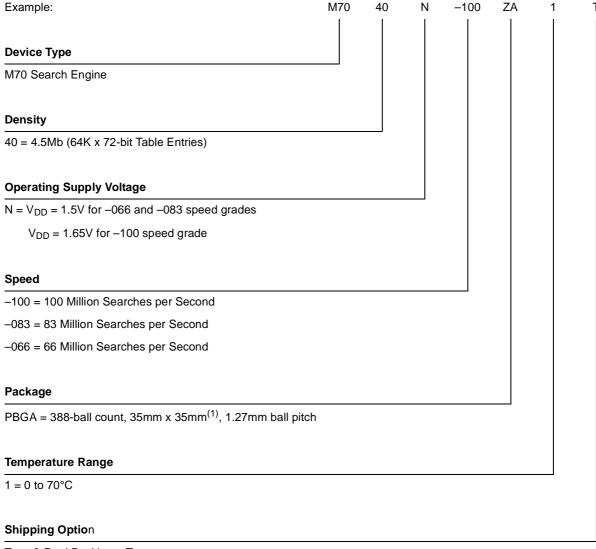

### **PART NUMBERING**

Tape & Reel Packing = T

Note: 1. Where "Z" is the symbol for BGA packages and "A" denotes 1.27mm ball pitch

For a list of available options (e.g., Speed, Package) or for further information on any aspect of this device, please contact the ST Sales Office nearest to you.

6/7

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is registered trademark of STMicroelectronics All other names are the property of their respective owners.

© 2002 STMicroelectronics - All Rights Reserved

STMicroelectronics GROUP OF COMPANIES

Australia - Brazil - Canada - China - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - U.S.A.

www.st.com