# **Application Note**

# ADC INPUT BUFFER AND PROTECTION TECHNIQUES

# By Steven Green

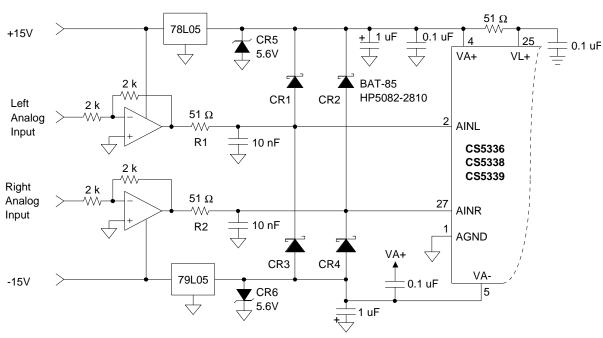

Figure 1. ADC Input Protection ±15 V Op-Amp

### INTRODUCTION

The design of input buffer and protection circuits for analog-to-digital-converters (ADC) is critical to an optimized and reliable data acquisition system. The Crystal Semiconductor application note "ADC Input Buffers" covered this area well and the system designer should review this information. Since the publication of "ADC Input Buffers" there have been many requests for additional information and circuits relating to ADC input protection. This application note describes suitable buffer/protection circuits for the CS5336 family of converters. The techniques described are equally applicable to the other families of Crystal analog-to-digital converters.

### SCR LATCH-UP

SCR latch-up has been defined as "the creation of a low impedance path between the power supply rails by the triggering of parasitic, four-layer bipolar structures (SCR's) inherent in CMOS input and output circuitry." This is a self-sustaining condition and once latched, a CMOS device will remain so regardless of the I/O pin voltages until the power supply voltages are removed. The excessive power dissipation during latch-up may also damage the device. Latch-up is most often caused by forcing current into the inputs or outputs of a CMOS device by applying voltages greater than the power supply rails. When powered, Crystal Semiconductor ADC's are extremely immune to latch-up because

of the amount of current required to initiate a latch. Problems can arise when input voltages greater than the instantaneous power supply voltages are applied during power-up. A less common but equally damaging SCR condition can occur when power-supply voltages exceed the absolute maximum specified value. There are several protection techniques available to the designer each with their own advantages and disadvantages.

# PROTECTION TECHNIQUES

The goal of input protection is to guarantee that the ADC input voltage never exceeds the supply voltages of the converter. This is accomplished with an op-amp buffer between the "outside" world and the ADC input, then limiting the ADC input voltage excursions to the range bounded by the converter power supply voltages.

### Method I

There are many high quality op-amps available to the design engineer for use as input buffers and the majority of these have been designed to operate from power supplies greater than ±5 V. The use of the required multiple supplies presents potential problems. It is possible for the ADC analog input to experience voltages greater than the ADC supplies either during signal amplitude excursions, transient power-on conditions or op-amp failure. Several methods are available to clamp the ADC input volt-

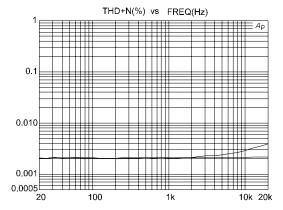

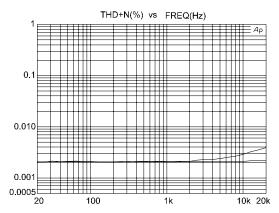

Figure 2. %THD Effects of 1N5818 Schottky Diodes with NE5532 Op-amp

age and are discussed in detail in references 1-7. Figure 1 shows a diode-clamped input buffer circuit utilizing multiple supplies. The type of diode selected for CR1-CR4 is crucial and must be evaluated using the following criteria:

- 1) Forward-biased voltage characteristics. Schottky diodes are preferred due to their low forward-biased voltage characteristics.

- 2) Reverse-bias leakage current. The effects of voltage dependent leakage currents are proportional to circuit impedences and can cause distortion. Leakage currents will also vary with temperature and must be evaluated over the intended temperature operating range.

- Reverse-bias capacitance. Voltage dependent junction capacitance can cause distortion and must be insignificant in comparison to the circuit component values.

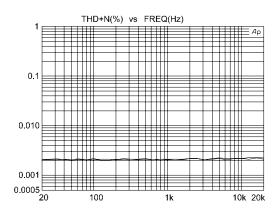

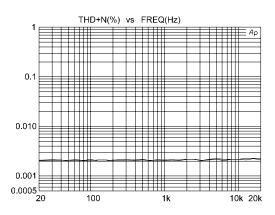

Figure 2 is a comparison %THD plot of the circuit of Figure 1 with and without 1N5818 Schottky diodes installed for CR1-CR4. Note the increase in %THD resulting from diode capacitance. Figure 3 is a comparison %THD plot of the circuit of Figure 1 with and without Philips BAT-85 Schottky diodes. Note the lack of distortion produced by the addition of suitable protection components. Hewlett-Packard 5082-2810 diodes give similar results.

Figure 3. %THD Effects of BAT-85 Schottky Diodes with NE5532 Op-amp

2 AN20REV2

# Notes for Method 1

The values of R1 and R2 were selected to optimize the source impedance for the CS5336 and utilize the current limiting characteristics of the op-amp.

Clamping circuits with diodes in the feedback loop of the op-amp work well for signal clamping but are not effective for power-on transient or op-amp failure conditions. These circuits are not recommended for protection.

# ADC Power Supply Overvoltage

Standard 3-terminal regulators are designed to either source (78L05) or sink (79L05) current but not both. It is possible to raise the ADC supply voltage above the regulation voltage through the Schottky diodes during error conditions. The 5.6 V zener diodes CR5 and CR6 are included to prevent the supply voltages from exceeding the maximum specified value and damaging the converter.

## **Method II**

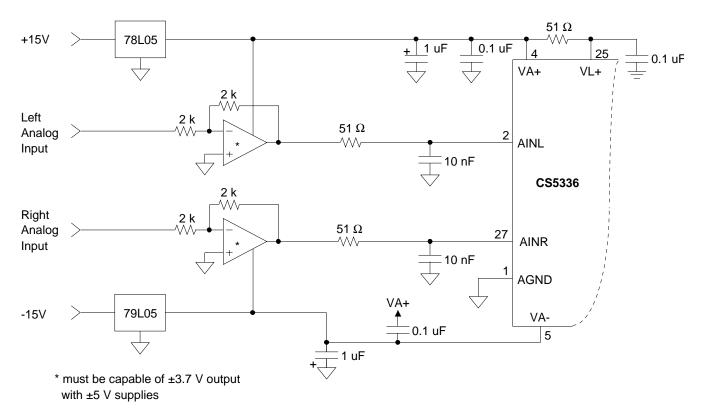

The goals of input protection can also be achieved by powering the input buffer from the same supplies as the converter as shown in Figure 4. This circuit requires fewer components than the circuit of Figure 1 and the use of common power supplies guarantees that the op-amp output will not exceed the ADC supply voltages. However, the required analog voltage to achieve full scale digital output for the CS5336 is typically  $\pm 3.68$  V and the majority of op-amps do not have this output capability with  $\pm 5$  V supplies.

The Motorola MC33078/9 is a viable contender for this application. Figure 5 shows the %THD vs Frequency of the MC33078 with  $\pm 15$  and  $\pm 5$  V supplies operating at 3.68 Vp. Note the lack of performance degradation resulting from the reduced supplies.

Figure 4. ADC Input Protection ±5 V Op-Amp

AN20REV2 3

Figure 5. %THD Effects of Power Supply Variation for MC33078 at ±15 V and ±5 V

The power supply voltages could be as low as 4.75 V due to the 5% tolerance of the 78L05/79L05. Figure 6 shows the increased %THD of the MC33078 at this supply voltage.

Due to the transient nature of audio signals, digital audio systems are generally operated at average levels 10 to 20 dB below full scale. This is to allow sufficient headroom to handle high amplitude transient signals. The increase in distortion at full scale due to regulator tolerances could be considered insignificant. If required, 2% regulators will avoid this increase in distortion.

### CONCLUSION

Two circuits have been described which utilize effective protection techniques. Use of either of these circuits or the techniques described will insure that the performance and reliability of a data acquisition system will not be limited by the input buffer and protection circuits.

Figure 6. %THD Effects of Power Supply Variation for MC33078 at ±15 V and ±4.75 V

### REFERENCES

- 1) Johnston, Jerome: ADC Input Buffers, Crystal Semiconductor Corp.

- Fredriksen, Thomas M.: Intuitive IC Op Amps, National Semiconductor Technology Series 1984

- Pease, Robert: Bounding, clamping techniques improve circuit performance, EDN Nov. 10, 1983

- 4) Pease, Robert: Active-component problems yield painstaking probing, EDN Aug. 3, 1989

- 5) Hewlett/Packard Components: Application Bulletin 14, Waveform Clipping With Schottky Diodes.

- 6) Hewlett/Packard Components: Application Bulletin 15, Waveform Clipping With Schottky Diodes.

- Hewlett/Packard Components: Application Note 942, Schottky Diodes for High Volume, Low Cost Applications

- 8) Application Note MSAN-107: Understanding and Eliminating Latch-up in CMOS Applications, MITEL August 1982

4 AN20REV2

• Notes •

# A STITIST MANAGEMENT OF THE PROPERTY OF THE PR