## CMOS 8-Bit Microcontroller

# TMP86FP24F

The TMP86FP24 is a Flash type MCU which includes 48 K bytes Flash memory. It is a pin compatible with a mask ROM product of the TMP86CP24. Writing the program to built-in Flash memory, the TMP86FP24 operates as the same way as the TMP86CP24. The TMP86FP24 has a 2 K bytes BOOT ROM (masked ROM) for programming to Flash memory.

| Product No. | Flash Memory         | BOOT ROM                            | RAM                                 | Package             |

|-------------|----------------------|-------------------------------------|-------------------------------------|---------------------|

| TMP86FP24F  | 48 K $\times$ 8 bits | $2 \text{ K} \times 8 \text{ bits}$ | $2 \text{ K} \times 8 \text{ bits}$ | P-LQFP80-1212-0.50A |

000707EBP1

For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.. The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document the test at the custometed our test. shall be made at the customer's own risk.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The products described in this document are subject to the foreign exchange and foreign trade laws. The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others

The information contained herein is subject to change without notice.

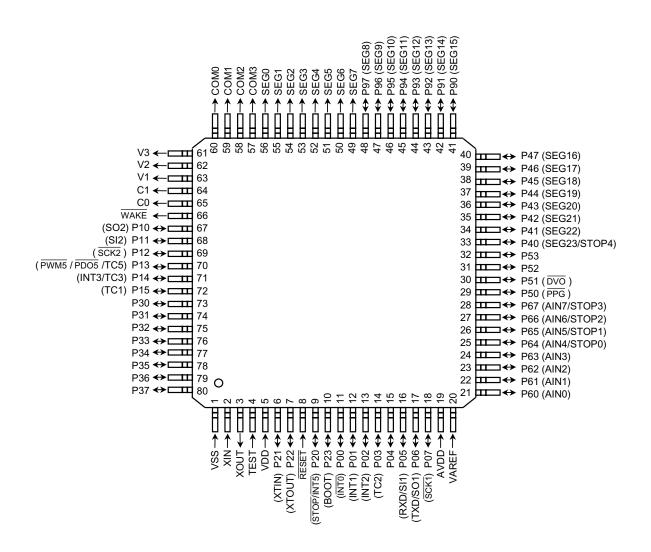

Pin Assignments (Top View)

P-LQFP80-1212-0.50A

Note: The mask ROM product (TMP86CP24) doesn't have a BOOT function in P23 pin.

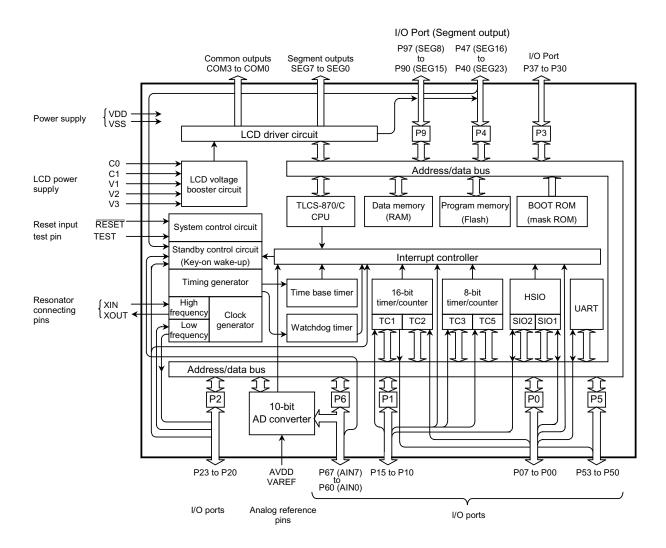

## Block Diagram

## **Pin Funtions**

The TMP86FP24 has MCU mode and serial PROM mode.

## (1)MCU mode

In the MCU mode, the TMP86FP24 is a pin compatible with the TMP86CP24 (Make sure to fix the TEST pin to low level).

(2)Serial PROM mode

In the Serial PROM mode, programming to Flash memory is available by executing BOOT ROM. For details, refer to "2.1 Serial PROM mode".

## 1.1 FLASH Memory

#### 1.1.1 Outline

The TMP86FP24 incorporates 49152 bytes of FLASH memory (address 4000H to FFFFH). The writing to FLASH is controlled by FLASH control register (EEPCR), FLASH status register (EEPSR) and FLASH write emulate time control register (EEPEVA).

To write data to the FLASH , execute the Serial PROM mode. For details about the Serial PROM mode, refer to "2.1 Serial PROM mode".

The FLASH memory of the TMP86FP24 features:

- The FLASH memory is constructed of 384 pages FLASH and one page size is 128 bytes (384 pages × 128 bytes = 49512 bytes).

- The TMP86FP24 incorporates a 128-byte temporary data buffer. The data written to FLASH is temporarily stored in this data buffer. After 128 bytes data have been written to the temporary data buffer, the writing to FLASH automatically starts by page writing (The 128 bytes data are written to specified page of FLASH simultaneously). At the same time, page-by-page erasing occurs automatically. So, it is unnecessary to erase individual pages in advance.

- The FLASH control circuit incorporates an oscillator dedicated to the FLASH. So FLASH writing time is independent of the system clock frequency (fc). In addition, because an FLASH control circuit controls writing time for each FLASH cell, the writing time varies in each page (Typically 4 ms per page).

- Controlling the power for the FLASH control circuit (regulator and voltage step-up circuit) achieves low power consumption if the FLASH is not in use (Example. When the program is executed in RAM area).

#### 1.1.2 Conditions for Accessing the FLASH Areas

The conditions for accessing the FLASH areas vary depending on each operation mode. The following tables shows FLASH are access conditions.

|              | Area           | Operation Mode    |                            |  |  |  |  |  |  |

|--------------|----------------|-------------------|----------------------------|--|--|--|--|--|--|

|              | Alea           | MCU mode (Note 1) | Serial PROM mode (Note 2)  |  |  |  |  |  |  |

| FLASH Memory | 4000H to FFFFH | Read/Fetch only   | Write/Read/Fetch supported |  |  |  |  |  |  |

Table 1.1.1 FLASH Area Access Conditions

Note1: "MCU mode" shows NORMAL1/2 and SLOW1/2 modes.

Note2: "Serial PROM mode" shows the FLASH controlling mode. For details, refer to "2.1 Serial PROM mode".

Note3: "Fetch" means reading operation of FLASH data as an instruction by CPU.

## 2.1 Serial PROM Mode

#### 2.1.1 Outline

The TMP86FP24 has a 2 Kbytes BOOT-ROM for programming to FLASH memory. This BOOT-ROM is a mask ROM that contains a program to write the FLASH memory on-board. The BOOT-ROM is available in a serial PROM mode and it is controlled by BOOT pin (P23) and RESET pin, and is communicated via TXD (P06) and RXD (P05) pins. There are four operation modes in a serial PROM mode: FLASH writing mode, RAM loader mode, FLASH memory SUM output mode and Product discrimination code output mode. Operating area of serial PROM mode differs from that of MCU mode. The operating area of serial PROM mode shows in Table 2.1.1.

| Parameter             | Min | Max | Unit |  |  |  |  |

|-----------------------|-----|-----|------|--|--|--|--|

| Operating voltage     | 2.7 | 3.6 | V    |  |  |  |  |

| High frequency (Note) | 2   | 16  | MHz  |  |  |  |  |

| Temperature           | 25  | °C  |      |  |  |  |  |

Table 2.1.1 Operating Area of Serial PROM Mode

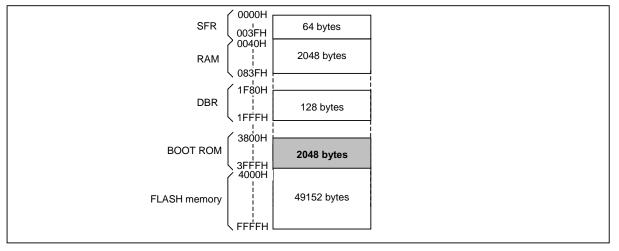

## 2.1.2 Memory Mapping

The BOOT-ROM is mapped in address 3800H to 3FFFH. The Figure 2.1.1 shows a memory mapping.

Figure 2.1.1 Memory Address Maps

#### 2.1.3 Serial PROM Mode Setting

#### 2.1.3.1 Serial PROM Mode Control Pins

To execute on-board programming, start the TMP86FP24 in serial PROM mode. Setting of a serial PROM mode is shown in Table 2.1.2.

| Pin            | Setting |

|----------------|---------|

| TEST pin       | High    |

| BOOT pin (P23) | High    |

| RESET pin      |         |

Table 2.1.2 Serial PROM Mode Setting

Note: Even though included in above operating area, part of frequency can not be supported in serial PROM mode. For details, refer to Table 2.1.4.

## **Electrical Characteristics**

Absolute Maximum Ratings  $(V_{SS} = 0 V)$

| Parameter                       | Symbol            | Pins                               | Rating                        | Unit |

|---------------------------------|-------------------|------------------------------------|-------------------------------|------|

| Supply voltage                  | V <sub>DD</sub>   |                                    | -0.3 to 4.0                   |      |

| Input voltage                   | VIN               |                                    | -0.3 to V <sub>DD</sub> + 0.3 | v    |

| Output valtage                  | V <sub>OUT1</sub> | Except V3 pin                      | -0.3 to V <sub>DD</sub> + 0.3 | v    |

| Output voltage                  | V <sub>OUT2</sub> | V3 pin                             | -0.3 to 4.0                   |      |

| Output current (Per 1 pin)      | I <sub>OUT1</sub> | P0, P1, P20, P23, P3, P5, P6 Ports | -2                            |      |

|                                 | I <sub>OUT2</sub> | P0, P1, P2, P4, P6, P9, WAKE Ports | 2                             |      |

|                                 | IOUT3             | P3, P5 Ports                       | 10                            |      |

|                                 | $\Sigma I_{OUT1}$ | P0, P1, P20, P23, P3, P5, P6 Ports | -80                           | mA   |

| Output current (Total)          | $\Sigma I_{OUT2}$ | P0, P1, P2, P4, P6, P9, WAKE Ports | 80                            |      |

|                                 | ΣΙΟυτ3            | P3, P5 Ports                       | 30                            |      |

| Power dissipation [Topr = 85°C] | PD                |                                    | 350                           | mW   |

| Soldering temperature (time)    | Tsld              |                                    | 260 (10 s)                    |      |

| Storage temperature             | Tstg              |                                    | -55 to 125                    | °C   |

| Operating temperature           | Topr              |                                    | -40 to 85                     |      |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

| Parameter                        | Symbol                               | Pins                                        | 0                                      | Condition                                       | Min                  | Max                                             | Unit |

|----------------------------------|--------------------------------------|---------------------------------------------|----------------------------------------|-------------------------------------------------|----------------------|-------------------------------------------------|------|

| Supply voltage V <sub>DD</sub>   |                                      |                                             | fc = 16 MHz                            | fc = 16 MHz NORMAL1, 2 mode<br>IDLE0, 1, 2 mode |                      |                                                 |      |

|                                  | V <sub>DD</sub>                      |                                             | fc = 8 MHz                             | NORMAL1, 2 mode<br>IDLE0, 1, 2 mode             | 1.8                  | 3.6                                             |      |

|                                  |                                      |                                             | fs =<br>32.768 kHz                     | SLOW1, 2 mode<br>SLEEP0, 1, 2 mode<br>STOP mode | 1.8                  |                                                 | v    |

|                                  | V <sub>IH1</sub>                     | Except hysteresis input                     |                                        |                                                 | $V_{DD} \times 0.70$ |                                                 | ľ    |

| nput high level V <sub>IH2</sub> |                                      | Hysteresis input                            | V <sub>DD</sub> ≥ 2.7 V                | V <sub>DD</sub> ≥ 2.7 V                         |                      | V <sub>DD</sub>                                 |      |

| V <sub>IH3</sub>                 | V <sub>IH3</sub>                     |                                             | $V_{DD}$ < 2.7 V                       | V <sub>DD</sub> < 2.7 V                         |                      |                                                 |      |

| Input low level                  | V <sub>IL1</sub><br>V <sub>IL2</sub> | Except hysteresis input<br>Hysteresis input | V <sub>DD</sub> ≥ 2.7 V                |                                                 |                      | $\frac{V_{DD} \times 0.30}{V_{DD} \times 0.25}$ | -    |

|                                  | V <sub>IL3</sub>                     |                                             | V <sub>DD</sub> < 2.7 V                |                                                 | -                    | V <sub>DD</sub> × 0.20                          |      |

| Clock frequency                  | fc                                   | XIN, XOUT                                   | $V_{DD} = 1.8$ to<br>$V_{DD} = 2.7$ to |                                                 | 1.0                  | 8.0<br>16.0                                     | MHz  |

|                                  | fs                                   | XTIN, XTOUT                                 | V <sub>DD</sub> = 1.8 to               | 3.6 V                                           | 30.0                 | 34.0                                            | kHz  |

| LCD reference                    | V1                                   |                                             | Booster circu                          | Booster circuit is enable                       |                      | 1.2                                             | v    |

| voltage                          | V2                                   |                                             | $(V3 \ge V_{DD})$                      | (V3 ≥ V <sub>DD</sub> )                         |                      | 2.4                                             | v    |

| Capacity for LCD booster circuit | C <sub>LCD</sub>                     |                                             | LCD booster<br>(V3 ≥ V <sub>DD</sub> ) | circuit is enable                               | 0.1                  | 0.47                                            | μF   |

Recommended Operating Condition-1  $(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

Note: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

| Recommended Operating Condition-2 (Serial PROM mode) | $(V_{SS} = 0 V, Topr = 25^{\circ}C \pm 5^{\circ}C)$ |

|------------------------------------------------------|-----------------------------------------------------|

|------------------------------------------------------|-----------------------------------------------------|

| Parameter       | Symbol | Pins      | Condition          | Min | Max  | Unit |

|-----------------|--------|-----------|--------------------|-----|------|------|

| Supply voltage  | VDD    |           | 2 MHz ≤ fc ≤ 16MHz | 2.7 | 3.6  | V    |

| Clock frequency | fc     | XIN, XOUT | VDD = 2.7 to 3.6 V | 2.0 | 16.0 | MHz  |

Note: The operating temperature area of serial PROM mode is  $25^{\circ}C \pm 5^{\circ}C$  and the operating area of high frequency of serial PROM mode is different from MCU mode.

| Parameter                           | Symbol              |                                 | Pir                 | าร                                          | Condition                                                                                                     |                                                  | Min    | Тур.             | Max    | Unit    |

|-------------------------------------|---------------------|---------------------------------|---------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------|------------------|--------|---------|

| Hysteresis voltage                  | V <sub>HS</sub>     | Hyste                           | eresis inp          | out                                         | $V_{DD} = 3.3 V$                                                                                              |                                                  | -      | 0.4              | I      | V       |

|                                     | I <sub>IN1</sub>    | TEST                            | -                   |                                             | $V_{DD} = 3.6 \text{ V}, \text{ V}_{IN}$                                                                      | = 0 V                                            | _      | -                | -5     |         |

| Input current                       | I <sub>IN2</sub>    | Sink-open drain, Tri-state      |                     |                                             | $V_{DD}=3.6$ V, $V_{IN}=3.6$ V/0 V                                                                            |                                                  | _      | -                | ±5     | μA      |

|                                     | I <sub>IN4</sub>    | RESE                            | T                   |                                             | $V_{DD} = 3.6 \text{ V}, \text{ V}_{IN}$                                                                      | = 3.6 V                                          | _      | -                | +5     |         |

|                                     | R <sub>IN1</sub>    | TEST pull-down                  |                     |                                             | $V_{DD}=3.6~V,~V_{IN}$                                                                                        | = 3.6 V                                          | _      | 70               | -      |         |

| Input resistance                    | R <sub>IN2</sub>    |                                 | T pull-L<br>P22 por | •                                           | $V_{DD}=3.6~V,~V_{IN}$                                                                                        | = 0 V                                            | 100    | 220              | 450    | kΩ      |

|                                     | R <sub>IN3</sub>    |                                 | ammabl<br>29 ports  | e pull-down<br>)                            |                                                                                                               |                                                  | _      | T.B.D.           | Ι      |         |

| High frequency<br>feedback resister | R <sub>FB</sub>     | XOU.                            | Г                   |                                             | $V_{DD} = 3.6 V$                                                                                              |                                                  | _      | 1.2              | -      | Мо      |

| Low frequency<br>feedback resister  | R <sub>FBT</sub>    | хтоі                            | JT                  |                                             | $V_{DD} = 3.6 V$                                                                                              |                                                  | -      | 14               | Ι      | MΩ      |

| Output leakage                      | l. a                | Sink                            | onon dri            | ain, Tri-state                              | $V_{DD} = 3.6 \text{ V}$                                                                                      |                                                  |        |                  | ±10    | μA      |

| current                             | ILO                 | SITIK-                          | openuia             | ani, m-siale                                | $V_{OUT} = 3.4 V / 0.2$                                                                                       | V                                                | -      | _                | ±ΙΟ    | μΑ      |

| Output high voltage                 | VOH                 | C-MOS, Tri-state                |                     |                                             | $V_{DD}=3.6~V,~I_{OH}=$                                                                                       | = -0.6 mA                                        | 3.2    | -                | -      |         |

| Output low voltage                  | V <sub>OL</sub>     | Except XOUT, P3 and P5<br>Ports |                     |                                             | $V_{DD} = 3.6 \text{ V}, \text{ I}_{OL} =$                                                                    | = 0.9 mA                                         | _      | -                | 0.4    | V       |

| Output low current                  | I <sub>OL</sub>     | P3, P5 ports                    |                     |                                             | $V_{DD} = 3.6 \text{ V}, \text{ V}_{OL}$                                                                      | / <sub>DD</sub> = 3.6 V, V <sub>OL</sub> = 1.0 V |        | 6                | -      | mA      |

| (LCD booster is                     | V <sub>2-3OUT</sub> | V2 pin<br>V3 pin                |                     | $V3 \ge V_{DD}$<br>Reference supply pin: V1 |                                                                                                               | -                                                | V1×2   | -                | _      |         |

|                                     | ¥2-3001             |                                 |                     | SEG/COM pin: No-lo                          | bad                                                                                                           | -                                                | V1×3   | -                | v      |         |

|                                     | V <sub>1-3OUT</sub> |                                 | V1 pin              |                                             | V3 ≥ V <sub>DD</sub><br>Reference supply pin: V2                                                              |                                                  | -      | V2 × 1/2         | -      | -       |

|                                     |                     | V3 pin                          |                     |                                             | SEG/COM pin: No-load                                                                                          |                                                  | _      | V2×3/2           | -      |         |

|                                     |                     |                                 |                     |                                             | V <sub>DD</sub> = 3.6 V<br>fc = 16 MHz<br>C <sub>LCD</sub> = 0.1 μF                                           | <vfsel> = 00</vfsel>                             | -      | T.B.D.<br>T.B.D. | -      | -       |

|                                     |                     |                                 |                     | <vfsel> = 01</vfsel>                        |                                                                                                               | _                                                | T.B.D. |                  |        |         |

| LCD output current<br>capacity      |                     |                                 | V3 pin              |                                             | Reference supply pin:<br>V1 = 1V<br>VDD = 3.6 V<br>fc = 16 MHz<br>CLCD = 0.1 $\mu$ F<br>Reference supply pin: | <vfsel> = 10<br/><vfsel> = 11</vfsel></vfsel>    | _      | T.B.D.           | _      | _ mV/μA |

| (LCD booster is                     | I <sub>LCDV3</sub>  | V3 pi                           |                     |                                             |                                                                                                               | <vfsel> = 00</vfsel>                             | _      | T.B.D.           | -      |         |

| enable)                             |                     |                                 |                     |                                             |                                                                                                               | <vfsel> = 00</vfsel>                             | _      | T.B.D.           | -      |         |

|                                     |                     |                                 |                     |                                             |                                                                                                               | <vfsel> = 10</vfsel>                             | _      | T.B.D.           | -      |         |

|                                     |                     |                                 |                     |                                             | Reference supply pin:<br>V2 = 2 V                                                                             | <vfsel> = 11</vfsel>                             | _      | T.B.D.           | _      |         |

|                                     |                     |                                 |                     | Flash area                                  |                                                                                                               | MNP = "1"                                        | _      | T.B.D.           | T.B.D. |         |

| Supply current in                   |                     |                                 | Fetch               |                                             | V <sub>DD</sub> = 3.6 V                                                                                       | MNP = "0"                                        | _      | T.B.D.           | T.B.D. | mA      |

| NORMAL1, 2 mode                     |                     |                                 | area                | RAM area                                    | $V_{IN} = 3.4 \text{ V}/0.2 \text{ V}$                                                                        | MNP = "1"                                        | _      | T.B.D.           | T.B.D. |         |

| Supply current in                   |                     |                                 |                     | •                                           | fc = 16 MHz<br>fs = 32.768 kHz                                                                                | MNP·ATP = "1"                                    | _      | T.B.D.           | T.B.D. |         |

| IDLE0, 1, 2 mode                    |                     |                                 |                     |                                             | 15 – 52.700 KHZ                                                                                               | MNP·ATP = "0"                                    | _      | T.B.D.           | T.B.D. |         |

|                                     |                     |                                 |                     | Flash area                                  |                                                                                                               | MNP = "1"                                        | _      | T.B.D.           | T.B.D. |         |

| Supply current in                   | 1                   |                                 | Fetch               | DAMAST                                      |                                                                                                               | MNP = "0"                                        | _      | T.B.D.           | T.B.D. | -       |

| SLOW1 mode                          | IDD                 |                                 | area                | RAM area                                    | $V_{DD} = 3.6 V$                                                                                              | MNP = "1"                                        | _      | T.B.D.           | T.B.D. |         |

| Supply current in                   |                     |                                 |                     |                                             | $V_{IN} = 3.4 \text{ V/0.2 V}$                                                                                | MNP·ATP = "1"                                    | -      | T.B.D.           | T.B.D. |         |

| SLEEP1 mode                         |                     |                                 |                     |                                             | fs = 32.768 kHz                                                                                               | MNP·ATP = "0"                                    | _      | T.B.D.           | T.B.D. | μA      |

| Supply current in                   |                     |                                 |                     |                                             |                                                                                                               | MNP·ATP = "1"                                    | _      | T.B.D.           | T.B.D. |         |

| SLEEP0 mode                         |                     |                                 |                     |                                             |                                                                                                               | MNP·ATP = "0"                                    | _      | T.B.D.           | T.B.D. |         |

| Supply current in<br>STOP mode      |                     |                                 |                     |                                             | V <sub>DD</sub> = 3.6 V<br>V <sub>IN</sub> = 3.4 V/0.2 V                                                      |                                                  | _      | T.B.D.           | T.B.D. |         |

| DC Characteristics $  (V_{SS} = 0 V, Topr = -40 \text{ to } 85^{\circ}C)  $ |

|-----------------------------------------------------------------------------|

|-----------------------------------------------------------------------------|

Note 1: Typical values show those at Topr =  $25^{\circ}$ C, V<sub>DD</sub> = 3.3 V.

Note 2: Input current (I<sub>IN1</sub>, I<sub>IN2</sub>): The current through pull-up or pull-down resistor is not included.

Note 3:  $I_{DD}$  does not include  $I_{REF}$  current.

Note 4: The supply currents of SLOW 2 and SLEEP 2 modes are equivalent to IDLE0, 1, 2.

Note 5: Current capacity indicates the drop in pin V3 output voltage per 1μA. Select an appropriate booster frequency setting in LCDCR<VFSEL> according to LCD panel. To maintain stable operation, the current capacity for the reference pin must be more than ten times that of the output current capacity.

Note 6: MNP (MNPWDW) shows bit0 in EEPCR register and ATP (ATPWDW) shows bit1 in EEPCR register.

Note 7: "Fetch" means reading operation of FLASH data as an instruction by CPU.

AD Conversion Characteristics | (V<sub>SS</sub> = 0.0 V, 2.7 V  $\leq$  V<sub>DD</sub>  $\leq$  3.6 V, Topr = -40 to 85°C)

| Parameter                                         | Symbol            | Condition                                                              | Min                    | Тур.            | Max    | Unit |

|---------------------------------------------------|-------------------|------------------------------------------------------------------------|------------------------|-----------------|--------|------|

| Analog reference voltage                          | VAREF             |                                                                        | A <sub>VDD</sub> - 1.0 | -               | Avdd   |      |

| Power supply voltage of analog<br>control circuit | A <sub>VDD</sub>  |                                                                        |                        | V <sub>DD</sub> |        | V    |

| Analog reference voltage range<br>(Note 4)        | $\Delta V_{AREF}$ |                                                                        | 2.5                    | -               | -      | V    |

| Analog input voltage                              | VAIN              |                                                                        | V <sub>SS</sub>        | -               | VAREF  |      |

| Power supply current of analog reference voltage  | I <sub>REF</sub>  | $V_{DD} = A_{VDD} = V_{AREF} = 3.6 \text{ V}$ $V_{SS} = 0.0 \text{ V}$ | _                      | T.B.D.          | T.B.D. | mA   |

| Non linearity error                               |                   | V <sub>D</sub> = A <sub>VD</sub> = 2.7 V                               | -                      | -               | ±2     |      |

| Zero point error                                  |                   | 55 155                                                                 | _                      | -               | ±2     |      |

| Full scale error                                  |                   | $V_{SS} = 0.0 V$                                                       | -                      | -               | ±2     | LSB  |

| Total error                                       |                   | V <sub>AREF</sub> = 2.7 V                                              | _                      | _               | ±2     |      |

$(V_{SS} = 0.0 \text{ V}, 2.0 \text{ V} \le V_{DD} < 2.7 \text{ V}, \text{ Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                                        | Symbol            | Condition                                             | Min                    | Тур.            | Max              | Unit |

|--------------------------------------------------|-------------------|-------------------------------------------------------|------------------------|-----------------|------------------|------|

| Analog reference voltage                         | VAREF             |                                                       | A <sub>VDD</sub> - 0.6 | -               | A <sub>VDD</sub> |      |

| Power supply voltage of analog control circuit   | A <sub>VDD</sub>  |                                                       |                        | V <sub>DD</sub> |                  | V    |

| Analog reference voltage range<br>(Note 4)       | $\Delta V_{AREF}$ |                                                       | 2.0                    | -               | -                | V    |

| Analog input voltage                             | VAIN              |                                                       | V <sub>SS</sub>        | -               | VAREF            |      |

| Power supply current of analog reference voltage | I <sub>REF</sub>  | $V_{DD} = A_{VDD} = V_{AREF} = 2.0V$ $V_{SS} = 0.0 V$ | -                      | T.B.D.          | T.B.D.           | mA   |

| Non linearity error                              |                   | V <sub>D</sub> = A <sub>VD</sub> = 2.0 V              | _                      | -               | ±4               |      |

| Zero point error                                 |                   | 55 155                                                | _                      | -               | ±4               | LSB  |

| Full scale error                                 |                   | $V_{SS} = 0.0 V$                                      | -                      | -               | ±4               | LOB  |

| Total error                                      |                   | V <sub>AREF</sub> = 2.0 V                             | _                      | _               | <u>+</u> 4       |      |

$(V_{SS} = 0.0 \text{ V}, 1.8 \text{ V} \le V_{DD} < 2.0 \text{ V}, \text{ Topr} = -10 \text{ to } 85^{\circ}\text{C}) \text{ (Note 5)}$

|                                                  |                   |                                                          | -                      |                 |                  | -    |

|--------------------------------------------------|-------------------|----------------------------------------------------------|------------------------|-----------------|------------------|------|

| Parameter                                        | Symbol            | Condition                                                | Min                    | Тур.            | Max              | Unit |

| Analog reference voltage                         | VAREF             |                                                          | A <sub>VDD</sub> - 0.1 | -               | A <sub>VDD</sub> |      |

| Power supply voltage of analog control circuit   | A <sub>VDD</sub>  |                                                          |                        | V <sub>DD</sub> |                  | V    |

| Analog reference voltage range<br>(Note 4)       | $\Delta V_{AREF}$ |                                                          | 1.8                    | -               | -                | V    |

| Analog input voltage                             | VAIN              |                                                          | V <sub>SS</sub>        | Ι               | VAREF            |      |

| Power supply current of analog reference voltage | I <sub>REF</sub>  | $V_{DD} = A_{VDD} = V_{AREF} = 1.8V$<br>$V_{SS} = 0.0 V$ | _                      | T.B.D.          | T.B.D.           | mA   |

| Non linearity error                              |                   | V <sub>D</sub> = A <sub>VD</sub> = 1.8 V                 | _                      | -               | ±4               |      |

| Zero point error                                 |                   | $V_{SS} = 0.0 V$                                         | _                      | -               | ±4               | LSB  |

| Full scale error                                 |                   |                                                          | _                      | _               | ±4               | LOB  |

| Total error                                      |                   | V <sub>AREF</sub> = 1.8 V                                | _                      | -               | ±4               |      |

Note 1: The total error includes all errors except a quantization error, and is defined as a maximum deviation from the ideal conversion line.

- Note 2: Conversion time is different in recommended value by power supply voltage. About conversion time, please refer to "2.12.2 Register Configuration".

- Note 3: Please use input voltage to AIN input Pin in limit of V<sub>AREF</sub> V<sub>SS</sub>. When voltage of range outside is input, conversion value becomes unsettled and gives affect to other channel conversion value.

- Note 4: Analog Reference Voltage Range:  $\Delta V_{AREF} = V_{AREF} V_{SS}$ .

- Note 5: When AD is used with  $V_{DD}$  < 2.0 V, the guaranteed temperature range varies with the operating voltage.

- Note 6: When AD converter is not used, fix the  $A_{VDD}$  pin on the  $V_{DD}$  level.

AC Characteristics  $(V_{SS} = 0 V, V_{DD} = 2.7 \text{ to } 3.6 V, \text{Topr} = -40 \text{ to } 85^{\circ}\text{C})$

| Parameter                        | Symbol | Condition                          | Min   | Тур.  | Max   | Unit |

|----------------------------------|--------|------------------------------------|-------|-------|-------|------|

| Machine cycle time               | tcy    | NORMAL1, 2 mode<br>IDLE1, 2 mode   | 0.25  | -     | 4     | μs   |

|                                  |        | SLOW1, 2 mode                      | 117.6 | -     | 133.3 |      |

|                                  |        | SLEEP1, 2 mode                     | 117.0 |       |       |      |

| High level clock pulse width     | twcH   | For external clock operation (XIN  |       |       |       |      |

| Low level clock pulse width twcL |        | input)<br>fc = 16 MHz              | -     | 31.25 | -     | ns   |

| High level clock pulse width     | twcH   | For external clock operation (XTIN |       |       |       |      |

| Low level clock pulse width      | twcL   | input)<br>fs = 32.768 kHz          | -     | 15.26 | -     | μS   |

| Parameter                                                   | Symbol       | Condition                                                       | Min   | Тур.  | Max   | Unit |  |

|-------------------------------------------------------------|--------------|-----------------------------------------------------------------|-------|-------|-------|------|--|

| Machine cycle time                                          | 4            | NORMAL1, 2 mode<br>IDLE1, 2 mode                                | 0.5   | -     | 4     |      |  |

|                                                             | tcy          | SLOW1, 2 mode<br>SLEEP1, 2 mode                                 | 117.6 | -     | 133.3 | μS   |  |

| High level clock pulse width<br>Low level clock pulse width | twcH<br>twcL | For external clock operation (XIN input)<br>fc = 8 MHz          | _     | 62.5  | _     | ns   |  |

| High level clock pulse width<br>Low level clock pulse width | twcH<br>twcL | For external clock operation (XTIN<br>input)<br>fs = 32.768 kHz | _     | 15.26 | _     | μs   |  |

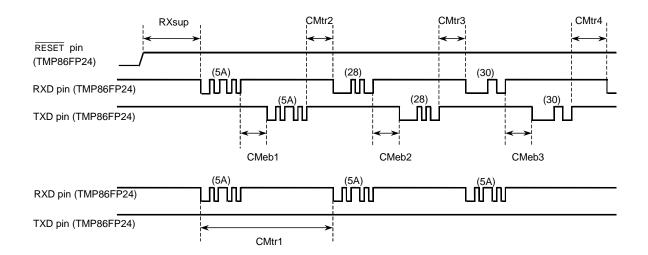

# UART Timing in Serial PROM Mode

UART Timing-1

(VDD = 2.7 V to 3.6 V, fc = 2 MHz to 16 MHz,Ta = 25°C)

| Parameter                                                                                    | Symbol | The Number of   | Required Minimum Time |                |  |

|----------------------------------------------------------------------------------------------|--------|-----------------|-----------------------|----------------|--|

| Falameter                                                                                    |        | Clock (fc)      | at fc = 2 MHz         | at fc = 16 MHz |  |

| Time from the reception of a matching data until the output of an echo back                  | CMeb1  | Approx. 600     | 300 μs                | 37.5 μs        |  |

| Time from the reception of a Baud Rate Modification<br>Data until the output of an echo back | CMeb2  | Approx. 700     | 350 μs                | 43.7 μs        |  |

| Time from the reception of an operation command until the output of an echo back             | CMeb3  | Approx. 600     | 300 µs                | 37.5 μs        |  |

| Calculation time of checksum                                                                 | CKsm   | Approx. 2360000 | 1180 ms               | 147.5 ms       |  |

UART Timing-2

(VDD = 2.7 V to 3.6 V, fc = 2 MHz to 16 MHz,Ta = 25°C)

| Parameter                                                        |           | The Number                                                                                                                                                                                                                   | Required Minimum Time |                |  |

|------------------------------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------|--|

|                                                                  | Symbol    | of Clock (fc)                                                                                                                                                                                                                | at fc = 2 MHz         | at fc = 16 MHz |  |

| Time from reset release until acceptance of start bit of RXD pin |           | 110000                                                                                                                                                                                                                       | 55 ms                 | 6.9 ms         |  |

| Time between a matching data and the next matching data          |           | 28500                                                                                                                                                                                                                        | 14.3 ms               | 1.8 ms         |  |

| Time from the echo back of matching data until the acceptance    | CMtr2     | 600                                                                                                                                                                                                                          | 300                   | 37.5 μs        |  |

| of baud rate modification data                                   | Civitiz   | of Clock (fc)         at fc = 2 MHz         at fc           110000         55 ms         6           28500         14.3 ms         1           600         300 $\mu$ s         3           750         375 $\mu$ s         4 | 57.5 μ5               |                |  |

| Time from the output of echo back of baud rate modification      | CMtr3 750 | 750                                                                                                                                                                                                                          | 375 μs                | 46.9 μs        |  |

| data until the acceptance of an operation command                |           | 750                                                                                                                                                                                                                          |                       | 40.9 μs        |  |

| Time from the output of echo back of operation command until     | CMtr4     | 050                                                                                                                                                                                                                          | 4750                  | 50.40          |  |

| the acceptance of Password count storage addresses               | CIVILI4   | 950                                                                                                                                                                                                                          | 475 µs                | 59.4 μs        |  |

#### **Recommended Oscillating Conditions**

- Note 1: An electrical shield by metal shield plate on the surface of IC package is recommended in order to protect the device from the high electric field stress applied from CRT (Cathodic Ray Tube) for continuous reliable operation.

- Note 2: The product numbers and specifications of the resonators by Murata Manufacturing Co., Ltd. are subject to change. For up-to-date information, please refer to the following http://www.murata.co.jp/search/index.html