# MICROCIRCUIT DATA SHEET

Original Creation Date: 07/17/98 Last Update Date: 04/05/99 Last Major Revision Date: 09/24/98

# HIGH-SPEED 2:1 ANALOG MULTIPLEXER

#### General Description

MNCLC532A-X REV 0A0

The CLC532 is a high-speed 2:1 multiplexer with active input and output stages. The CLC532 also employs a closed-loop design which dramatically improves accuracy. This accurate monolithic device is constructed using an advanced high-performance bipolar process.

The CLC532 has been specifically designed to provide settling times of 17ns to 0.01%. This design, coupled with the adjustable noise bandwidth, makes the CLC532 an ideal choice for infrared and CCD imaging systems. Channel-to-channel isolation is better than 80dB @ 10 MHz. Low distortion (80dBc) and spurious signal levels make the CLC532 a very suitable choice for both I/Q processors and receivers.

#### Industry Part Number

NS Part Numbers

CLC532A

CLC532AE-QML\*\* CLC532AJ-QML\*

Prime Die

UB1451A

#### Controlling Document

5962-9203501MCA\*, M2A\*\*

| Processing                     | Subgrp              | Description                                                                                                  | Temp ( $^{\circ}$ C)              |

|--------------------------------|---------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------|

| MIL-STD-883, Method 5004       | 1<br>2<br>3         | Static tests at<br>Static tests at<br>Static tests at                                                        | +25<br>+125<br>-55                |

| Quality Conformance Inspection | 4<br>5              | Dynamic tests at<br>Dynamic tests at                                                                         | +25<br>+125                       |

| MIL-STD-883, Method 5005       | 6<br>7<br>8A        | Dynamic tests at Functional tests at Functional tests at                                                     | -55<br>+25<br>+125                |

|                                | 8B<br>9<br>10<br>11 | Functional tests at<br>Functional tests at<br>Switching tests at<br>Switching tests at<br>Switching tests at | +125<br>-55<br>+25<br>+125<br>-55 |

|                                |                     | -                                                                                                            |                                   |

### **Features**

- 12-bit settling (0.01%) 17ns

- Low noise 32uVrms

- High isolation 80dB @ 10MHz

- Low distortion 80dB @ 5MHz

- Adjustable bandwidth 190MHz (max)

# Applications

- Infrared system multiplexing

- CCD sensor signals

- Radar I/Q switching

- High definition video HDTV

- Test and calibration

# (Absolute Maximum Ratings)

(Note 1)

```

Positive Supply Voltage (+Vcc)

-0.5V to +7.0V

Negative Supply Voltage (-Vee)

+0.5V to -7.0V

Differential Voltage Between Any Two Ground Pins

200mV

Analog Input Voltage Range

-Vee to +Vcc

Digital Input Voltage Range

-Vee to +Vcc

Maximum Power Dissipation (Pd)

(Note 2)

1.76 W

Ceramic DIP

LCC

3.0 W

Output Current (Iout)

36mA

Output Short Circuit Duration (output shorted to GND)

Infinite

Junction Temperature (Tj)

+175 C

Storage Temperature Range

-65 C to +150 C

Lead Temperature (soldering, 10 seconds)

+300 C

Thermal Resistance

Junction -to-ambient (ThetaJA)

Ceramic DIP

(Still Air)

TBD

(500 LFPM)

TBD

LCC

(Still Air)

TBD

(500 LFPM)

TBD

Junction -to-case

(ThetaJC)

Ceramic DIP

TBD

LCC

TBD

Package Weight

(Typical)

2190 mg

Ceramic DIP

LCC

TBD

ESD Tolerance

ESD Rating

500 V

```

- Note 1: Absolute Maximum Ratings are limits beyond which damage to the device may occur. Operating Ratings are conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- Note 2: The maximum power dissipation must be derated at elevated temperatures and is dictated by Tjmax (maximum junction temperature), ThetaJA (package junction to ambient thermal resistance), and TA (ambient temperature). The maximum allowable power dissipation at any temperature is Pdmax = (Tjmax TA) / ThetaJA or the number given in the Absolute Maximum Ratings, whichever is lower.

- Note 3: Human body model, 100pF discharged through 1.5K Ohms.

# Recommended Operating Conditions

Positive Supply Voltage (+Vcc) +5.0V

Negative Supply Voltage (-Vee)

-5.2V or -5.0V

Differential Voltage Between Any Two Ground Pins  $$10 \mathrm{mV}$$

Analog Input Voltage Range  $$\pm 2V$$

SELECT Input Voltage Range (TTL Mode) 0V to +3.0V

SELECT Input Voltage Range (ECL Mode)  $-2.0 \mbox{V to } 0 \mbox{V}$

COMPENSATION Capacitance Range (Ccomp)  $$\operatorname{\textsc{OMPENSATION}}$$  OpF to 100pF

Ambient Operating Temperature Range (Ta)  $$-55\ \mbox{C}$$  to +125  $\mbox{C}$

# Electrical Characteristics

### DC PARAMETERS

(The following conditions apply to all the following parameters, unless otherwise specified.) DC: +Vs = +5.0V, -Vs = -5.2V, Rin = 500hms, Rl = 5000hms, Ccomp = 10pF, and ECL mode, pin 6 = no connection. See figure 3. -55 C  $\leq$  Ta  $\leq$  +125 C (Note 3).

| SYMBOL         | PARAMETER                       | CONDITIONS                            | NOTES | PIN-<br>NAME | MIN  | MAX   | UNIT | SUB-<br>GROUPS |

|----------------|---------------------------------|---------------------------------------|-------|--------------|------|-------|------|----------------|

| IBN            | Input Bias<br>Current           |                                       |       |              | -120 | +120  | uA   | 1, 2           |

|                |                                 |                                       |       |              | -250 | +250  | uA   | 3              |

| Voo            | Output Offset<br>Voltage        |                                       |       |              | -3.5 | +3.5  | mV   | 1, 2           |

|                |                                 |                                       |       |              | -6.5 | +6.5  | mV   | 3              |

| Icc            | Supply Current                  | Vcc = +5V, Vin = 0V, no load          |       |              | 18   | 28    | mA   | 1              |

|                |                                 |                                       |       |              | 16   | 25    | mA   | 2              |

|                |                                 |                                       |       |              | 18   | 30    | mA   | 3              |

| Iee            | Supply Current                  | Vee = -5.2V, Vin = 0V, no load        |       |              | -30  | -19   | mA   | 1              |

|                |                                 |                                       |       |              | -26  | -16   | mA   | 2              |

|                |                                 |                                       |       |              | -31  | -19   | mA   | 3              |

| PSRR           | Power Supply<br>Rejection Ratio |                                       |       |              |      | -63   | dB   | 1              |

| Rejection Rati | nejeeten naere                  |                                       |       |              |      | -64   | dВ   | 2              |

|                |                                 |                                       |       |              |      | -60   | dВ   | 3              |

| GA             | Gain Accuracy                   | ±2V                                   |       |              | .988 | 1.000 | V/V  | 1, 2,          |

| SSBW           | Small Signal<br>Bandwidth       | -3 dB Bandwidth, Vout < 0.1 Vpp       |       |              | 140  |       | MHz  | 4              |

|                | Ballawiach                      |                                       | 2     |              | 110  |       | MHz  | 5              |

|                |                                 |                                       | 2     |              | 140  |       | MHz  | 6              |

| GFP            | Gain Flatness                   | Vout < 0.1 Vpp, at 0.1 MHz to 200 MHz |       |              |      | 0.7   | dB   | 4              |

| Peaking        | reaking                         |                                       | 2     |              |      | 0.8   | dB   | 5              |

|                |                                 |                                       | 2     |              |      | 0.7   | dВ   | 6              |

| GFR            | Gain Flatness<br>Rolloff        | Vout < 0.1 Vpp, at 0.1 MHz to 100 MHz |       |              | -1.8 |       | dB   | 4              |

| ROTTOTT        | ROTTOTT                         |                                       | 2     |              | -2.6 |       | dВ   | 5              |

|                |                                 |                                       | 2     |              | -1.8 |       | dВ   | 6              |

| HD2            | 2nd Harmonic<br>Distortion      | 2 Vpp at 5 MHz                        |       |              |      | -67   | dBc  | 4              |

|                |                                 |                                       | 2     |              |      | -67   | dBc  | 5, 6           |

| HD3            | 3rd Harmonic<br>Distortion      | 2 Vpp at 5 MHz                        |       |              |      | -68   | dBc  | 4              |

|                |                                 |                                       | 2     |              |      | -68   | dBc  | 5, 6           |

Note 1: If not tested, shall be guaranteed to the limits specified in table  ${\tt I}$

Note 2: Group A testing only.

Note 3: The algebraic convention, whereby the most negative value is a minimum and most positive is a maximum, is used in this table. Negative current shall be defined as convential current flow out of a device terminal.

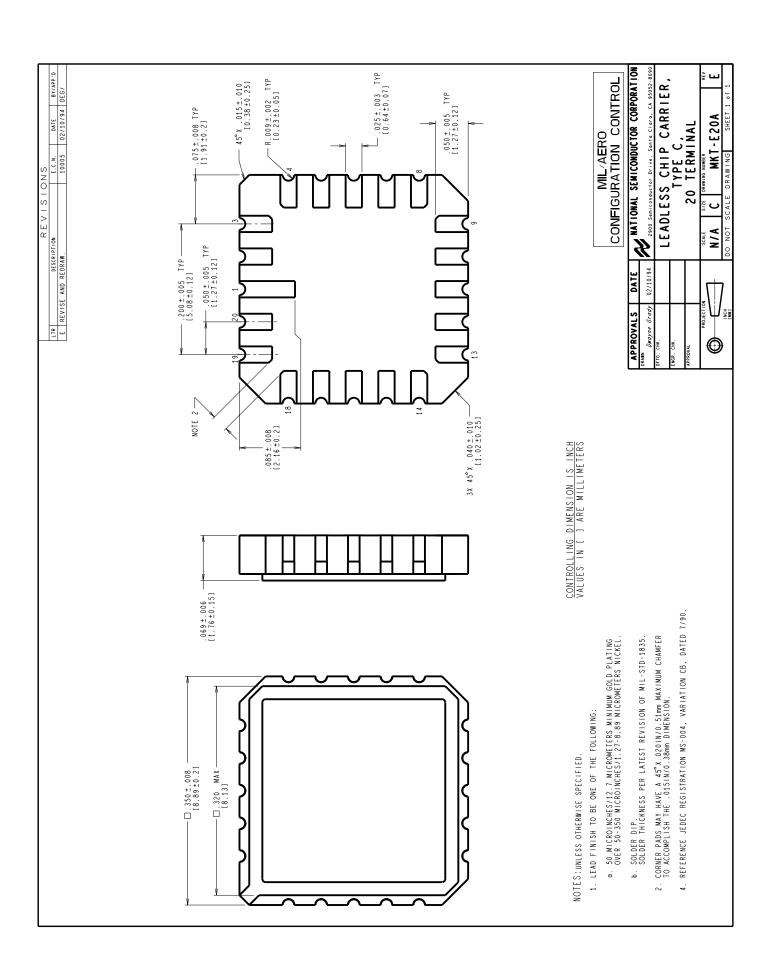

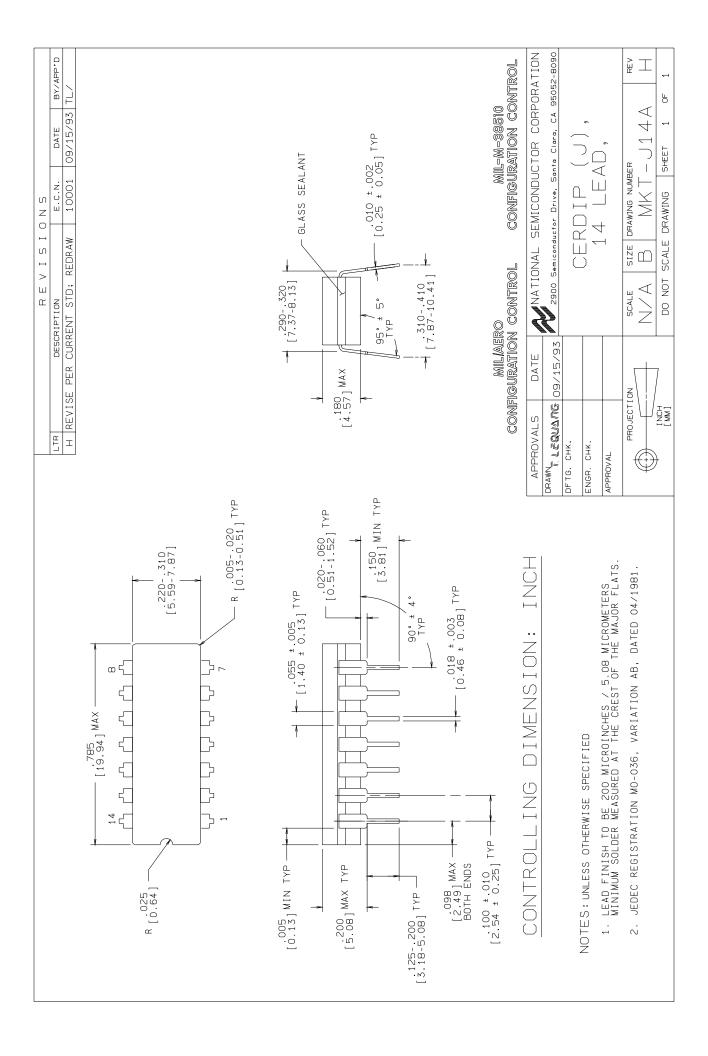

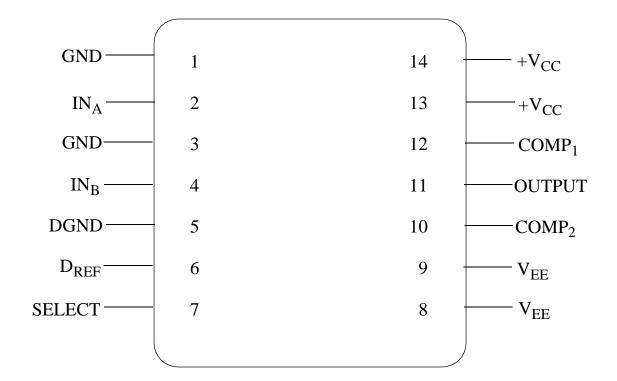

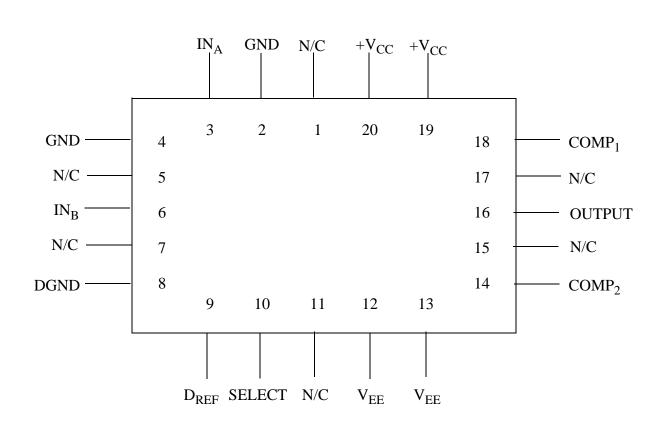

# Graphics and Diagrams

| GRAPHICS# | DESCRIPTION                            |  |

|-----------|----------------------------------------|--|

| 07067HRA2 | CERDIP (J), 14 LEAD (B/I CKT)          |  |

| 07074HRA2 | LCC (E), TYPE C, 20 TERMINAL (B/I CKT) |  |

| E20ARE    | LCC (E), TYPE C, 20 TERMINAL(P/P DWG)  |  |

| J14ARH    | CERDIP (J), 14 LEAD (P/P DWG)          |  |

| P000398A  | CERDIP (J), 14 LEAD (PINOUT)           |  |

| P000399A  | LCC (E), TYPE C, 20 TERMINAL (PINOUT)  |  |

See attached graphics following this page.

SE

B | B

# CLC532J 14 - LEAD DIP CONNECTION DIAGRAM TOP VIEW P000398A

# CLC532E 20 - LEAD LCC CONNECTION DIAGRAM TOP VIEW P000399A

# Revision History

| Rev | ECN #    | Rel Date | Originator | Changes             |

|-----|----------|----------|------------|---------------------|

| 0A0 | м0003339 | 04/05/99 | Shaw Mead  | Initial MDS Release |