## CAN-LDO

### Target Data

#### Features

- Standard fault tolerant differential CAN-transceiver

- Bus failure management

- Low power mode management

- CAN data transmission rate up to 125 kBaud

- Low-dropout voltage 5 V regulator for internal and external supply; tolerance ± 2%

- High Side Switche

- · Power on and under-voltage reset generator

- Window watchdog

- Programable time base

- Standard 8 bit SPI-Interface

- Wide input voltage range

- Wide temperature range

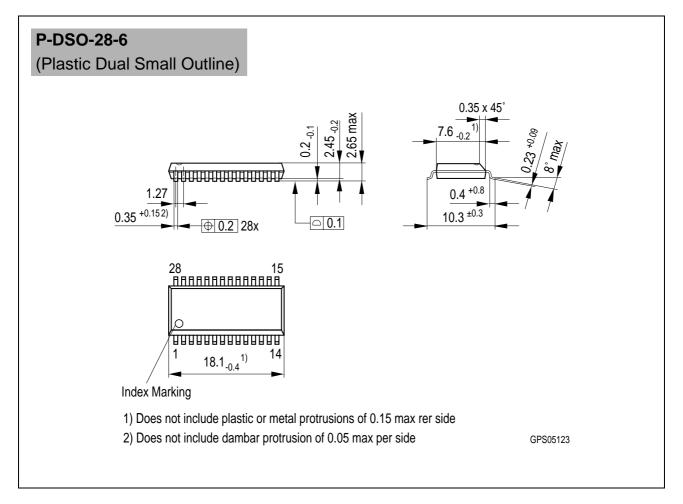

- Enhanced power P-DSO-Package

|   | Туре       | Ordering Code | Package          |

|---|------------|---------------|------------------|

| ▼ | TLE 6263 G | on request    | P-DSO-28-6 (SMD) |

▼ New type

#### **Functional Description**

The TLE 6263 G is a monolithic integrated circuit in a P-DSO-28-6 package, which incorporates a failure tolerant low speed CAN-transceiver for differential mode data transmission, a low dropout voltage regulator for internal and external 5V supply as well as a SPI (serial peripheral interface) to control and monitor the IC. Further there are integrated a high side switch, a wake-up input, a window watchdog circuit as well as a reset and early warning feature. Both, the window watchdog and reset function are referring to a time base that is programmable via an external resistor.

The IC is designed to withstand the severe conditions of automotive applications.

TLE 6263 G

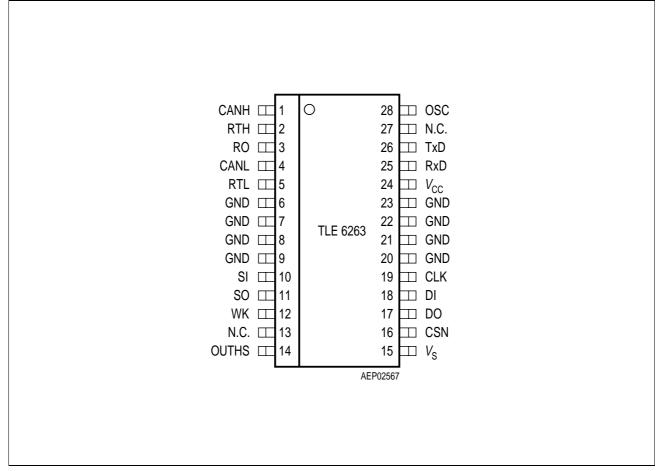

### Pin Configuration (not yet fixed)

(top view)

Figure 1

### Pin Definitions and Functions

| Pin No.                          | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|----------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                                  | CANH   | H Bus Line; HIGH in dominant state                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

|                                  | RTH    | Termination Input for CANH                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

|                                  | RO     | Reset Output; integrated pull up                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                  | CANL   | L Bus Line; LOW in dominant state                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

|                                  | RTL    | Termination Input for CANL                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 6, 7, 8, 9,<br>20, 21,<br>22, 23 | GND    | <b>Ground</b> ; to reduce thermal resistance place cooling areas on PCB close to this pins.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|                                  | SI     | Early Warning Input                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|                                  | SO     | Early Warning Output; internal pull up                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

|                                  | WK     | Wake-Up Input; for wake-up via external contacts                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                  | N.C.   | not connected                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|                                  | OUTHS  | <b>High Side Output</b> ; controlled via SPI, in sleep mode optionaly controlled by internal autotiming function                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                                  | Vs     | <b>Power Supply</b> ; block to GND directly at the IC with ceramic capacitor                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|                                  | CSN    | <b>SPI Interface Chip Select Not</b> ; CSN is an active low input; serial communication is enabled by pulling the CSN terminal low; CSN input should only be transitioned when CLK is low; CSN has an internal active pull up and requires CMOS logic level inputs                                                                                                           |  |  |  |  |  |

|                                  | DO     | SPI Interface Data Out; this tristate output transfers diagnosis data to the control device; the output will remain 3-stated unless the device is selected by a low on Chip-Select-Not (CSN); see Table 2 for Diagnosis protocol                                                                                                                                             |  |  |  |  |  |

|                                  | DI     | <b>SPI Interface Data In</b> ; receives serial data from the control device; serial data transmitted to DI is a 16 bit control word with the Least Significant Bit (LSB) being transferred first: the input has an active pull down and requires CMOS logic level inputs; DI will accept data on the falling edge of CLK-signal; see <b>Table 1</b> for input data protocol. |  |  |  |  |  |

|                                  | CLK    | <b>SPI Interface Clock Input</b> ; clocks the shiftregister; CLK has an internal active pull down and requires CMOS logic level inputs                                                                                                                                                                                                                                       |  |  |  |  |  |

| Pin No. | Symbol          | Function                                                                                                                                        |  |  |  |  |

|---------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|         | V <sub>cc</sub> | <b>Output Voltage Regulator</b> ; 5 V logic supply, block to GND with an external capacitor $C_Q \ge 10 \ \mu$ F, ESR > 1 $\Omega$              |  |  |  |  |

|         | RxD             | Receive Data Output; integrated pull upTransmit Data Input; integrated pull up                                                                  |  |  |  |  |

|         | TxD             |                                                                                                                                                 |  |  |  |  |

|         | N.C.            | not connected                                                                                                                                   |  |  |  |  |

|         | OSC             | <b>Oscillator Input</b> ; time base for power on reset, watchdog window and stand by timer for HS3, to program connect external resistor to GND |  |  |  |  |

## Pin Definitions and Functions (cont'd)

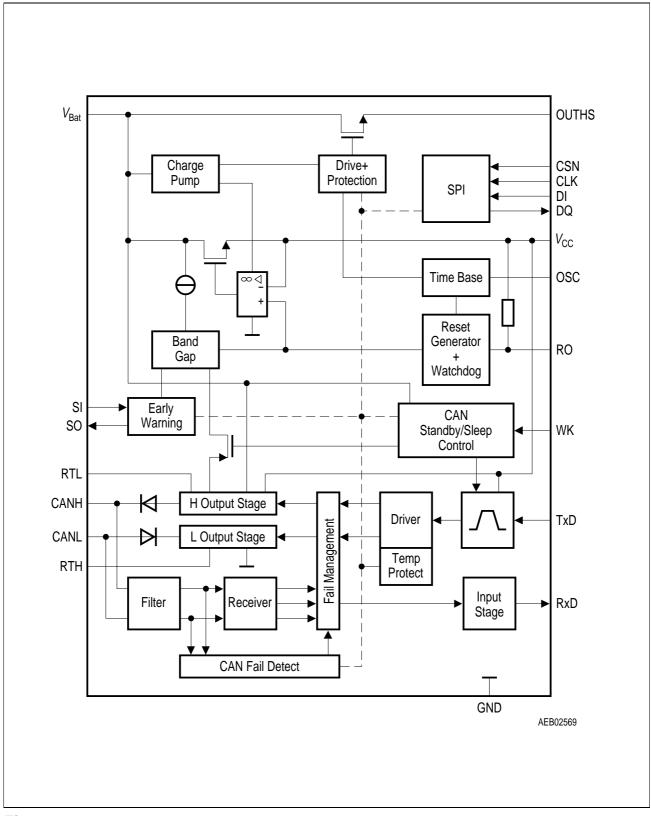

#### **Functional Block Diagram**

#### **Circuit Description**

The TLE 6263 G is a monolithic IC, which incorporates a failure tolerant low speed CANtransceiver for differential mode data transmission, a low dropout voltage regulator for internal and external 5 V supply as well as a SPI (serial periperal interface) to control and monitor the IC. Further there are integrated a high side switche, a wake-up input, a window watchdog circuit as well as a reset circuit and early warning function. Both, the window watchdog and reset function are referring to a time base that is programmable via an external resistor.

Figure 2 shows a block schematic diagram of the TLE 6263 G.

#### **CAN Transceiver**

Apart from the following deviations the CAN transceiver integrated in the TLE 6263 G is identical to the stand-alone transceiver TLE 6252:

A pin NERR for flagging any failure does not exist. The bus failures according to **Table 3** can be monitored via the diagnosis protocol of the SPI interface. Therefore it is possible to distinguish 6 CAN bus failures or failure groups on the bits 8 to 13 (see **Table 2**).

When setting the transceiver into sleep mode the internal and external 5 V supplies are automatically disabled. This feature can be masced via the SPI input bit 7.

Setting/waking up of the CAN-transceiver into/from sleep mode or stand-by mode is done via the SPI interface (bits 2 and 3, see **Table 1**). When a reset occurs the transceiver circuit is switched to  $V_{\text{bat}}$ -stand-by mode because the SPI input bits are automatically set LOW for this event.

#### Wake-Up Input

In addition to a wake-up via the bus lines CANH or CANL it is also possible to wake-up the application via the Wake-up input WK.

#### Low Dropout Voltage Regulator

The TLE 6262 is able to drive external 5 V loads up to typ. 100 mA. Its output voltage tolerance is less than  $\pm$  2%.

An external reverse current protection is recommended to prevent the output capacitor from being discharged by negative transients or low input voltage.

Stability of the output voltage is guaranteed for output capacitors  $C_Q \ge 100 \text{ nF}$ . Nevertheless a lot of applications require a much larger output capacitance to buffer the output voltage in case of low input voltage or negative transients. Furthermore the due function of e.g. the reset and early warning circuit circuit is supported by a larger output capacitance because of their reaction times. Therefore a output capacitance  $C_Q \ge 10 \mu \text{F}$ , ESR > 1  $\Omega$  is recommended.

#### **SPI (Serial Peripheral Interface)**

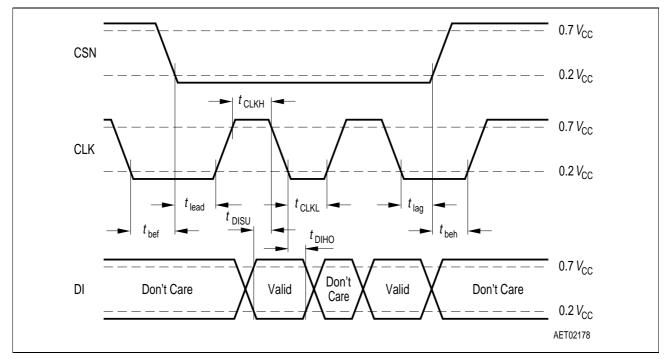

The 8-bit wide programming word or input word (see **Table 1**) is read in via the data input DI, and this is synchronised with the clock input CLK supplied by the  $\mu$ C. The diagnosis word appears synchronously at the data output DO (see **Table 2**).

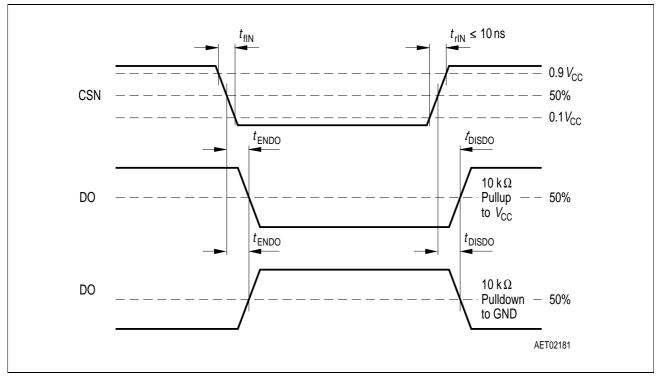

The transmision cycle begins when the chip is selected by the chip select not input CSN (H to L). After the CSN input returns from L to H, the word that has been read in becomes the new control word. The DO output switches to tristate status at this point, thereby releasing the DO bus circuit for other uses.

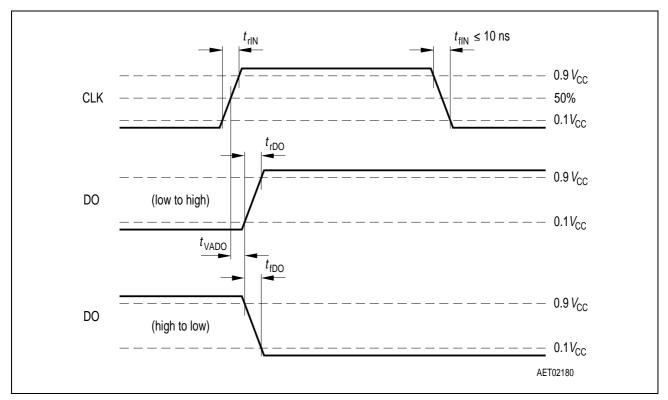

For details of the SPI timing please refer to Figure 3 to Figure 6.

#### Oscillator

All internal delay times are referring to the internal oscillator frequency, which is set by an external resistor from pin OSC to GND. The oscillator frequency and the resulting internal cycling time can be calculated by the equations:

$$f_{\rm OSC} = 35.9 \times 10^6 \, [\text{Hz}\Omega]/R_{\rm OSC}$$

$t_{\rm CYL} = 32/f_{\rm OSC}$

#### Window Watchdog, Reset

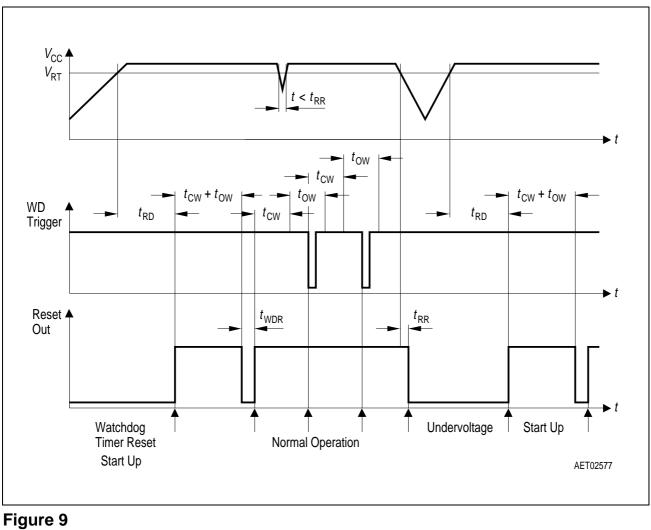

When the input voltage exceeds the reset threshold voltage the reset output RO is switched HIGH after a delay time of 16 cycles. This is necessary for a defined start of the microcontroller when the application is switched on. As soon as an under-voltage condition of the output voltage ( $V_{CC} < V_{RT}$ ) appears, the reset output RO is switched LOW again. The LOW signal is guaranteed down to an output voltage  $V_{Q} \ge 1$  V. Please refer to **Figure 9**, reset timing diagram.

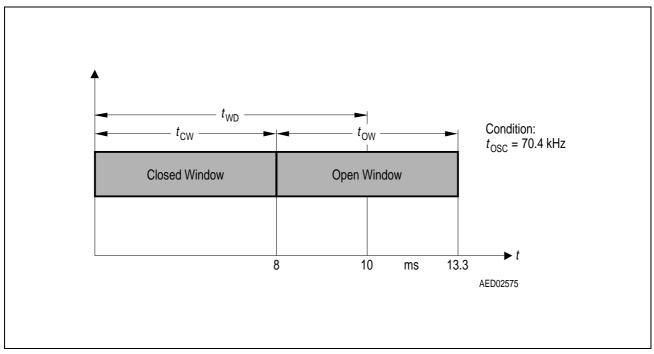

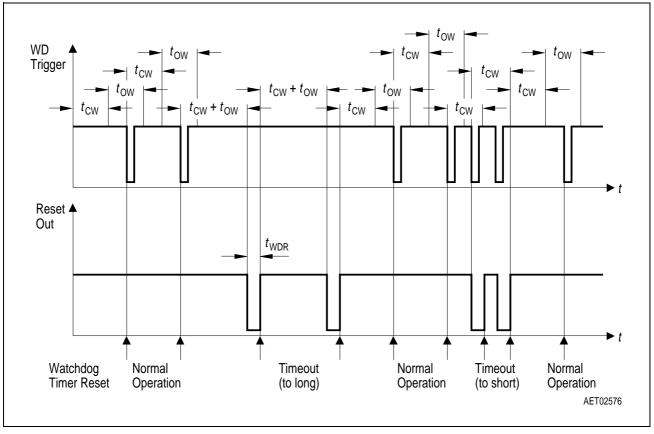

After the above described delayed reset (LOW to HIGH transitition of RO) the window watchdog circuit is started. Now the microcontroller has to service a watchdog trigger signal via the SPI interface (input bit 0) after a closed window of 16 cycles. A watchdog trigger is detected as a falling edge by sampling a HIGH followed by a LOW of the SPI input bit 0. If the trigger signals do not meet the open window (16 cycles) following the closed window, the reset output RO is set LOW for a periode of 4 cycles. In addition, the SPI diagnosis bit 1 is set HIGH to monitor a watchdog reset. A correct watchdog service immediately results in starting the next closed window. Please refer to **Figure 8**, watchdog timing diagram.

Both, the undervoltage reset and the watchdog reset are setting all SPI input bits LOW.

To avoid a cyclic wake-up of the microcontroller in low power mode (sleep mode) the watchdog circuit can be automatically disabled at low output currents ( $I_{CC} < I_{CCWD}$ ). To activate this feature the SPI input bit 1 has to be set HIGH. In this under-current mode the low side switches are switched off by the TLE 6261. When the microcontroller returns

back to normal mode ( $I_{CC} > I_{CCWD}$ ) the first closed window is transformed to an open window so that the total open window time is 32 cycles. This ensures a simple synchronisation of the watchdog timing to the watchdog services.

#### Early Warning

This sense comparator can e.g. be used to supervise the input voltage  $V_S$  to give the microcontroller a prewarning before an undervoltage reset due to low input voltage occures. The prewarning is indicated by setting the sense out SO low. To activate this featrue, the sense out has to be set high via the SPI input bit 6.

#### High Side Switch

The high side output OUTHS is able to switch loads up to 150 mA. Its on-resistance is 1.0  $\Omega$  typ. @ 25 °C. This switch is controlled via the SPI input bits 4 and 5. In normal mode and stand-by mode the high side output is swiched on resp. off via bit 5. To supply external wake-up circuits in sleep mode the output OUTHS can be periodically switched on by the internal oscillator circuit. For activating this feature the SPI input bits 4 and 5 have be set high. The autotiming period then is 128 internal cycle times; the on-time is 2 cycles. In case of a watchdog reset the autotiming period is shortened.

The SPI diagnosis bit 0 flaggs a thermal prewarning. By this the microcontroller is able to reduce the power dissipation of the TLE 6263 G by switching off functions of minor priority until the temperature threshold of the thermal shutdown is reached. Further OUTH1 is protected against short circuit and overload. As soon as the under-voltage condition of the supply voltage is met ( $V_{\rm S} < V_{\rm UVOFF}$ ), the switch is automatically disabled by the under-voltage lockout circuit. Moreover the switch is disabled when a reset occurs.

| BIT |                      |  |  |  |  |

|-----|----------------------|--|--|--|--|

| 7   | Mask Inhibit         |  |  |  |  |

| 6   | Early Warning Enable |  |  |  |  |

| 5   | OUTHS ON             |  |  |  |  |

| 4   | OUTHS Auto Timing    |  |  |  |  |

| 3   | Not Standby          |  |  |  |  |

| 2   | Enable Transmit      |  |  |  |  |

| 1   | Watchdog Control     |  |  |  |  |

| 0   | Watchdog Trigger     |  |  |  |  |

#### Table 1 Input Data Protocol (H = ON, L = OFF)

#### Table 2

Diagnosis Data Protocoll (H = ON, L = OFF)

| Bit |                         |

|-----|-------------------------|

| 7   | CAN Failure 2 and 4     |

| 6   | CAN Failure 1 and 3a    |

| 5   | CAN Failure 6           |

| 4   | CAN Failure 6a          |

| 3   | CAN Failure 6a, 5 and 7 |

| 2   | CAN Failure 3           |

| 1   | Window Watchdog Reset   |

| 0   | Temperature Prewarning  |

# Table 3CAN Bus Line Failure Cases (According to ISO 11519-2)

| Failure             | Failure Description                                     |  |  |  |  |  |  |

|---------------------|---------------------------------------------------------|--|--|--|--|--|--|

| #                   |                                                         |  |  |  |  |  |  |

| 1                   | CANL line interrupted                                   |  |  |  |  |  |  |

| 2                   | CANH line interrupted                                   |  |  |  |  |  |  |

| 3                   | CANL shorted to $V_{\text{bat}}$ ; CANH > 7.2 V         |  |  |  |  |  |  |

| 3a (no ISO failure) | CANL shorted to $V_{\text{bat}}$ ; 2.2 V < CANH < 7.2 V |  |  |  |  |  |  |

| 4                   | CANH shorted to GND                                     |  |  |  |  |  |  |

| 5                   | CANL shorted to GND                                     |  |  |  |  |  |  |

| 6                   | CANH shorted to $V_{\text{bat}}$ ; CANL > 7.2 V         |  |  |  |  |  |  |

| 6a (no ISO failure) | CANH shorted to $V_{\text{bat}}$ ; 2.2 V < CANL < 7.2 V |  |  |  |  |  |  |

| 7                   | CANL shorted to CANH                                    |  |  |  |  |  |  |

#### **Absolute Maximum Ratings**

| Parameter | Symbol | Limit Values |      | Unit | Remarks |

|-----------|--------|--------------|------|------|---------|

|           |        | min.         | max. |      |         |

#### Voltages

| Supply voltage                                   | $V_{ m S}$             | - 0.3 | 28                       | V | -                                                                                                                 |

|--------------------------------------------------|------------------------|-------|--------------------------|---|-------------------------------------------------------------------------------------------------------------------|

| Supply voltage                                   | Vs                     | - 0.3 | 40                       | V | $t_{\rm p}$ < 0.5 s; $t_{\rm p}/T$ < 0.1                                                                          |

| Regulator output voltage                         | V <sub>CC</sub>        | - 0.3 | 5.5                      | V | -                                                                                                                 |

| CAN input voltage (CANH,<br>CANL)                | $V_{CANH/L}$           | - 10  | 27                       | V | -                                                                                                                 |

| CAN input voltage<br>(CANH, CANL)                | $V_{CANH/L}$           | - 40  | 40                       | V | $V_{\rm S}$ >0 V<br>$t_p$ < 0.5 s; $t_p/T$ < 0.1                                                                  |

| Logic input voltages (DI, CLK,<br>CSN, OSC, TxD) | V                      | - 0.3 | V <sub>cc</sub><br>+ 0.3 | V | $0 V < V_{\rm S} < 24 V$<br>$0 V < V_{\rm CC} < 5.5 V$                                                            |

| Logic output voltage<br>(DO, RO, SO, RxD)        | $V_{\mathrm{DRSO,RD}}$ | - 0.3 | V <sub>cc</sub><br>+ 0.3 | V | $\begin{array}{l} 0 \ {\rm V} < V_{\rm S} < 24 \ {\rm V} \\ 0 \ {\rm V} < V_{\rm CC} < 5.5 \ {\rm V} \end{array}$ |

| Termination input voltage<br>(RTH, RTL)          | $V_{TL/TH}$            | - 0.3 | V <sub>s</sub><br>+ 0.3  | V | $0 V < V_{\rm S} < 24 V$<br>$0 V < V_{\rm CC} < 5.5 V$                                                            |

| Input voltages at WK and SI                      | $V_{ m WK/SI}$         | - 0.3 | 28                       | V | -                                                                                                                 |

| Input voltages at WK and SI                      | $V_{ m WK/SI}$         | - 0.3 | 40                       | V | $t_{\rm p}$ < 0.5 s; $t_{\rm p}/T$ < 0.1                                                                          |

#### Currents

| Output current; $V_{\rm CC}$ | I <sub>CC</sub> | - | -   | А | internally limited   |

|------------------------------|-----------------|---|-----|---|----------------------|

| Output current; OUTHS        | $I_{\rm OUTH1}$ | * | 0.2 | А | * internally limited |

#### Temperatures

| Junction temperature | Tj           | - 40 | 150 | °C | _ |

|----------------------|--------------|------|-----|----|---|

| Storage temperature  | $T_{ m stg}$ | - 50 | 150 | °C | - |

Note: Maximum ratings are absolute ratings; exceeding any one of these values may cause irreversible damage to the integrated circuit.

### **Operating Range**

| Parameter                                   | Symbol           | Limit Values    |                 | Unit | Remarks                                            |

|---------------------------------------------|------------------|-----------------|-----------------|------|----------------------------------------------------|

|                                             |                  | min.            | max.            |      |                                                    |

| Supply voltage                              | Vs               | $V_{\rm UVOFF}$ | 28              | V    | After $V_{\rm S}$ rising above $V_{\rm UV ON}$     |

| Supply voltage slew rate                    | $dV_S/dt$        | - 0.5           | 5               | V/µs | _                                                  |

| Logic input voltage (DI, CLK,<br>CSN, TxD ) | $V_1$            | - 0.3           | V <sub>cc</sub> | V    | -                                                  |

| Output capacitor                            | C <sub>cc</sub>  | 10              | -               | μF   | _                                                  |

| $C_{\rm CC}$ -Series Resistor               | R <sub>ESR</sub> | -               | 10              | Ω    | $T_{\rm a} = -40 {}^{\circ}{\rm C};$<br>f = 10 kHz |

| SPI clock frequency                         | $f_{\rm CLK}$    | -               | 1               | MHz  | -                                                  |

| Junction temperature                        | Tj               | - 40            | 150             | °C   | _                                                  |

### **Thermal Resistances**

| Junction pin     | $R_{ m thj-pin}$ | _ | 25 | K/W | measured to pin 7 |

|------------------|------------------|---|----|-----|-------------------|

| Junction ambient | $R_{ m thj-a}$   | _ | 65 | K/W | _                 |

#### **Electrical Characteristics**

$9 \text{ V} < V_{\text{S}} < 16 \text{ V}$ ;  $I_{\text{CC}} = 1 \text{ mA}$ ; normal mode; all outputs open;  $-40 \text{ °C} < T_{\text{j}} < 150 \text{ °C}$ ; all voltages with respect to ground; positive current defined flowing into pin; unless otherwise specified.

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

#### Quiescent current Pin $V_{\rm S}$

| Current consumption                            | Is                | - | 5 | -   | mA | -                                                                       |

|------------------------------------------------|-------------------|---|---|-----|----|-------------------------------------------------------------------------|

| Quiescent current<br>$I_{SSB1} = I_S - I_{CC}$ | I <sub>SSB1</sub> | - | - | 100 | μA | sleep mode; $V_{\rm S}$ = 12 V;<br>$T_{\rm j}$ = 25 °C                  |

| Quiescent current<br>$I_{SSB2} = I_S - I_{CC}$ | I <sub>SSB2</sub> | - | - | 3   | mA | OUTHS active;<br>sleep mode; $V_{\rm S}$ = 12 V;<br>$T_{\rm j}$ = 25 °C |

### Voltage Regulator; Pin $V_{\rm CC}$

| Output voltage                                       | $V_{\sf CC}$       | 4.9 | 5.0  | 5.1 | V  | 0.1 mA < I <sub>CC</sub> < 100 mA                                                   |

|------------------------------------------------------|--------------------|-----|------|-----|----|-------------------------------------------------------------------------------------|

| Output voltage                                       | V <sub>cc</sub>    | 4.8 | 5.00 | 5.5 | V  | 0 A < I <sub>CC</sub> < 100 μA                                                      |

| Line regulation                                      | $\Delta V_{ m CC}$ | -   | -    | 50  | mV | $6 V < V_{s} < 16 V;$<br>$I_{cc} = 1 mA$                                            |

| Load regulation                                      | $\Delta V_{ m CC}$ | _   | _    | 50  | mV | 5 mA < $I_{\rm CC}$ < 100 mA;<br>$V_{\rm S}$ = 6 V                                  |

| Power supply ripple rejection                        | PSRR               | tbd | 40   | _   | dB | $V_{\rm S}$ < 1 $V_{\rm SS}$ ; $C_{\rm Q} \ge$ 10 $\mu$ F<br>100 Hz < $f$ < 100 kHz |

| Output current limt                                  | I <sub>CCmax</sub> | 110 | -    | -   | mA | Note 1                                                                              |

| Dropvoltage<br>$V_{\rm DR} = V_{\rm S} - V_{\rm CC}$ | $V_{\rm DR}$       | -   | -    | 0.5 | V  | <i>I</i> <sub>cc</sub> = 80 mA;<br>Note 1                                           |

1) measured when the output voltage  $V_{\rm CC}$  has dropped 100 mV from the nominal value obtained at 13.5 V input voltage  $V_{\rm S}$

9 V <  $V_{\rm S}$  < 16 V;  $I_{\rm CC}$  = 1 mA; normal mode; all outputs open; - 40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current defined flowing into pin; unless otherwise specified.

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

#### **Oscillator; Pin OSC**

| Adjust resistor                                    | R <sub>osc</sub> | 51    | _     | 680   | kΩ  | -                                 |

|----------------------------------------------------|------------------|-------|-------|-------|-----|-----------------------------------|

| Oscillating frequency                              | $f_{\sf OSC}$    | 52.8  | 70.4  | 88.0  | kHz | $R_{\rm OSC}$ = 510 k $\Omega$    |

| Internal cycling time $(1/32 \times f_{OSC})^{-1}$ | t <sub>CYL</sub> | 0.363 | 0.454 | 0.606 | ms  | $R_{\rm OSC} = 510 \ \rm k\Omega$ |

#### Reset Generator; Pin RO

| Reset threshold voltage       | $V_{RT}$        | 4.0 | 4.3 | 4.6                   | V  | -                                                                                                                               |

|-------------------------------|-----------------|-----|-----|-----------------------|----|---------------------------------------------------------------------------------------------------------------------------------|

| Reset low output<br>voltage   | $V_{\sf RO}$    | -   | 0.2 | 0.4                   | V  | $I_{\rm RO} = 1 \text{ mA } (V_{\rm CC} \ge V_{\rm RT})$<br>or $V_{\rm CC} \ge 1 \text{ V}$<br>$(I_{\rm RO} = 200 \mu\text{A})$ |

| Reset high output voltage     | $V_{RO}$        | 4.0 | -   | V <sub>cc</sub> + 0.1 | V  | -                                                                                                                               |

| Reset pull up current         | I <sub>RO</sub> | 20  | 150 | 500                   | μA | $V_{\rm RO} = 0 \ V$                                                                                                            |

| Reset reaction time           | t <sub>RR</sub> | 1   | 3   | 10                    | μs | $V_{\rm CC} < V_{\rm RT}$ to RO = L                                                                                             |

| Reset delay time<br>(16 cyl.) | t <sub>RD</sub> | 5.8 | 7.3 | 10.6                  | ms | $R_{\rm OSC} = 510 \ \rm k\Omega$                                                                                               |

#### **Early Warning**

| Sense In threshold voltage | V <sub>ST</sub> | _   | 2.5 | _                     | V  | <i>V</i> <sub>S</sub> > 3 V                         |

|----------------------------|-----------------|-----|-----|-----------------------|----|-----------------------------------------------------|

| Sense Out low voltage      | V <sub>SO</sub> | -   | 0.2 | 0.4                   | V  | $I_{\rm SO}$ = 1 mA ( $V_{\rm CC} \ge V_{\rm RT}$ ) |

| Sense Out high<br>voltage  | V <sub>SO</sub> | 4.0 | _   | V <sub>cc</sub> + 0.1 | V  | -                                                   |

| Sense pull up current      | $I_{\rm RO}$    | 20  | 150 | 500                   | μA | $V_{\rm SO} = 0 \ V$                                |

| Sense reaction time        | t <sub>SR</sub> | -   | 5   | -                     | μs | $V_{\rm S} < V_{\rm ST}$ to SO = low                |

9 V <  $V_{\rm S}$  < 16 V;  $I_{\rm CC}$  = 1 mA; normal mode; all outputs open; - 40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current defined flowing into pin; unless otherwise specified.

| Parameter | Symbol | Lir  | nit Valı | les  | Unit | Test Condition |

|-----------|--------|------|----------|------|------|----------------|

|           |        | min. | typ.     | max. |      |                |

#### Watchdog Generator

| Watchdog time<br>(22 cyl.)                | $t_{\rm WD}$         | 8.0  | 10   | 13.3 | ms | $R_{\rm OSC} = 510 \ \rm k\Omega$                                                            |

|-------------------------------------------|----------------------|------|------|------|----|----------------------------------------------------------------------------------------------|

| Closed window time (16 cyl.)              | t <sub>CW</sub>      | 5.8  | 7.3  | 10.6 | ms | $R_{\rm OSC} = 510 \ \rm k\Omega$                                                            |

| Open window time<br>(16 cyl.)             | t <sub>ow</sub>      | 5.8  | 7.3  | 10.6 | ms | $R_{\rm OSC} = 510 \ \rm k\Omega$                                                            |

| Watchdog reset-puls time (4 cyl.)         | t <sub>WDR</sub>     | 1.5  | 1.8  | 2.4  | ms | $R_{\rm OSC} = 510 \ \rm k\Omega$                                                            |

| Watchdog activating current               | I <sub>CCWD</sub>    | 2    | 4    | 7    | mA | $T_{\rm j}$ < 85 °C; Watchdog<br>OFF when $I_{\rm CC}$ < $I_{\rm CCWD}$<br>and SPI-bit 1 = H |

| Watchdog activating<br>current hysteresis | I <sub>CCWDhys</sub> | -    | 0.5  | -    | mA | -                                                                                            |

| Long open window<br>(32 cyl.)             | I <sub>CCWDhys</sub> | 11.2 | 14.6 | 21.2 | ms | $R_{\rm OSC}$ = 510 k $\Omega$<br>sleep mode (WD OFF)<br>to normal mode                      |

9 V <  $V_{\rm S}$  < 16 V;  $I_{\rm CC}$  = 1 mA; normal mode; all outputs open; - 40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current defined flowing into pin; unless otherwise specified.

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

#### High Side Output OUTHS; (Controlled by Bit 4 and Bit 5 of SPI Input Word)

| Static                           | $R_{\rm DSONHS}$    |          | 1.0   | 1.5   | Ω  | <i>T</i> <sub>i</sub> = 25 °C                                    |

|----------------------------------|---------------------|----------|-------|-------|----|------------------------------------------------------------------|

| Drain-Source                     | TOSON HS            | <b> </b> | 1.0   | _     |    | $I_j = 25 \text{ G}$                                             |

| ON-Resistance;                   |                     |          | _     | 3.0   | Ω  | -                                                                |

| $I_{\rm OUTH3} = -0.15 \rm A$    |                     |          | 2.5   | 3.0   | Ω  | 5.2 V $\leq V_{\rm S} \leq$ 9 V<br>$T_{\rm j}$ = 25 °C           |

|                                  |                     |          | -     | 5.0   | Ω  | 5.2 V $\leq V_{\rm S} \leq$ 9 V                                  |

| Active zener voltage             | $V_{\rm OUTHS}$     | -        | - 3   | _     | V  | $I_{\rm OUTHS} = -0.15  {\rm A}$                                 |

| Clamp diode forward voltage      | V <sub>OUTHS</sub>  | _        | _     | 1     | V  | <i>I</i> <sub>OUTHS</sub> = 0.15 A                               |

| Leakage current                  | $I_{\rm QLHS}$      | - 100    | _     | -     | μA | $V_{\rm OUTHS} = 0 V$                                            |

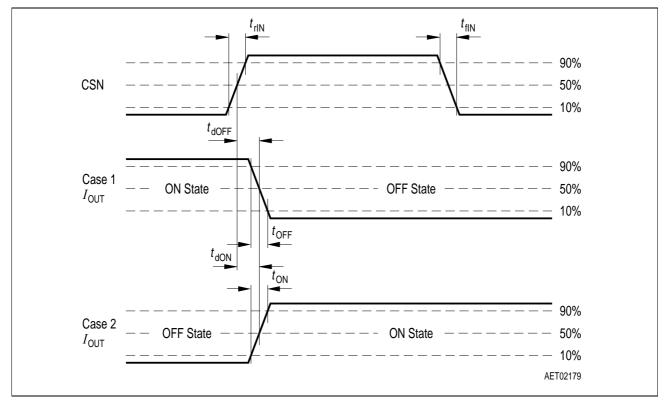

| Switch ON delay time             | t <sub>dONHS</sub>  | -        | -     | 100   | μs | CSN high to OUTHS                                                |

| Switch OFF delay time            | t <sub>dOFFHS</sub> | -        | -     | 100   | μs | CSN high to OUTHS                                                |

| Overcurrent shutdown threshold   | I <sub>SDHS</sub>   | - 0.8    | - 0.4 | - 0.2 | A  | -                                                                |

| Shutdown delay time              | t <sub>dSDHS</sub>  | 10       | 25    | 40    | μs | -                                                                |

| Current limit                    | I <sub>OCLHS</sub>  | - 1.2    | - 0.6 | - 0.3 | А  | -                                                                |

| UV-Switch-ON voltage             | $V_{\rm UVON}$      | -        | 5.35  | 6.00  | V  | $V_{\rm S}$ increasing                                           |

| UV-Switch-OFF<br>voltage         | $V_{\rm UVOFF}$     | 4.50     | 4.85  | 5.20  | V  | $V_{\rm S}$ decreasing                                           |

| UV-ON/OFF-<br>Hysteresis         | $V_{\rm UV  HY}$    | -        | 0.5   | -     | V  | $V_{\rm UV  ON} - V_{\rm UV  OFF}$                               |

| Auto time periode<br>(128 cyl.)  | t <sub>PHS</sub>    | 29       | 58    | 87    | ms | $R_{\rm OSC}$ = 510 k $\Omega$ ; SPI-bit<br>4/5 = H, no WD reset |

| Auto time ON duty cycle (2 cyl.) | D.C.                | -        | 1/64  | -     | -  | refering to t <sub>PHS</sub>                                     |

9 V <  $V_{\rm S}$  < 16 V;  $I_{\rm CC}$  = 1 mA; normal mode; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current defined flowing into pin; unless otherwise specified.

| Parameter | Symbol | Lir  | nit Valı | les  | Unit | Test Condition |

|-----------|--------|------|----------|------|------|----------------|

|           |        | min. | typ.     | max. |      |                |

#### SPI-Interface Logic Inputs DI, CLK and CSN

| H-input voltage<br>threshold               | $V_{IH}$             | _                        | _    | 0.7 *<br>V <sub>CC</sub> | V  | _                                  |

|--------------------------------------------|----------------------|--------------------------|------|--------------------------|----|------------------------------------|

| L-input voltage<br>threshold               | $V_{IL}$             | 0.2 *<br>V <sub>cc</sub> | _    | -                        | V  | _                                  |

| Hysteresis of input voltage                | V <sub>IHY</sub>     | 50                       | 200  | 500                      | mV | -                                  |

| Pull up current at pin<br>CSN              | I <sub>ICSN</sub>    | - 100                    | - 25 | - 5                      | μA | $V_{\rm CSN}$ = 0.7 × $V_{\rm CC}$ |

| Pull down current at<br>pin DI and CLK     | I <sub>ICLK/DI</sub> | 5                        | 25   | 100                      | μA | $V_{\rm DI}$ = 0.2 × $V_{\rm CC}$  |

| Pull down current at<br>pin CLK            | I <sub>ICLK</sub>    | 10                       | 25   | 50                       | μA | $V_{\rm CLK}$ = 0.2 × $V_{\rm CC}$ |

| Input capacitance at<br>pin CSN, DI or CLK | $C_1$                | _                        | 10   | 15                       | pF | $0 V < V_{\rm CC} < 5.25 V$        |

#### Logic Output DO

| H-output voltage level         | $V_{DOH}$         | V <sub>cc</sub> –<br>1.0 | V <sub>CC</sub> –<br>0.7 | _   | V  | $I_{\rm DOH} = 1  \rm mA$                                       |

|--------------------------------|-------------------|--------------------------|--------------------------|-----|----|-----------------------------------------------------------------|

| L-output voltage level         | $V_{DOL}$         | -                        | 0.2                      | 0.4 | V  | $I_{\rm DOL} = -1.6  {\rm mA}$                                  |

| Tri-state leakage current      | I <sub>dolk</sub> | - 10                     | _                        | 10  | μA | $V_{\rm CSN} = V_{\rm CC}$<br>0 V < $V_{\rm DO}$ < $V_{\rm CC}$ |

| Tri-state input<br>capacitance | C <sub>DO</sub>   | _                        | 10                       | 15  | pF | $V_{\rm CSN} = V_{\rm CC}$<br>0 V < $V_{\rm CC}$ < 5.25 V       |

9 V <  $V_{\rm S}$  < 16 V;  $I_{\rm CC}$  = 1 mA; normal mode; all outputs open; – 40 °C <  $T_{\rm j}$  < 150 °C; all voltages with respect to ground; positive current defined flowing into pin; unless otherwise specified.

| Parameter | Symbol | Limit Values |      |      | Unit | Test Condition |

|-----------|--------|--------------|------|------|------|----------------|

|           |        | min.         | typ. | max. |      |                |

| Clock period                                     | t <sub>pCLK</sub> | 1000 | - | -   | ns | - |

|--------------------------------------------------|-------------------|------|---|-----|----|---|

| Clock high time                                  | t <sub>CLKH</sub> | 500  | - | -   | ns | - |

| Clock low time                                   | t <sub>CLKL</sub> | 500  | - | -   | ns | - |

| Clock low before CSN low                         | t <sub>bef</sub>  | 500  | - | _   | ns | _ |

| CSN setup time                                   | $t_{\text{lead}}$ | 500  | - | -   | ns | - |

| CLK setup time                                   | $t_{\rm lag}$     | 500  | _ | -   | ns | - |

| Clock low after CSN high                         | t <sub>beh</sub>  | 500  | - | _   | ns | _ |

| DI setup time                                    | t <sub>DISU</sub> | 250  | - | -   | ns | - |

| DI hold time                                     | t <sub>DIHO</sub> | 250  | - | -   | ns | - |

| Input signal rise time at pin DI, CLK and CSN    | t <sub>rIN</sub>  | -    | - | 200 | ns | - |

| Input signal fall time at<br>pin DI, CLK and CSN | t <sub>fIN</sub>  | _    | _ | 200 | ns | _ |

#### **Data Input Timing**

#### Data Output Timing

| DO rise time    | t <sub>rDO</sub>   | - | 50  | 100 | ns | <i>C</i> <sub>L</sub> = 100 pF                                                                |

|-----------------|--------------------|---|-----|-----|----|-----------------------------------------------------------------------------------------------|

| DO fall time    | t <sub>fDO</sub>   | - | 50  | 100 | ns | <i>C</i> <sub>L</sub> = 100 pF                                                                |

| DO enable time  | t <sub>ENDO</sub>  | _ | -   | 250 | ns | low impedance                                                                                 |

| DO disable time | t <sub>DISDO</sub> | _ | -   | 250 | ns | high impedance                                                                                |

| DO valid time   | t <sub>VADO</sub>  | _ | 100 | 250 | ns | $V_{\rm DO} < 0.1 V_{\rm CC};$<br>$V_{\rm DO} > 0.9 V_{\rm CC};$<br>$C_{\rm L} = 100  \rm pF$ |

$9 \text{ V} < V_{\text{S}} < 16 \text{ V}$ ;  $I_{\text{CC}} = 1 \text{ mA}$ ; normal mode; all outputs open;  $-40 \text{ °C} < T_{\text{j}} < 150 \text{ °C}$ ; all voltages with respect to ground; positive current defined flowing into pin; unless otherwise specified.

| Parameter | Symbol | Limit Values   |  |  | Unit | Test Condition |

|-----------|--------|----------------|--|--|------|----------------|

|           |        | min. typ. max. |  |  |      |                |

#### **Thermal Prewarning and Shutdown (Junction Temperatures)**

| Thermal prewarning<br>ON temperature | T <sub>jPW</sub>          | 120  | 145  | 170 | °C | bit 0 of SPI diagnosis<br>word |

|--------------------------------------|---------------------------|------|------|-----|----|--------------------------------|

| Thermal prewarning hyst.             | $\Delta T$                | _    | 30   | -   | К  | -                              |

| Thermal shutdown temp.               | $T_{\rm jSD}$             | 150  | 175  | 200 | °C | -                              |

| Thermal switch-on temp.              | $T_{\rm jSO}$             | 120  | -    | 170 | °C | -                              |

| Thermal shutdown hyst.               | $\Delta T$                | -    | 30   | -   | К  | -                              |

| Ratio of SD to PW temp.              | $T_{\rm jSD}/T_{\rm jPW}$ | 1.05 | 1.20 | _   | _  | -                              |

#### **Timing Diagrams**

#### Figure 3 SPI-Input Timing

#### Figure 4 Turn OFF/ON Time

Figure 5 DO Valid Data Delay Time and Valid Time

#### Figure 7 Watchdog Timeout Definitions

#### Figure 8 Watchdog Timing Diagram

Reset Timing Diagram

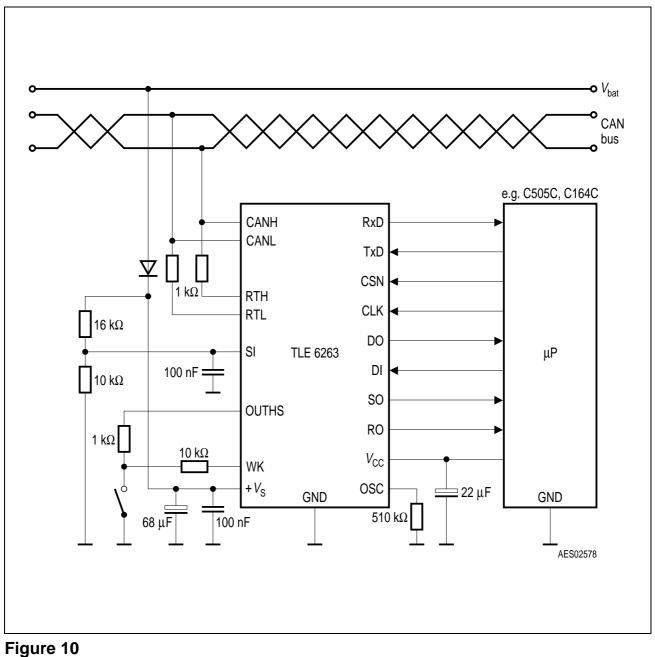

### Application

Application Circuit

#### **Package Outlines**

Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book "Package Information". SMD = Surface Mounted Device

Dimensions in mm