# SiGe – Low Noise Amplifier (900 MHz)

#### **Description**

The TST0950 is a low-noise amplifier (LNA) in SiGe technology. This LNA offers the possibility to apply a gain switching through a control input pin, and provides a power-down mode function for extending the battery operation time.

In low-gain mode, the output drive capability is not reduced, resulting in improved intermodulation performance. The nominal gain is very precise and has max. ±1.0 dB gain variation over full temperature range and supply-voltage range.

Electrostatic sensitive device.

Observe precautions for handling.

#### **Features**

- Input frequency 925 to 960 MHz

- Low noise figure at high gain mode (typ. 2.2 dB)

- Precise gain (19 dB, ±1.0 dB)

- Low-/high gain mode

- High gain flatness (±0.3 dB max.)

- Power-down function

- High reverse isolation (min. –40 dB)

- Small package (TSSO8)

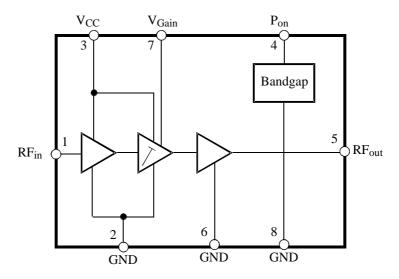

#### **Block Diagram**

Figure 1. Block diagram

## **Ordering Information**

| Extended Type Number | Package | Remarks          |

|----------------------|---------|------------------|

| TST0950B-MFPG3       | TSSO8   | Taped and reeled |

Rev. A6, 25-Apr-00

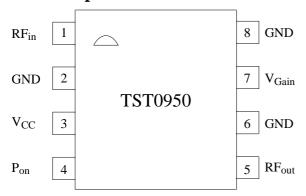

### **Pin Description**

| Pin | Symbol            | Function             |

|-----|-------------------|----------------------|

| 1   | RF <sub>in</sub>  | RF input             |

| 2   | GND               | Ground               |

| 3   | $V_{CC}$          | Supply voltage       |

| 4   | Pon               | Power-down input     |

| 5   | RF <sub>out</sub> | RF output            |

| 6   | GND               | Ground               |

| 7   | $V_{Gain}$        | Gain switching input |

| 8   | GND               | Ground               |

Figure 2. Pinning

## **Functional Description**

The TST0950 is a very precise amplifer, especially designed for GSM telephone applications. The circuit consists of three stages. By attenuating the output signal of the first stage, the complete amplifier gain is reduced and the intermodulation behavior is improved.

#### **Absolute Maximum Ratings**

All voltages are referred to GND (Pins 2, 6 and 8)

| Parameters                 | Symbol            | Min. | Max.     | Unit |

|----------------------------|-------------------|------|----------|------|

| Supply voltage Pin 3       | V <sub>CC</sub>   | 2.7  | 3.3      | V    |

| Junction temperature       | Ti                | -40  | +125     | °C   |

| Storage temperature        | T <sub>stg</sub>  | -40  | +150     | °C   |

| Input power Pin 1          | RFin              | _    | -10      | dBm  |

| Power-down input Pin 4     | Pon               | 0    | $V_{CC}$ | V    |

| Gain switching input Pin 7 | V <sub>Gain</sub> | 0    | $V_{CC}$ | V    |

## **Solder Reflow Profile (SMD Packages)**

| Parameters                                     | Symbol            | Value              | Unit |

|------------------------------------------------|-------------------|--------------------|------|

| Maximum heating rate                           | $T_{\mathrm{D}}$  | 1 to 3             | °C/s |

| Peak temperature in preheat zone               | $T_{PH}$          | 100 to 140         | °C   |

| Duration of time above melting point of solder | t <sub>MP</sub>   | Min. 10 / Max. 130 | S    |

| Peak reflow temperature                        | T <sub>Peak</sub> | 220 to 225         | °C   |

| Maximum cooling rate                           | T <sub>Peak</sub> | 2 to 4             | °C/s |

## **Wave Soldering (Through-Hole Packages)**

| Parameters                     | Symbol           | Value | Unit |

|--------------------------------|------------------|-------|------|

| Maximum lead temperature (5 s) | $T_{\mathrm{D}}$ | 260   | °C   |

2 (6) Rev. A6, 25-Apr-00

# **Operation Range**

All voltages are referred to GND (Pins 2, 6 and 8)

| Parameters          | Symbol           | Min. | Тур. | Max. | Unit |

|---------------------|------------------|------|------|------|------|

| Supply voltage      | $V_{CC}$         | 2.7  | 2.8  | 2.9  | V    |

| Ambient temperature | T <sub>amb</sub> | -20  |      | +70  | °C   |

| Input frequency     | IF <sub>in</sub> | 925  |      | 960  | MHz  |

#### Note for biasing:

Apply first  $V_{CC}$  , then  $P_{on}$  and  $V_{Gain}$  (see absolute maximum ratings)

### **Electrical Characteristics**

Test conditions:  $V_{CC} = +2.8 \text{ V}$ ,  $T_{amb} = +25 ^{\circ}\text{C}$ , unless otherwise specified

| Parameters                      | Test Conditions / Pins | Symbol          | Min.                 | Тур. | Max.                 | Unit |

|---------------------------------|------------------------|-----------------|----------------------|------|----------------------|------|

| Power supply                    |                        |                 |                      |      |                      |      |

| Supply voltage                  | Pin 3                  | V <sub>CC</sub> | 2.7                  | 2.8  | 2.9                  | V    |

| Current consumption             |                        |                 |                      |      |                      |      |

| active mode                     |                        | Ia              |                      | 10   | 12                   | mA   |

| power-down mode                 |                        | I <sub>pd</sub> |                      | 50   | 200                  | μΑ   |

| IF input                        |                        |                 |                      |      |                      |      |

| Input impedance *)              | Pin 1                  | Zi              |                      | 50   |                      | Ω    |

| Output impedance *)             | Pin 5                  | Zo              |                      | 50   |                      | Ω    |

| Frequency band                  |                        | Fin             | 925                  |      | 960                  | MHz  |

| Nominal gain                    | Pin 1 to 5             | G               | 18                   | 19   | 20                   | dB   |

| Gain attenuation related to     | Pin 1 to 5             | ΔG              | 15                   |      | 17                   | dB   |

| nominal gain                    |                        |                 |                      |      |                      |      |

| Gain flatness                   | Pin 1 to 5             |                 | -0.3                 |      | +0.3                 | dB   |

| Noise figure                    | Pin 1 to 5             |                 |                      |      |                      |      |

| in low-gain mode                |                        | NF              |                      | 11   | 20                   | dB   |

| in high-gain mode               |                        | NF              |                      | 2.2  | 2.5                  | dB   |

| Input VSWR *)                   | LNA active             |                 |                      |      |                      |      |

| in low-gain mode                | Pin 1                  | VSWR            |                      |      | 2:1                  |      |

| in high-gain mode               |                        | VSWR            |                      |      | 2:1                  |      |

| Output VSWR *)                  | LNA active             |                 |                      |      |                      |      |

|                                 | PON = '1' Pin 5        | VSWR            |                      |      | 2:1                  |      |

|                                 | LNA inactive           |                 |                      |      |                      |      |

|                                 | PON = '0' Pin 5        | VSWR            |                      |      | 3:1                  |      |

| Input 1 dB compression point    |                        |                 |                      |      |                      |      |

| in low-gain mode                | Pin 1 to 5             |                 | -16                  |      |                      | dBm  |

| in high-gain mode               |                        |                 | -21                  |      |                      | dBm  |

| Input intercept point 3rd order |                        |                 |                      |      |                      |      |

| in low-gain mode                | Pin 1 to 5             |                 | <b>-7</b>            |      |                      | dBm  |

| in high-gain mode               |                        |                 | -12                  |      |                      | dBm  |

| Reverse isolation               |                        |                 |                      |      |                      |      |

| in low-gain mode                | Pin 5 to 1             |                 | 40                   |      |                      | dB   |

| in high-gain mode               |                        |                 | 38                   |      |                      | dB   |

| <b>Control function</b>         |                        |                 |                      |      |                      |      |

| Control inputs threshold        |                        |                 |                      |      |                      |      |

| high level                      | Pins 4 and 7           | $V_{TH}$        | $0.97 \times V_{CC}$ |      |                      | V    |

| low level                       |                        | $V_{TH}$        |                      |      | $0.03 \times V_{CC}$ | V    |

| Leakage current on control      | Pins 4 and 7           | I <sub>l</sub>  |                      |      | 100                  | μA   |

| inputs low level                |                        |                 |                      |      |                      |      |

<sup>\*)</sup> with external matching (see application circuit)

Rev. A6, 25-Apr-00 3 (6)

# **Power Down Logic**

| Level | Pon | Power Status |

|-------|-----|--------------|

|       | '0' | Power OFF    |

|       | '1' | Power ON     |

## **Gain Control Logic**

| Gain Level | V <sub>Gain</sub> | Gain         |

|------------|-------------------|--------------|

|            | '0'               | Minimum gain |

|            | '1'               | Maximum gain |

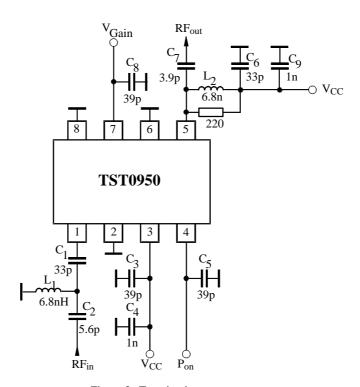

# **Test Circuit**

Figure 3. Test circuit

4 (6) Rev. A6, 25-Apr-00

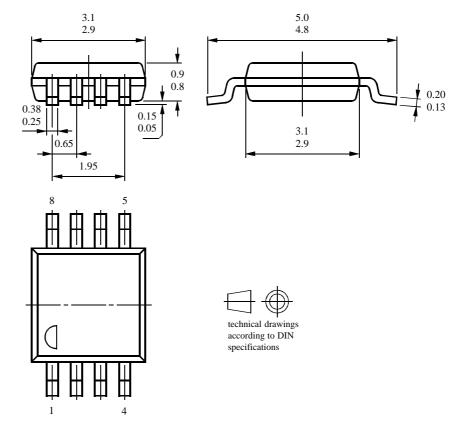

# **Package Information**

Package TSSO8 Dimensions in mm

Rev. A6, 25-Apr-00 5 (6)

#### **Ozone Depleting Substances Policy Statement**

It is the policy of **TEMIC Semiconductor GmbH** to

- 1. Meet all present and future national and international statutory requirements.

- Regularly and continuously improve the performance of our products, processes, distribution and operating systems with respect to their impact on the health and safety of our employees and the public, as well as their impact on the environment.

It is particular concern to control or eliminate releases of those substances into the atmosphere which are known as ozone depleting substances (ODSs).

The Montreal Protocol (1987) and its London Amendments (1990) intend to severely restrict the use of ODSs and forbid their use within the next ten years. Various national and international initiatives are pressing for an earlier ban on these substances.

**TEMIC Semiconductor GmbH** has been able to use its policy of continuous improvements to eliminate the use of ODSs listed in the following documents.

- 1. Annex A, B and list of transitional substances of the Montreal Protocol and the London Amendments respectively

- 2. Class I and II ozone depleting substances in the Clean Air Act Amendments of 1990 by the Environmental Protection Agency (EPA) in the USA

- 3. Council Decision 88/540/EEC and 91/690/EEC Annex A, B and C (transitional substances) respectively.

**TEMIC Semiconductor GmbH** can certify that our semiconductors are not manufactured with ozone depleting substances and do not contain such substances.

We reserve the right to make changes to improve technical design and may do so without further notice.

Parameters can vary in different applications. All operating parameters must be validated for each customer.

Parameters can vary in different applications. All operating parameters must be validated for each customer application by the customer. Should the buyer use TEMIC Semiconductors products for any unintended or unauthorized application, the buyer shall indemnify TEMIC Semiconductors against all claims, costs, damages, and expenses, arising out of, directly or indirectly, any claim of personal damage, injury or death associated with such unintended or unauthorized use.

Data sheets can also be retrieved from the Internet: http://www.temic-semi.com

TEMIC Semiconductor GmbH, P.O.B. 3535, D-74025 Heilbronn, Germany Telephone: 49 (0)7131 67 2594, Fax number: 49 (0)7131 67 2423

6 (6) Rev. A6, 25-Apr-00