UCB1500 PCI to AC97 bridge/host controller Rev. 02 — 7 July 2000

**Product specification**

# 1. General description

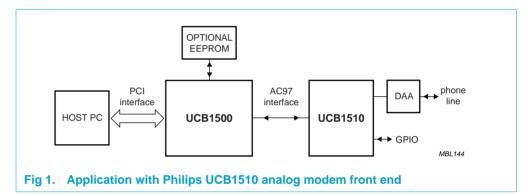

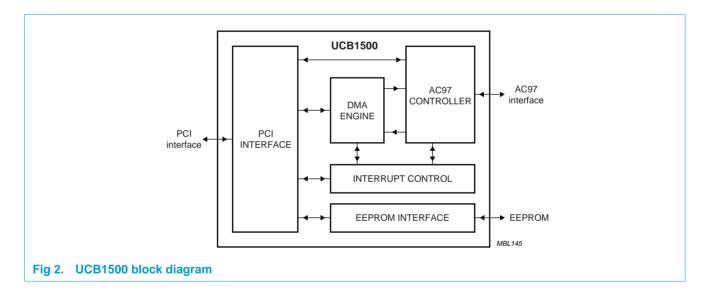

UCB1500 is a PCI-to-AC97 Bridge/Host Controller for modem or audio codecs equipped with the AC-link interface. It integrates a PCI 2.2 compliant interface for communication with the host PC, with built in support for PPMI (PCI Power Management Interface) and wake-up. It also integrates an AC97 Rev. 2.1 compliant host controller for connection to up to two AC-Link codecs, including analog modem front ends such as the Philips UCB1510, and audio codecs.

# 2. Features

32-bit PCI 2.2 interface with bus master support

- Support up to two PCI functions with independent scatter/gather DMA

- PPMI and wake-up support via PME and V<sub>AUX</sub>

- Download of subsystem IDs and auxiliary power consumption via optional serial EEPROM

- 5 V tolerant interface for motherboard/PC add-on

- AC97 rev 2.1 compliant host controller interface

- Supports up to two codecs

- Supports variable sample rate via the SLOTREQ protocol and valid tag bits

- Low latency GPIO data transfer

- Support modem wake-up on ring from D3cold

- Advanced power management support

- PPMI (PCI Power Management Interface)

- Instantly available PC

- ACPI

# 3. Applications

- PCI-AC97 bridge/host controller

- PCI modem cards

- Host based modems

# 4. Ordering information

## Table 1: Ordering information

| Type number | Package |                                                                                            |          |

|-------------|---------|--------------------------------------------------------------------------------------------|----------|

|             | Name    | Description                                                                                | Version  |

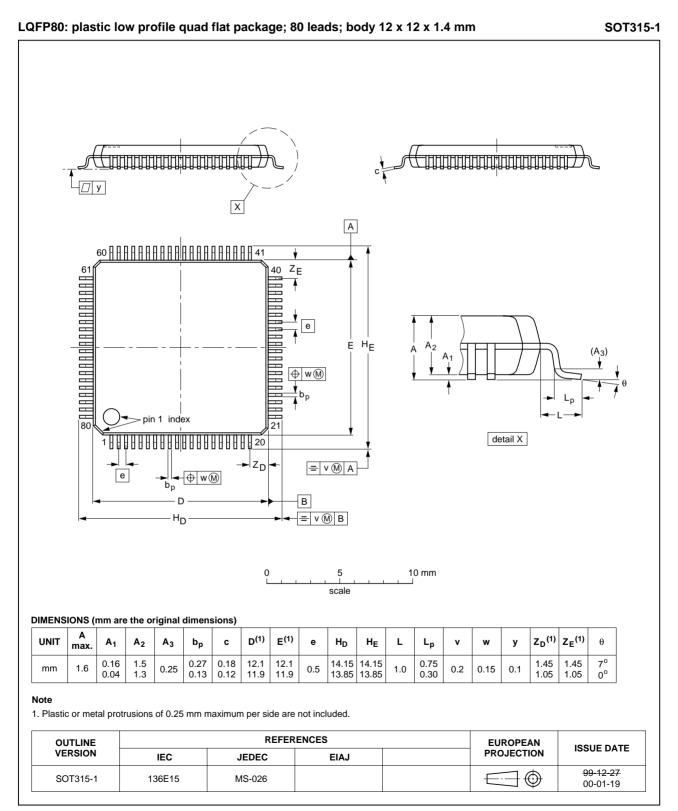

| UCB1500     | LQFP80  | plastic low profile quad flat package, 80 leads; body $12 \times 12 \times 1.4 \text{ mm}$ | SOT315-1 |

# 5. Block diagram

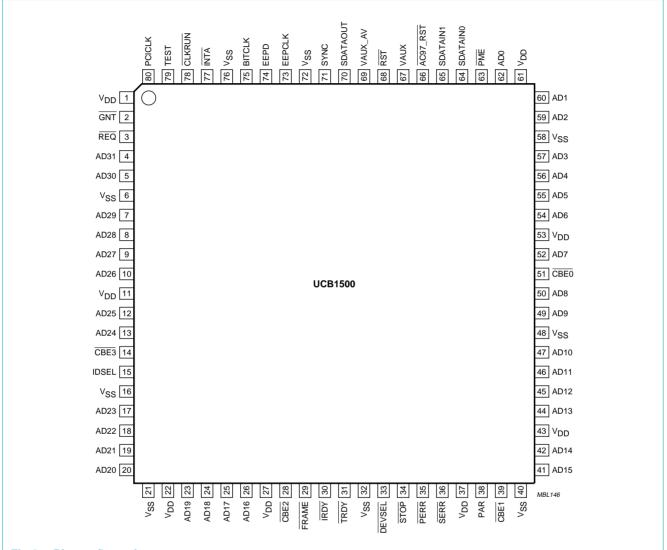

# 6. Pinning information

## 6.1 Pinning

### Fig 3. Pin configuration

## 6.2 Pin description

| Table 2:Pin   | description |                      |                                                      |

|---------------|-------------|----------------------|------------------------------------------------------|

| Symbol        | Pin         | Туре                 | Description                                          |

| PCI interface |             |                      |                                                      |

| PCICLK        | 80          | I                    | PCI system clock.                                    |

| RST           | 68          | I                    | PCI system reset, V <sub>AUX</sub> powered.          |

| REQ           | 3           | T/S                  | PCI bus request.                                     |

| GNT           | 2           | T/S                  | PCI bus grant.                                       |

| FRAME         | 29          | S/T/S <sup>[1]</sup> | PCI FRAME, input during slave, output during master. |

| Symbol               | Pin                                                                                                                                     | Туре               | Description                                                                                                                            |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| IRDY                 | 30                                                                                                                                      | S/T/S              | PCI IRDY, input during slave, output during master.                                                                                    |  |  |

| TRDY                 | 31                                                                                                                                      | S/T/S              | PCI TRDY, output during slave, input during master.                                                                                    |  |  |

| DEVSEL               | 33                                                                                                                                      | S/T/S              | PCI DEVSEL, output during slave, input during master.                                                                                  |  |  |

| STOP                 | 34                                                                                                                                      | S/T/S              | PCI STOP, output during slave, input during master.                                                                                    |  |  |

| IDSEL                | 15                                                                                                                                      | I                  | PCI IDSEL signal.                                                                                                                      |  |  |

| AD[31:0]             | 4, 5, 7, 8, 9, 10, 12,<br>13, 17, 18, 19, 20,<br>23, 24, 25, 26,41,<br>42, 44, 45, 46, 47,<br>49, 50, 52, 54, 55,<br>56, 57, 59, 60, 62 | T/S                | PCI address/data.<br>slave mode: output only during data read phase.<br>master mode: output during address phase and data write phase. |  |  |

| CBE[3:0]             | 14, 28, 39, 51                                                                                                                          | T/S                | PCI command/byte-enable, input during slave, output during master.                                                                     |  |  |

| PAR                  | 38                                                                                                                                      | T/S                | PCI parity.                                                                                                                            |  |  |

| INTA                 | 77                                                                                                                                      | 0/D <sup>[2]</sup> | PCI interrupt.                                                                                                                         |  |  |

| PME                  | 63                                                                                                                                      | O/D                | Open drain, $V_{AUX}$ powered PCI power management pin. SDA TAIN[1:0] pins are $V_{AUX}$ powered and can trigger $\overline{PME}$ .    |  |  |

| SERR                 | 36                                                                                                                                      | O/D                | PCI system error                                                                                                                       |  |  |

| PERR                 | 35                                                                                                                                      | S/T/S              | PCI parity error                                                                                                                       |  |  |

| CLKRUN               | 78                                                                                                                                      | S/T/S              | Primary PCI bus clock run. Used by the central resource to stop the PCI clock or to slow it down                                       |  |  |

| AC link contro       | oller interface                                                                                                                         |                    |                                                                                                                                        |  |  |

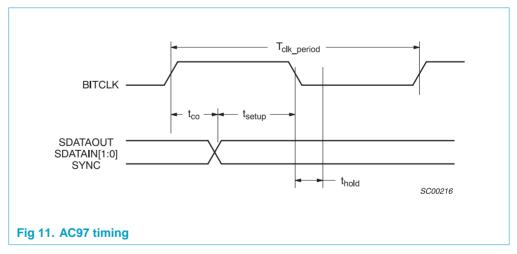

| BITCLK               | 75                                                                                                                                      | I                  | Serial data clock; or input for secondary codecs.                                                                                      |  |  |

| SDATAIN[1:0]         | 65. 64                                                                                                                                  | I                  | Input from AC97/MC97 codecs. $V_{AUX}$ powered and can trigger $\overline{PME}$ .                                                      |  |  |

| SDATAOUT             | 70                                                                                                                                      | 0                  | Output to AC97/MC97 codecs. Driven to 0 at power-up or when $\overline{RST}$ asserted.                                                 |  |  |

| SYNC                 | 71                                                                                                                                      | 0                  | AC97 sync. Driven to 0 at power-up or when $\overline{RST}$ asserted.                                                                  |  |  |

| AC97_RST             | 66                                                                                                                                      | 0                  | AC97 reset. Driven to 0 at power-up or when $\overline{RST}$ asserted. V <sub>AUX</sub> powered                                        |  |  |

| Serial EEPRO         | M interface                                                                                                                             |                    |                                                                                                                                        |  |  |

| EEPCLK               | 73                                                                                                                                      | 0                  | EEPROM clock.                                                                                                                          |  |  |

| EEPD                 | 74                                                                                                                                      | I/O                | EEPROM serial data port.                                                                                                               |  |  |

| Power manage         | ement; miscellaneou                                                                                                                     | S                  |                                                                                                                                        |  |  |

| V <sub>AUX</sub> _AV | 69                                                                                                                                      | I                  | Auxiliary power available, V <sub>AUX</sub> powered.                                                                                   |  |  |

| TEST                 | 79                                                                                                                                      | I                  | Test mode.                                                                                                                             |  |  |

| Power pins           |                                                                                                                                         |                    |                                                                                                                                        |  |  |

| V <sub>DD</sub>      | 1, 11, 22, 27, 37,<br>43, 53, 61                                                                                                        | S                  | 3.3 V power pins.                                                                                                                      |  |  |

| V <sub>SS</sub>      | 6, 16, 21, 32, 40,<br>48, 58, 72, 76                                                                                                    | S                  | Ground pins.                                                                                                                           |  |  |

| V <sub>AUX</sub>     | 67                                                                                                                                      | S                  | Auxiliary power. If auxiliary power is not available or not necessary, this pin must be connected to $V_{\text{DD}}$ .                 |  |  |

#### Table 2: Pin description...continued

[1] S/T/S: Sustained 3-State is an active-LOW 3-state signal owned and driven by one agent at a time. The agent that drives an S/T/S pin LOW must drive it HIGH for at least one clock before letting it float. A new agent cannot start driving a S/T/S signal any sooner than one clock after the previous owner 3-states it.

[2] O/D: Open Drain allows multiple devices to share as a wired OR.

Table 3: EEPROM data map

# 7. PCI configuration space

## 7.1 Overview

By default, UCB1500 supports a single modem function. Under control of BIOS or an external serial EEPROM, UCB1500 can support a maximum of two PCI functions, which are typically one modem plus one audio functions. To allow IHV to overwrite parameters such as Device ID, Vendor ID, Subsystem Vendor ID, Subsystem ID, Class Code and Power Management Capabilities, UCB1500 provides two schemes:

- For each function, Device ID, Vendor ID, Subsystem Vendor ID, Subsystem ID, Class Code and Power Management Capabilities are placed in a dedicated PCI configuration read/write area accessible by the corresponding function. An enable bit for Function 1 is placed in a dedicated read/write area accessible by Function 0. This allows IHVs to enable Function 1 and change the corresponding read-only parameters of Functions 0 and 1 (if enabled) in the BIOS POST routine when UCB1500 is used as a motherboard device.

- In case UCB1500 is used as a PCI card which BIOS cannot control, the above parameters, together with Function 1 enable, can be changed by the external serial EEPROM.

| Byte address | Taq          | Description                                                                    |

|--------------|--------------|--------------------------------------------------------------------------------|

| 00-01h       | signature    | 1516h = valid signature, otherwise disable autoloading.                        |

| 02-03h       | control      | Bit 0: $1 = \text{enable function } 1, 0 = \text{disable function } 1$         |

| 02 0011      |              | Bit 1: 1 = enable function 0 auto-loading from address 04-9Dh                  |

|              |              | Bit 2: 1 = enable function 0 auto-loading from address $0A-11h$                |

|              |              | Bit 2: $1 = \text{enable function 1 auto-loading from address 10-17h}$         |

|              |              | Bit 4: $1 = \text{enable function 1 auto-loading from address 18-1Fh}$         |

|              |              | Other bits: reserved and must be 0s.                                           |

| 04-05h       | sub vendorID |                                                                                |

|              | _            | Function 0 subsystem vendor ID, PCI configuration space address 2C-2Dh.        |

| 06-07h       | subsystemID  | Function 0 subsystem ID, PCI configuration space address 2E-2Fh.               |

| 08-09h       | pmc          | Function 0 power management capabilities, PCI configuration space address 82h. |

| 0A-0Bh       | vendorID     | Function 0 vendor ID, PCI configuration space address 00-01h.                  |

| 0C-0Dh       | deviceID     | Function 0 device ID, PCI configuration space address 02-03h.                  |

| 0Eh          |              | Reserved.                                                                      |

| 0F-11h       | classCode    | Function 0 Class Code, PCI configuration space address 09-0Bh.                 |

| 12-13h       | sub_vendorID | Function 1 subsystem vendor ID, PCI configuration space address 2C-2Dh.        |

| 14-15h       | subsystemID  | Function 1 subsystem ID, PCI configuration space address 2E-2Fh.               |

| 16-17h       | pmc          | Function 1 power management capabilities, PCI configuration space offset 82h.  |

| 18-19h       | vendorID     | Function 1 vendor ID, PCI configuration space address 00-01h.                  |

| 1A-1Bh       | deviceID     | Function 1 device ID, PCI configuration space address 02-03h.                  |

| 1Ch          |              | Reserved.                                                                      |

| 1D-1Fh       | classCode    | Function 1 Class Code, PCI configuration space address 09-0Bh.                 |

|              |              |                                                                                |

The EEPROM data map is given in Table 3.

## 7.2 Configuration registers

## 7.2.1 Function 0 configuration registers

UCB1500 supports the PCI configuration cycle to control the UCB1500 access. It sets up the PCI configuration bits and the UCB1500 IO port address. The following table shows the supported PCI registers and their default values. Some of the registers are programmable through the EEPROM interface (See EEPROM section for details).

**Remark:** All registers are read/write, unless specified otherwise. Shaded registers are read-only. A register with (S) means it is powered by  $V_{AUX}$  and is sticky. Unless sticky or otherwise stated, all read/write registers defaults to zero at PCI reset. All reserved or unimplemented registers are hardwired to 0.

#### Table 4: Function 0 configuration registers

| 31-24                                 | 23-16                                                    | 15-8                                                       | 7-0                                                        | Address |

|---------------------------------------|----------------------------------------------------------|------------------------------------------------------------|------------------------------------------------------------|---------|

| Device ID = 3400                      |                                                          | Vendor ID = 1131                                           |                                                            | 00h     |

| Modified by BIOS via writi<br>loading | ng to 42h or EEPROM auto                                 | Modified by BIOS via wri<br>loading                        | Modified by BIOS via writing to 40h or EEPROM auto loading |         |

| Status = 0290                         |                                                          | Command = 0000                                             |                                                            | 04h     |

| Class Code = 070300                   |                                                          |                                                            | Revision ID = 01                                           | 08h     |

| Simple communication co               | ntroller, generic modem.                                 |                                                            |                                                            |         |

| Modified by BIOS via writi            | ng to 45h or EEPROM auto                                 | loading.                                                   |                                                            |         |

| BIST = 00                             | Header Type                                              | Latency Timer = 00                                         | Cache Line Size = 00                                       | 0Ch     |

|                                       | If multifunction,<br>header type = 80h,<br>otherwise 00h |                                                            |                                                            |         |

| I/O port Base Address [3              | 31:16]                                                   | I/O port Base Address                                      | [15:0] = 0001                                              | 10h     |

| Hardwired to 0000h                    |                                                          |                                                            |                                                            |         |

| Reserved.                             |                                                          |                                                            |                                                            | 14h-2Bh |

| Subsystem ID = 3400                   |                                                          | Subsystem Vendor ID = 1131                                 |                                                            | 2Ch     |

| Modified by BIOS via writi<br>loading | ng to 6Eh or EEPROM auto                                 | Modified by BIOS via writing to 6Ch or EEPROM auto loading |                                                            |         |

| Reserved                              |                                                          |                                                            |                                                            | 30h     |

| Reserved                              |                                                          |                                                            | Capability Pointer = 80                                    | 34h     |

| Reserved                              |                                                          |                                                            |                                                            | 38h     |

| Reserved                              |                                                          | Interrupt Pin = 01                                         | Interrupt Line = 00                                        | 3Ch     |

| Device ID Write = 3400                |                                                          | Vendor ID Write = 1131                                     |                                                            | 40h     |

| Class Code Write = 0703               | 800                                                      |                                                            | Revision ID = 01                                           | 44h     |

| Reserved                              |                                                          |                                                            | EEPROM Status = 00                                         | 48h     |

| Reserved                              |                                                          |                                                            |                                                            | 4C-4Fh  |

| Reserved                              |                                                          |                                                            | Test Register = 00                                         | 50      |

| Reserved                              |                                                          |                                                            |                                                            | 54-67h  |

| PMC Write = C801                      |                                                          | Reserved                                                   |                                                            | 68h     |

|                                       |                                                          |                                                            |                                                            |         |

| 7-0 Address                        |

|------------------------------------|

| 70-7Fh                             |

| em Per = 00 Capability ID = 01 80h |

|                                    |

|                                    |

|                                    |

| <b>R = 0000 (S)</b> 84h            |

|                                    |

## Table 4: Function 0 configuration registers...continued

**[01-00]: Vendor ID (read only):** Programmable through EEPROM interface, or register 40h. Default value = 1131h

**[03-02]: Device ID (read only):** Programmable through EEPROM interface, or register 42h. Default value = 3400h

### [05-04]: Command Register

| Table 5: | Command Register bit description                                                                                                                                                            |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit      | Description                                                                                                                                                                                 |

| 15-10    | Reserved.                                                                                                                                                                                   |

| 9(r)     | Fast Back-to-back Transactions                                                                                                                                                              |

|          | Always 0, fast back-to-back transactions is not supported.                                                                                                                                  |

| 8        | SERR enable                                                                                                                                                                                 |

|          | If set, $\overline{\text{SERR}}$ driver is enabled; if 0, $\overline{\text{SERR}}$ is disabled.                                                                                             |

| 7(r)     | Address/Data Stepping                                                                                                                                                                       |

|          | Always 0, address/data stepping is not implemented.                                                                                                                                         |

| 6        | Parity Error Response                                                                                                                                                                       |

|          | When set, the device must take its normal action when a parity error is detected. If this bit is 0, the device must ignore any parity errors that it detects and continue normal operation. |

| 5(r)     | VGA Snooping                                                                                                                                                                                |

|          | Always 0, not implemented.                                                                                                                                                                  |

| 4(r)     | Memory Write and Invalidate Command                                                                                                                                                         |

|          | Always 0, UCB1500 does not generate memory write and invalidate command.                                                                                                                    |

| 3(r)     | Special Cycle Response                                                                                                                                                                      |

|          | Always 0, UCB1500 ignores all special cycles.                                                                                                                                               |

| 2        | Bus Master Control                                                                                                                                                                          |

|          | PCI Master access enable; this bit must be enabled to activate UCB1500 DMA register.                                                                                                        |

|          | 1 = enable.                                                                                                                                                                                 |

| 1(r)     | Memory Space Response                                                                                                                                                                       |

|          | Always 0, UCB1500 does not respond to memory space accesses.                                                                                                                                |

| 0        | I/O Space Control                                                                                                                                                                           |

|          | UCB1500 control register I/O space access enable.                                                                                                                                           |

|          | 1 = enable.                                                                                                                                                                                 |

### [07-06]: Status Register

| Table 6: | Status Register bit description                                                           |

|----------|-------------------------------------------------------------------------------------------|

| Bit      | Description                                                                               |

| 15       | PERR detected                                                                             |

|          | Set to '1' whenever parity error is detected. Write '1' to clear.                         |

| 14       | SERR asserted                                                                             |

|          | Set to '1' if UCB1500 asserted SERR. Write '1' to clear.                                  |

| 13       | Received master abort                                                                     |

|          | If set, UCB1500 has received master abort during its slave operation. Write '1' to clear. |

| 12       | Received target abort                                                                     |

|          | If set, UCB1500 has received target abort during its master operation. Write `1' to clear |

| 11(r)    | Target abort                                                                              |

|          | Always '0'; UCB1500 never signals target abort.                                           |

| 10-9(r)  | Timing                                                                                    |

|          | Always 01b; wait state during slave access to UCB1500.                                    |

| 8        | PERR reported                                                                             |

|          | Not implemented, always 0.                                                                |

| 7(r)     | Fast back-to-back capable                                                                 |

|          | Always '1'; NO wait state between PCI cycles.                                             |

| 6(r)     | User Definable features                                                                   |

|          | Always '0'; device does not support user definable features.                              |

| 5(r)     | 66 MHz capable bit                                                                        |

|          | Always '0'; device is 33 MHz device only.                                                 |

| 4(r)     | Capabilities bit (read only)                                                              |

|          | Always '1'; capabilities present.                                                         |

| 3-0      | Reserved.                                                                                 |

|          |                                                                                           |

[08]: Revision ID (read only): Current revision of chip = 1.

**[0B-09]: Class Code Register (read only):** Value = 070300h for simple communication controller, generic modem. Programmable through EEPROM interface or register 47-45h.

[0C]: Cache Line Size (read only): Always 0; no cache supported.

## [0D]: Latency Timer

| Table 7: Latency Timer register bit description |

|-------------------------------------------------|

|-------------------------------------------------|

| Bit    | Description                                                 |

|--------|-------------------------------------------------------------|

| 7-4    | Latency Timer                                               |

|        | Bits 7-4 of the latency timer, in units of PCI clocks * 16. |

| 3-0(r) | Latency Timer                                               |

| (- )   |                                                             |

[0E]: Header Type (read only): If multifunction device, value is 80h otherwise 00h.

[0F]: BIST (read only): Always 0; no built-in test capability.

## [10]: I/O port base address

| Table 8: | I/O Port Base Address register bit description             |

|----------|------------------------------------------------------------|

| Bit      | Description                                                |

| 31-16(r) | I/O port Base address                                      |

|          | A[31:16] always 0.                                         |

| 15-4     | I/O port Base address                                      |

|          | A[15:4]; programmable address space for control registers. |

| 3-1      | Always 000b                                                |

| 0        | Always 1b                                                  |

|          |                                                            |

[2C-2F] Subsystem ID/Subsystem Vendor ID (read only): Programmable through EEPROM interface or through register 6E-6Ch. Default Value = 3400h/1131h.

[34] Capability pointer (read only): 80h points to start offset of power management registers.

#### [3C]: Interrupt Register

Table 9:

Interrupt Register bit description

| Bit  | Description                                                                      |

|------|----------------------------------------------------------------------------------|

| 15:8 | <b>Interrupt pin</b> (read only)<br>Always 01h; interrupt pin connected to INTA. |

| 7:0  | Interrupt line Interrupt line routing information.                               |

**[40-43] Device ID Write / Vendor ID Write:** This register contains a copy of the Device ID and Vendor ID registers. Writing to this register will update the original Device ID and Vendor ID registers (offset 0h - 3h).

[44h]: Revision ID: Same as offset 08h.

**[45-47] Class code Write:** This register contains a copy of the Class Code registers. Writing to this register will update the original Class Code registers (offset 9h-Bh).

#### [48]: EEPROM status register /Misc

#### Table 10: EEPROM Status register bit description

| Bit | Description                                   |

|-----|-----------------------------------------------|

| 0   | EEPROM autoload status                        |

|     | If set, EEPROM autoload cycle is in progress. |

## [50]: Test Register (For internal use only)

Table 11: Test Register bit description

| Bit | Description                                                                                                                                                |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Test Mode Enable                                                                                                                                           |

|     | If set, chip operates under test mode. If '0', chip operates normally.                                                                                     |

| 1   | EEPROM Autoload enable                                                                                                                                     |

|     | If set, EEPROM autoload is disabled. If '0', EEPROM autoload sequence operates as normal, depending on the EEPROM signature. This bit is for testing only. |

**[6A-6B]: Power Management capabilities Write:** This register contains a copy of the Power Management capabilities register. Writing to this register will update the original Power Management capabilities register (offset 82h-83h).

**[6C-6F]:** Subsystem-ID Write / Vendor ID Write: This register contains a copy of the Subsystem-ID/Vendor ID register. Writing to this register will update the original Subsystem-ID/Vendor ID registers (offset 2Ch-2Fh).

[80]: Capability Identifier (read only): This register is set to 01h to indicate power management interface registers.

[81]: Next Item Pointer (read only): This field provides an offset into the function's PCI Configuration Space pointing to the location of next item in the function's capability list. This register is set to zero, signifying that there are no additional items in the capability list.

## [82]: Power Management Capabilities (read only)

Table 12: Power Management Capabilities register bit description

Read only

| Read only |                                                                                                                                                                                                                                                                                                                                 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit       | Description                                                                                                                                                                                                                                                                                                                     |

| 15-11(r)  | PME support                                                                                                                                                                                                                                                                                                                     |

|           | This 5-bit field indicates the power states in which the function may assert $\overline{PME}$ . Value is set to 11001b if $V_{AUX\_AV} = 1$ to indicate $\overline{PME}$ can be asserted from D3cold and D0. If $V_{AUX\_AV} = 0$ , this field is set to 01001b to indicate $\overline{PME}$ can be asserted from D3hot and D0. |

|           | The entire setting can be overwritten by BIOS via writing to 6Ah, or an external EEPROM. If $V_{AUX_{AV}} = 0$ , bit 15 shall always be zero. If $V_{AUX} = 1$ , bit 15 shall reflect the setting of 6Ah, or that loaded from EEPROM.                                                                                           |

| 10(r)     | D2 support                                                                                                                                                                                                                                                                                                                      |

|           | This bit is set to '0' to indicate that function does not support the D2 power management state. This setting can be overwritten by BIOS via 6Ah, or with the external EEPROM.                                                                                                                                                  |

| 9(r)      | D1 support                                                                                                                                                                                                                                                                                                                      |

|           | This bit is set to '0' to indicate that function does not support the D1 power management state. This setting can be overwritten by BIOS via 6Ah, or with the external EEPROM.                                                                                                                                                  |

| 8-6(r)    | Aux_Current                                                                                                                                                                                                                                                                                                                     |

|           | These bits are set to '0' for PCI-PM 1.0 compliance. For PCI-PM 1.1 compliance, these bits are overwritten by BIOS via 6Ah, or loaded from an external EEPROM to reflect the $3.3V_{AUX}$ current requirement.                                                                                                                  |

| 5(r)      | DSI                                                                                                                                                                                                                                                                                                                             |

|           | The Device Specific Initialization bit indicates whether special initialization of this function is required (beyond the standard PCI configuration header) before the generic class device driver is able to use it. This register is set to '0' to indicate that it does not require special initialization.                  |

| 4(r)      | Reserved.                                                                                                                                                                                                                                                                                                                       |

| 3(r)      | PME Clock                                                                                                                                                                                                                                                                                                                       |

|           | This bit is a '0', indicating that the function does not rely on the presence of the PCI clock for $\overline{\text{PME}}$ operation.                                                                                                                                                                                           |

| 2:0(r)    | Version                                                                                                                                                                                                                                                                                                                         |

|           | This register is set to 001b, indicating that this function complies with Rev 1.0 of the <i>PCI Power Management Interface Specification</i> . These bits can also be overwritten by BIOS via 6Ah, or loaded from an external EEPROM to 010b for compliance with PCI-PM 1.1.                                                    |

[84]: Power Management Control/Status: (V<sub>AUX</sub> powered: Only PME Status and PME\_EN are sticky.)

Table 13: Power Management Control/Status register bit description

| Table 13. | rower management control/status register bit description                                                                                                                                  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit       | Description                                                                                                                                                                               |

| 15        | PME Status - Sticky Bit                                                                                                                                                                   |

|           | This bit is set when the function would normally assert the PME signal independent of the state of the PME_EN bit. This bit is set when a power management event occurs.                  |

|           | Writing a '1' to this bit will clear it and cause the function to stop asserting a $\overline{PME}$ (if enabled). Writing a '0' has no effect.                                            |

| 14-13(r)  | Data scale                                                                                                                                                                                |

|           | Not implemented.                                                                                                                                                                          |

| 12-9      | Data select                                                                                                                                                                               |

|           | This 4-bit field is used to select which data is to be reported through the Data register and <b>Data scale</b> field. This function is not implemented in this chip.                     |

| 8         | PME_EN - Sticky Bit                                                                                                                                                                       |

|           | A '1' enables the function to assert $\overline{\text{PME}}$ . When '0', $\overline{\text{PME}}$ assertion is disabled.                                                                   |

| 7-2(r)    | Reserved.                                                                                                                                                                                 |

| 1-0       | Power State                                                                                                                                                                               |

|           | This 2-bit field is used both to determine the current power state of a function<br>and to set the function into a new power state. The definition of the field values is<br>given below. |

|           | 00b - D0                                                                                                                                                                                  |

|           | 01b - D1                                                                                                                                                                                  |

|           | 10b - D2                                                                                                                                                                                  |

|           | 11b - D3hot                                                                                                                                                                               |

|           | If software writes D1 or D2 and the corresponding bit 10 or 9 or register 82 indicates it is not supported, the state change is discarded.                                                |

|           |                                                                                                                                                                                           |

[86-87]: Reserved.

## 7.2.2 Function 1 Configuration Registers

#### Table 14: Function 1 configuration registers

| 31-24                                                         | 23-16                                       | 15-8                                    | 7-0                                                           | Address |

|---------------------------------------------------------------|---------------------------------------------|-----------------------------------------|---------------------------------------------------------------|---------|

| Device ID = 3401                                              |                                             | Vendor ID = 1131                        | !                                                             | 00h     |

| Modified by BIOS via writing to 42h or<br>EEPROM auto loading |                                             | -                                       | Modified by BIOS via writing to 40h or<br>EEPROM auto loading |         |

| Status = 0290                                                 |                                             | Command = 0000                          |                                                               | 04h     |

| Class Code = 040                                              | 100                                         |                                         | Revision ID = 01                                              | 08h     |

| Multimedia Audio I                                            | Device.                                     |                                         |                                                               |         |

| Modified by BIOS                                              | via writing to 45h or EEPRO                 | M auto loading.                         |                                                               |         |

| BIST = 00                                                     | Header Type = 00                            | Latency Timer = 0                       | 0 Cache Line Size = 00                                        | 0Ch     |

| I/O port Base Add                                             | dress [31:16]                               | I/O port Base Add                       | ress[15:0] = 0001                                             | 10h     |

| Hardwired to 0000                                             | h                                           |                                         |                                                               |         |

| Reserved.                                                     |                                             |                                         |                                                               | 14h-2Bh |

| Subsystem ID = 3                                              | 401                                         | Subsystem Vendo                         | r ID = 1131                                                   | 2Ch     |

| Modified by BIOS via writing to 6Eh or<br>EEPROM auto loading |                                             | Modified by BIOS vi<br>EEPROM auto load |                                                               |         |

| Reserved                                                      |                                             |                                         |                                                               | 30h     |

|                                                               |                                             |                                         | Capability Pointer = 80                                       | 34h     |

| Reserved                                                      |                                             |                                         |                                                               | 38h     |

| Reserved                                                      |                                             | Interrupt Pin = 01                      | Interrupt Line = 00                                           | 3Ch     |

| Device ID Write =                                             | 3401                                        | Vendor ID Write =                       | 1131                                                          | 40h     |

| Class Code Write                                              | = 040100                                    |                                         | Revision ID = 01                                              | 44h     |

| Reserved                                                      |                                             |                                         | EEPROM Status = 00                                            | 48h     |

| Reserved                                                      |                                             |                                         |                                                               | 4C-4Fh  |

| Reserved                                                      |                                             |                                         | Test Register = 00                                            | 50      |

| Reserved                                                      |                                             |                                         |                                                               | 54-67h  |

| PMC Write = 0401                                              |                                             | Reserved                                | Reserved                                                      |         |

| Subsystem ID Write = 3401                                     |                                             | Subsystem Vendo                         | Subsystem Vendor ID Write = 1131                              |         |

| Reserved                                                      |                                             |                                         |                                                               | 70-7Fh  |

| PMC = 0401                                                    |                                             | Next Item Ptr = 00                      | Capability ID = 01                                            | 80h     |

| Modified by BIOS                                              | via writing to 6Ah, or<br>ding to PCI-PM1.1 |                                         |                                                               |         |

| Reserved                                                      |                                             | PMCSR = 0000 (S)                        |                                                               | 84h     |

**[01-00]: Vendor ID (read only):** Programmable through EEPROM interface, or register 40h. Default value = 1131h

**[03-02]: Device ID (read only):** Programmable through EEPROM interface, or register 42h. Default value = 3401h

## [05-04]: Command Register

## Table 15: Command Register bit description

|       | <b>o</b>                                                                                                                                                                                          |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit   | Description                                                                                                                                                                                       |

| 15-10 | Reserved.                                                                                                                                                                                         |

| 9(r)  | Fast Back-to-back Transactions                                                                                                                                                                    |

|       | Always 0, fast back-to-back transactions is not supported.                                                                                                                                        |

| 8     | SERR enable                                                                                                                                                                                       |

|       | If set, $\overline{\text{SERR}}$ driver is enabled; if 0, $\overline{\text{SERR}}$ is disabled.                                                                                                   |

| 7(r)  | Address/Data Stepping                                                                                                                                                                             |

|       | Always 0, address/data stepping is not implemented.                                                                                                                                               |

| 6     | Parity Error Response                                                                                                                                                                             |

|       | When set, the device must take its normal action when a parity error is detected.<br>If this bit is 0, the device must ignore any parity errors that it detects and continue<br>normal operation. |

| 5(r)  | VGA Snooping                                                                                                                                                                                      |

|       | Always 0, not implemented.                                                                                                                                                                        |

| 4(r)  | Memory Write and Invalidate Command                                                                                                                                                               |

| .,    | Always 0, UCB1500 does not generate memory write and invalidate command.                                                                                                                          |

| 3(r)  | Special Cycle Response                                                                                                                                                                            |

|       | Always 0, UCB1500 ignores all special cycles.                                                                                                                                                     |

| 2     | Bus Master Control                                                                                                                                                                                |

|       | PCI Master access enable; this bit must be enabled to activate UCB1500 DMA register.                                                                                                              |

|       | 1 = enable.                                                                                                                                                                                       |

| 1(r)  | Memory Space Response                                                                                                                                                                             |

|       | Always 0, UCB1500 does not respond to memory space accesses.                                                                                                                                      |

| 0     | I/O Space Control                                                                                                                                                                                 |

|       | UCB1500 control register I/O space access enable.                                                                                                                                                 |

|       | 1 = enable.                                                                                                                                                                                       |

### [07-06]: Status Register

| Bit       Description         15       FERR detected         Set to '1' whenever parity error is detected. Write '1' to clear.         14       SERR asserted         Set to '1' if UCB1500 asserted SERR. Write '1' to clear.         13       Received master abort         If set, UCB1500 has received master abort during its slave operation. Write '1' to clear.         12       Received target abort         If set, UCB1500 has received target abort during its master operation. Write '1' to clear         11(r)       Target abort         Always '0'; UCB1500 never signals target abort.         10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features         Always '0'; device does not support user definable features. | Table 16: | Status Register bit description                                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-------------------------------------------------------------------------------------------|

| Set to '1' whenever parity error is detected. Write '1' to clear.         14       SERR asserted         Set to '1' if UCB1500 asserted SERR. Write '1' to clear.         13       Received master abort         If set, UCB1500 has received master abort during its slave operation. Write '1' to clear.         12       Received target abort         If set, UCB1500 has received target abort during its master operation. Write '1' to clear         11(r)       Target abort         Always '0'; UCB1500 never signals target abort.         10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                   | Bit       | Description                                                                               |

| 14       SERR asserted         Set to '1' if UCB1500 asserted SERR. Write '1' to clear.         13       Received master abort         If set, UCB1500 has received master abort during its slave operation. Write '1' to clear.         12       Received target abort         If set, UCB1500 has received target abort during its master operation. Write '1' to clear.         11       If set, UCB1500 has received target abort during its master operation. Write '1' to clear         11(r)       Target abort         Always '0'; UCB1500 never signals target abort.         10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                 | 15        | PERR detected                                                                             |

| Set to '1' if UCB1500 asserted SERR. Write '1' to clear.         13       Received master abort         If set, UCB1500 has received master abort during its slave operation. Write '1' to clear.         12       Received target abort         If set, UCB1500 has received target abort during its master operation. Write '1' to clear         11(r)       Target abort         Always '0'; UCB1500 never signals target abort.         10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                                                                                                                            |           | Set to '1' whenever parity error is detected. Write '1' to clear.                         |

| <ul> <li>13 Received master abort <ul> <li>If set, UCB1500 has received master abort during its slave operation. Write '1' to clear.</li> </ul> </li> <li>12 Received target abort <ul> <li>If set, UCB1500 has received target abort during its master operation. Write '1' to clear</li> </ul> </li> <li>11(r) Target abort <ul> <li>Always '0'; UCB1500 never signals target abort.</li> </ul> </li> <li>10-9(r) Timing <ul> <li>Always 01b; wait state during slave access to UCB1500.</li> </ul> </li> <li>8 PERR reported <ul> <li>Not implemented, always 0.</li> </ul> </li> <li>7(r) Fast back-to-back capable <ul> <li>Always '1'; NO wait state between PCI cycles.</li> </ul> </li> <li>6(r) User Definable features</li> </ul>                                                                                                                                                                                                                                               | 14        | SERR asserted                                                                             |

| If set, UCB1500 has received master abort during its slave operation. Write '1' to clear.         12       Received target abort         If set, UCB1500 has received target abort during its master operation. Write `1' to clear         11(r)       Target abort         Always '0'; UCB1500 never signals target abort.         10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                                                                                                                                                                                                                                    |           | Set to '1' if UCB1500 asserted SERR. Write '1' to clear.                                  |

| clear.         12       Received target abort         If set, UCB1500 has received target abort during its master operation. Write `1' to clear         11(r)       Target abort         Always '0'; UCB1500 never signals target abort.         10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                                                                                                                                                                                                                                                                                                                       | 13        | Received master abort                                                                     |

| If set, UCB1500 has received target abort during its master operation. Write `1' to clear         11(r)       Target abort         Always '0'; UCB1500 never signals target abort.         10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |           | If set, UCB1500 has received master abort during its slave operation. Write '1' to clear. |

| to clear11(r)Target abort<br>Always '0'; UCB1500 never signals target abort.10-9(r)Timing<br>Always 01b; wait state during slave access to UCB1500.8PERR reported<br>Not implemented, always 0.7(r)Fast back-to-back capable<br>Always '1'; NO wait state between PCI cycles.6(r)User Definable features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 12        | Received target abort                                                                     |

| Always '0'; UCB1500 never signals target abort.         10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                                                                           |

| 10-9(r)       Timing         Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11(r)     | Target abort                                                                              |

| Always 01b; wait state during slave access to UCB1500.         8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |           | Always '0'; UCB1500 never signals target abort.                                           |

| 8       PERR reported         Not implemented, always 0.         7(r)       Fast back-to-back capable         Always '1'; NO wait state between PCI cycles.         6(r)       User Definable features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10-9(r)   | Timing                                                                                    |