ML2330\*

# Selectable Dual 3V/3.3V/5V 8-Bit DACs

### GENERAL DESCRIPTION

The ML2330 Selectable Dual 3V/3.3V/5V 8-bit DACs are dual voltage output digital-to-analog converters which can be independently programmed, or powered down to conserve power. The devices are intended for use in portable or low power 3V systems where space is critical.

Programming access to the DACs is provided over a high speed (10Mb/s), 3-wire serial interface which is compatible to the SPI<sup>TM</sup> and Microwire<sup>TM</sup> data formats. In addition to independent programming of the DAC output voltages, each device may be powered down, independent of the other DAC, to conserve power. Each DAC draws 2mA maximum quiescent current when operating, and typically less than 1µA when powered down.

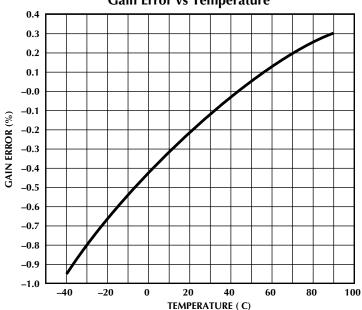

The device comes in an 8-pin SOIC package and in a special Extended Commercial temperature range (-20°C to 70°C) or Industrial temperture range (-40°C to 85°C).

### FEATURES

- 3V ±10%, 3.3 ±10% or 5V ±10% operation

- Low supply current (3.5mA max)

- Individual and full power down (down to 1µA)

- 10Mb/s three-wire serial interface, compatible to SPI and Microwire

- 8-pin SOIC package

- Available in Extended Commercial temperature range (-20°C to 70°C) and Industrial temperture range (-40°C to 85°C)

- Guaranteed monotonicity

#### \*Some Packages Are End Of Life Or Obsolete

#### - 8 VCC OUT A R DAC A **20k**Ω SCLK Din CONTROL POWER AND VREF DOWN TIMING CS DOUT 4 OUT B DAC B **20k**Ω GND - 5

### **BLOCK DIAGRAM**

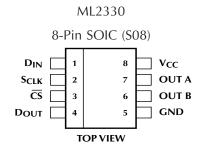

# PIN CONFIGURATION

## PIN DESCRIPTION

| FIN DESCRIFTION |                        |                 |  |  |  |

|-----------------|------------------------|-----------------|--|--|--|

| PIN             | NAME                   | FUNCTION        |  |  |  |

| 1               | D <sub>IN</sub>        | Data In         |  |  |  |

| 2               | S <sub>CLK</sub>       | Serial Clock    |  |  |  |

| 3               | $\overline{\text{CS}}$ | Chip Select     |  |  |  |

| 4               | D <sub>OUT</sub>       | Data Out        |  |  |  |

| 5               | GND                    | Ground          |  |  |  |

| 6               | OUT B                  | Output of DAC B |  |  |  |

| 7               | OUT A                  | Output of DAC A |  |  |  |

| 8               | V <sub>CC</sub>        | Positive Supply |  |  |  |

# ABSOLUTE MAXIMUM RATINGS

| Supply Voltage (V <sub>CC</sub> )          | 6.0V                     |

|--------------------------------------------|--------------------------|

| GND                                        | -0.3V to $V_{CC}$ + 0.3V |

| Logic Inputs                               | -0.3V to $V_{CC} + 0.3V$ |

| Input Current per Pin                      | ±25mA                    |

| Storage Temperature                        | –65°C to 150°C           |

| Package Dissipation at $T_A = 25^{\circ}C$ | 750mW                    |

| Lead Temperature (Soldering 10 sec.)       |                          |

| SOIC                                       | 150°C                    |

|                                            |                          |

## OPERATING CONDITIONS

| 3V ± 10%      |

|---------------|

| 3.3V ± 10%    |

| 5V ± 10%      |

|               |

| –20°C to 70°C |

| 40°C to 85°C  |

|               |

### ELECTRICAL CHARACTERISTICS

Unless otherwise specified,  $T_A = T_{MIN}$  to  $T_{MAX}$ ,  $V_{CC} = Operating Supply Voltage Range$ ,  $f_{CLK} = 10MHz R_L = 1ký$ ,  $(R_L = 2k\Omega \text{ for } V_{CC} = 5V)$ ,  $C_L = 100pF$  (Note 1)

| PARAMETER                    | SYMBOL          | CONDITIONS                                   |               | MIN | TYP | MAX  | UNITS |

|------------------------------|-----------------|----------------------------------------------|---------------|-----|-----|------|-------|

| Converter                    |                 | 1                                            |               | I   |     |      | I     |

| Resolution                   |                 |                                              |               | 8   |     |      | bits  |

| Integral Linearity Error     | ILE             |                                              |               |     |     | ±1.5 | LSB   |

| Differential Linearity Error | DLE             |                                              |               |     |     | ±1   | LSB   |

| Offset Error                 |                 | $V_{CC} = 3.3 V \text{ or } 3.0 V$           | E Suffix      | 10  | 20  | 30   | mV    |

|                              |                 |                                              | I Suffix      | 5   | 20  | 35   | mV    |

|                              |                 | $V_{CC} = 5V$                                | E Suffix      | 15  | 25  | 35   | mV    |

|                              |                 |                                              | I Suffix      | 10  | 25  | 40   | mV    |

| Gain Error                   |                 |                                              |               |     |     | ±5   | %FS   |

| Analog Output                |                 |                                              |               |     |     |      |       |

| Output Drive Current         | IOUTPP          | Full scale output                            |               |     |     | 2    | mA    |

| Power Supply Rejection Ratio | PSRR            | @00 & FF                                     |               |     | 40  |      | dB    |

| Digital and DC               |                 |                                              |               | l   |     |      | ł     |

| Logic Input Low              | V <sub>IL</sub> | V <sub>CC</sub> = 3V, 3.3V, or 5V            |               |     |     | 0.8  | V     |

| Logic Input High             | V <sub>IH</sub> | $V_{CC} = 3V \text{ or } 3.3V$ $V_{CC} = 5V$ |               | 2.0 |     |      | V     |

|                              |                 |                                              |               | 2.8 |     |      | V     |

| Logic Input Low Current      | IIL             | V <sub>IN</sub> = GND                        |               | -1  |     |      | μΑ    |

| Logic Input High Current     | IIH             | $V_{IN} = V_{CC}$                            |               |     |     | 1    | μΑ    |

| Logic Output Low             | V <sub>OL</sub> | I = 3.2mA                                    |               |     |     | 0.4  | V     |

| Logic Output High            | V <sub>OH</sub> | I = 0.4mA                                    |               | 2.4 |     |      | V     |

| Supply Current               | I <sub>CC</sub> | $R_L = \Box$                                 |               |     | 2.5 | 3.5  | mA    |

| Power Down Current           | A               | All digital inputs at                        | $V_{CC} = 3V$ |     |     | 3    | μΑ    |

|                              |                 | static 0V or $V_{\mbox{\scriptsize CC}}$     | $V_{CC} = 5V$ |     |     | 5    | μΑ    |

| AC Performance               |                 |                                              |               |     |     |      |       |

| Settling Time                | ts              | ±1/2 LSB                                     |               |     | 5   | 10   | μs    |

| Slew Rate                    |                 | -                                            |               |     | 1.4 |      | V/µs  |

| Crosstalk                    |                 |                                              |               | 60  |     |      | dB    |

Note 1: Limits are guaratneed by 100% testing, sampling or correlation with worst case test conditions.

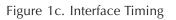

## TIMING CHARACTERISTICS (Serial Interface)

$V_{CC}$  = Operating Supply Voltage Range,  $C_L$  = 50pF,  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted

| PARAMETER SYMBOL                                       |                  | CONDITIONS                       | MIN | TYP | MAX | UNITS |

|--------------------------------------------------------|------------------|----------------------------------|-----|-----|-----|-------|

| Converter                                              |                  |                                  |     |     |     |       |

| $\overline{CS}$ Fall to S <sub>CLK</sub><br>Setup Time | t <sub>CSS</sub> |                                  | 20  |     |     | ns    |

| $S_{CLK}$ Rise to $\overline{CS}$<br>Rise Hold Time    | t <sub>CSH</sub> |                                  | 50  |     |     | ns    |

| D <sub>IN</sub> to S <sub>CLK</sub><br>Rise Setup Time | t <sub>DS</sub>  |                                  | 20  |     |     | ns    |

| D <sub>IN</sub> to S <sub>CLK</sub><br>Rise Hold Time  | t <sub>DH</sub>  |                                  | 20  |     |     | ns    |

| S <sub>CLK</sub> Frequency                             | f <sub>CLK</sub> |                                  |     | 10  |     | MHz   |

| S <sub>CLK</sub> Duty Cycle                            |                  |                                  | 40  |     | 60  | %     |

| S <sub>CLK</sub> to D <sub>OUT</sub> Valid             | t <sub>DO</sub>  | $V_{CC} = 3.3 V \text{ or } 5 V$ |     | 30  | 60  | ns    |

|                                                        |                  | $V_{CC} = 3V$                    |     | 45  | 90  | ns    |

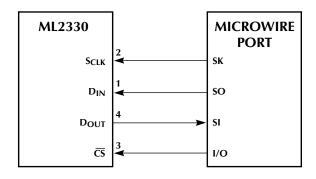

Figure 1a. Connections for Microwire.

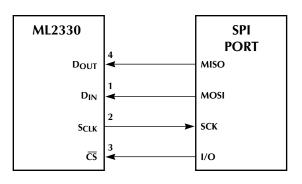

Figure 1b. Connections for SPI.

M

**Micro Linear**

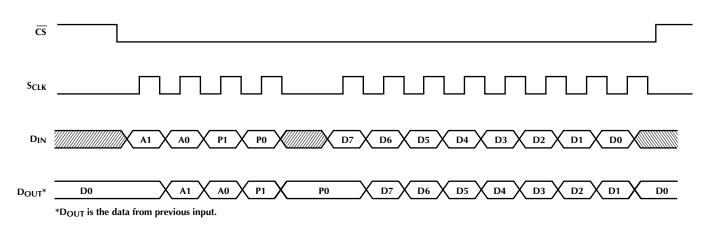

Figure 2. Detail Interface Timing

### FUNCTIONAL DESCRIPTION

#### SERIAL INTERFACE

The ML2330 communicates with microprocessors through a synchronous, full-duplex, 3-wire interface (figure 1A & B). At power on, the control registers are cleared and both DACs have high impedance outputs. Data timing shown in Figure 1C is sent MSB-first and can be transmitted in one 4-bit and one 8-bit packet or in one 12-bit word. If a 16-bit control word is used, the first four bits are ignored. The serial clock (S<sub>CLK</sub>) synchronizes the data transfer. Data is transmitted and received simultaneously. Figure 2 shows detailed serial interface timing. Note that the clock should be low between updates. D<sub>OUT</sub> does not go into a high impedance state if the clock idles or  $\overline{CS}$  is high.

Serial data is clocked into the data registers in MSB-first format, with the address and configuration information preceding the actual DAC data. Data is sampled on the  $S_{CLK}$ 's rising edge while  $\overline{CS}$  is low. Data at  $D_{OUT}$  is clocked out 12.5 clock cycles later, on the  $S_{CLK}$ 's falling edge.

Chip Select ( $\overline{CS}$ ) must be low to enable the read or write operation. If  $\overline{CS}$  is high, the interface is disabled and D<sub>OUT</sub> remains unchanged.  $\overline{CS}$  must go low at least 10ns before the first clock pulse to properly clock in the first bit. With  $\overline{CS}$  low, data is clocked into the ML2330's internal shift register on the rising edge of the external serial clock. S<sub>CLK</sub> can be driven at rates up to 10MHz.

# SERIAL INPUT DATA FORMAT AND CONFIGURATION CODES

The 12-bit serial input format shown in Figure 3 comprises two DAC address bits (A1, A0), two power down control bits (P1, P0) and eight bits of data (D7 . . . D0).

Figure 3. Serial Input Format

The 4-bit address/control code configures the DAC as shown in Table 1.

| A1 | A0 | Function                          |

|----|----|-----------------------------------|

| 0  | 0  | No operation                      |

| 0  | 1  | Select control bits and DAC A     |

| 1  | 0  | Select control bits and DAC B     |

| 1  | 1  | Select control bits and both DACs |

Table 1.1 Address Selection

| P1 | PO | Function               |

|----|----|------------------------|

| 0  | 0  | Normal                 |

| 0  | 1  | Power down DAC A       |

| 1  | 0  | Power down DAC B       |

| 1  | 1  | Power down entire chip |

Table 1.2 Power Down Selection

#### DAC OPERATION

The DACs are implemented using an array of equal current sources that are decoded linearly for the four most significant bits to improve differential linearity and to reduce output glitch around major carries. A voltage difference between on-board bandgap reference voltage and GND is converted to a reference current using an internal resistor to set up the appropriate current level in the DACs. The DACs output current is then converted to a voltage output by an output buffer and a resistive network. The matching among the on-chip resistors preserves the gain accuracy between these conversions.

# ML2330

### VOLTAGE REFERENCE

A bandgap voltage reference is incorporated on the ML2330. It is trimmed for zero temperature coefficient at 25°C to minimize output voltage drift over the specified operating temperature range.

#### OUTPUT BUFFER AND GAIN SETTING

The output buffer converts the DAC output current to a voltage output using a resistive network. The outputs can swing from GND +0.02V to either 2.02V (3V) or 4.02V (5V). The DAC transfer function is:

$$V_{OUT} = \frac{K \times DATA}{256} + 0.02$$

where K = 2 if  $V_{CC}$  = 3V and K = 4 if  $V_{CC}$  = 5V

In the 3V operation, the amplifier outputs will settle to 1/2LSB in 10µs when loads are greater than 1ký (2ký for 5V operation) and capacitive loads smaller than 100pF.

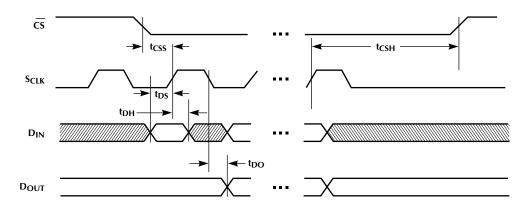

#### GAIN ERROR

The graph below shows how gain error varies with temperature when  $V_{CC} = 3.3V$ .

#### Gain Error vs Temperature

#### POWER DOWN MODE

There are three power-down modes in the ML2330. By clearing the control bits P1-P0 (Table 3.2), the entire chip will be powered down with a supply current less than  $5\mu$ A. Individual DACs can also be powered down to save power (1.75mA per DAC).

### PHYSICAL DIMENSIONS inches (millimeters)

### ORDERING INFORMATION

| PART NUMBER              | V <sub>CC</sub> | TEMPERATURE RANGE | PACKAGE          |

|--------------------------|-----------------|-------------------|------------------|

| ML2330ES-2               | 3V              | -20°C to 70°C     | 8-Pin SOIC (S08) |

| ML2330ES-3 (End Of Life) | 3.3V            | -20°C to 70°C     | 8-Pin SOIC (S08) |

| ML2330ES-5 (End Of Life) | 5V              | -20°C to 70°C     | 8-Pin SOIC (S08) |

| ML2330IS–2               | 3V              | -40°C to 85°C     | 8-Pin SOIC (S08) |

| ML2330IS–3 (Obsolete)    | 3.3V            | -40°C to 85°C     | 8-Pin SOIC (S08) |

| ML2330IS–5               | 5V              | -40°C to 85°C     | 8-Pin SOIC (S08) |

#### DS2330-01

© Micro Linear 1997 🕸 Micro Linear is a registered trademark of Micro Linear Corporation

Products described in this document may be covered by one or more of the following patents, U.S.: 4,897,611;4,964,026;5,027,116;5,281,862;5,283,483;5,418,502;5,508,570;5,510,727;5,523,940;5,546,017; 5,559,470;5,565,761;5,592,128;5,594,376; Japan: 2598946;2619299. Other patents are pending.

Micro Linear reserves the right to make changes to any product herein to improve reliability, function or design. Micro Linear does not assume any liability arising out of the application or use of any product described herein, neither does it convey any license under its patent right nor the rights of others. The circuits contained in this data sheet are offered as possible applications only. Micro Linear makes no warranties or representations as to whether the illustrated circuits infringe any intellectual property rights of others, and will accept no responsibility or liability for use of any application herein. The customer is urged to consult with appropriate legal counsel before deciding on a particular application.

2092 Concourse Drive San Jose, CA 95131 Tel: 408/433-5200 Fax: 408/432-0295

5/6/97 Printed in U.S.A.