# 24C08

# CMOS I<sup>2</sup>C 2-WIRE BUS 8K ELECTRICALLY ERASABLE PROGRAMMABLE ROM 1K X 8 BIT EEPROM

#### **FEATURES:**

- Extended Power Supply Voltage

Single Vcc for Read and Programming

(Vcc = 2.7 V to 5.5 V)

- Low Power (Isb = 2µa @ 5.5 V)

- I2C Bus, 2-Wire Serial Interface

- Support Byte Write and Page Write (16 Bytes)

- Automatic Page write Operation (maximum 10 ms) Internal Control Timer Internal Data Latches for 16 Bytes

- High Reliability CMOS Technology with EEPROM Cell Endurance: 1,000,000 Cycles

Data Retention: 100 Years

#### PIN DESCRIPTION

#### **DESCRIPTION:**

The Turbo IC 24C08 is a serial 8K EEPROM fabricated with Turbo's proprietary, high reliability, high performance CMOS technology. It's 8K of memory is organized as 1,024 x 8 bits. The memory is configured as 64 pages with each page containing 16 bytes. This device offers significant advantages in low power and low voltage applications.

The Turbo IC 24C08 uses the I<sup>2</sup>C addressing protocol and 2-wire serial interface which includes a bidirectional serial data bus synchronized by a clock. It offers a flexible byte write and a faster 16-byte page write.

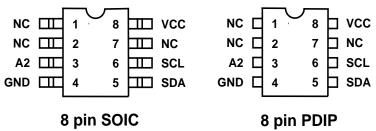

The Turbo IC 24C08 is assembled in either a 8-pin PDIP or 8-pin SOIC package. Pin #1, #2 and #7 are not connected (NC). Pin #3 is the A2 device address input for the 24C08, such that a total of two 24C08 devices can be connected on a single bus. Pin #4 is the ground (Vss). Pin #5 is the serial data (SDA) pin used for bidirectional transfer of data. Pin #6 is the serial clock (SCL) input pin. Pin #8 is the power supply (Vcc) pin.

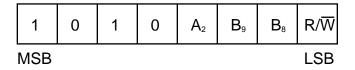

All data is serially transmitted in bytes (8 bits) on the SDA bus. To access the Turbo IC 24C08 (slave) for a read or write operation, the controller (master) issues a start condition by pulling SDA from high to low while SCL is high. The master then issues the device address byte which consists of 1010 (A2) (B9) (B8) (R/W). The most significant bits (1010) are a device type code signifying an EEPROM device. A2 is SDA the device address select bit which has to match the A2 pin input on the 24C08 device. The B[9:8] bits are the 2 most significant bits of the memory address. The read/write bit determines whether to do a read or write operation. After each byte is transmitted, the receiver has to provide an acknowledge by pulling the SDA bus low on the ninth clock cycle. The acknowledge is a handshake signal to the transmitter indicating a successful data transmission.

#### PIN DESCRIPTION

#### **DEVICE ADDRESS (A2)**

A2 is a device address input that enables a total of two 24C08 devices to connect on a single bus. When the address input pin is left unconnected, it is interpreted as zero.

#### **SERIAL DATA (SDA)**

SDA is a bidirectional pin used to transfer data in and out of the Turbo IC 24C08. The pin is an open-drain output. A pullup resistor must be connected from SDA to Vcc.

#### SERIAL CLOCK (SCL)

The SCL input synchronizes the data on the SDA bus. It is used in conjunction with SDA to define the start and stop conditions. It is also used in conjunction with SDA to transfer data to and from the Turbo IC 24C08.

1

## 24C08

#### **DESCRIPTION (Continued):**

For a write operation, the master issues a start condition, a device address byte, a memory address byte, and then up to 16 data bytes. The Turbo IC 24C08 acknowledges after each byte transmission. To terminate the transmission, the master issues a stop condition by pulling SDA from low to high while SCL is high.

For a read operation, the master issues a start condition and a device address byte. The Turbo IC 24C08 acknowledges, and then transmits a data byte, which is accessed from the EEPROM memory. The master acknowledges, indicating that it requires more data bytes. The Turbo IC 24C08 transmits more data bytes, with the memory address counter automatically incrementing for each data byte, until the master does not acknowledge, indicating that it is terminating the transmission. The master then issues a stop condition.

#### **DEVICE OPERATION:**

#### **BIDIRECTIONAL BUS PROTOCOL:**

The Turbo IC 24C08 follows the I²C bus protocol. The protocol defines any device that sends data onto the SDA bus as a transmitter, and the receiving device as a receiver. The device controlling the transfer is the master and the device being controlled is the slave. The master always initiates the data transfers, and provides the clock for both transmit and receive operations. The Turbo IC 24C08 acts as a slave device in all applications. Either the master or the slave can take control of the SDA bus, depending on the requirement of the protocol.

#### START/STOP CONDITION AND DATA TRANSITIONS:

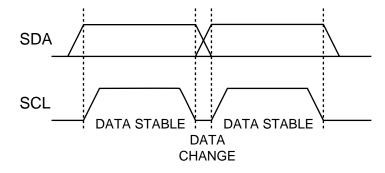

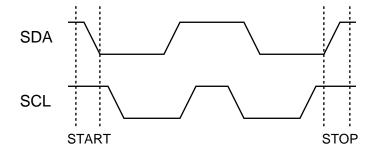

While SCL clock is high, a high to low transition on the SDA bus is recognized as a START condition which precedes any read or write operation. While SCL clock is high, a low to high transition on the SDA bus is recognized as a STOP condition which terminates the communication and places the Turbo IC 24C08 into standby mode. All other data transitions on the SDA bus must occur while SCL clock is low to ensure proper operation.

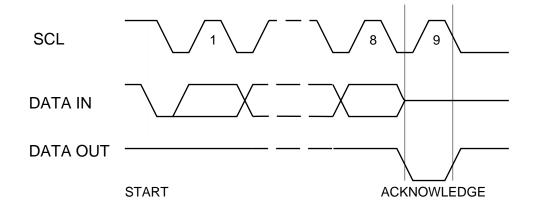

#### **ACKNOWLEDGE:**

All data is serially transmitted in bytes (8 bits) on the SDA bus. The acknowledge protocol is used as a handshake signal to indicate successful transmission of a byte of data. The bus transmitter, either the master or the slave (Turbo IC 24C08), releases the bus after sending a byte of data on the SDA bus. The receiver pulls the SDA bus low during the ninth clock cycle to acknowledge the successful transmission of a byte of data. If the SDA is not pulled low during the ninth clock cycle, the Turbo IC 24C08 terminates the data transmission and goes into standby mode.

For the write operation, the Turbo IC 24C08 acknowledges after the device address byte, acknowledges after the memory address byte, and acknowledges after each subsequent data byte.

For the read operation, the Turbo IC 24C08 acknowledges after the device address byte. Then the Turbo IC 24C08 transmits each subsequent data byte, and the master acknowledges after each data byte transfer, indicating that it requires more data bytes. The Turbo IC 24C08 monitors the SDA bus for the acknowledge. To terminate the transmission, the master does not acknowledge, and then sends a stop condition.

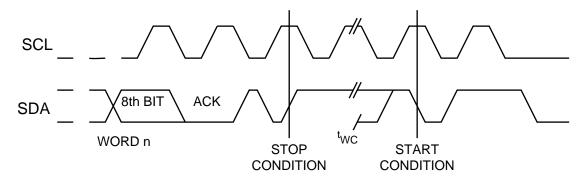

## **Write Cycle Timing**

Note: The write cycle time  $t_{WC}$  is the time from a valid stop condition of a write sequence to the end of the internal clear / write cycle.

# 24C08

#### **Data Valid**

## **Start and Stop Definition**

## **Output Acknowledge**

## 24C08

#### **DEVICE ADDRESSING:**

Following the start condition, the master will issue a device address byte consisting of 1010 (A2) (B9) (B8) (R/W) to access the selected Turbo IC 24C08 for a read or write operation. A2 is the device address select bit which has to match the A2 pin input on the 24C08 device. The B[9:8] bits are the 2 most significant bits of the memory address. The (R/W) bit is a high (1) for read and low (0) for write.

#### DATA INPUT DURING WRITE OPERATION:

During the write operation, the Turbo IC 24C08 latches the SDA bus signal on the rising edge of the SCL clock.

#### DATA OUTPUT DURING READ OPERATION:

During the read operation, the Turbo IC 24C08 serially shifts the data onto the SDA bus on the falling edge of the SCL clock.

#### **MEMORY ADDRESSING:**

The memory address is sent by the master in the form of 2 bytes. Device address A2 and memory address bits B[9:8], are included in the device address byte. The remaining memory address bits B[7:0] are included in the second byte. The memory address byte can only be sent as part of a write operation.

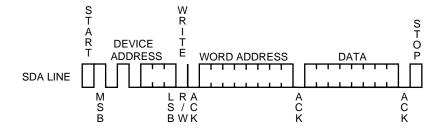

#### **BYTE WRITE OPERATION:**

The master initiates the byte write operation by issuing a start condition, followed by the device address byte 1010 (A2) (B9) (B8) 0, followed by the memory address byte, followed by one data byte, followed by an acknowledge, then a stop condition. After each byte transfer, the Turbo IC 24C08 acknowledges the successful data transmission by pulling the SDA bus low. The stop condition starts the internal EEPROM write cycle, and all inputs are disabled until the completion of the write cycle.

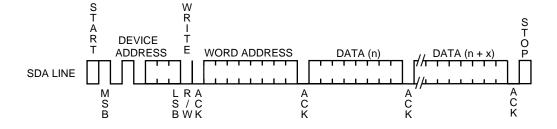

#### PAGE WRITE OPERATION:

The master initiates the page write operation by issuing a start condition, followed by the device address byte 1010 (A2) (B9) (B8) 0, followed by the memory address byte, followed by up to 16 data bytes, followed by an acknowledge, then a stop condition. After each byte transfer, the Turbo IC 24C08 acknowledges the successful data transmission by pulling SDA low. After each data byte transfer, the memory address counter is automatically incremented by one. The stop condition starts the internal EEPROM write cycle only if the stop condition occurs in the clock cycle immediately following the acknowledge (10th clock cycle). All inputs are disabled until the completion of the write cycle.

#### **POLLING ACKNOWLEDGE:**

During the internal write cycle of a write operation in the Turbo IC 24C08, the completion of the write cycle can be detected by polling acknowledge. The master starts acknowledge polling by issuing a start condition, then followed by the device address byte 1010 (A2) (B9) (B8) 0. If the internal write cycle is finished, the Turbo IC 24C08 acknowledges by pulling the SDA bus low. If the internal write cycle is still ongoing, the Turbo IC 24C08 does not acknowledge because it's inputs are disabled. Therefore, the device will not respond to any command. By using polling acknowledge, the system delay for write operations can be reduced. Otherwise, the system needs to wait for the maximum internal write cycle time, tWC, given in the spec.

#### **POWER ON RESET:**

The Turbo IC 24C08 has a Power On Reset circuit (POR) to prevent data corruption and accidental write operations during power up. On power up, the internal reset signal is on and the Turbo IC 24C08 will not respond to any command until the VCC voltage has reached the POR threshold value.

# 24C08

#### **Device Address**

## **Byte Write**

## Page Write

## 24C08

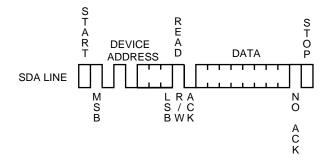

#### **CURRENT ADDRESS READ:**

The internal memory address counter of the Turbo IC 24C08 contains the last memory address accessed during the previous read or write operation, incremented by one. To start the current address read operation, the master issues a start condition, followed by the device address byte 1010 (A2) (B9) (B8) 1. The Turbo IC 24C08 responds with an acknowledge by pulling the SDA bus low, and then serially shifts out the data byte accessed from memory at the location corresponding to the memory address counter. The master does not acknowledge, then sends a stop condition to terminate the read operation. It is noted that the memory address counter is incremented by one after the data byte is shifted out.

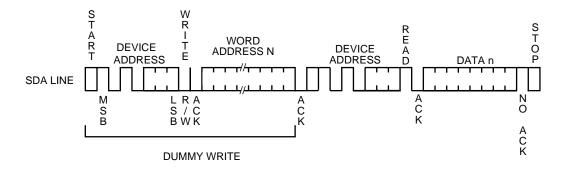

#### **RANDOM ADDRESS READ:**

The master starts with a dummy write operation (one with no data bytes) to load the internal memory address counter by first issuing a start condition, followed by the device address byte 1010 (A2) (B9) (B8) 0, followed by the memory address bytes. Following the acknowledge from the Turbo IC 24C08, the master starts the current read operation by issuing a start condition, followed by the device address byte 1010 (A2) (B9) (B8) 1. The Turbo IC 24C08 responds with

an acknowledge by pulling the SDA bus low, and then serially shifts out the data byte accessed from memory at the location corresponding to the memory address counter. The master does not acknowledge, then sends a stop condition to terminate the read operation. It is noted that the memory address counter is incremented by one after the data byte is shifted out.

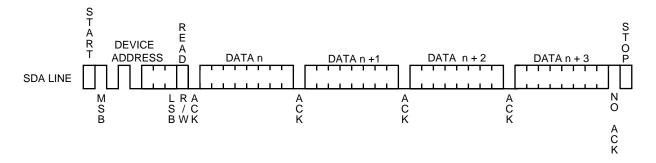

#### **SEQUENTIAL READ:**

The sequential read is initiated by either a current address read or random address read. After the Turbo IC 24C08 serially shifts out the first data byte, the master acknowledges by pulling the SDA bus low, indicating that it requires additional data bytes. After the data byte is shifted out, the Turbo IC 24C08 increments the memory address counter by one. Then the Turbo IC 24C08 shifts out the next data byte. The sequential reads continues for as long as the master keeps acknowledging. When the memory address counter is at the last memory location, the counter will 'roll-over' when incremented by one to the first location in memory (address zero). The master terminates the sequential read operation by not acknowledging, then sends a stop condition.

#### **Current Address Read**

#### **Random Read**

# 24C08

#### Sequential Read

#### **ABSOLUTE MAXIMUM RATINGS**

**TEMPERATURE**

-65° C to 150° C -55° C to 125° C Storage: Under Bias:

ALL INPUT OR OUTPUT VOLTAGES

with respect to Vss +6 V to -0.3 V

\* "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **RECOMMENDED OPERATING CONDITIONS**

Temperature Range: Commercial: 0° C to 70° C

-40° C to 85° C Industrial:

-55° C to 125° C Military:

Vcc Supply Voltage: 2.7 to 5.5 Volts

4.5 to 5.5 Volts

**Endurance:** 100,000 Cycles/Byte (Typical)

Data Retention: 100 Years

#### D.C. CHARACTERISTICS

| Symbol           | Parameter              | Condition             | Min     | Max     | Units |

|------------------|------------------------|-----------------------|---------|---------|-------|

| I <sub>cc1</sub> | Active Vcc Current     | READ at 100 KHZ       |         | 1.0     | MA    |

| I <sub>cc2</sub> | Active Vcc Current     | WRITE at 100 KHZ      |         | 3.0     | MA    |

| I <sub>sb1</sub> | Standby Current        | Vcc = 2.7 v           |         | 0.5     | uA    |

| 351              |                        | Vcc = 5.5 v           |         | 2.0     | uA    |

| I <sub>sb2</sub> | Standby Current        | Vcc = 4.5 v           |         | 20.0    | uA    |

| 352              |                        | Vcc = 5.5 v           |         | 35.0    | uA    |

| l <sub>il</sub>  | Input Leakage Current  | Vin=Vcc Max           |         | 3       | uA    |

| I <sub>ol</sub>  | Output Leakage Current |                       |         | 3       | uA    |

| V <sub>il</sub>  | Input Low Voltage      |                       | -1.0    | 8.0     | V     |

| V <sub>ih</sub>  | Input High Voltage     |                       | Vccx0.7 | Vcc+0.5 | V     |

| V <sub>ol2</sub> | Output Low             | Vcc=3.0v Iol=2.1 mA   |         | 0.4     | V     |

| V <sub>ol1</sub> | Output Low             | Vcc=2.7v lol=-0.15 mA |         | 0.25    | V     |

# 24C08

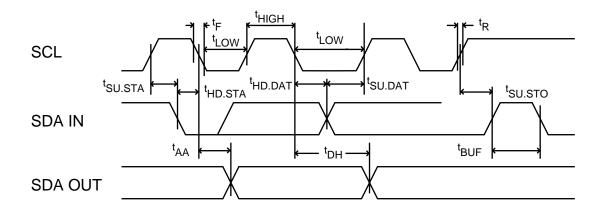

#### **Bus Timing**

#### A.C. CHARACTERISTICS

| Symbol                                                                                                                                                    | Parameter                                                                                                                                                                                                                             | 2.7 volt                                                 |                   | 5.5 volt                                            |                   |                                      |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-------------------|-----------------------------------------------------|-------------------|--------------------------------------|

| SCL T t <sub>LOW</sub> t <sub>HIGH</sub> t <sub>AA</sub> t <sub>BUF</sub> t <sub>HD.STA</sub> t <sub>SU.STA</sub> t <sub>HD.DAT</sub> t <sub>SU.DAT</sub> | SCL Clock Frequency Noise Suppression Time (1) Clock Low Period Clock High Period SCL Low to SDA Data Out Bus Free to New Start (1) Start Hold Time Start Set-up Time Data-in Hold Time Data-in Set-up Time SCL and SDA Rise Time (1) | 2.7 vo<br>Min  4.7  4.0  0.1  4.7  4.0  4.7  0  200  1.0 | Max<br>100<br>100 | 5.5 v<br>Min  1.2 0.6 0.1 1.2 0.6 0.6 0.6 0 100 0.3 | Max<br>400<br>100 | Units kHZ ns us us us us us us us us |

| t <sub>R</sub><br>t <sub>F</sub><br>t <sub>SU.STO</sub><br>t <sub>DH</sub><br>t <sub>WC</sub>                                                             | SCL and SDA Fall Time (1) Stop Set-up Time Data-out Hold Time Write Cycle Time                                                                                                                                                        | 300<br>4.7<br>100<br>10                                  |                   | 300<br>0.6<br>50<br>10                              |                   | ns<br>us<br>ns<br>ms                 |

Note: 1 This parameter is characterized and not 100% tested.

#### TURBO IC PRODUCTS AND DOCUMENTS

- All documents are subject to change without notice. Please contact Turbo IC for the latest revision of documents.

- Turbo IC does not assume any responsibility for any damage to the user that may result from accidents or operation under abnormal conditions.

- Turbo IC does not assume any responsibility for the use of any circuitry other than what embodied in a Turbo IC product. No other circuits, patents, licenses are implied.

- 4. Turbo IC products are not authorized for use in life support systems or other critical systems where component failure may endanger life. System designers should design with error detection and correction, redundancy and back-up features.

# Part Numbers & Order Information TU24C08BS3I 1K X 8 Serial Package Voltage Temperature EEPROM P -PDIP 3 - 2.7V to 5.5V -Commercial s - 4.5V to 5.5 V I -Industrial