# 512K x 32 SSRAM / 1M x 64 SDRAM EXTERNAL MEMORY SOLUTION FOR LUCENT'S LUCTAPC640 ATM PORT CONTROLLER

## **FEATURES**

■ Clock speeds:

SSRAM: 100 MHzSDRAM: 100 MHz

■ 100% tested to timing requirements of LUCTAPC640's memory interface

Packaging:

192 pin BGA, 21mm x 21mm

3.3V Operating supply voltage

Direct control interface to both the CRAM and VCRAM ports on the LUCTAPC640

■ 62% space savings vs. monolithic solution

Reduced system inductance and capacitance

## DESCRIPTION

The WED9LAPC3C16V8BC is a 3.3V, 512K x 32 Synchronous Pipeline SRAM and a 1M x 64 Synchronous DRAM array packaged in a 21mm x 21mm 192 lead BGA.

The WED9LAPC3C16V8BC provides the memory required for the CRAM (Control Memory) and VCRAM (Virtual Connection Memory) memory ports for Lucent's LUCTAPC640 ATM port controller. When used in conjunction with the WED9LAPC2B16P8BC, which provides memory for the BRAM (Buffer Memory) and PRAM (Pointer Memory) memory ports, the entire memory requirement of the LUCTAPC640 can be met using these 2 BGA devices.

The WED9LAPC3C16V8BC facilitates the addition of an external Synchronous SRAM, effectively doubling the SRAM array by adding a chip select/de-select function (SSCE#).

The WED9LAPC3C16V8BC is 100% tested to the timing requirements of the LUCTAPC640's memory interface timing for both Commercial and Industrial temperature ranges.

## PIN CONFIGURATION PINOUT CRAM AND VCRAM MCM -- TOP VIEW

|   | 1        | 2        | 3        | 4        | 5        | 6       | 7       | 8       | 9        | 10         | 11       | 12       | 13       | 14       | 15       | 16       |

|---|----------|----------|----------|----------|----------|---------|---------|---------|----------|------------|----------|----------|----------|----------|----------|----------|

| Α | CADDR    | CADDR    | Vcc      | CDATA    | CDATA    | Vss     | CDATA   | CDATA   | Vcc      | CDATA      | CDATA    | Vss      | CDATA    | CDATA    | Vcc      | CADDR    |

| В | CWE#     | CADDR    | CDATA    | CDATA    | CDATA    | CDATA   | CDATA   | CDATA   | CDATA    | CDATA      | CDATA    | CDATA    | CDATA    | CDATA    | CADDR    | CADDR    |

| С | COE#     | CADDR    | CDATA    | CDATA    | CDATA    | CDATA   | CDATA   | CDATA   | CDATA    | CDATA      | CDATA    | CDATA    | CDATA    | CDATA    | CADDR    | CADDR    |

| D | Vss      | CADDR    | CADDR    | Vcc      | Voc      | Vcc     | Vss     | Vss     | Vss      | Vcc        | Vcc      | Vcc      | Vss      | CADDR    | CADDR    | CADDR    |

| Е | GCK      | Vss      | SSCE#    | Vcc      |          |         |         |         |          |            |          |          | Vss      | CADDR    | CADDR    | CADDR    |

| F | Vss      | VCDATA_b | VCDATA_b | Vcc      |          |         |         |         |          |            |          |          | Vcc      | CADDR0   | CADDR1   | Vss      |

| G | VCDATA_b | VCDATA_b | VCDATA_b | Vss      |          |         |         |         |          |            |          |          | Vcc      | VCDATA_a | VCDATA_a | VCDATA_a |

| Н | VCDATA_b | VCDATA_b | VCDATA_b | Vss      |          |         |         |         |          |            |          |          | Vss      | VCDATA_a | VCDATA_a | VCDATA_a |

| J | Vcc      | VCDATA_b | VCDATA_b | Vss      |          |         |         |         |          |            |          |          | Vss      | VCDATA_a | VCDATA_a | Vcc      |

| К | VCDATA_b | VCDATA_b | VCDATA_b | Vcc      |          |         |         |         |          |            |          |          | Vss      | VCDATA_a | VCDATA_a | VCDATA_a |

| L | VCDATA_b | VCDATA_b | VCDATA_b | Vcc      |          |         |         |         |          |            |          |          | Vcc      | VCDATA_a | VCDATA_a | VCDATA_a |

| М | Vss      | VCDATA_b | VCDATA_b | Vcc      |          |         |         |         |          |            |          |          | Vcc      | VCDATA_a | VCDATA_a | Vss      |

| N | VCDATA_b | VCDATA_b | VCDATA_b | Vss      | Vss      | Vss     | Vcc     | Voc     | Vcc      | Vss        | Vss      | Vss      | Vss      | Vcc      | VCDATA_a | VCDATA_a |

| Р | VCDATA_b | VCDATA_b | VCDATA_b | VCDATA_b | VCDATA_b | Vss     | VCADDR0 | VCADDR2 | VCADDR10 | VCADDR6    | Vss      | VCDATA_a | VCDATA_a | VCDATA_a | VCDATA_a | VCDATA_a |

| R | Vcc      | VCDATA_b | VCDATA_b | VCDATA_b | VCBS     | VCADDR8 | VCADDR1 | VCADDR3 | VCADDR4  | VCADDR7    | VCDATA_a | VCDATA_a | VCDATA_a | VCDATA_a | VCDATA_a | Vcc      |

| Т | VCDATA_b | VCDATA_b | Vss      | VCDATA_b | VCDQM    | VCCAS#  | VCWE#   | VCRAS#  | VCADDR5  | VCADDR9/AP | Vcc      | VCDATA_a | VCDATA_a | Vss      | VCDATA_a | VCDATA_a |

## **PIN CONFIGURATION (CONTINUED) PIN DESCRIPTION**

| Symbol | Pin Name                    | Description                                                                            |

|--------|-----------------------------|----------------------------------------------------------------------------------------|

| CADDR  | CRAM Address                | Address pins for the SSRAM that serves as the control RAM (CRAM)                       |

| CDATA  | CRAM Data                   | Data I/O pins for the SSRAM control memory (CRAM)                                      |

| CWE#   | CRAM write enable           | Write enable control for the SSRAM control memory (CRAM)                               |

| COE#   | CRAM output enable          | Output enable control pin for the SSRAM control memory (CRAM)                          |

| VCADDR | VCRAM address               | Address pins for the SDRAM memory that serves as the virtual connection memory (VCRAM) |

| VCDATA | VCRAM data                  | Data I/O pins for the SDRAM virtual connection memory (VCRAM)                          |

| VCBS   | VCRAM bank select           | Bank address pin for the SDRAM virtual connection memory (VCRAM)                       |

| VCDQM  | VCRAM DQM                   | DQM (data mask) pin for the SDRAM virtual conection memory (VCRAM)                     |

| VCRAS# | VCRAM row address strobe    | RAS# pin for the SDRAM virtual connection memory (VCRAM)                               |

| VCCAS# | VCRAM column address strobe | CAS# pin for the SDRAM virtual connection memory (VCRAM)                               |

| VCWE#  | VCRAM write enable          | Write enable pin for the SDRAM virtual connection memory (VCRAM)                       |

| GCK    | Global clock                | Common clock pin for both the CRAM and VCRAM memory arrays                             |

| Vcc    | Power supply                | Power supply pins                                                                      |

| Vss    | Ground                      | Ground Pins                                                                            |

| SSCE#  | SSRAM Chip Enable           | Allows banking with external 512K x 32 SSRAM                                           |

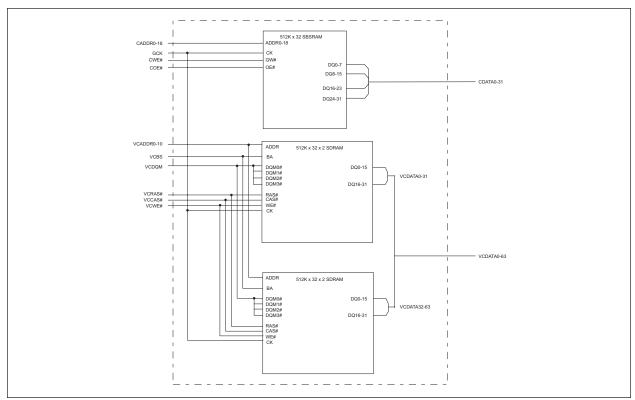

## FIGURE 1 - BLOCK DIAGRAM 512K X 32 SSRAM / 1M X 64

White Electronic Designs Corp. reserves the right to change products or specifications without notice.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage on Vcc Relative to Vss | -0.5V to +4.6V     |

|--------------------------------|--------------------|

| Vin (DQx)                      | -0.5V to Vcc +0.5V |

| Storage Temperature (BGA)      | -55°C to +125°C    |

| Junction Temperature           | +125°C             |

| Short Circuit Output Current   | 50 mA              |

<sup>\*</sup> Stress greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions greater than those indicated in operational sections of this specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## RECOMMENDED DC OPERATING CONDITIONS

$(0^{\circ}C \le T_A \le 70^{\circ}C; V_{CC} = 3.3V \pm 5\% \text{ unless otherwise noted})$

| Parameter                                                      | Symbol          | Min   | Max      | Units |

|----------------------------------------------------------------|-----------------|-------|----------|-------|

| Supply Voltage <sup>1</sup>                                    | Vcc             | 3.135 | 3.465    | V     |

| Input High Voltage <sup>1,2</sup>                              | V <sub>IH</sub> | 2.0   | Vcc +0.3 | V     |

| Input Low Voltage <sup>1,2</sup>                               | VIL             | -0.3  | 0.8      | V     |

| Input Leakage Current<br>0 ≤ V <sub>IN</sub> ≤ V <sub>CC</sub> | lu              | -10   | 10       | μΑ    |

| Output Leakage (Output Disabled)<br>0 ≤ V <sub>IN</sub> ≤ Vcc  | llo             | -10   | 10       | μΑ    |

| CRAM Output High (IoH = -4mA)1                                 | Vон             | 2.4   | _        | V     |

| CRAM Output Low (IoL = 8mA)1                                   | Vol             | _     | 0.4      | V     |

| VCRAM Output High (IoH = -2mA)1                                | Vон             | 2.4   | _        | V     |

| VCRAM Output Low (IoL = 2mA)1                                  | Vol             | _     | 0.4      | V     |

### NOTES:

- 1. All voltages referenced to Vss (GND).

- 2. Overshoot:  $-V_{IH} \le +6.0V$  for  $t \le t_{KC/2}$ Undershoot:  $-V_{IL} \ge -2.0V$  for  $t \le t_{KC/2}$

### DC ELECTRICAL CHARACTERISTICS

| Description       | Conditions                   | Symbol | Тур | Max | Units |

|-------------------|------------------------------|--------|-----|-----|-------|

| Operating Current | CRAM and VCRAM active        | Icc1   | 400 | 500 | mA    |

| Operating Current | CRAM active/VCRAM inactive   | Icc2   | 350 | 390 | mA    |

| Operating Current | CRAM inactive/VCRAM active   | Іссз   | 270 | 330 | mA    |

| Operating Current | CRAM inactive/VCRAM inactive | Icc4   | 150 | 180 | mA    |

## **BGA CAPACITANCE**

| Description                            | Conditions                      | Symbol | Тур | Max | Units |

|----------------------------------------|---------------------------------|--------|-----|-----|-------|

| Address Input Capacitance <sup>1</sup> | T <sub>A</sub> = 25°C; f = 1MHz | CL     | 5   | 8   | pF    |

| Input/Output Capacitance (DQ)1         | T <sub>A</sub> = 25°C; f = 1MHz | Co     | 8   | 10  | pF    |

| Control Input Capacitance <sup>1</sup> | T <sub>A</sub> = 25°C; f = 1MHz | CA     | 5   | 8   | pF    |

| Clock Input Capacitance <sup>1</sup>   | T <sub>A</sub> = 25°C; f = 1MHz | Сск    | 4   | 6   | pF    |

### NOTE:

### **SSRAM AC CHARACTERISTICS**

| Parameter                                     | Symbol | Min | Max | Units |

|-----------------------------------------------|--------|-----|-----|-------|

| Clock Cycle Time                              | tкнкн  | 7.5 |     | ns    |

| Clock HIGH Time                               | tklkh  | 3.0 |     | ns    |

| Clock LOW Time                                | tkhkl  | 3.0 |     | ns    |

| Clock to output valid                         | tkhqv  |     | 4.2 | ns    |

| Clock to output invalid                       | tkhqx  | 1.5 |     | ns    |

| Clock to output in Low-Z                      | tkqlz  | 1.5 |     | ns    |

| Clock to output in High-Z                     | tkqHz  | 1.5 | 3.5 | ns    |

| Output Enable to output valid                 | toelqv |     | 4.2 | ns    |

| Output Enable to output in Low-Z              | toelz  | 0   |     | ns    |

| Output Enable to output in High-Z             | toenz  |     | 3.5 | ns    |

| Address, Control, Data-in Setup Time to Clock | ts     | 1.5 |     | ns    |

| Address, Control, Data-in Hold Time to Clock  | tн     | 0.5 |     | ns    |

White Electronic Designs Corp. reserves the right to change products or specifications without notice.

<sup>1.</sup> This parameter is sampled.

### SSRAM OPERATION TRUTH TABLE

| Operation                | Address Used | CWE# | COE# | CDATA  |

|--------------------------|--------------|------|------|--------|

| WRITE Cycle, Begin Burst | External     | L    | Х    | D      |

| READ Cycle, Begin Burst  | External     | Н    | L    | Q      |

| READ Cycle, Begin Burst  | External     | Н    | Н    | High-Z |

#### NOTE:

- 1.  $\,$  X means "don't care", H means logic HIGH. L means logic LOW.

- All inputs except SSOE# must meet setup and hold times around the rising edge (LOW to HIGH) of SSCLK.

- For a write operation following a read operation, SSOE# must be HIGH before the input data required setup time plus High-Z time for SSOE# and staying HIGH thoughout the input data hold time.

- 4. This device contains circuitry that will ensure the outputs will be in High-Z during power-up.

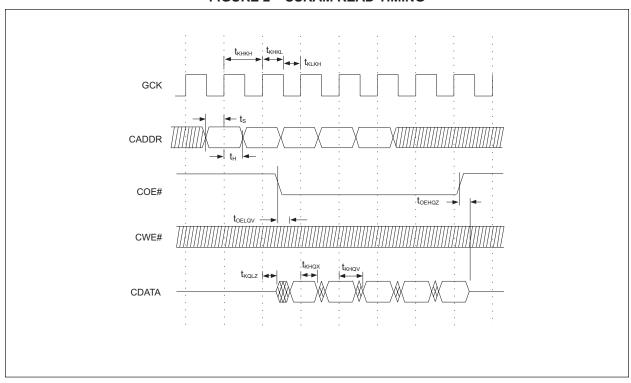

### FIGURE 2 - SSRAM READ TIMING

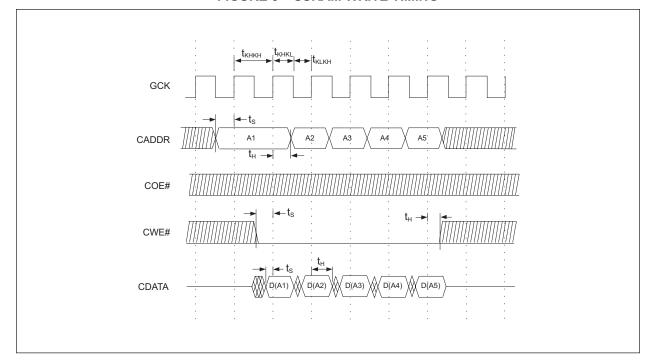

## FIGURE 3 - SSRAM WRITE TIMING

### SDRAM AC CHARACTERISTICS

| Parameter                                             |                                       | Symbol           | Min | Max    | Units |

|-------------------------------------------------------|---------------------------------------|------------------|-----|--------|-------|

| Clark Cycle Time1                                     | CL = 3                                | tcc              | 8   | 1000   | ns    |

| Clock Cycle Time <sup>1</sup>                         | CL = 2                                | tcc              | 10  | 1000   | ns    |

| Clock to valid Output delay <sup>1,2</sup>            |                                       | tsac             |     | 6      | ns    |

| Output Data Hold Time <sup>2</sup>                    |                                       | tон              | 2.5 |        | ns    |

| Clock HIGH Pulse Width <sup>3</sup>                   |                                       | tсн              | 3   |        | ns    |

| Clock LOW Pulse Width <sup>3</sup>                    |                                       | tcL              | 3   |        | ns    |

| Input Setup Time <sup>3</sup>                         |                                       | tss              | 2   |        | ns    |

| Input Hold Time <sup>3</sup>                          |                                       | tsн              | 1   |        | ns    |

| CK to Output Low-Z <sup>2</sup>                       |                                       | tsız             | 1   |        | ns    |

| CK to Output High-Z                                   |                                       | tsнz             |     | 6      | ns    |

| Row Active to Row Active Delay <sup>4</sup>           |                                       | t <sub>RRD</sub> | 16  |        | ns    |

| RAS# to CAS# Delay <sup>4</sup>                       |                                       | trcd             | 20  |        | ns    |

| Row Precharge Time <sup>4</sup>                       |                                       | t <sub>RP</sub>  | 20  |        | ns    |

| Row Active Time <sup>4</sup>                          |                                       | tras             | 48  | 10,000 | ns    |

| Row Cycle Time - Operation <sup>4</sup>               |                                       | trc              | 70  |        | ns    |

| Row Cycle Time - Auto Refresh <sup>4,8</sup>          |                                       | trfc             | 70  |        | ns    |

| Last Data in to New Column Address Delay <sup>5</sup> |                                       | tcdl             | 1   |        | CK    |

| Last Data in to Row Precharge <sup>5</sup>            |                                       | t <sub>RDL</sub> | 2   |        | CK    |

| Last Data in to Burst Stop <sup>5</sup>               |                                       | t <sub>BDL</sub> | 1   |        | CK    |

| Column Address to Column Address Delay <sup>6</sup>   | · · · · · · · · · · · · · · · · · · · | tccp             | 1   |        | CK    |

| Number of Valid Output Data <sup>7</sup>              |                                       |                  |     | 2      | ea    |

| Number of valid Output Data                           |                                       |                  |     | 1      | ea    |

### NOTES:

- 1. Parameters depend on programmed CAS latency.

- 2. If clock rise time is longer than 1ns (trise/2 -0.5)ns should be added to the parameter.

- 3. Assumed input rise and fall time = 1ns. If trise of tFALL are longer than 1ns. [(trise = tFALL)/2] 1ns should be added to the parameter.

- 4. The minimum number of clock cycles required is determined by dividing the minimum time required by the clock cycle time and then rounding up to the next higher integer.

- 5. Minimum delay is required to complete write.

- 6. All devices allow every cycle column address changes.

- 7. In case of row precharge interrupt, auto precharge and read burst stop.

- 8. A new command may be given trec after self-refresh exit.

## **CLOCK FREQUENCY AND LATENCY PARAMETERS**

(Unit = number of clock)

| Cycle Time | CAS     | trc  | tras | t <sub>RP</sub> | t <sub>RRD</sub> | trcd | tccp | tcdl | t <sub>RDL</sub> |

|------------|---------|------|------|-----------------|------------------|------|------|------|------------------|

|            | Latency | 70ns | 48ns | 20ns            | 16ns             | 20ns | 10ns | 10ns | 10ns             |

| 8.0ns      | 3       | 9    | 6    | 3               | 2                | 3    | 1    | 1    | 2                |

| 10.0ns     | 2       | 7    | 5    | 2               | 2                | 2    | 1    | 1    | 2                |

## REFRESH CYCLE PARAMETERS

| Parameter                     | Symbol | Min | Max | Units |

|-------------------------------|--------|-----|-----|-------|

| Refresh Period <sup>1,2</sup> | tref   | _   | 64  | ms    |

### NOTES:

- 2. Any time that the Refresh Period has been exceeded, a minimum of two Auto (CBR) Refresh commands must be given to "wake-up" the device.

White Electronic Designs Corp. reserves the right to change products or specifications without notice.

### SDRAM COMMAND TRUTH TABLE

| FUNCTION                  |                     | VCRAS# | VCCAS# | VCWE# | VCDQM# | VCBS           | VCADDR | NOTES |

|---------------------------|---------------------|--------|--------|-------|--------|----------------|--------|-------|

| Mode Register             | Set                 | L      | L      | L     | Х      | OP CODE        |        |       |

| Auto Refresh (            | CBR)                | L      | L      | Н     | Х      | Х              | Х      |       |

| Precharge                 | Single Bank         | L      | Н      | L     | Х      | BA             | L      | 2     |

|                           | Precharge all Banks | L      | Н      | L     | Х      | Х              | Н      |       |

| Bank Activate             | •                   | L      | Н      | Н     | Х      | BA Row Address |        | 2     |

| Write                     |                     | Н      | L      | L     | Х      | BA             | L      | 2     |

| Write with Auto           | Precharge           | Н      | L      | L     | Х      | BA             | Н      | 2     |

| Read                      | -                   | Н      | L      | L     | Х      | BA             | L      | 2     |

| Read with Auto            | Precharge           | Н      | L      | Н     | Х      | BA             | Н      | 2     |

| Burst Terminati           | on                  | Н      | Н      | L     | Х      | Х              | Х      | 3     |

| No Operation              |                     | Н      | Н      | Н     | Х      | Х              | Х      |       |

| Data Write/Output Disable |                     | Х      | Х      | Х     | L      | Х              | Х      | 4     |

| Data Mask/Output Disable  |                     | Х      | Х      | Х     | Н      | Х              | Х      | 4     |

### NOTES:

- 1. All of the SDRAM operations are defined by states of VCWE#, VCRAS#, VCCAS#, and VCDQM# at the positive rising edge of the clock.

- 2. Bank Select (VCBS), if VCBS = 0 then bank A is selected, if VCBS = 1 then bank B is selected.

- 3. During a Burst Write cycle there is a zero clock delay, for a Burst Read cycle the delay is equal to the CAS latency.

- 4. The VCDQM# has two functions for the data DQ Read and Write operations. During a Read cycle, when VCDQM# goes high at a clock timing the data outputs are disabled and become high impedance after a two clock delay. VCDQM# also provides a data mask function for Write cycles. When it activates, the Write operation at the clock is prohibited (zero clock latency).

## **SDRAM CURRENT STATE TRUTH TABLE**

| 0              |        |        |       | Comn | Action      | Notes                |                                          |       |

|----------------|--------|--------|-------|------|-------------|----------------------|------------------------------------------|-------|

| Current State  | VCRAS# | VCCAS# | VCWE# | VCBS | VCADDR      | Description          | Action                                   | Notes |

|                | L      | L      | L     | Ol   | Code Code   | Mode Register Set    | Set the Mode Register                    | 1     |

|                | L      | L      | Н     | Х    | Х           | Auto or Self Refresh | Start Auto                               | 1     |

|                | L      | Н      | L     | Х    | Х           | Precharge            | No Operation                             |       |

| L.II.          | L      | Н      | Н     | BA   | Row Address | Bank Activate        | Activate the specified bank and row      |       |

| Idle           | Н      | L      | L     | BA   | Column      | Write w/o Precharge  | ILLEGAL                                  | 2     |

|                | Н      | L      | Н     | BA   | Column      | Read w/o Precharge   | ILLEGAL                                  | 1     |

|                | Н      | Н      | L     | Х    | Х           | Burst Termination    | No Operation                             | 1     |

|                | Н      | Н      | Н     | Х    | Х           | No Operation         | No Operation                             |       |

|                | L      | L      | L     | Ol   | Code        | Mode Register Set    | ILLEGAL                                  |       |

|                | L      | L      | Н     | Х    | Х           | Auto or Self Refresh | ILLEGAL                                  |       |

|                | L      | Н      | L     | Х    | Х           | Precharge            | Precharge                                | 3     |

| D 4 "          | L      | Н      | Н     | BA   | Row Address | Bank Activate        | ILLEGAL                                  | 1     |

| Row Active     | Н      | L      | L     | BA   | Column      | Write                | Start Write; Determine if Auto Precharge | 4,5   |

|                | Н      | L      | Н     | BA   | Column      | Read                 | Start Read; Determine if Auto Precharge  | 4,5   |

|                | Н      | Н      | L     | Х    | Х           | Burst Termination    | No Operation                             |       |

|                | Н      | Н      | Н     | Х    | Х           | No Operation         | No Operation                             |       |

|                | L      | L      | L     | Ol   | Code        | Mode Register Set    | ILLEGAL                                  |       |

|                | L      | L      | Н     | Х    | Х           | Auto or Self Refresh | ILLEGAL                                  |       |

|                | L      | Н      | L     | Х    | Х           | Precharge            | Terminate Burst; Start the Precharge     |       |

| 5 .            | L      | Н      | Н     | BA   | Row Address | Bank Activate        | ILLEGAL                                  | 2     |

| Read           | Н      | L      | L     | BA   | Column      | Write                | Terminate Burst; Start the Write cycle   | 5,6   |

|                | Н      | L      | Н     | BA   | Column      | Read                 | Terminate Burst; Start a new Read cycle  | 5,6   |

|                | Н      | Н      | L     | Х    | Х           | Burst Termination    | Terminate the Burst                      |       |

|                | Н      | Н      | Н     | Х    | Х           | No Operation         | Continue the Burst                       |       |

|                | L      | L      | L     | Ol   | Code        | Mode Register Set    | ILLEGAL                                  |       |

|                | L      | L      | Н     | Х    | Х           | Auto or Self Refresh | ILLEGAL                                  |       |

|                | L      | Н      | L     | Х    | Х           | Precharge            | Terminate Burst; Start the Precharge     |       |

| 14/1           | L      | Н      | Н     | BA   | Row Address | Bank Activate        | ILLEGAL                                  | 2     |

| Write          | Н      | L      | L     | BA   | Column      | Write                | Terminate Burst; Start a new Write cycle | 5,6   |

|                | Н      | L      | Н     | BA   | Column      | Read                 | Terminate Burst; Start the Read cycle    | 5,6   |

|                | Н      | Н      | L     | Х    | Х           | Burst Termination    | Terminate the Burst                      |       |

|                | Н      | Н      | Н     | Х    | Х           | No Operation         | Continue the Burst                       |       |

|                | L      | L      | L     | Ol   | Code        | Mode Register Set    | ILLEGAL                                  |       |

|                | L      | L      | Н     | Х    | Х           | Auto or Self Refresh | ILLEGAL                                  |       |

|                | L      | Н      | L     | Х    | Х           | Precharge            | ILLEGAL                                  | 2     |

| Read with      | L      | Н      | Н     | BA   | Row Address | Bank Activate        | ILLEGAL                                  | 2     |

| Auto Precharge | Н      | L      | L     | BA   | Column      | Write                | ILLEGAL                                  | 1     |

|                | Н      | L      | Н     | BA   | Column      | Read                 | ILLEGAL                                  |       |

|                | Н      | Н      | L     | Х    | Х           | Burst Termination    | ILLEGAL                                  |       |

|                | Н      | Н      | Н     | Х    | Х           | No Operation         | Continue the Burst                       |       |

## **SDRAM CURRENT STATE TRUTH TABLE** (continued)

| Current State    | VCRAS# | VCCAS# | VCWE# | VCBS | VCADDR            | Description          | Action                                           | Notes |

|------------------|--------|--------|-------|------|-------------------|----------------------|--------------------------------------------------|-------|

|                  | L      | L      | L     | 0    | P Code            | Mode Register Set    | ILLEGAL                                          |       |

|                  | L      | L      | Н     | Х    | Χ                 | Auto or Self Refresh | ILLEGAL                                          |       |

|                  | L      | Н      | L     | Х    | X Precharge ILLEG |                      | ILLEGAL                                          | 2     |

| Write with       | L      | Н      | Н     | BA   | Row Address       | Bank Activate        | ILLEGAL                                          | 2     |

| Auto Precharge   | Н      | L      | L     | BA   | Column            | Write                | ILLEGAL                                          |       |

|                  | Н      | L      | Н     | BA   | Column            | Read                 | ILLEGAL                                          |       |

|                  | Н      | Н      | L     | Х    | Х                 | Burst Termination    | ILLEGAL                                          |       |

|                  | Н      | Н      | Н     | Х    | Х                 | No Operation         | Continue the Burst                               |       |

|                  | L      | L      | L     | 0    | P Code            | Mode Register Set    | ILLEGAL                                          |       |

|                  | L      | L      | Н     | Х    | Х                 | Auto or Self Refresh | ILLEGAL                                          |       |

|                  | L      | Н      | L     | Х    | Х                 | Precharge            | No Operation; Bank(s) idle after trp             |       |

| Donale and       | L      | Н      | Н     | BA   | Row Address       | Bank Activate        | ILLEGAL                                          | 2     |

| Precharging      | Н      | L      | L     | BA   | Column            | Write w/o Precharge  | ILLEGAL                                          | 2     |

|                  | Н      | L      | Н     | BA   | Column            | Read w/o Precharge   | ILLEGAL                                          | 20    |

|                  | Н      | Н      | L     | Х    | Х                 | Burst Termination    | No Operation; Bank(s) idle after t <sub>RP</sub> |       |

|                  | Н      | Н      | Н     | Х    | Х                 | No Operation         | No Operation; Bank(s) idle after t <sub>RP</sub> |       |

|                  | L      | L      | L     | 0    | P Code            | Mode Register Set    | ILLEGAL                                          |       |

|                  | L      | L      | Н     | Х    | Χ                 | Auto or Self Refresh | ILLEGAL                                          |       |

|                  | L      | Н      | L     | Х    | Х                 | Precharge            | ILLEGAL                                          | 2     |

|                  | L      | Н      | Н     | BA   | Row Address       | Bank Activate        | ILLEGAL                                          | 2     |

| Row Activating   | Н      | L      | L     | BA   | Column            | Write                | ILLEGAL                                          | 2     |

|                  | Н      | L      | Н     | BA   | Column            | Read                 | ILLEGAL                                          | 2     |

|                  | Н      | Н      | L     | Х    | Х                 | Burst Termination    | No Operation; Row active after t <sub>RCD</sub>  |       |

|                  | Н      | Н      | Н     | Х    | Х                 | No Operation         | No Operation; Row active after t <sub>RCD</sub>  |       |

|                  | L      | L      | L     | 0    | P Code            | Mode Register Set    | ILLEGAL                                          |       |

|                  | L      | L      | Н     | Х    | Χ                 | Auto orSelf Refresh  | ILLEGAL                                          |       |

|                  | L      | Н      | L     | Х    | Х                 | Precharge            | ILLEGAL                                          | 2     |

|                  | L      | Н      | Н     | BA   | Row Address       | Bank Activate        | ILLEGAL                                          | 2     |

| Write Recovering | Н      | L      | L     | BA   | Column            | Write                | Start Write; Determine if Auto Precharge         | 6     |

|                  | Н      | L      | Н     | BA   | Column            | Read                 | Start Read, Determine if Auto Precharge          | 6     |

|                  | Н      | Н      | L     | Х    | Х                 | Burst Termination    | No Operation; Row active after topl              |       |

|                  | Н      | Н      | Н     | Х    | Х                 | No Operation         | No Operation; Row active after topl              |       |

|                  | L      | L      | L     | 0    | P Code            | Mode Register Set    | ILLEGAL                                          |       |

|                  | L      | L      | Н     | Х    | Χ                 | Auto orSelf Refresh  | ILLEGAL                                          |       |

|                  | L      | Н      | L     | X    | X                 | Precharge            | ILLEGAL                                          | 2     |

| Write Recovering | L      | Н      | Н     | BA   | Row Address       | Bank Activate        | ILLEGAL                                          | 2     |

| with Auto        | Н      | L      | L     | BA   | Column            | Write                | ILLEGAL                                          | 2,6   |

| Precharge        | Н      | L      | H     | BA   | Column            | Read                 | ILLEGAL                                          | 2.6   |

|                  | Н      | Н      | L     | X    | X                 | Burst Termination    | No Operation; Precharge after t <sub>DPL</sub>   | _,-   |

|                  | Н      | Н      | Н     | X    | X                 | No Operation         | No Operation; Precharge after t <sub>DPL</sub>   |       |

## SDRAM CURRENT STATE TRUTH TABLE (continued)

| 0             |   |   |                    | Comma   | Autom       | Notes                |                                           |  |

|---------------|---|---|--------------------|---------|-------------|----------------------|-------------------------------------------|--|

| Current State |   |   | VCADDR Description |         | Action      | Notes                |                                           |  |

|               | L | L | L                  | OP Code |             | Mode Register Set    | ILLEGAL                                   |  |

|               | L | L | Н                  | X X A   |             | Auto or Self Refresh | ILLEGAL                                   |  |

|               | L | Н | L                  | Х       | Х           | Precharge            | ILLEGAL                                   |  |

| Dofrachina    | L | Н | Н                  | BA      | Row Address | Bank Activate        | ILLEGAL                                   |  |

| Refreshing    | Н | L | L                  | BA      | Column      | Write                | ILLEGAL                                   |  |

|               | Н | L | Н                  | BA      | Column      | Read                 | ILLEGAL                                   |  |

|               | Н | Н | L                  | Х       | Х           | Burst Termination    | No Operation; Idle after t <sub>RC</sub>  |  |

|               | Н | Н | Н                  | Х       | X           | No Operation         | No Operation; Idle after tRc              |  |

|               | L | L | L                  | OP Code |             | Mode Register Set    | ILLEGAL                                   |  |

|               | L | L | Н                  | X       | X           | Auto or Self Refresh | ILLEGAL                                   |  |

|               | L | Н | L                  | Х       | X           | Precharge            | ILLEGAL                                   |  |

| Mode Register | L | Н | Н                  | BA      | Row Address | Bank Activate        | ILLEGAL                                   |  |

| Accessing     | Н | L | L                  | BA      | Column      | Write                | ILLEGAL                                   |  |

|               | Н | L | Н                  | BA      | Column      | Read                 | ILLEGAL                                   |  |

|               | Н | Н | L                  | Х       | Х           | Burst Termination    | ILLEGAL                                   |  |

|               | Н | Н | Н                  | Х       | Х           | No Operation         | No Operation; Idle after two clock cycles |  |

- 1. Both Banks must be idle otherwise it is an illegal action.

- 2. The Current State refers only refers to one of the banks, if VCBS selects this bank then the action is illegal. If VCBS selects the bank not being referenced by the Current State then the action may be legal depending on the state of that bank.

- 3. The minimum and maximum Active time (tras) must be satisfied.

- 4. The VCRAS# to VCCAS# Delay (tRCD) must occur before the command is given.

- Address VCADDR9/AP is used to determine if the Auto Precharge function is activated.

- 6. The command must satisfy any bus contention, bus turn around, and/or write recovery requirements. The command is illegal if the minimum bank-to-bank delay time (trrb) is not satisfied.

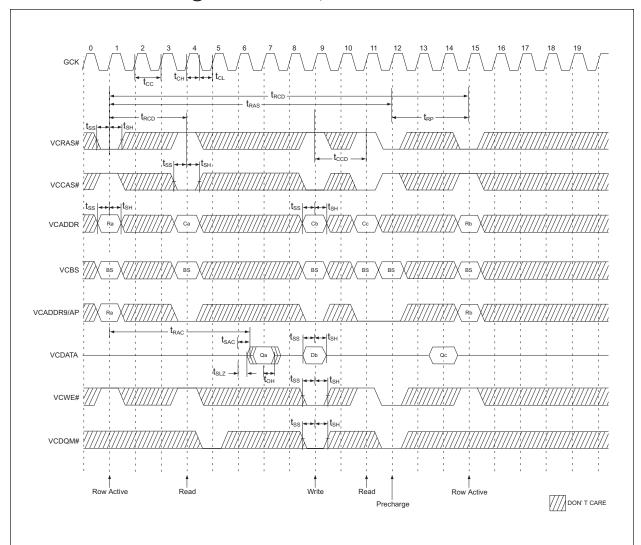

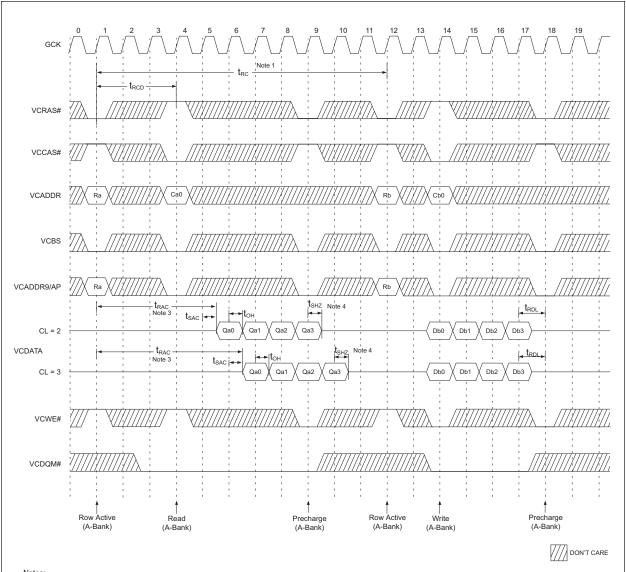

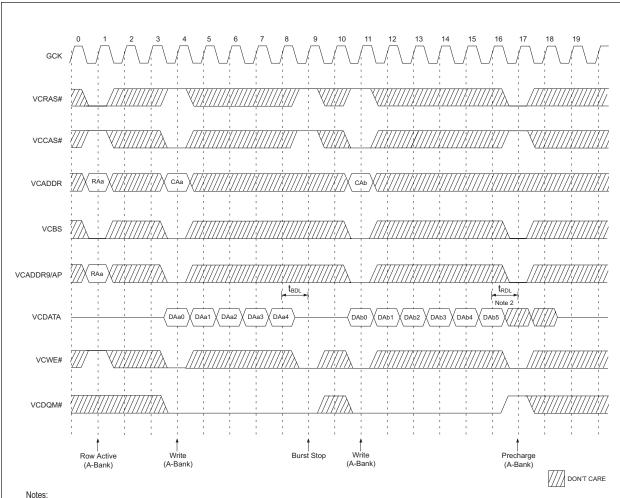

## FIGURE 4 – SDRAM SINGLE BIT READ-WRITE-READ CYCLE (SAME PAGE) @CAS LATENCY = 3, BURST LENGTH = 1

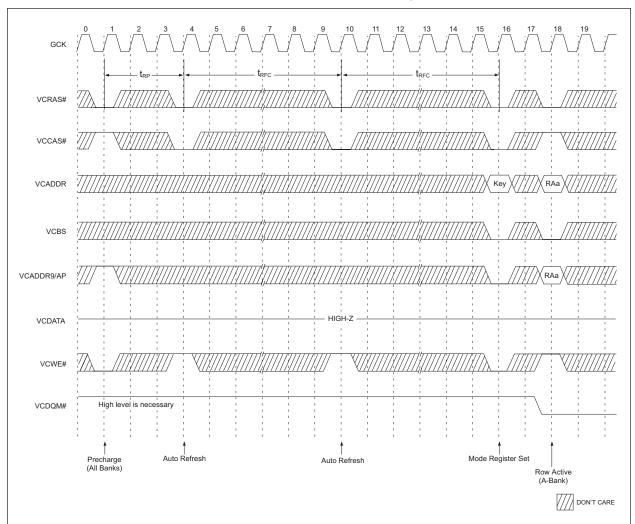

### FIGURE 5 – SDRAM POWER UP SEQUENCE

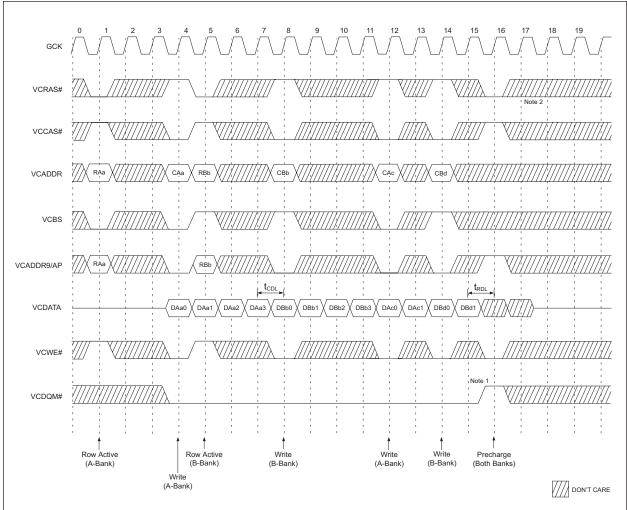

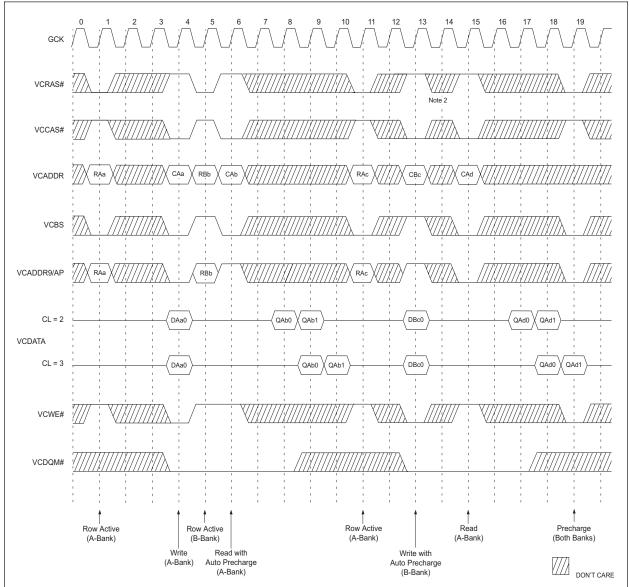

## FIGURE 6 - SDRAM READ & WRITE CYCLE AT SAME BANK @ BURST LENGTH = 4

- 1. Minimum row cycle times are required to complete internal DRAM operation.

- 2. Row precharge can interrupt burst on any cycle. (CAS Latency 1) number of valid output data is available after Row precharge. Last valid output will be Hi-Z (tsHz) after the clock.

- 3. Access time from Row active command. tcc \*(tRCD + CAS Latency 1) + tsAc.

- 4. Output will be Hi-Z after the end of burst. (1, 2, 4, 8 & Full page bit burst)

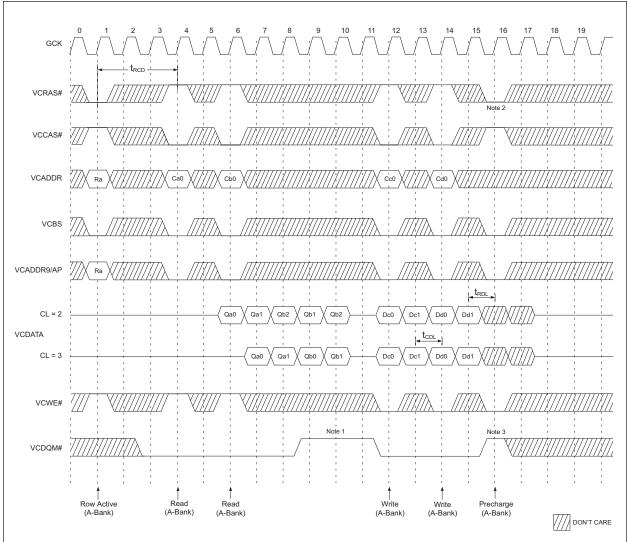

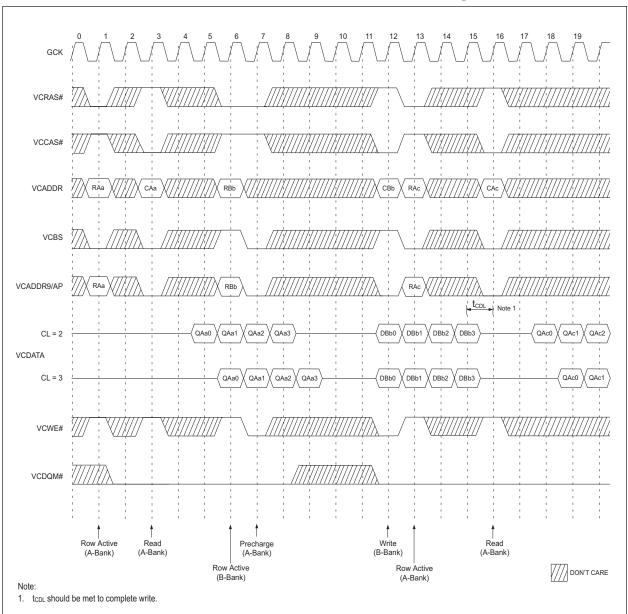

## FIGURE 7 – SDRAM PAGE READ & WRITE CYCLE AT SAME BANK @ BURST LENGTH = 4

- 1. To write data before burst read ends. VCDQM# should be asserted three cycle prior to write command to avoid bus contention.

- 2. Row precharge will interrupt writing. Last data input, tRDL before Row precharge will be written.

- 3. VCDQM# should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input data after Row precharge cycle will be masked internally.

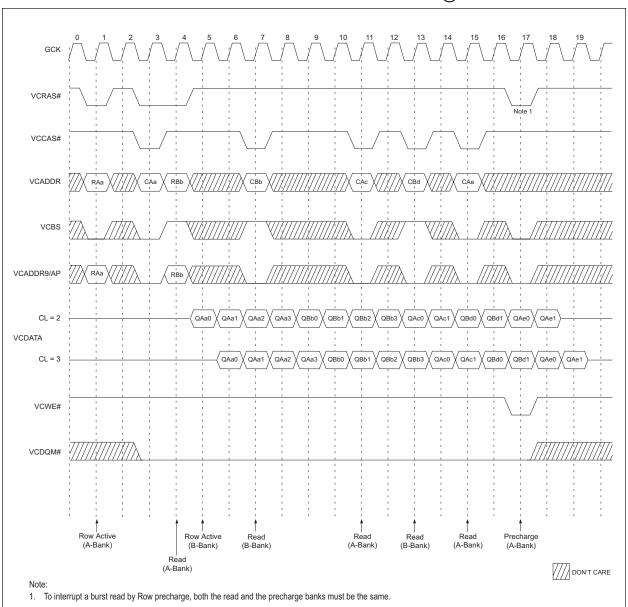

## FIGURE 8 – SDRAM PAGE READ CYCLE AT DIFFERENT BANK @ BURST LENGTH = 4

## FIGURE 9 – SDRAM PAGE WRITE CYCLE AT DIFFERENT BANK @ BURST LENGTH = 4

### NOTES:

- 1. To interrupt burst write by Row precharge, VCDQM# should be asserted to mask invalid input data.

- 2. To interrupt a burst read by Row precharge, both the read and the precharge banks must be the same.

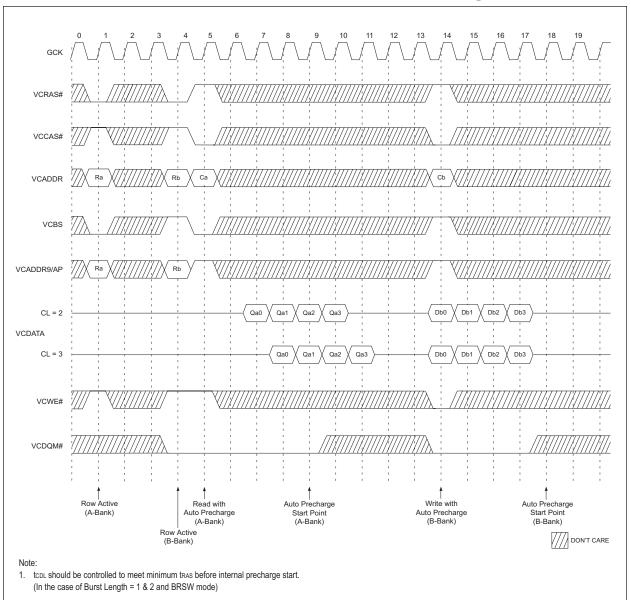

## FIGURE 10 – SDRAM READ & WRITE CYCLE AT DIFFERENT BANK @ BURST LENGTH = 4

## FIGURE 11 – SDRAM READ & WRITE CYCLE WITH AUTO PRECHARGE @BURST LENGTH = 4

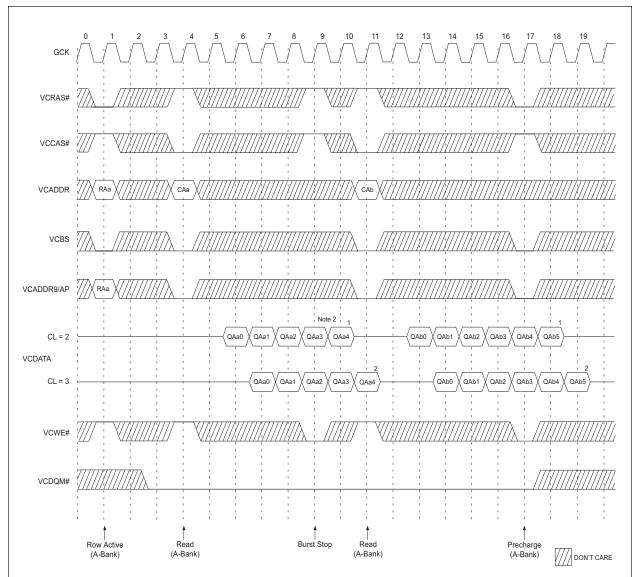

## FIGURE 12 – SDRAM READ INTERRUPTED BY PRECHARGE COMMAND & READ BURST STOP @ BURST LENGTH = FULL PAGE

- 1. At full page mode, burst is end at the end of burst. So auto precharge is possible.

- About the valid VCDATAs after burst stop, it is the same as the case of VCRAS# interrupt. Both cases are illustrated in the above timing diagram. See the label 1, 2 on each of them. But at burst write, burst stop and VCRAS# interrupt should be compared carefully. Refer to the timing diagram of "Full page write burst stop cycle."

- Burst stop is valid at every burst length.

## FIGURE 13 – SDRAM WRITE INTERRUPTED BY PRECHARGE COMMAND & WRITE BURST STOP @ BURST LENGTH = FULL PAGE

- 1. At full page mode, burst is end at the end of burst. So auto precharge is possible.

- 2. Data-in at the cycle of interrupted by precharge can not be written into the corresponding memory cell. It is defined by AC parameter of tRDL. VCDQM# at write interrupt by precharge command is needed to prevent invalid write.

- VCDQM# should mask invalid input data on precharge command cycle when asserting precharge before end of burst. Input data after Row precharge cycle will be masked internally.

- 3. Burst stop is valid at every burst length.

## FIGURE 14 – SDRAM BURST READ SINGLE BIT WRITE CYCLE @ BURST LENGTH = 2

- 1. BRSW modes enabled by setting VCADDR8 "High" at MRS (Mode Register Set). At the BRSW Mode, the burst length at Write is fixed to "1" regardless of programmed burst length.

- When BRSW write command with auto precharge is executed, keep it in mind that tras should not be violated. Auto precharge is executed at the burst-end cycle, so in the case of BRSW write command, the next cycle starts the precharge.

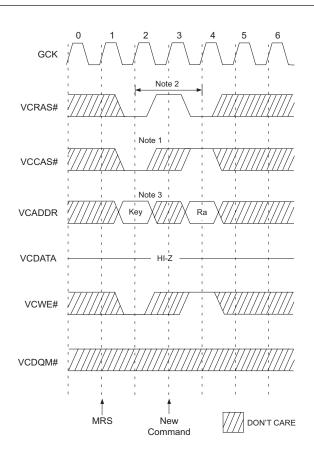

### FIGURE 15 – SDRAM MODE REGISTER SET CYCLE

\*Both banks precharge should be completed before Mode Register Set cycle.

### NOTES:

MODE REGISTER SET CYCLE

- 1. VCRAS#, VCCAS# & VCWE# activation at the same clock cycle with address key will set internal mode register.

- 2. Minimum 2 clock cycles should be met before new VCRAS# activation.

- 3. Please refer to Mode Register Set table.

## MODE REGISTER FIELD TABLE TO PROGRAM MODES

REGISTER PROGRAMMED WITH MRS

|   | Address  | VCBS | VCADDR9/AP | VCADDR8 | VCADDR10  | VCADDR7 | VCADDR6     | VCADDR5 | VCADDR4 | VCADDR3 | VCADDR2 | VCADDR1      | VCADDR0 |

|---|----------|------|------------|---------|-----------|---------|-------------|---------|---------|---------|---------|--------------|---------|

| Γ | Function | RFU  | RFU RFU    |         | W.B.L. TM |         | CAS Latency |         |         | BT      |         | Burst Length |         |

|          | Test N             | lode              |         | CAS L   | atency  |          | Burs    | st Type    | Burst Length |         |         |           |          |

|----------|--------------------|-------------------|---------|---------|---------|----------|---------|------------|--------------|---------|---------|-----------|----------|

| VCADDR10 | VCADDR7            | Туре              | VCADDR6 | VCADDR5 | VCADDR4 | Latency  | VCADDR3 | Type       | VCADDR2      | VCADDR1 | VCADDR0 | BT = 0    | BT = 1   |

| 0        | 0                  | Mode Register Set | 0       | 0       | 0       | Reserved | 0       | Sequential | 0            | 0       | 0       | 1         | 1        |

| 0        | 1                  | Reserved          | 0       | 0       | 1       | Reserved | 1       | Interleave | 0            | 0       | 1       | 2         | 2        |

| 1        | 0                  | Reserved          | 0       | 1       | 0       | 2        |         |            | 0            | 1       | 0       | 4         | 4        |

| 1        | 1                  | Reserved          | 0       | 1       | 1       | 3        |         |            | 0            | 1       | 1       | 8         | 8        |

|          | Write Burst Length |                   | 1       | 0       | 0       | Reserved |         |            | 1            | 0       | 0       | Reserved  | Reserved |

| VCAE     | VCADDR9 Length     |                   | 1       | 0       | 1       | Reserved |         |            | 1            | 0       | 1       | Reserved  | Reserved |

| 0 Burst  |                    | Burst             | 1       | 1       | 0       | Reserved |         |            | 1            | 1       | 0       | Reserved  | Reserved |

| 1        | 1                  | Single Bit        | 1       | 1       | 1       | Reserved |         |            | 1            | 1       | 1       | Full Page | Reserved |

Full Page Length: x32 (256)

### **POWER UP SEQUENCE**

SDRAMs must be powered up and initialized in a predefined manner to prevent undefined operations.

- Apply power and start clock. Must maintain CKE= "H" ,DQM = "H" and the other pins are NOP condition at the inputs.

- Maintain stable power, stable clock and NOP input condition for a minimum of 200µs.

- Issue precharge commandes for all banks of the devices.

- 4. Issue 2 or more auto-refresh commands.

- 5. Issue a mode register set command to initialize the mode register.

- cf.) Sequence of 4 & 5 is regardless of the order.

The device is now ready for normal operation.

- If VCADDR8 is high during MRS cycle, "Burst Read Single Bit Write" function will be enabled.

- 2. RFU (Reserved for future use) shuld stay "0" during MRS cycle.

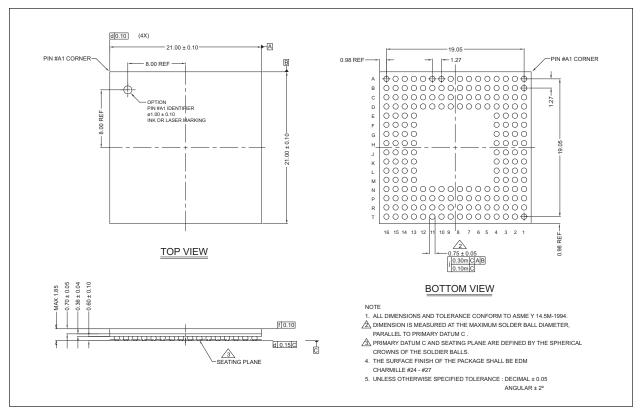

### PACKAGE DESCRIPTION: 192 LEAD BGA 21MM X 21MM

## ORDERING INFORMATION

| WED9LAPC3C16V8BC | Commercial Temperature: | 0°C to +70°C   |

|------------------|-------------------------|----------------|

| WED9LAPC3C16V8BI | Industrial Temperature: | -40°C to +85°C |