## Buck-Boost Converter to Drive a Single LED from 1 Li-Ion or 3 Alkaline Batteries

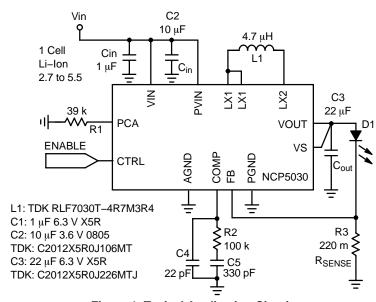

The NCP5030 is a fixed frequency PWM buck–boost converter optimized for constant current applications such as driving high–powered white LED. The buck–boost is implemented in an H–bridge topology and has an adaptive architecture where it operates in one of three modes: boost, buck–boost, or buck depending on the input and output voltage condition. This device has been designed with high–efficiency for use in portable applications and is capable of driving in DC up to 900 mA into a high power LED for flashlight / torch applications. To protect the device cycle–by–cycle current limiting and a thermal shutdown circuit have been incorporated as well as output over–voltage protection. The 700 kHz switching frequency allows the use of a low value 4.7  $\mu$ H and ceramic capacitors. The NCP5030 is housed in a low profile space efficient 3x4 mm thermally enhanced WDFN.

#### **Features**

- Efficiency: 87% at 500 mA and 3.3 V V<sub>IN</sub>

- Internal Synchronous Rectifier, No Schottky Diodes

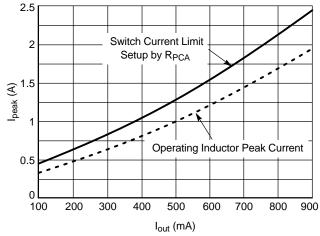

- Adjustable Switching Limit Current to Optimize inductor size

- 0.3 µA Shut-down Control with "True-Cut off"

- Input Voltage Range from 2.7 V to 5.5 V

- 200 mV Feedback Voltage

- Output Over-voltage and Thermal Shut Down Protection

#### **Typical Applications**

• Portable Flashlight / Torch Lights

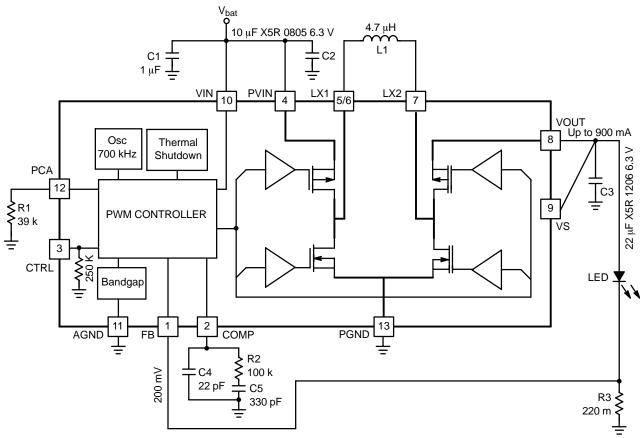

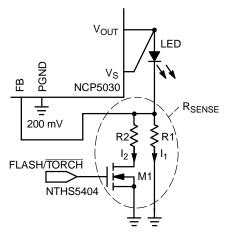

**Figure 1. Typical Application Circuit**

#### ON Semiconductor®

http://onsemi.com

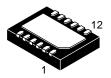

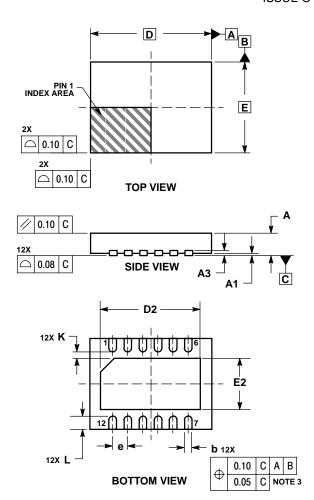

## MARKING DIAGRAM

WDFN12 3x4 MT SUFFIX CASE 506AY

5030 = Specific Device Code A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

(Note: Microdot may be in either location)

= Pb-Free Package

#### **PIN CONNECTIONS**

Exposed pad (Pin 13) is PGND must be soldered to PCB GND plane

#### ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 13 of this data sheet.

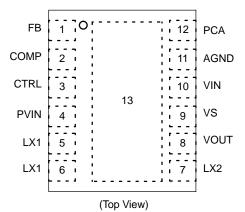

Figure 2. Efficiency vs. V<sub>in</sub> Voltage

Figure 3. Simplified Block Diagram

## PIN FUNCTION DESCRIPTION

| Pin | Name | Туре  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | FB   | INPUT | <b>Feedback:</b> Reference voltage is 200 mV. The cathode of the LED and a resistor to ground to set the LED current should be connected at this point. A $\pm 5\%$ metal film resistor, or better, is recommended for best output accuracy. An analog signal can be applied to this input to dim the LED.                                                                                                                                                                   |

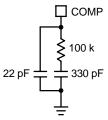

| 2   | COMP | INPUT | <b>Loop Compensation:</b> A frequency compensation network must be connected between this pin to the ground to ensure the stability of the closed loop. See "loop compensation" guidelines.                                                                                                                                                                                                                                                                                  |

| 3   | CTRL | INPUT | Control and Enable: An active High logic level on this pin enables the device. A built–in pulldown resistor disables the device if the input is left open. This pin can also be used to control the average current into the load by applying a low frequency PWM signal. If a PWM signal is applied, the frequency should be high enough to avoid optical flicker, but be no greater than 1.0 kHz.                                                                          |

| 4   | PVIN | POWER | Power Voltage Input Supply: A 10 $\mu$ F ceramic capacitor or larger must bypass this input to the ground. This capacitor should be placed as close a possible to this input.                                                                                                                                                                                                                                                                                                |

| 5/6 | LX1  | POWER | <b>Switch LX1:</b> Both pins are connected to the input node of the H–bridge. The inductor should be connected between this node and LX2. The recommended inductor size is $4.7~\mu$ H.                                                                                                                                                                                                                                                                                      |

| 7   | LX2  | POWER | <b>Switch LX2:</b> This pin is connected to the opposite node of the H–bridge and the power inductor is connected between this node and LX1.                                                                                                                                                                                                                                                                                                                                 |

| 8   | VOUT | POWER | <b>Power Output:</b> A filter capacitor is necessary on this pin for the stability of the loop, to smooth the current flowing into the load, and to limit the noise created by the fast transients present in this circuitry. A 22 $\mu$ F ceramic capacitor bypass to GND or larger is recommended. For White LED applications, this pin is also connected to the anode of the LED. Care must be observed to avoid EMI through the PCB copper tracks connected to this pin. |

| 9   | VS   | POWER | <b>Voltage Sense:</b> This pin must be connected to $C_{OUT}$ with a dedicated track to minimize serial parasitic inductor and to sense $V_{OUT}$ with high accuracy. This pin supplies some of the NCP5030 internal blocks when the voltage is higher than $V_{IN}$ .                                                                                                                                                                                                       |

| 10  | VIN  | POWER | Supply Pin: This pin supplies the internal control circuitry and must be connected to PVIN. Recommended bypass capacitor is 1.0 $\mu$ F ceramic or larger.                                                                                                                                                                                                                                                                                                                   |

| 11  | AGND | POWER | <b>Analog Ground:</b> This pin is the system ground and carries the analog signals. This pin must be connected to the ground plan like PGND.                                                                                                                                                                                                                                                                                                                                 |

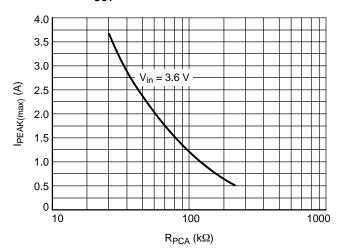

| 12  | PCA  | INPUT | Peak Current Adjust: A resistor between this input and ground controls the maximum peak current allowed in the inductor. The minimum value for this resistor is 30 k $\Omega$ . Increasing this value decreases the peak current. This allows the user to adjust the current based on the application needs and scale the size of the inductor accordingly. See "Switch Current Limit" guidelines in application section.                                                    |

| 13  | PGND | POWER | <b>Power Ground:</b> This pin is the power ground for NCP5030 and carries the switching current. Care must be observed to avoid high-density current flow in a limited PCB copper track.                                                                                                                                                                                                                                                                                     |

## MAXIMUM RATINGS (Note 1)

| Rating                                                                                                                                        | Symbol                                                   | Value                                  | Unit              |

|-----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------|-------------------|

| Power Supply Voltage (Note 2)                                                                                                                 | V <sub>bat</sub>                                         | 7.0                                    | V                 |

| Over Voltage Protection                                                                                                                       | V <sub>out</sub>                                         | 6.5                                    | V                 |

| Human Body Model (HBM) ESD Rating (Note 3)                                                                                                    | ESD HBM                                                  | 2.0                                    | kV                |

| Machine Model (MM) ESD Rating (Note 3)                                                                                                        | ESD MM                                                   | 200                                    | V                 |

| Digital Input Voltage<br>Digital Input Current                                                                                                | CTRL                                                     | $-0.3 < V_{in} < V_{bat} + 0.3$<br>1.0 | V<br>mA           |

| WDFN 3x4 Package Power Dissipation @ T <sub>A</sub> = +85°C (Note 5) Thermal Resistance, Junction-to-Case Thermal Resistance, Junction-to-Air | P <sub>D</sub><br>R <sub>θ</sub> JC<br>R <sub>θ</sub> JA | Internally Limited<br>6.0<br>(Note 6)  | W<br>°C/W<br>°C/W |

| Operating Ambient Temperature Range                                                                                                           | T <sub>A</sub>                                           | -40 to +85                             | °C                |

| Operating Junction Temperature Range                                                                                                          | T <sub>J</sub>                                           | -40 to +125                            | °C                |

| Maximum Junction Temperature                                                                                                                  | T <sub>JMAX</sub>                                        | +150                                   | °C                |

| Storage Temperature Range                                                                                                                     | T <sub>stg</sub>                                         | -65 to +150                            | °C                |

| Moisture Sensitivy Level (Note 7)                                                                                                             | MSL                                                      | 1                                      |                   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

- 1. Maximum electrical ratings are defined as those values beyond which damage to the device may occur at T<sub>A</sub> = 25°C.

- 2. According to JEDEC standard JESD22-A108B.

- 3. This device series contains ESD protection and passes the following tests:

Human Body Model (HBM) ± 2.0 kV per JEDEC standard: JESD22–A114 for all pins

Machine Model (MM) ± 200 V per JEDEC standard: JESD22–A115 for all pins

- 4. Latchup Current Maximum Rating: ±100 mA per JEDEC standard: JESD78.

- 5. The thermal shutdown set to 160°C (typical) avoids irreversible damage on the device due to power dissipation.

- For the 12-Pin 3x4 WDFN Package, the R<sub>θJA</sub> is highly dependent on the PCB heat-sink area. For example, R<sub>θJA</sub> can be 57°C/W for a one layer board and 43 for a four layer board.

- 7. Per IPC/JEDEC standard: J-STD-020A.

## **ELECTRICAL CHARACTERISTICS** (Limits apply for $T_A$ between $-40^{\circ}$ C to $+85^{\circ}$ C and $V_{in} = 3.6$ V unless otherwise noted.)

| Maximum Inductor Current (Note 11) (See Figure 8) $I_{PEAK,MAX}$ $-20\%$ $4.0$ $+20\%$ A           Switches P1 and P2 ON Resistance $P_{MOS} R_{DSON}$ $ 100$ $ m\Omega$ Switches N1 and N2 ON Resistance $N_{MOS} R_{DSON}$ $ 100$ $ m\Omega$ Switches P1 and P2 Leakage Current $P_{MOS} L$ $ 0.5$ $ \mu$ Switches N1 and N2 Leakage Current $N_{MOS} L$ $ 0.5$ $ \mu$ Switches N1 and N2 Leakage Current $N_{MOS} L$ $ 0.5$ $ \mu$ Switches N1 and N2 Leakage Current $N_{MOS} L$ $ 0.5$ $ \mu$ Internal Oscillator Frequency (Note 8) $E_{ER}$ $ 0.5$ $ \mu$ Internal Oscillator Frequency (Note 8) $E_{ER}$ $ 0.5$ $ \mu$ Uput Voltage Threshold to Change Mode from Boost to Buck $E_{EF}$ $ 0.5$ $ m$ Vin-Vout Threshold to Change Mode from Buck-Boost to Buck $E_{BUL}$ $-$ <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Characteristic                                                                                              | Symbol                             | Min  | Тур  | Max  | Unit |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|------------------------------------|------|------|------|------|

| Switches P1 and P2 ON Resistance $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Operational Power Supply                                                                                    | V <sub>IN</sub>                    | 2.7  | -    | 5.5  | V    |

| Switches N1 and N2 ON Resistance   Nos Roson   -   100   -   mΩ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Maximum Inductor Current (Note 11) (See Figure 8)                                                           | I <sub>PEAK_MAX</sub>              | -20% | 4.0  | +20% | Α    |

| Switches P1 and P2 Leakage Current   P <sub>MOS</sub> L   -   0.5   -   μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Switches P1 and P2 ON Resistance                                                                            | P <sub>MOS</sub> R <sub>DSON</sub> | 1    | 100  | -    | mΩ   |

| Switches N1 and N2 Leakage Current $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Switches N1 and N2 ON Resistance                                                                            | N <sub>MOS</sub> R <sub>DSON</sub> | 1    | 100  | -    | mΩ   |

| Internal Oscillator Frequency (Note 8) Fosc 600 700 800 MHz Efficiency (Notes 9, 10 and 11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Switches P1 and P2 Leakage Current                                                                          | P <sub>MOS</sub> L                 | 1    | 0.5  | -    | μΑ   |

| Efficiency (Notes 9, 10 and 11)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Switches N1 and N2 Leakage Current                                                                          | N <sub>MOS</sub> L                 | -    | 0.5  | -    | μΑ   |

| Output Voltage Range (Note 11) $V_{OUT}-V_{IN} \text{ Threshold to Change Mode from Boost to Buck-Boost} \qquad V_{OUT}-V_{IN} \text{ Threshold to Change Mode from Buck-Boost} \qquad T_{BOOST} \qquad - 375 \qquad - mV$ $V_{IN}-V_{OUT} \text{ Threshold to Change Mode from Buck-Boost to Buck} \qquad T_{BUCK} \qquad - 650 \qquad - mV$ $V_{IN}-V_{OUT} \text{ Threshold to Change Mode Hysteresis} \qquad H_{MODE} \qquad - 100 \qquad - mV$ $Available Output Power (Note 11) \qquad P_{OUT} \qquad 4.3 \qquad - \qquad - mV$ $Available Output Power (Note 11) \qquad When V_{In} \geq 3.1 \text{ V } (V_{Out} = 4.7 \text{ V, } 900 \text{ mA}) \qquad 4.3 \qquad - \qquad - mV$ $Feedback Voltage Threshold in Steady State at 25°C \qquad F_{BV} \qquad 190 \qquad 200 \qquad 210 \qquad mV$ $Line Regulation, Measured on FB Pin (Note 8) \qquad F_{BVLR} \qquad - 5.0 \qquad - mV/V$ $From DC to 100 Hz and R_{FB} = 1 \Omega$ $Feedback Input Current \qquad F_{BC} \qquad - \qquad - 0.1 \qquad \mu A$ $Standby Current at I_{OUT} = 0 \text{ mA, CTRL} = Low, V_{bat} = 4.2 \text{ V} \qquad I_{STB} \qquad - \qquad 0.3 \qquad 3.0 \qquad \mu A$ $Quiescent Current Switching at I_{OUT} = 0 \text{ mA, CTRL} = High, V_{bat} = 4.2 \text{ V} \qquad I_{QS} \qquad - \qquad 5.0 \qquad - \qquad mA$ $(Note 12) \qquad U_{VLO} \qquad U_{VLO} \qquad 2.2 \qquad 2.4 \qquad 2.6 \qquad V$ $Undervoltage Lockout Hysteresis \qquad U_{VLOH} \qquad - \qquad 100 \qquad - \qquad mV$ $Soft-start Time (Note 11) \qquad S_{ST} \qquad - \qquad 1000 \qquad - \qquad \mu_S$ $Limit of CTRL pin PWM Dimming Frequency (Note 11) \qquad F_{DIM} \qquad - \qquad 0.2 \qquad - \qquad kHz$ $Thermal Shutdown Protection \qquad T_{SD} \qquad - \qquad 160 \qquad - \qquad ^{\circ}C$ $Thermal Shutdown Protection Hysteresis \qquad T_{SDH} \qquad - \qquad 20 \qquad - \qquad ^{\circ}C$ $Voltage Input Logic Low \qquad V_{IL} \qquad - \qquad - \qquad V$                                                                                                                                                                                                                                                                   | Internal Oscillator Frequency (Note 8)                                                                      | Fosc                               | 600  | 700  | 800  | MHz  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Efficiency (Notes 9, 10 and 11)                                                                             | E <sub>FF</sub>                    | -    | 85   | -    | %    |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Output Voltage Range (Note 11)                                                                              | V <sub>OUT</sub>                   | 2.2  | -    | 5.5  | V    |

| Threshold to Change Mode Hysteresis $H_{MODE} = - 100 - mV$ Available Output Power (Note 11) $When V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.7 \ V, 900 \ mA)$ $V_{in} \ge 3.1 \ V \ (V_{out} = 4.2 \ V)$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V_{in} = 4.2 \ V$ $V_{in} \ge 3.1 \ V_{in} = 4.2 \ V_{in} $ | V <sub>OUT</sub> -V <sub>IN</sub> Threshold to Change Mode from Boost to Buck-Boost                         | T <sub>BOOST</sub>                 | -    | 375  | -    | mV   |

| Available Output Power (Note 11) $ \text{When } V_{\text{in}} \geq 3.1 \text{ V (Vout} = 4.7 \text{ V}, 900 \text{ mA}) $ $ P_{\text{OUT}}                                   $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | V <sub>IN</sub> -V <sub>OUT</sub> Threshold to Change Mode from Buck-Boost to Buck                          | T <sub>BUCK</sub>                  | -    | 650  | -    | mV   |

| When $V_{in} \ge 3.1 \text{ V}$ ( $V_{out} = 4.7 \text{ V}$ , 900 mA)       4.3       -       -         Feedback Voltage Threshold in Steady State at 25°C       F <sub>BV</sub> 190       200       210       mV         Line Regulation, Measured on FB Pin (Note 8) From DC to 100 Hz and R <sub>FB</sub> = 1 Ω       F <sub>BVLR</sub> -       5.0       -       mV/V         Feedback Input Current       F <sub>BC</sub> -       -       0.1       μA         Standby Current at I <sub>OUT</sub> = 0 mA, CTRL = Low, V <sub>bat</sub> = 4.2 V       I <sub>STB</sub> -       0.3       3.0       μA         Quiescent Current Switching at I <sub>OUT</sub> = 0 mA, CTRL = High, V <sub>bat</sub> = 4.2 V       I <sub>QS</sub> -       5.0       -       mA         V <sub>IN</sub> Undervoltage Lockout Threshold to Enable the Converter       U <sub>VLO</sub> U <sub>VLO</sub> 2.2       2.4       2.6       V         Undervoltage Lockout Hysteresis       U <sub>VLO</sub> H       -       100       -       mV         Soft—start Time (Note 11)       S <sub>ST</sub> -       1000       -       μs         Limit of CTRL pin PWM Dimming Frequency (Note 11)       F <sub>DIM</sub> -       0.2       -       kHz         Thermal Shutdown Protection       T <sub>SD</sub> -       160       -       °C         Voltage Input Logic High       V <sub>IL</sub> -       -<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Threshold to Change Mode Hysteresis                                                                         | H <sub>MODE</sub>                  | -    | 100  | -    | mV   |

| Line Regulation, Measured on FB Pin (Note 8)       FBVLR       -       5.0       -       mV/V         From DC to 100 Hz and RFB = 1 Ω       FBC       -       -       0.1       μA         Standby Current at I <sub>OUT</sub> = 0 mA, CTRL = Low, V <sub>bat</sub> = 4.2 V       I <sub>STB</sub> -       0.3       3.0       μA         Quiescent Current Switching at I <sub>OUT</sub> = 0 mA, CTRL = High, V <sub>bat</sub> = 4.2 V (Note 12)       I <sub>QS</sub> -       5.0       -       mA         V <sub>IN</sub> Undervoltage Lockout Threshold to Enable the Converter       U <sub>VLO</sub> 2.2       2.4       2.6       V         Undervoltage Lockout Hysteresis       U <sub>VLOH</sub> -       100       -       mV         Soft-start Time (Note 11)       S <sub>ST</sub> -       1000       -       μs         Limit of CTRL pin PWM Dimming Frequency (Note 11)       F <sub>DIM</sub> -       0.2       -       kHz         Thermal Shutdown Protection       T <sub>SD</sub> -       160       -       °C         Thermal Shutdown Protection Hysteresis       T <sub>SD</sub> -       20       -       °C         Voltage Input Logic Low       V <sub>IL</sub> -       -       -       V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Available Output Power (Note 11) When $V_{in} \ge 3.1 \text{ V } (V_{out} = 4.7 \text{ V}, 900 \text{ mA})$ | P <sub>OUT</sub>                   | 4.3  | -    | _    | W    |

| From DC to 100 Hz and R <sub>FB</sub> = 1 $\Omega$ Feedback Input Current  FeC  FeC  To  O.1 $\mu$ A  Standby Current at I <sub>OUT</sub> = 0 mA, CTRL = Low, V <sub>bat</sub> = 4.2 V  Quiescent Current Switching at I <sub>OUT</sub> = 0 mA, CTRL = High, V <sub>bat</sub> = 4.2 V  (Note 12) $V_{IN}$ Undervoltage Lockout  Threshold to Enable the Converter  UvLO  UVLO  UVLO  UVLO  UVLO  Soft—start Time (Note 11)  SST  To  1000  MY  Soft—start Time (Note 11)  Fight  Figh                                                   | Feedback Voltage Threshold in Steady State at 25°C                                                          | F <sub>BV</sub>                    | 190  | 200  | 210  | mV   |

| Standby Current at $I_{OUT} = 0$ mA, CTRL = Low, $V_{bat} = 4.2 \text{ V}$ Quiescent Current Switching at $I_{OUT} = 0$ mA, CTRL = High, $V_{bat} = 4.2 \text{ V}$ (Note 12) $V_{IN}$ Undervoltage Lockout  Threshold to Enable the Converter  UvLO  UvLOH  UvLOH  UvLOH  UvloH  UvloH  UvloH  Soft—start Time (Note 11)  Soft—start Time (Note 11)  Soft—start Time (Note 11)  Find  Fi                                                                                                     | Line Regulation, Measured on FB Pin (Note 8) From DC to 100 Hz and $R_{FB}$ = 1 $\Omega$                    | F <sub>BVLR</sub>                  | -    | 5.0  | _    | mV/V |

| Quiescent Current Switching at $I_{OUT} = 0$ mA, CTRL = High, $V_{bat} = 4.2 \text{ V}$ $I_{QS}$ $ 5.0$ $-$ mA $(Note 12)$ $V_{IN}$ Undervoltage Lockout $I_{IN}$ Undervoltage Lockout $I_{IN}$ Undervoltage Lockout Hysteresis $I_{IN}$ UvLoH $I_{IN}$ UvLoH $I_{IN}$ Undervoltage Lockout Hysteresis $I_{IN}$ UvLoH $I_{IN}$ UvLoH $I_{IN}$ Undervoltage Lockout Hysteresis $I_{IN}$ UvLoH                                                                                                          | Feedback Input Current                                                                                      | F <sub>BC</sub>                    | ı    | -    | 0.1  | μΑ   |

| V <sub>IN</sub> Undervoltage Lockout                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Standby Current at I <sub>OUT</sub> = 0 mA, CTRL = Low, V <sub>bat</sub> = 4.2 V                            | I <sub>STB</sub>                   | -    | 0.3  | 3.0  | μΑ   |

| Threshold to Enable the Converter         2.2         2.4         2.6           Undervoltage Lockout Hysteresis         UVLOH         -         100         -         mV           Soft-start Time (Note 11)         SST         -         1000         -         μs           Limit of CTRL pin PWM Dimming Frequency (Note 11)         FDIM         -         0.2         -         kHz           Thermal Shutdown Protection         TSD         -         160         -         °C           Thermal Shutdown Protection Hysteresis         TSDH         -         20         -         °C           Voltage Input Logic Low         VIL         -         -         0.4         V           Voltage Input Logic High         VIH         1.2         -         -         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Quiescent Current Switching at $I_{OUT} = 0$ mA, CTRL = High, $V_{bat} = 4.2$ V (Note 12)                   | I <sub>QS</sub>                    | -    | 5.0  | _    | mA   |

| Soft-start Time (Note 11) $S_{ST} - 1000 - \mu_S$ Limit of CTRL pin PWM Dimming Frequency (Note 11) $F_{DIM} - 0.2 - kHz$ Thermal Shutdown Protection $T_{SD} - 160 - ^{\circ}C$ Thermal Shutdown Protection Hysteresis $T_{SDH} - 20 - ^{\circ}C$ Voltage Input Logic Low $V_{IL} 0.4 V$ Voltage Input Logic High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | V <sub>IN</sub> Undervoltage Lockout<br>Threshold to Enable the Converter                                   | U <sub>VLO</sub>                   | 2.2  | 2.4  | 2.6  | V    |

| Limit of CTRL pin PWM Dimming Frequency (Note 11) $F_{DIM} - 0.2 - kHz$ Thermal Shutdown Protection $T_{SD} - 160 - ^{\circ}C$ Thermal Shutdown Protection Hysteresis $T_{SDH} - 20 - ^{\circ}C$ Voltage Input Logic Low $V_{IL} 0.4 V$ Voltage Input Logic High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Undervoltage Lockout Hysteresis                                                                             | U <sub>VLOH</sub>                  | -    | 100  | -    | mV   |

| Thermal Shutdown Protection $T_{SD}$ - 160 - °C  Thermal Shutdown Protection Hysteresis $T_{SDH}$ - 20 - °C  Voltage Input Logic Low $V_{IL}$ 0.4 $V$ Voltage Input Logic High $V_{IH}$ 1.2 - $V_{IL}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Soft-start Time (Note 11)                                                                                   | S <sub>ST</sub>                    | -    | 1000 | _    | μS   |

| Thermal Shutdown Protection Hysteresis  TSDH  - 20 - °C  Voltage Input Logic Low  VIL 0.4  V  Voltage Input Logic High                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Limit of CTRL pin PWM Dimming Frequency (Note 11)                                                           | F <sub>DIM</sub>                   | -    | 0.2  | -    | kHz  |

| Voltage Input Logic Low         V <sub>IL</sub> -         -         0.4         V           Voltage Input Logic High         V <sub>IH</sub> 1.2         -         -         V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Thermal Shutdown Protection                                                                                 | T <sub>SD</sub>                    | -    | 160  | -    | °C   |

| Voltage Input Logic High V <sub>IH</sub> 1.2 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Thermal Shutdown Protection Hysteresis                                                                      | T <sub>SDH</sub>                   | -    | 20   | -    | °C   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Voltage Input Logic Low                                                                                     | V <sub>IL</sub>                    | -    | _    | 0.4  | V    |

| CTRL Pin Pulldown Resistance $R_{CTRL}$ 150 220 290 $k\Omega$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Voltage Input Logic High                                                                                    | V <sub>IH</sub>                    | 1.2  | -    | -    | V    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | CTRL Pin Pulldown Resistance                                                                                | R <sub>CTRL</sub>                  | 150  | 220  | 290  | kΩ   |

<sup>8.</sup>  $T_A$  between  $-10^{\circ}$ C to  $+85^{\circ}$ C 9. Efficiency is defined by  $100^{\circ}$  ( $P_{out}/P_{in}$ ) at  $25^{\circ}$ C.  $V_{in} = 3.3$  V,  $I_{OUT} = 500$  mA, Load = 1 LED ( $V_f = 3.9$  V)  $10.L = 4.7 \ \mu H$  (TDK RLF7030T–4R7M3R4),  $C_{out} = 22 \ \mu F$  X5R 11. Guaranteed by design and characterized. 12. The overall tolerance is dependent on the accuracy of the external resistor.

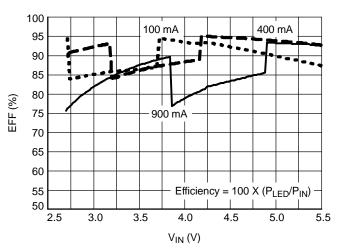

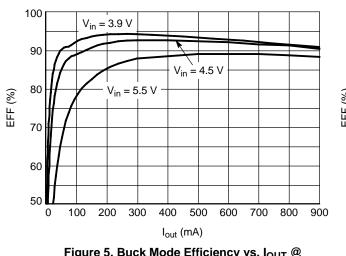

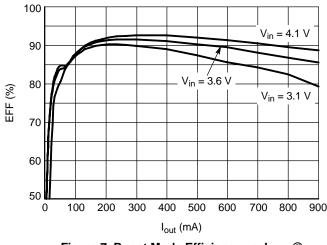

#### TYPICAL PERFORMANCE CHARACTERISTICS

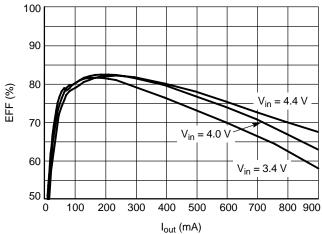

Figure 4. Efficiency vs. V<sub>IN</sub> LED = Lumileds LUXEON III, L = TDK RLF7030T-4R7

Figure 5. Buck Mode Efficiency vs.  $I_{OUT}$  @  $V_{OUT}$  = 3.1 V L = TDK RLF7030T-4R7

Figure 7. Boost Mode Efficiency vs.  $I_{OUT}$  @  $V_{OUT}$  = 5.0 V L = TDK RLF7030T-4R7

Figure 6. Buck-Boost Mode Eff. vs. I<sub>OUT</sub> @ V<sub>OUT</sub> = 3.8 V L = TDK RLF7030T-4R7

Figure 8. IPEAK MAX vs. RPCA

#### TYPICAL PERFORMANCE CHARACTERISTICS

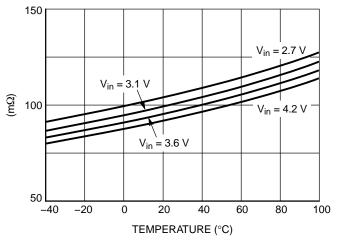

Figure 9. NMOS R<sub>DSON</sub> vs. Temperature

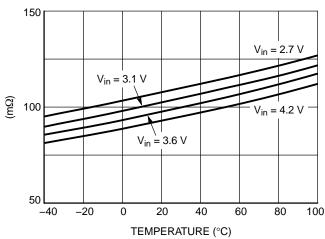

Figure 10. PMOS R<sub>DSON</sub> vs. Temperature

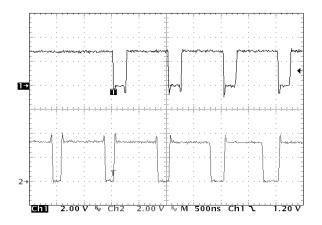

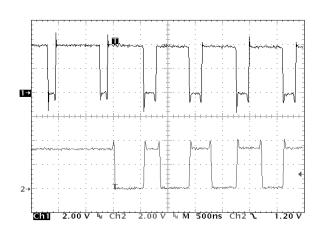

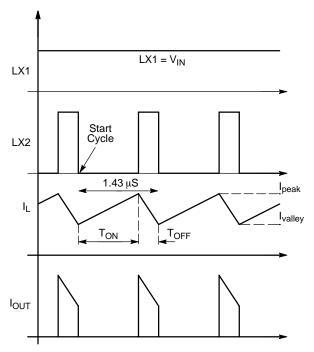

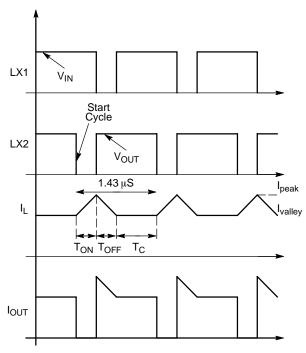

Figure 11. Transitional Period Switch Pins (LX1 and LX2) from Boost to Buck–Boost when  $V_{OUT} - V_{IN}$  is < than 375 mV

Figure 12. Transitional Period Switch Pins (LX1 and LX2) from Buck to Buck-Boost when  $V_{IN} - V_{OUT}$  is > than 650 mV

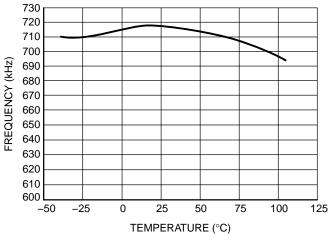

Figure 13. Oscillator Frequency vs. Temperature  $V_{OUT} = 3.6 \text{ V}$ ,  $V_{IN} = 3.6 \text{ V}$

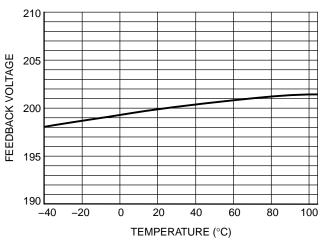

Figure 14. Feedback Voltage vs. Temperature  $V_{OUT}$  = 3.6 V,  $V_{IN}$  = 3.6 V

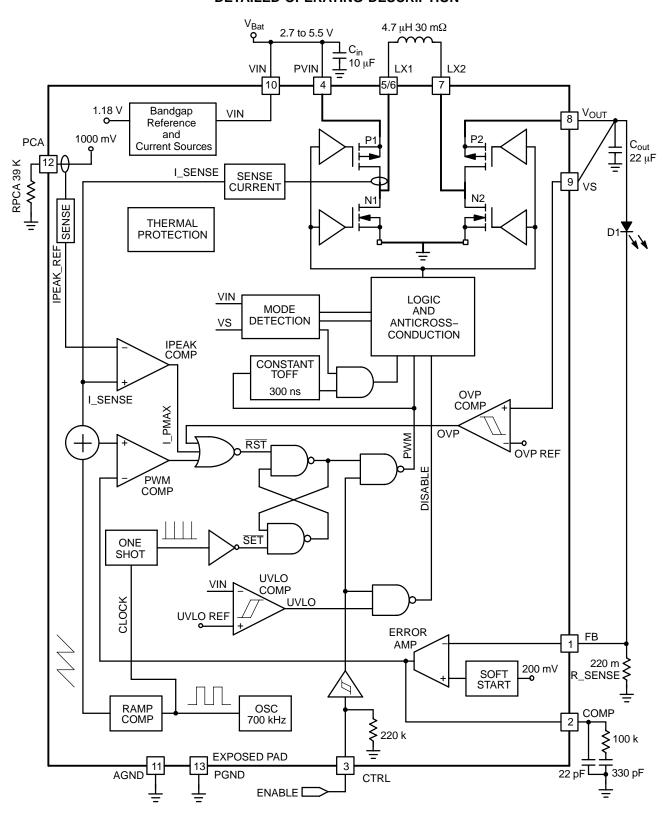

#### **DETAILED OPERATING DESCRIPTION**

Figure 15. Functional Block Diagram

#### Operation

The NCP5030 DC-DC converter is based on a Current Mode PWM architecture specifically designed to efficiently provide a regulated current to a high current white LED. This device utilizes fixed frequency synchronous buck-boost switching regulator architecture. This topology is critical in single cell Lithium-Ion/Polymer battery or 3 Alkaline powered applications as the forward voltage of the LED may be greater than or less than the battery voltage. A low feedback voltage of 200 mV (nom) minimizes power losses in the current setting resistor connected between the cathode of the LED and ground.

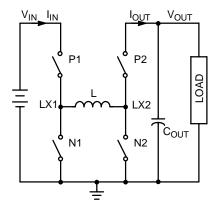

The core switching regulator is configured as a full bridge with four low  $R_{DSON} \left( 0.1 \; \Omega \right)$  MOSFET switches to maximize efficient power delivery. Another advantage of this topology is that it supports a true–shut down mode where the LED will be disconnected from the power supply when the device is placed in disable mode.

Figure 16 shows how the four switches are connected to charge and discharge the current from  $P_{VIN}$  to  $V_{OUT}$  through the inductor.

Figure 16. Basic Power Switches Topology

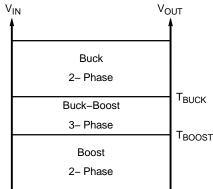

The converter operates in three different modes as a function of  $V_{OUT} - V_{IN}$  (Figure 17): In Buck mode when  $V_{OUT}$  is below  $V_{IN} - 650$  mV ( $T_{BUCK}$  nominal), in Boost mode when  $V_{OUT}$  is above  $V_{IN} + 375$  mV ( $T_{BOOST}$  nominal) and in Buck–Boost mode when  $V_{OUT}$  is between this tow thresholds.

Figure 17. Conversion Mode