# THIS DOCUMENT IS FOR MAINTENANCE PURPOSES ONLY AND IS NOT RECOMMENDED FOR NEW DESIGNS

# SL6440 HIGH LEVEL MIXER

The SL6440 is a double balanced mixer intended for use in radio systems up to 150MHz. A special feature of the circuit allows external selection of the DC operating conditions by means of a resistor connected between pin 11 (bias) and Vcc When biased for a supply current of 50mA the SL6440 offers a 3rd order intermodulation intercept point of typically +30dBm, a value previously unobtainable with integrated circuits. This makes the device suitable for many applications where diode ring mixers had previously been used and offers the advantages of a voltage gain, low local oscillator drive requirement and superior isolation.

### **FEATURES**

- +30dBm Input Intercept Point

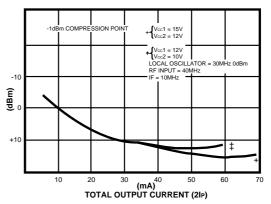

- +15dBm Compression Point (1dB)

- Programmable Performance

- Full Military Temperature Range (SL644A)

### **APPLICATIONS**

- Mixers in Radio Transceivers

- Phase Comparators

- Modulators

## ORDERING INFORMATION SL6440 A DG SL6440 C DP

# ELECTRICAL CHARACTERISTICS

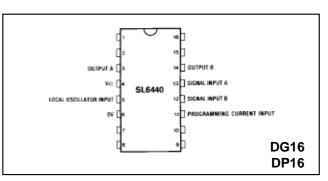

Fig.1 Pin connections - top view

#### **ABSOLUTE MAXIMUM RATINGS**

| Supply voltage and output pins                           | 15V             |

|----------------------------------------------------------|-----------------|

| Maximum power dissipation<br>(Derate above 25°C: 8mW/°C) | 1200mW          |

| Storage temperature range                                | -65°C to +150°C |

| Programming current into pin 11                          | 50mA            |

| THERMAL CHARACTERISTICS                                  |                 |

| Thermal resistance: OJA                                  | 125°C/W         |

| <i>O</i> JC                                              |                 |

| Time constant: Junction-Ambient                          | 1.9 mins        |

| Maximum chip temperature                                 | 150°C           |

Vcc1 = 12V; Vcc2 = 10V; IP = 25mA; T<sub>amb</sub> = -55°C to +125°C (SL64440A), -30°C to +85°C (SL6440C) Local oscillator input level = 0dBm; Test circuit Fig.2.

|                                                                                                                                                                                                               | Value      |                                       |      |                                      |                                                                                                                |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|---------------------------------------|------|--------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Characteristic                                                                                                                                                                                                | Min.       | Тур.                                  | Max. | Units                                | Inits Conditions                                                                                               |

| Signal frequency 3dB point<br>Oscillator frequency 3dB point<br>3rd order input intercept point<br>Third order intermodulation distortion<br>Second order intermodulation distortion<br>1dB compression point | 100<br>100 | 150<br>150<br>+30<br>-60<br>-75<br>15 |      | MHz<br>MHz<br>dBm<br>dB<br>dB<br>dBm | Two 0dBm input<br>Signals<br>Vcc1 = 15V Vcc2 = 12V<br>Vcc1 = 12V Vcc2 = 10V                                    |

| Noise figure<br>Conversion gain<br>Carrier leak to signal input<br>Level of carrier at IF output<br>Supply current<br>Supply current (total from Vcc1 & Vcc2)                                                 | -40        | 11<br>-1<br>-25<br>7<br>60            |      | dB<br>dB<br>dBm<br>mA<br>mA          | Fig.8 test circuit<br>$50\Omega$ load Fig.2<br>Test circuit Fig.8<br>See applications information<br>$I_P = 0$ |

| Local oscillator input<br>Local oscillator input impedance<br>Signal input impedance                                                                                                                          | 100        | 250<br>1.5<br>500<br>1000             | 500  | mV rms<br>kΩ<br>Ω<br>Ω               | l⊵ = 35mA<br>Single ended<br>Differential                                                                      |

NOTE Supply current in Pin 3 is equal to that in Pin 14 and is equal to IP See over. Vpin11 3Vbe 2.1V.

# SL6440

# **CIRCUIT DESCRIPTION**

The SL6440 is a high level mixer designed to have a linear RF performance. The linearity can be programmed using the IP pin (11).

The output pins are open collector outputs so that the conversion gain and output loads can be chosen for the specific application.

Since the outputs are open collectors they should be returned to a supply Vcc1 through a load.

The choice of Vcc1 is important since it must be ensured that the voltage on pins 3 and 14 is not low enough to saturate the output transistors and so limit the signal swing unnecessarily. If the voltage on pins 3 and 14 is always greater than Vcc2 the outputs will not saturate. The output frequency response will reduce as the output transistors near saturation.

In this case the signal will be limiting at the input before the output saturates.

The device has a separates supply (Vcc2) for the oscillator buffer (pin 4).

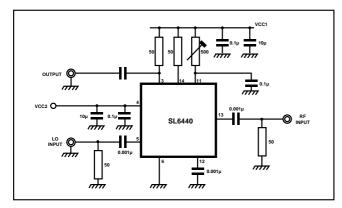

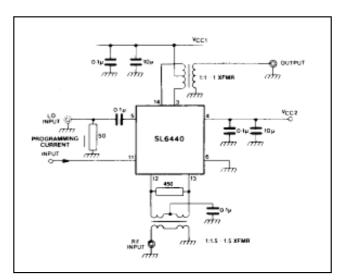

Fig.2 Typical application and test circuit

The current (I<sub>P</sub>) programmed into pin 11 can be supplied via a resistor from Vcc1 or form a current source.

The conversion gain is equal to

| GdB = 20 Log 56.                | RL IP<br>.61 IP + 0.078                                | for single-ended output                                                                                                            |

|---------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| GdB = 20 Log 56.                | 2RL lp<br>61 lp + 0.078                                | for differential output<br>5                                                                                                       |

| mW diss<br>where Vo<br>VP<br>IP | = 2 IP Vo +<br>= voltage o<br>= voltage o<br>= program | ed using the formula<br>VPIP + Vcc2 Diss<br>In pin 3 or pin 14<br>In pin 11<br>ming current (mA)<br>In obtained from graph (Fig.6) |

|                                 |                                                        |                                                                                                                                    |

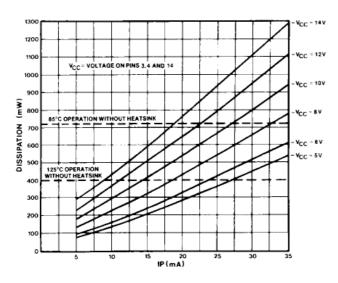

As an example Fig.7 shows typical dissipations assuming Vcc1 and Vo are equal. This may not be the case in pratice and the device dissipation will have to be calculated for any particular application.

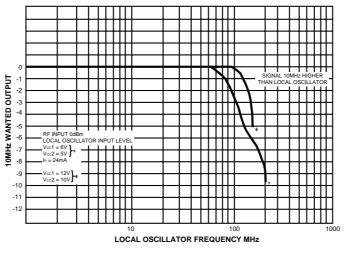

Fig.5 shows the intermodulation performance against IP. The curves are independent of Vcc1 and Vcc2 but if Vcc1 becomes too low the output signal swing cannot be accommodated, and if Vcc2 becomes too low the circuit will not provide enough drive to sink the programmed current. Examples are shown of performance at various supply voltages.

The current in pin 14 is equal to the current in pin 3 which is equal to the current in pin 11.

Fig.3 Compression point v. total output current

Fig.4 Frequency response at constant output IF

Fig.5 Intermodulation v. programming current

# **APPLICATIONS**

The SL6440 can be used with differential or singleended inputs and outputs. A balanced input will give bettercarrier leak The high input impedanceallowsstepup transformers to be used if desired, whilst high output impedance allows a choice of output impedance and conversion gain.

Fig. 2 shows the simplest application circuit. The input and output are single-ended and Ip is supplied from Vcc1 via a resistor. Increasing RL will increase the conversion gain, care being taken to choose a suitable value for Vcc1.

Fig. 8 shows an application with balanced input, for improved carrier leak, and balanced output for increased conversion gain. A lower Vcc1 giving lower device dissipation can be used with this arrangement.

Fig.7 Device dissipation v. IP

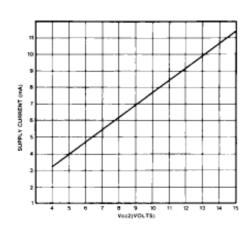

Fig.6 Supply current v. Vcc2 (IP = 0)

## **DESIGN PROCEDURE**

1. Decide on input configuration using local oscillator data. If using transformer on input, decide on ratio from noise considerations.

2. Decide on output configuration and value of conversion gain required.

3. Decide on value of IP and Vcc2 using intermodulation and compression point graphs.

4. Using values of conversion gain, Vcc2, load and Ip already chosen, decide on value of Vcc1.

5. Calculate device dissipation and decide whether heatsink is required from maximum operating temperature considerations.

Fig.8 Typical application circuit for highest performance

# For more information about all Zarlink products visit our Web Site at

# www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. trading as Zarlink Semiconductor or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in an I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright 2003, Zarlink Semiconductor Inc. All Rights Reserved.

**TECHNICAL DOCUMENTATION - NOT FOR RESALE**