# mos integrated circuit $\mu PD75218$

## 4-BIT SINGLE-CHIP MICROCOMPUTER

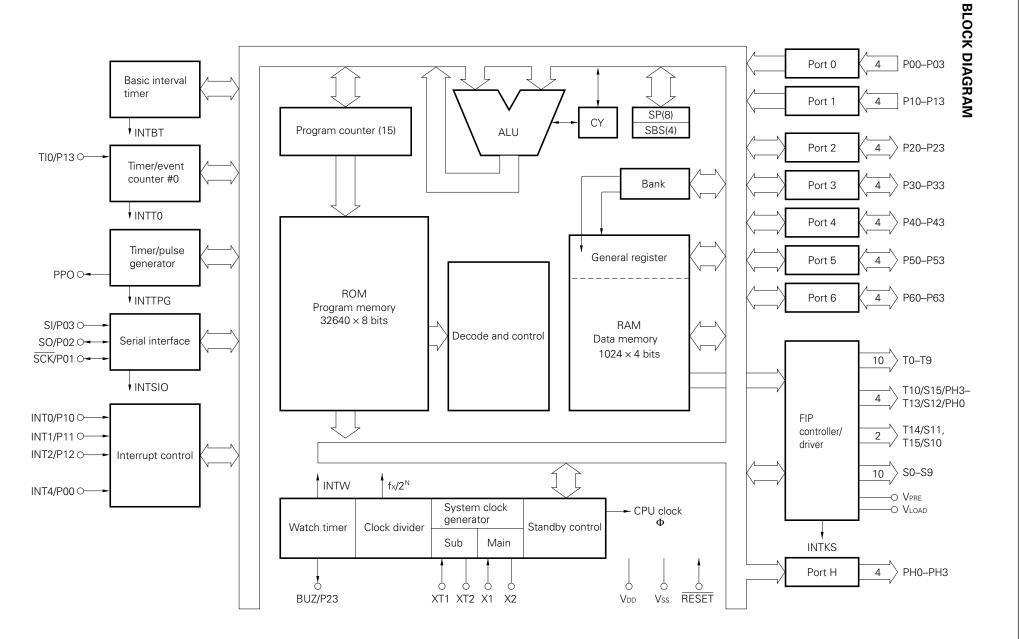

The  $\mu$ PD75218 is a microcomputer with a CPU capable of 1-, 4-, and 8-bit-wise data processing, ROM, RAM, I/O ports, an FIP controller/driver, a watch timer, a timer/pulse generator capable of outputting 14-bit PWM pulses, a serial interface and a vectored interrupt function integrated on a single chip.

It is most suitable for applications which use fluorescent display tubes as display devices and require the timer/watch function and high-speed interrupt servicing, such as VCR, CD and ECR. It can help to provide the unit with many functions and to decrease performance costs.

The  $\mu$ PD75218 has larger ROM and RAM capacity than its predecessor,  $\mu$ PD75217. So several codes required before have been reduced to only one code in the  $\mu$ PD75218 specifications.

The one-time PROM product,  $\mu$ PD75P218 and various development tools (IE-75001-R, assembler, etc.) are available for system development evaluation or small production.

The following manual provides detailed description of the functions of the  $\mu$ PD75218. Be sure to read this manual when you design an application system.

μPD75218 User's Manual: IEU-692

#### **FEATURES**

- On-chip large-capacity ROM and RAM

- Program memory (ROM): 32K × 8 bits

- Data memory (RAM) : 1K × 4 bits

- Architecture equal to that of an 8-bit microcomputer

- High-speed operation: Minimum instruction execution time : 0.67  $\mu$ s (when the microcomputer operates at 6.0 MHz)

- Instruction execution time variable function realizing a wide range of operating voltages

- On-chip programmable fluorescent indication panel (FIP) controller/driver

- Timer function: 4 ch

- 14-bit PWM output capability with the voltage synthesizer type electronic tuner

- · Buzzer output capability

- Interrupt function with importance attached to applications

- · For power-off detection

- · For reception of remote-controller signal

- Product with an on-chip PROM : μPD75P218 (on-chip EPROM : WQFN package)

The information in this document is subject to change without notice.

# **ORDERING INFORMATION**

| Part number                             | Package                                | Quality grade |  |

|-----------------------------------------|----------------------------------------|---------------|--|

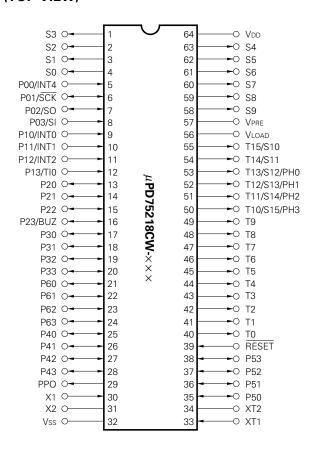

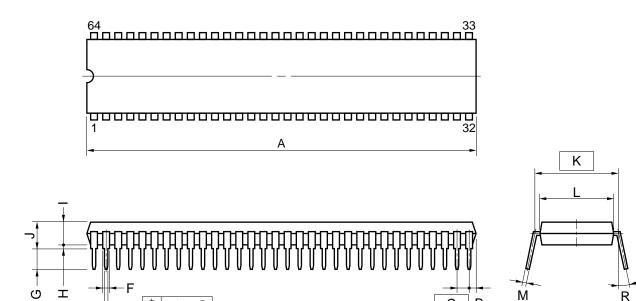

| $\mu$ PD75218CW- $\times\!\!\times\!\!$ | 64-pin plastic shrink DIP (750 mil)    | Standard      |  |

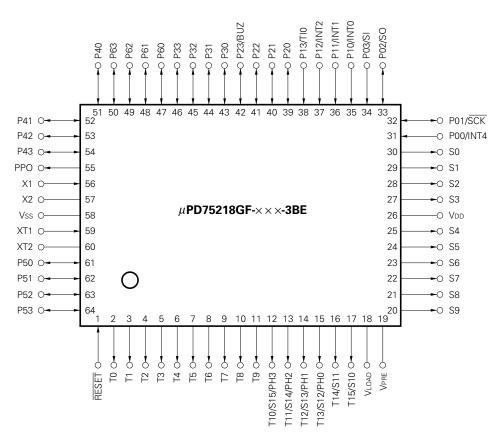

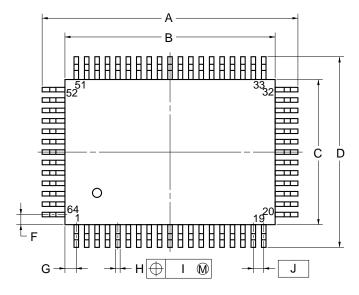

| $\mu$ PD75218GF-×××-3BE                 | 64-pin plastic QFP (14 $\times$ 20 mm) | Standard      |  |

**Remark** ××× is a ROM code.

Please refer to "Quality Grades on NEC Semiconductor Devices" (Document number IEI-1209) published by NEC Corporation to know the specification of quality grade on the devices and its recommended applications

# **LIST OF FUNCTIONS**

| Item                                                                                             | Function                                                                                                                                                                                                                                        |  |  |

|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Built-in memory                                                                                  | ROM: 32640 × 8 bits, RAM: 1024 × 4 bits                                                                                                                                                                                                         |  |  |

| I/O line (including FIP <sup>®</sup> dual-<br>function pins and excluding<br>FIP dedicated pins) | 33 lines  - CMOS input : 8 lines  - CMOS I/O : 20 lines (LED drive: 8 lines)  - CMOS output : 1 line (PWM/pulse output)  - P-ch open-drain output with high withstand voltage and high current: 4 lines (LED drive)                             |  |  |

| Instruction cycle                                                                                | <ul> <li>0.67 μs, 1.33 μs, 10.7 μs (with main system clock operating at 6.0 MHz)</li> <li>0.95 μs, 1.91 μs, 15.3 μs (with main system clock operating at 4.19 MHz)</li> <li>122 μs (with subsystem clock operating at 32.768 kHz)</li> </ul>    |  |  |

| FIP controller/driver                                                                            | <ul> <li>Number of segments: 9 to 16 segments</li> <li>Number of digits: 9 to 16 digits</li> <li>Dimmer function: 8 levels</li> <li>Mask option for pull-down resistors</li> <li>Key scan interrupt generation</li> </ul>                       |  |  |

| Timer                                                                                            | 4 channels  Timer/pulse generator : 14-bit PWM output enabled  Watch timer : Buzzer output enabled  Timer/event counter  Basic interval timer : Watchdog timer application capability                                                           |  |  |

| Serial interface                                                                                 | MSB start/LSB start switchable     Serial bus configuration capability                                                                                                                                                                          |  |  |

| Vectored interrupt                                                                               | External : 3, Internal : 5                                                                                                                                                                                                                      |  |  |

| Test input                                                                                       | External : 1, Internal : 1                                                                                                                                                                                                                      |  |  |

| System clock oscillator                                                                          | Ceramic/crystal oscillator for main system clock oscillation: 6.0 MHz standard     Ceramic/crystal oscillator for main system clock oscillation: 4.19 MHz standard     Crystal oscillator for subsystem clock oscillation : 32.768 kHz standard |  |  |

| Mask option                                                                                      | High withstand-voltage port (pull-down resistor)     Port 6 (pull-down resistor)                                                                                                                                                                |  |  |

| Operating temperature range                                                                      | −40 to +85 °C                                                                                                                                                                                                                                   |  |  |

| Operating supply voltage                                                                         | 2.7 to 6.0 V (standby data hold : 2.0 to 6.0 V)                                                                                                                                                                                                 |  |  |

| Package                                                                                          | 64-pin plastic shrink DIP (750 mil)     64-pin plastic QFP (14 × 20 mm)                                                                                                                                                                         |  |  |

# **CONTENTS**

| 1.  | 1. PIN CONFIGURATION (TOP VIEW) |                                                |    |  |  |  |

|-----|---------------------------------|------------------------------------------------|----|--|--|--|

| 2.  | BLO                             | CK DIAGRAM                                     | 6  |  |  |  |

| 3.  | PIN F                           | UNCTIONS                                       | 7  |  |  |  |

|     | 3.1                             | PORT PINS                                      | 7  |  |  |  |

|     | 3.2                             | NON-PORT PINS                                  | 8  |  |  |  |

|     | 3.3                             | PIN INPUT/OUTPUT CIRCUIT LIST                  | 9  |  |  |  |

|     | 3.4                             | HANDLING UNUSED PINS                           | 10 |  |  |  |

|     | 3.5                             | NOTES ON USE OF THE P00/INT4 PIN AND RESET PIN | 11 |  |  |  |

|     | 3.6                             | NOTES ON USE OF THE XT1, XT2 AND P50 PIN       | 11 |  |  |  |

| 4.  | MEM                             | ORY CONFIGURATION                              | 12 |  |  |  |

| 5.  | PERI                            | PHERAL HARDWARE FUNCTIONS                      | 15 |  |  |  |

|     | 5.1                             | PORTS                                          | 15 |  |  |  |

|     | 5.2                             | CLOCK GENERATOR                                | 16 |  |  |  |

|     | 5.3                             | BASIC INTERVAL TIMER                           | 17 |  |  |  |

|     | 5.4                             | WATCH TIMER                                    | 18 |  |  |  |

|     | 5.5                             | TIMER/EVENT COUNTER                            | 19 |  |  |  |

|     | 5.6                             | TIMER/PULSE GENERATOR                          | 20 |  |  |  |

|     | 5.7                             | SERIAL INTERFACE                               | 21 |  |  |  |

|     | 5.8                             | FIP CONTROLLER/DRIVER                          | 23 |  |  |  |

| 6.  | INTE                            | RRUPT FUNCTIONS                                | 24 |  |  |  |

| 7.  | STAI                            | NDBY FUNCTIONS                                 | 26 |  |  |  |

| 8.  | RESE                            | T FUNCTIONS                                    | 27 |  |  |  |

| 9.  | INST                            | RUCTION SET                                    | 29 |  |  |  |

| 10. | MAS                             | K OPTION SELECTION                             | 38 |  |  |  |

| 11. | APPL                            | ICATION BLOCK DIAGRAM                          | 39 |  |  |  |

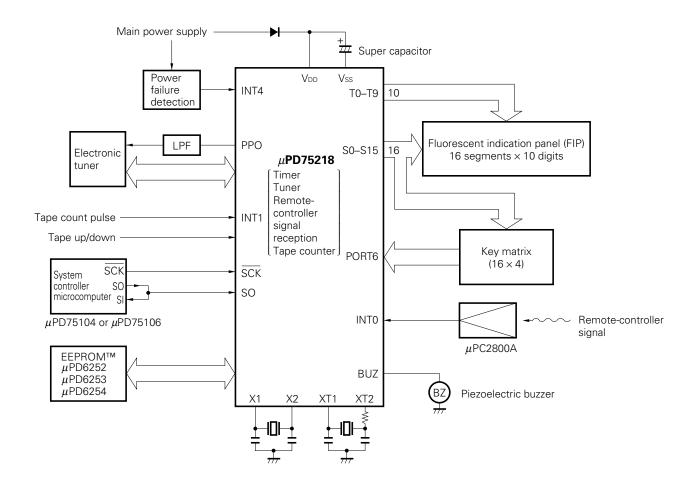

|     | 11.1                            | VCR TIMER TUNER                                | 39 |  |  |  |

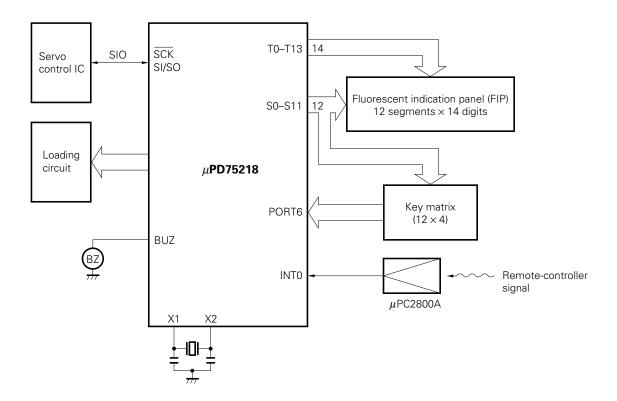

|     | 11.2                            | COMPACT DISK PLAYER                            | 40 |  |  |  |

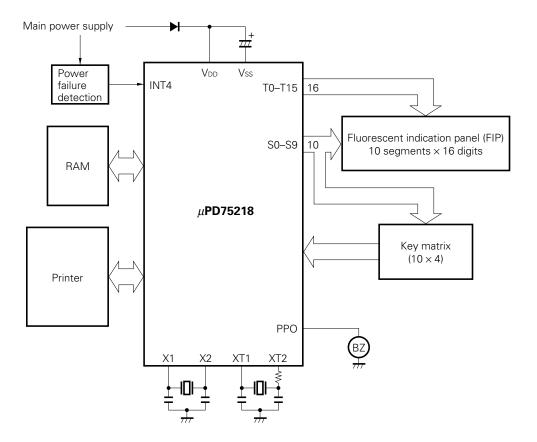

|     | 11.3                            | ECR                                            | 41 |  |  |  |

| * | 12. ELECTRICAL SPECIFICATIONS                         | 42 |

|---|-------------------------------------------------------|----|

| * | 13. CHARACTERISTIC CURVES (FOR REFERENCE)             | 53 |

|   | 14. PACKAGE DIMENSIONS                                | 55 |

|   | 15. RECOMMENDED SOLDERING CONDITIONS                  | 57 |

|   | APPENDIX A FUNCTIONS OF $\mu$ PD752×× SERIES PRODUCTS | 58 |

|   | APPENDIX B DEVELOPMENT TOOLS                          | 59 |

| * | APPENDIX C RELATED DOCUMENTS                          | 60 |

## 1. PIN CONFIGURATION (TOP VIEW)

Ņ

# 3. PIN FUNCTIONS

# 3.1 PORT PINS

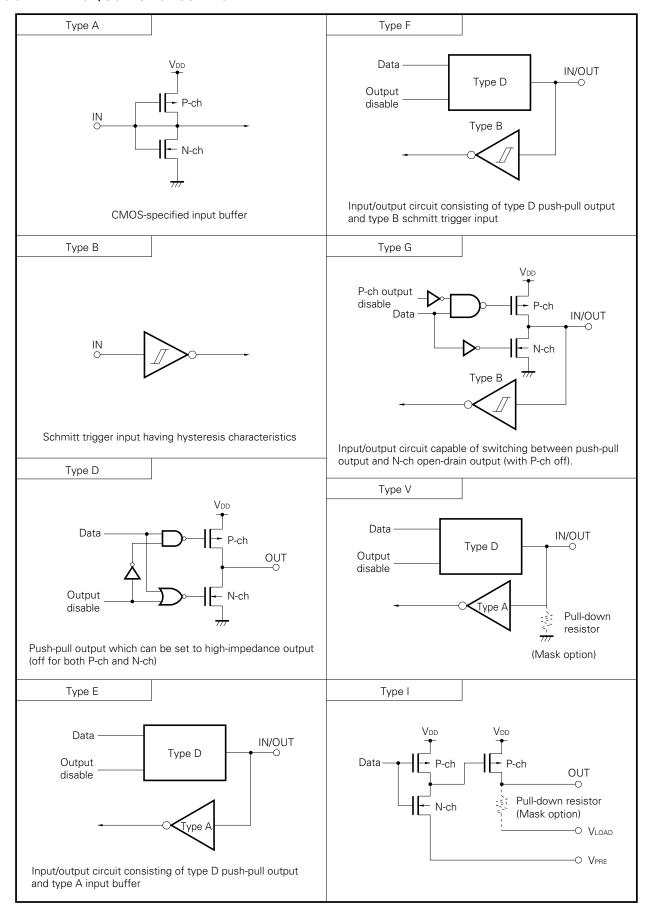

| Pin        | I/O              | Dual-<br>function pin | - ··                                                                                                                                                               |                                      | 8-bit<br>I/O | After reset                | Input / output<br>circuit type <sup>Note</sup> |

|------------|------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--------------|----------------------------|------------------------------------------------|

| P00        | Input            | INT4                  | 4-bit input port (PORT0)                                                                                                                                           |                                      | ×            | Input                      | B                                              |

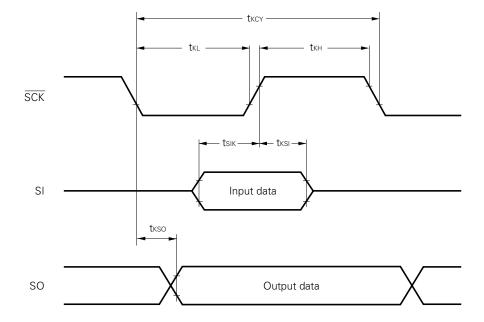

| P01        | Input/output     | SCK                   |                                                                                                                                                                    |                                      |              |                            | E                                              |

| P02        | Input/output     | SO                    |                                                                                                                                                                    |                                      |              |                            | G                                              |

| P03        | Input            | SI                    |                                                                                                                                                                    |                                      |              |                            | B                                              |

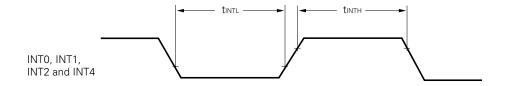

| P10        | Input            | INT0                  |                                                                                                                                                                    | Noise elimination function available |              | Input                      | B                                              |

| P11        |                  | INT1                  |                                                                                                                                                                    | Noise elimination function available |              |                            |                                                |

| P12        |                  | INT2                  | 4-bit input po                                                                                                                                                     | ort (PORT1)                          |              |                            |                                                |

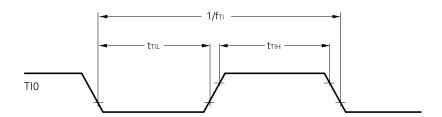

| P13        |                  | TI0                   |                                                                                                                                                                    |                                      |              |                            |                                                |

| P20        | Input/           |                       | 4-bit input/or                                                                                                                                                     | utput port (PORT2)                   | ×            | Input                      | Е                                              |

| P21        | output           |                       |                                                                                                                                                                    |                                      |              |                            |                                                |

| P22        |                  |                       |                                                                                                                                                                    |                                      |              |                            |                                                |

| P23        |                  | BUZ                   |                                                                                                                                                                    |                                      |              |                            |                                                |

| P30 to P33 | Input/<br>output |                       | Programmable 4-bit input/ output port (PORT3). Input/output specifiable in 1-bit units.                                                                            |                                      |              | Input                      | E                                              |

| P40 to P43 | Input/<br>output |                       | 4-bit input/output port (PORT4).<br>LED direct drive capability.                                                                                                   |                                      | 0            | Input                      | E                                              |

| P50 to P53 | Input/<br>output |                       | 4-bit input/output port (PORT5).<br>LED direct drive capability.                                                                                                   |                                      |              | Input                      | E                                              |

| P60 to P63 | Input/<br>output |                       | Programmable 4-bit input/output port (PORT6). Input/output specifiable in 1-bit units. On-chip pull-down resistor available (mask option). Suitable for key input. |                                      | ×            | Input                      | V                                              |

| PH0        | Output           | T13/S12               | 4-bit P-ch open-drain output port with high                                                                                                                        |                                      | ×            | Low level                  | I                                              |

| PH1        |                  | T12/S13               | withstand voltage and high current (PORTH).                                                                                                                        |                                      |              | (with an on-<br>chip pull- |                                                |

| PH2        |                  | T11/S14               | LED direct drive capability. On-chip pull-down resistor available (mask option).                                                                                   |                                      |              | down resistor)<br>or high  |                                                |

| PH3        | 1                | T10/S15               |                                                                                                                                                                    | and a second production.             |              | impedance.                 |                                                |

**Note** The circuit-type codes enclosed in circles indicate that the corresponding circuits have a Schmitt-triggered input.

# 3.2 NON-PORT PINS

| Pin                   | I/O          | Dual-<br>function pin |                                                                              | Function                                                                                                                     | After reset                                             | Input / output<br>circuit type <sup>Note</sup> |

|-----------------------|--------------|-----------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|------------------------------------------------|

| T0 to T9              | Output       |                       | FIP controller/<br>driver output                                             | Output pins with high withstand voltage and high current for digit output                                                    | Low level<br>(with an on-<br>chip pull-                 | I                                              |

| T10/S15 to<br>T13/S12 |              | PH3 to PH0            | pins. Pull-down resistor can be incorpo-                                     | Output pins with high withstand voltage and high current also used for digit/segment output Extra pins can be used as PORTH. | down<br>resistor) or<br>high<br>impedance<br>(without a |                                                |

| T14/S11,<br>T15/S10   |              | _                     | rated in bit<br>units (mask<br>option).                                      | Output pins with high withstand voltage and high current also used for digit/ segment output Static output also possible.    | pull-down<br>resistor)                                  |                                                |

| S9                    |              |                       |                                                                              | High withstand-voltage output for segment output. Static output also possible.                                               |                                                         |                                                |

| S0 to S8              |              |                       |                                                                              | High withstand-voltage output for segment output                                                                             |                                                         |                                                |

| PPO                   | Output       |                       | Timer/pulse ge                                                               | enerator pulse output                                                                                                        | High<br>impedance                                       | D                                              |

| TI0                   | Input        | P13                   | External event                                                               | pulse input for timer/event counter                                                                                          |                                                         | B                                              |

| SCK                   | Input/output | P01                   | Serial clock in                                                              | put/output                                                                                                                   | Input                                                   | (F)                                            |

| SO                    | Input/output | P02                   | Serial data out                                                              | put or serial data input/output                                                                                              | Input                                                   | G                                              |

| SI                    | Input        | P03                   | Serial data inp                                                              | ut or normal input                                                                                                           | Input                                                   | B                                              |

| INT4                  | Input        | P00                   | Edge-detected vectored interrupt input (rising and falling edge detection).  |                                                                                                                              |                                                         | B                                              |

| INT0                  | Input        | P10                   | Edge-detected vectored interrupt input with noise                            |                                                                                                                              |                                                         | B                                              |

| INT1                  | _            | P11                   | elimination function (detection edge selection possible).                    |                                                                                                                              |                                                         |                                                |

| INT2                  | Input        | P12                   | Edge-detected                                                                | Edge-detected testable input (rising edge detection).                                                                        |                                                         | B                                              |

| BUZ                   | Input/output | P23                   | Fixed frequency output (for buzzer or system clock trimming).                |                                                                                                                              | Input                                                   | E                                              |

| X1                    | Input        |                       | _                                                                            | Crystal/ceramic connection pin for main system clock                                                                         |                                                         |                                                |

| X2                    |              |                       | oscillation.  External clock input to X1 and its inverted clock input to X2. |                                                                                                                              |                                                         |                                                |

| XT1                   | Input        |                       | Crystal connection pin for subsystem clock oscillation.                      |                                                                                                                              |                                                         |                                                |

| XT2                   |              |                       | External clock input to XT1. Leave XT2 open.                                 |                                                                                                                              |                                                         |                                                |

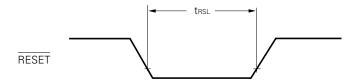

| RESET                 | Input        |                       | System reset input (low level active).                                       |                                                                                                                              |                                                         | B                                              |

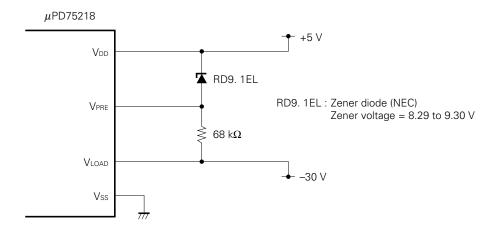

| VPRE                  |              |                       | FIP controller/driver output buffer power supply.                            |                                                                                                                              |                                                         | I                                              |

| VLOAD                 |              |                       | FIP controller/driver pull-down resistor connection pin.                     |                                                                                                                              |                                                         | I                                              |

| V <sub>DD</sub>       |              |                       | Positive power supply.                                                       |                                                                                                                              |                                                         |                                                |

| Vss                   |              |                       | GND potential.                                                               |                                                                                                                              |                                                         |                                                |

**Note** The circuit-type codes enclosed in circles indicate that the corresponding circuits have a Schmitt-triggered input.

\*

## 3.3 PIN INPUT/OUTPUT CIRCUIT LIST

# 3.4 HANDLING UNUSED PINS

| Pin                        | Recommended connection              |

|----------------------------|-------------------------------------|

| P00/INT4                   | Connect to Vss                      |

| P01/SCK                    | Connect to Vss or VDD               |

| P02/SO                     |                                     |

| P03/SI                     |                                     |

| P10/INT0 to P12/INT2       | Connect to Vss                      |

| P13/TI0                    |                                     |

| P20 to P22                 | Input state : Connect to Vss or VDD |

| P23/BUZ                    | Output state : Leave open           |

| P30 to P33                 |                                     |

| P40 to P43                 |                                     |

| P50 to P53                 |                                     |

| P60 to P63                 |                                     |

| PPO                        | Leave open                          |

| S0 to S9                   |                                     |

| T15/S10 to T14/S11         |                                     |

| T0 to T9                   |                                     |

| T10/S15/PH3 to T13/S12/PH0 |                                     |

| XT1                        | Connect to Vss or VDD               |

| XT2                        | Leave open                          |

| VLOAD when there is no on- | Connect to Vss or VDD               |

| chip load resistor         |                                     |

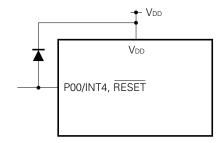

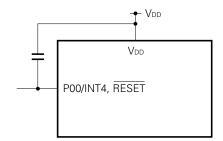

#### 3.5 NOTES ON USE OF THE P00/INT4 PIN AND RESET PIN

P00/INT4 and RESET pins have the function (especially for IC test) to test  $\mu$ PD75218 internal operations in addition to the functions described in **sections 3.1** and **3.2**.

The test mode is set when a voltage larger than VDD is applied to one of these pins. If noise larger than VDD is applied in normal operation, the test mode may be set thereby adversely affecting normal operation.

Since there is a display output pin having a high-voltage amplitude (35 V) next to the P00/INT4 and RESET pins, if cables for the related signals are routed in parallel, wiring noise larger than VDD may be applied to the P00/INT4 and RESET pins causing errors.

Thus, carry out wiring so that wiring noise can be minimized, If noise still cannot be suppressed, take the measure against noise using the following external components.

#### Connecting a diode between the pins and VDD

#### Connecting a capacitor between the pins and VDD

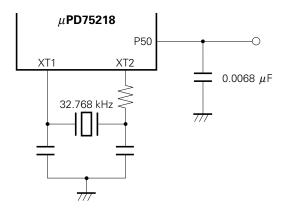

#### 3.6 NOTES ON USE OF THE XT1, XT2 AND P50 PIN

When selecting the 32.768 kHz subsystem clock connected to the XT1 and XT2 pins as the watch timer source clock, the signal to be input or output to the P50 pin next to the XT2 pin must be a signal required to be switched between high and low the minimum number of times (once/second or less).

If the P50 pin signal is switched frequently between high and low, a spike is generated in the XT2 pin because of capacitance coupling of the P50 and XT2 pins and the correct watch functions cannot be achieved (the watch becomes fast).

If it is necessary to allow the P50 pin signal to switch between high and low, mount an external capacitor to the P50 pin as shown below.

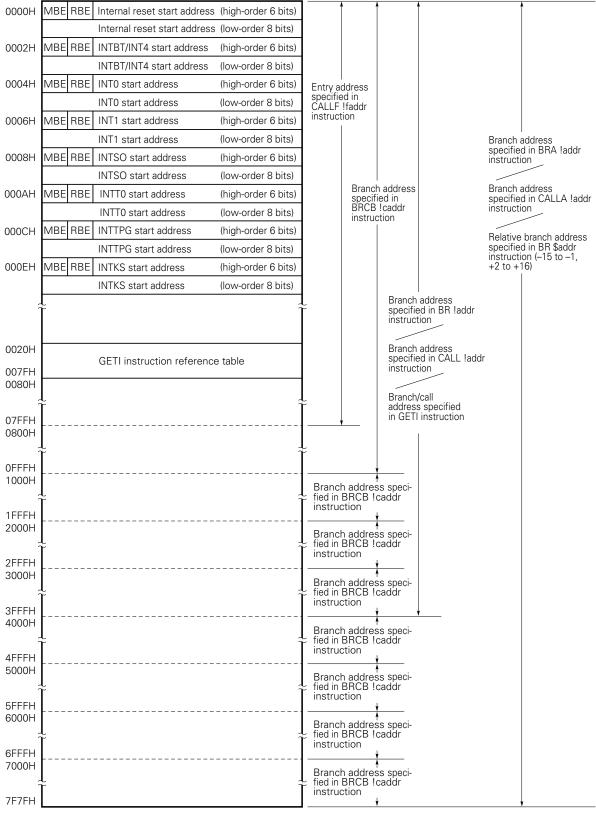

# 4. MEMORY CONFIGURATION

• Program memory (ROM): 32640 words × 8 bits

• 0000H and 0001H: Vector table which contains the program start address after reset

· 0002H to 000FH : Vector table which contains the program start addresses when interrupts occur

• 0020H to 007FH : Table area referenced by a GETI instruction

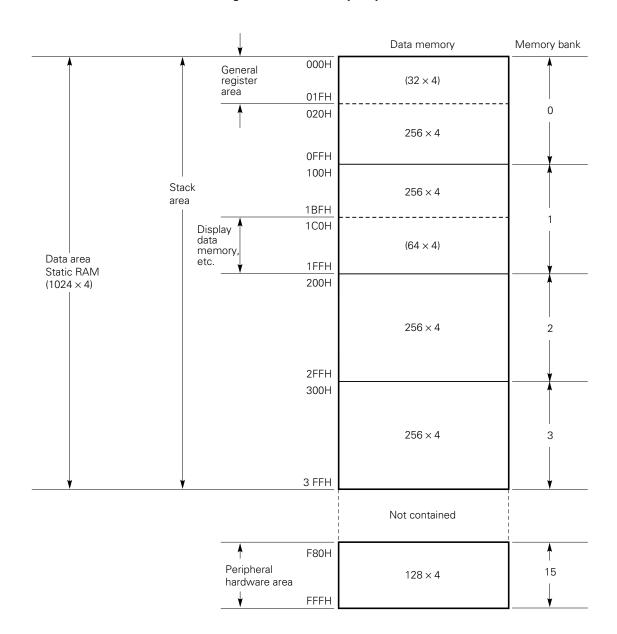

Data memory

• Data area :  $1024 \text{ words} \times 4 \text{ bits (000H to 3FFH)}$ • Peripheral hardware area:  $128 \text{ words} \times 4 \text{ bits (F80H to FFFH)}$

Fig. 4-1 Program Memory Map

Caution The start address of an interrupt vector shown above consists of 14 bits. So the start address must be set within a 16K-byte space (0000H to 3FFFH).

**Remark** In all cases other than those listed above, branch to the address with only the lower 8 bits of the PC changed is enabled by BR PCDE and BR PCXA instructions.

Fig. 4-2 Data Memory Map

# 5. PERIPHERAL HARDWARE FUNCTIONS

## 5.1 PORTS

The  $\mu$ PD75218 has the following three types of I/O port:

- 8 CMOS input pins (PORT0 and PORT1)

- 20 CMOS I/O pins (PORT2, PORT3, PORT4, PORT5, and PORT6)

- 4 P-ch open-drain output pins with high withstand voltage and high current (PORTH)

Total: 32 pins

**Table 5-1 Functions of Ports**

| Port                    | Function              | Operation and feature                                                                                                                                                          | Remarks                                    |

|-------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| PORT0                   | 4-bit input           | Always read or test possible irrespective of the dual-function pin operating mode.                                                                                             | Shares the pins with SI, SO, SCK and INT4. |

| PORT1                   |                       | Always read or test possible, P10 and P11 are inputs with the noise elimination function.                                                                                      | Shares the pins with INTO to INT2 and TIO. |

| PORT2<br>PORT4<br>PORT5 | 4-bit<br>input/output | Can be set to the input or output mode in 4-bit units.  Ports 4 and 5 can input/output data in pairs in 8-bit units.  Ports 4 and 5 can directly drive LEDs.                   | P23 shares the pin with BUZ.               |

| PORT3<br>PORT6          |                       | Can be set bit-wise to the input or output mode. Port 6 can incorporate a pull-down resistor by mask option.                                                                   |                                            |

| PORTH                   | 4-bit output          | P-ch open-drain output port with high withstand voltage and high current. Can drive an FIP and LED directly. Can incorporate a pull-down resistor in bit units by mask option. | Shares the pins with T10/S15 to T13/S12.   |

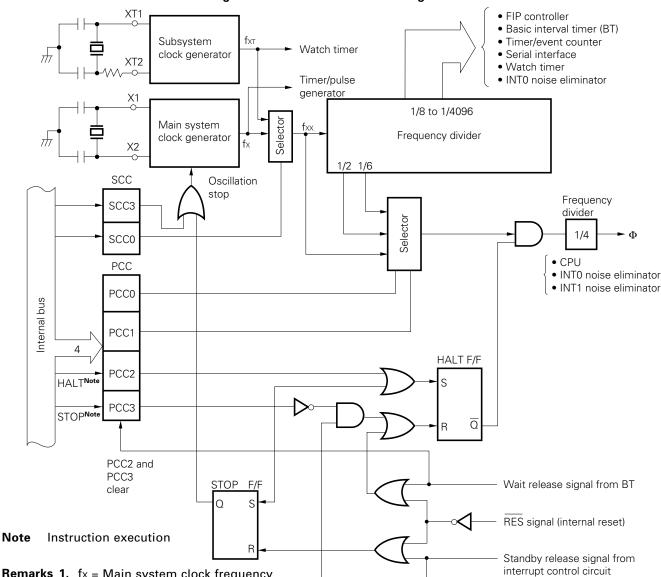

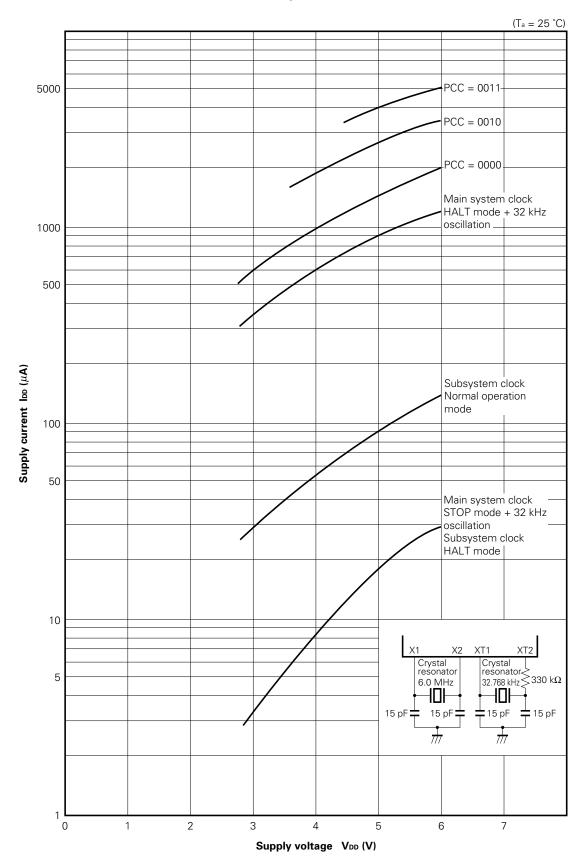

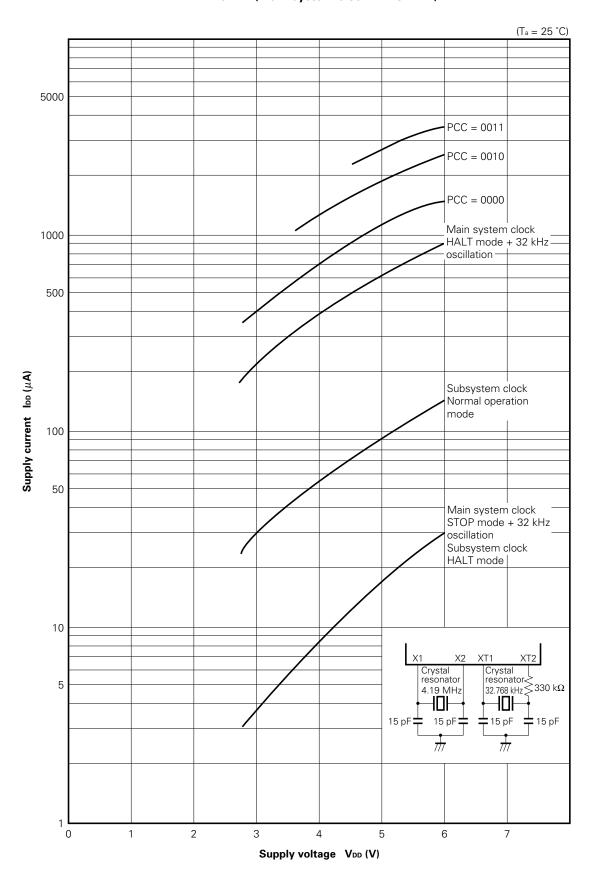

#### 5.2 CLOCK GENERATOR

Operation of the clock generator is specified by the processor clock control register (PCC) and system clock control register (SCC).

The main system clock or subsystem clock can be selected.

The instruction execution time is variable.

0.67  $\mu$ s, 1.33  $\mu$ s, 10.7  $\mu$ s (main system clock: 6.0 MHz) 0.95  $\mu$ s, 1.91  $\mu$ s, 15.3  $\mu$ s (main system clock: 4.19 MHz)

122  $\mu$ s (subsystem clock: 32.768 kHz)

Fig. 5-1 Clock Generator Block Diagram

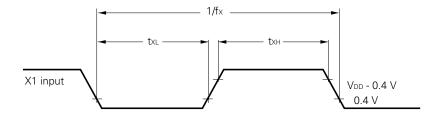

- **Remarks 1.** fx = Main system clock frequency

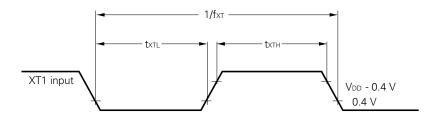

- 2. fxt = Subsystem clock frequency

- 3. fxx = System clock frequency

- 4.  $\Phi = CPU clock$

- 5. PCC: Processor clock control register

- 6. SCC: System clock control register

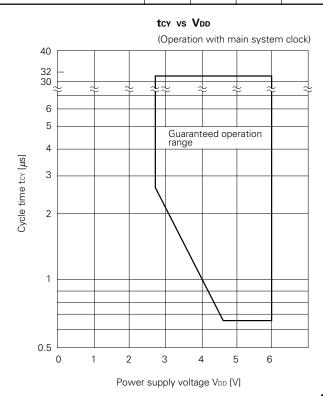

- 7. 1 clock cycle (tcy) of  $\Phi$  is 1 machine cycle of an instruction. For tcy, see "AC Characteristics" in Chapter 12.

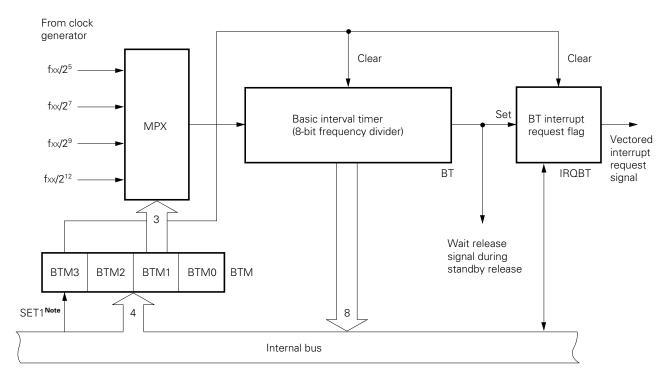

## 5.3 BASIC INTERVAL TIMER

The basic interval timer has the following functions:

- · Interval timer operation to generate reference time

- · Watchdog timer application to detect inadvertent program loop

- · Wait time select and count upon standby mode release

- · Count contents read

Fig. 5-2 Basic Interval Timer Configuration

Note Instruction execution

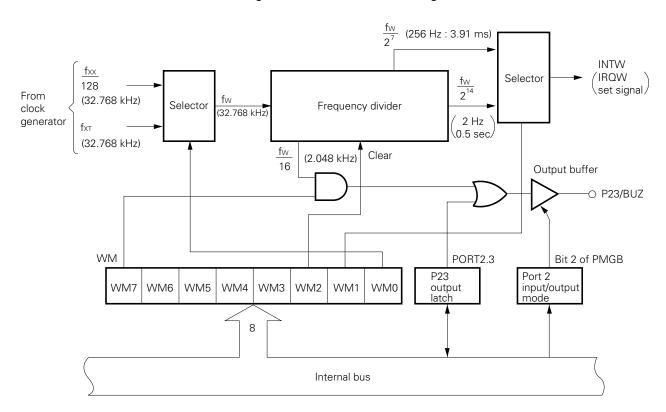

#### 5.4 WATCH TIMER

The  $\mu$ PD75218 incorporates one channel of watch timer. The watch timer has the following functions:

- Sets the test flag (IRQW) at 0.5 sec intervals.

The standby mode can be released by IRQW.

- 0.5 second interval can be set with the main system clock and subsystem clock.

- The fast mode enables to set 128-time (3.91 ms) interval useful to program debugging and inspection.

- The fixed frequencies (2.048 kHz) can be output to the P23/BUZ pin for use to generate buzzer sound and trim the system clock oscillator frequency.

- · Since the frequency divider can be cleared, the watch can be started from zero second.

Fig. 5-3 Watch Timer Block Diagram

**Remark** Values when fxx is 4.194304 MHz and fxT is 32.768 kHz are indicated in parentheses.

Caution When the main system clock operates at 6.0 MHz, a time interval of 0.5 second cannot be produced.

Before producing this time interval, the main system clock must be changed to the subsystem clock.

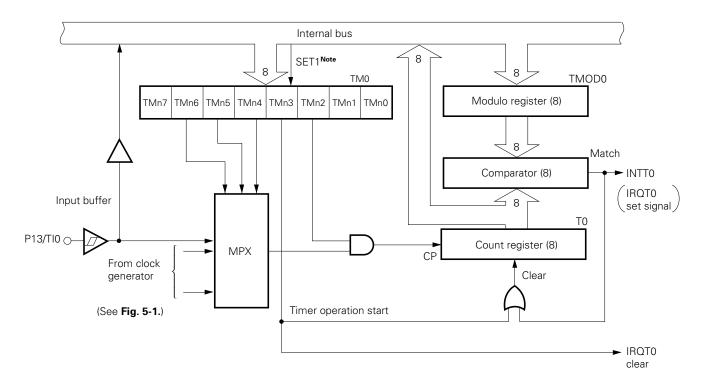

# 5.5 TIMER/EVENT COUNTER

The  $\mu$ PD75218 incorporates one channel of timer/event counter. The timer/event counter has the following functions:

- · Program interval timer operation

- · Event counter operation

- · Count state read function

Fig. 5-4 Timer/Event Counter Block Diagram

Note Instruction execution

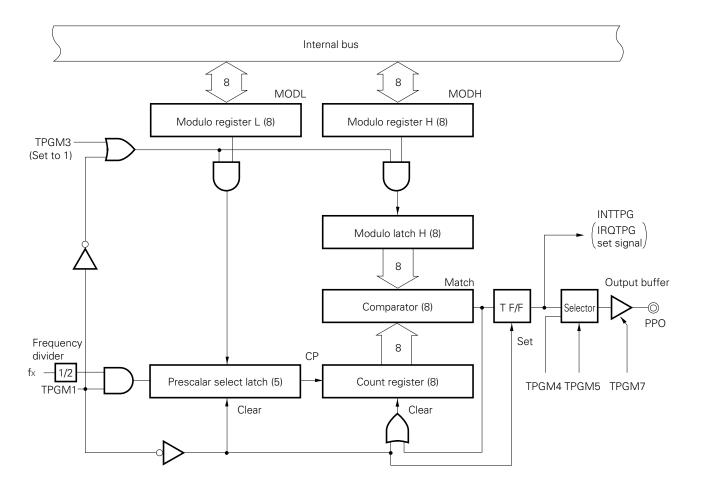

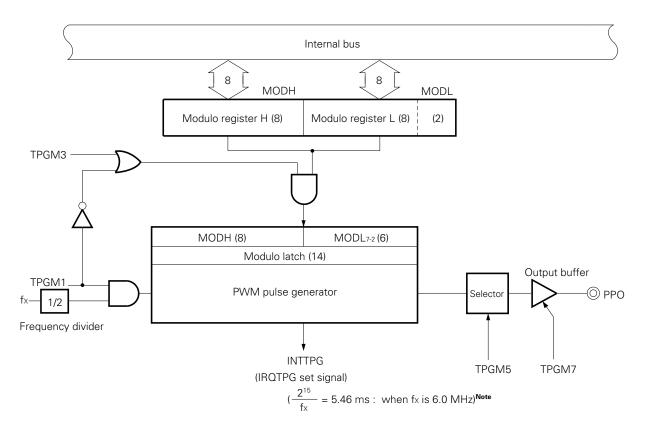

#### 5.6 TIMER/PULSE GENERATOR

The  $\mu$ PD75218 incorporates one channel of timer/pulse generator which can be used as a timer or a pulse generator. The timer/pulse generator has the following functions:

#### (a) Functions available in the timer mode

- 8-bit interval timer operation (IRQTPG generation) enabling the clock source to be varied at 5 levels

- · Square wave output to PPO pin

#### (b) Functions available in the PWM pulse generation mode

- 14-bit accuracy PWM pulse output to the PPO pin (Used as a digital-to-analog converter and applicable to tuning)

- Fixed time interval  $(\frac{2^{15}}{f_X} = 5.46 \text{ ms})$  when the microcomputer operates at 6.0 MHz) Note interrupt generation

If pulse output is not necessary, the PPO pin can be used as a 1-bit output port.

Note 7.81 ms when the microcomputer operates at 4.19 MHz

Caution If the STOP mode is set while the timer/pulse generator is in operation, erroneous operation may result.

To prevent that from occurring, preset the timer/pulse generator to the stop state using its mode register.

Fig. 5-5 Block Diagram of Timer/Pulse Generator (Timer Mode)

Fig. 5-6 Timer/Pulse Generator Block Diagram (PWM Pulse Generation Mode)

Note 7.81 ms when the microcomputer operates at 4.19 MHz.

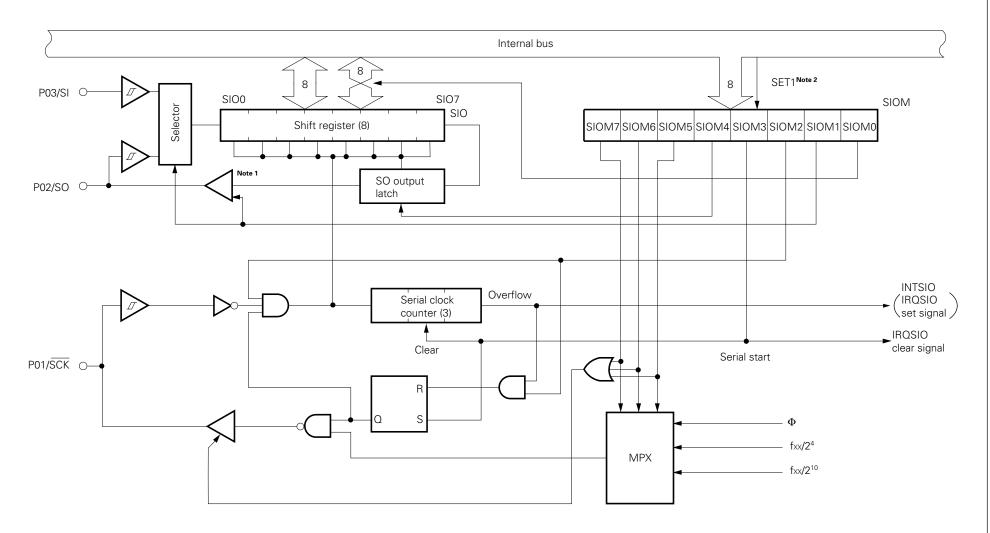

## 5.7 SERIAL INTERFACE

The serial interface has the following functions:

- Clock synchronous 8-bit send/receive operation (simultaneous send/receive)

- · Clock synchronous 8-bit serial bus operation (data input/output from the SO pin. N-ch open-drain SO output)

- · Start LSB/MSB switching

These functions facilitate data communication with another microcomputer of  $\mu$ PD7500 series or 78K series via a serial bus and coupling with peripheral devices.

Fig 5-7 Serial Interface Block Diagram

- Notes 1. CMOS output and N-ch open-drain output switchable output buffer.

- 2. Instruction execution

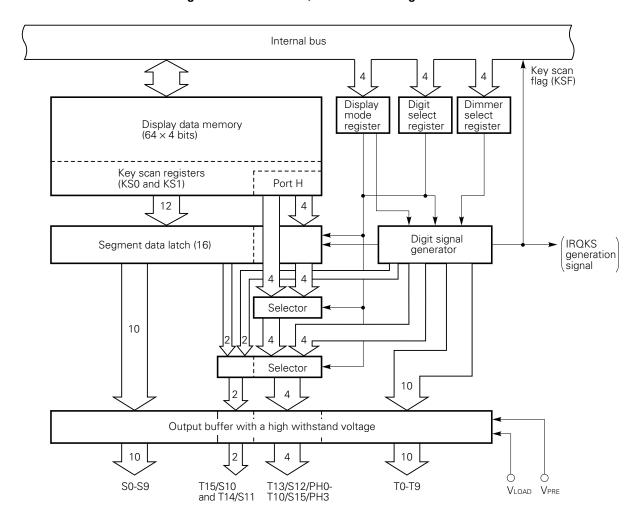

#### 5.8 FIP CONTROLLER/DRIVER

The FIP controller/driver in the  $\mu$ PD75218 has the same functions as that in its predecessor,  $\mu$ PD75216A:

- The FIP controller/driver outputs the segment signal by automatically reading display data (DMA operation) and automatically generates the digit signal.

- The FIP controller/driver can control the FIP of 9 to 16 segments and 9 to 16 digits with the display mode register (DSPM) and the digit select register (DIGS) (within the range of up to 26 display outputs).

- The display outputs unused for dynamic display can be used as static outputs.

- · The dimmer function provides eight levels of intensity.

- Such hardware is contained that a key scan application is possible.

- A key scan interrupt (IRQKS) is caused. (A key scan timing is detected.)

- Key scan data can be output from key scan registers (KS0 and KS1) onto a segment output pin.

- A high-voltage output pin (40 V) is provided which can directly drive the FIP.

- Pins dedicated to segments (S0 to S9): VoD = 40 V, IoD = 3 mA

- Digit output pins (T0 to T15): VoD = 40 V, loD = 15 mA

- · A mask option enables a pull-down resistor to be incorporated for each bit.

Fig. 5-8 FIP Controller/Driver Block Diagram

Caution The FIP controller/driver can only operate at the high and intermediate speeds (PCC = 0011B or 0010B) of the main system clock (SCC.0 = 0). It may cause errors with any other clock or in the standby mode. Thus, be sure to stop FIP controller operation (DSPM.3 = 0) and then shift the unit to any other clock mode or the standby mode.

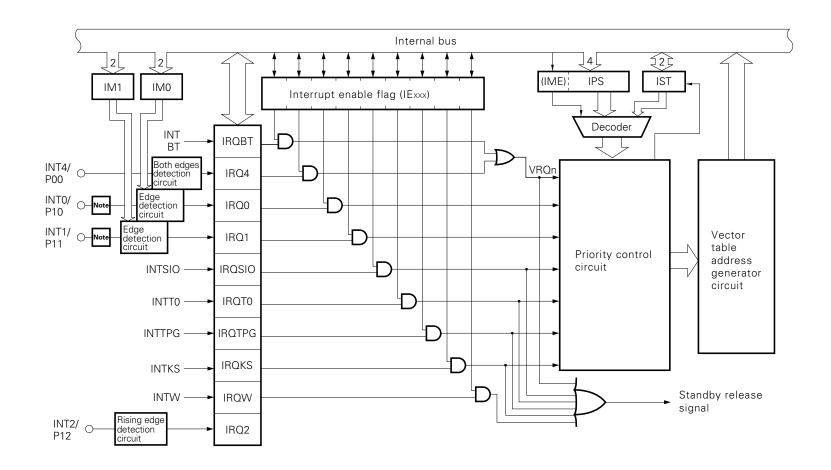

#### 6. INTERRUPT FUNCTIONS

The  $\mu$ PD75218 has eight types of interrupt sources and can generate multiple interrupts with priority order. It is also equipped with two types of test sources. INT2 is an edge detected testable input. The  $\mu$ PD75218 interrupt control circuit has the following functions:

- Hardware-controlled vectored interrupt function which can control interrupt acknowledge with the interrupt enable flag (IExxx) and the interrupt master enable flag (IME).

- · Function of setting any interrupt start address.

- Multiple interrupt function which can specify priority order with the interrupt priority select register (IPS).

- Interrupt request flag (IRQxxx) test function. (Interrupt generation can be checked by software.)

- · Standby mode release function (Interrupts to be released can be selected by interrupt enable flags.)

Fig. 6-1 Interrupt Control Circuit Block Diagram

Note Noise eliminator

# 7. STANDBY FUNCTIONS

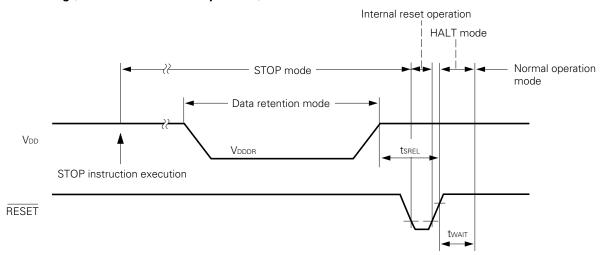

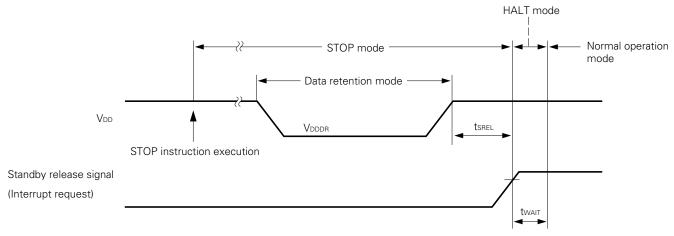

Two standby modes (STOP mode and HALT mode) are available for the  $\mu$ PD75218 to decrease power consumption in the program standby mode.

Table 7-1 Operation Status in Standby Mode

|                                                                                                                                                   |                       | STOP mode                                                                   | HALT mode                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|

| Set                                                                                                                                               | instruction           | STOP instruction                                                            | HALT instruction                                                                |

| Sys                                                                                                                                               | tem clock when set    | Setting enabled only for main system clock                                  | Setting enabled for either main system clock or subsystem clock                 |

|                                                                                                                                                   | Clock oscillator      | Oscillator stops only for main system clock                                 | Stops only for CPU clock $\Phi$ (oscillation continued)                         |

|                                                                                                                                                   | Basic interval timer  | Operation stopped                                                           | Operation continued (IRQBT set at reference time intervals)                     |

| State                                                                                                                                             | Serial interface      | Operation enabled only when external SCK input is selected for serial clock | Operation enabled when serial clock other than $\boldsymbol{\Phi}$ is specified |

| Operating (                                                                                                                                       | Timer/event counter   | Operation enabled only when TI0 pin input is specified for count clock      | Operation enabled                                                               |

| ďO                                                                                                                                                | Timer/pulse generator | Operation stopped                                                           | Operation enabled                                                               |

|                                                                                                                                                   | Watch timer           | Operation enabled only fxT is selected for count clock                      | Operation enabled                                                               |

|                                                                                                                                                   | FIP controller/driver | Operation disabled (display off mode set                                    | before disabling)                                                               |

|                                                                                                                                                   | CPU                   | Operation stopped                                                           |                                                                                 |

| Release signal  Interrupt request signals (except INT0, INT1, and INT2) from operable hardvent enabled by interrupt enable flags, or RESET input. |                       | ` ·                                                                         |                                                                                 |

# 8. RESET FUNCTIONS

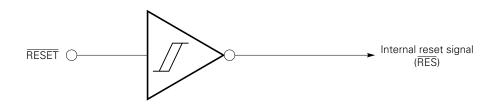

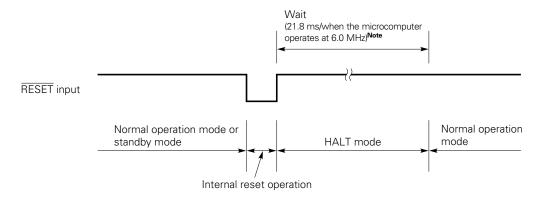

The reset signal (RES) generator has a configuration shown in Fig. 8-1.

Fig. 8-1 Reset Signal Generator

Fig. 8-2 shows the reset operation.

Fig. 8-2 Reset Operation by RESET Input

Note 31.3 ms when the microcomputer operates at 4.19 MHz

Table 8-1 lists the hardware statuses after reset operation.

Table 8-1 Hardware Statuses after Reset Operation

| Hardware    |                       |                                        | RESET input in standby mode                                                                                                                                                      | RESET input during operation                                                                                                                                                     |

|-------------|-----------------------|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                       |                                        | Set the low-order six bits at address 0000H in program memory to PC <sub>13-8</sub> , set the contents of address 0001H to PC <sub>7-0</sub> , and set PC <sub>14</sub> to zero. | Set the low-order six bits at address 0000H in program memory to PC <sub>13-8</sub> , set the contents of address 0001H to PC <sub>7-0</sub> , and set PC <sub>14</sub> to zero. |

| PSW Ca      | PSW   Carry flag (CY) |                                        | Retained                                                                                                                                                                         | Undefined                                                                                                                                                                        |

| Ski         | ip flag (SK0          | -SK2)                                  | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

| Inte        | errupt statu          | s flag (IST0, IST1)                    | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

| Ba          | nk enable fl          | ag (MBE, RBE)                          | Set bit 6 of address 0000H in program memory to RBE and set bit 7 to MBE.                                                                                                        | Set bit 6 of address 0000H in program memory to RBE and set bit 7 to MBE.                                                                                                        |

| Stack poir  | nter (SP)             |                                        | Undefined                                                                                                                                                                        | Undefined                                                                                                                                                                        |

| Stack ban   | k selection           | register (SBS)                         | Undefined                                                                                                                                                                        | Undefined                                                                                                                                                                        |

| Data mem    | nory (RAM)            |                                        | Retained <sup>Note</sup>                                                                                                                                                         | Undefined                                                                                                                                                                        |

| General re  | egister (X, A         | A, H, L, D, E, B, C)                   | Retained                                                                                                                                                                         | Undefined                                                                                                                                                                        |

| Bank sele   | ction registe         | er (MBS, RBS)                          | 0, 0                                                                                                                                                                             | 0, 0                                                                                                                                                                             |

| Basic inte  | rval timer            | Counter (BT)                           | Undefined                                                                                                                                                                        | Undefined                                                                                                                                                                        |

|             |                       | Mode register (BTM)                    | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

| Timer/eve   | ent counter           | Counter (T0)                           | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

|             |                       | Modulo register (TMOD0)                | FFH                                                                                                                                                                              | FFH                                                                                                                                                                              |

|             |                       | Mode register (TM0)                    | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

| Timer/pulse |                       | Modulo register (MODH, MODL)           | Retained                                                                                                                                                                         | Undefined                                                                                                                                                                        |

| generator   | •                     | Mode register (TPGM)                   | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

| Clock timer |                       | Mode register (WM)                     | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

| Serial inte | erface                | Shift register (SIO)                   | Retained                                                                                                                                                                         | Undefined                                                                                                                                                                        |

|             |                       | Mode register (SIOM)                   | Set bit 4 to 1 and other bits to 0.                                                                                                                                              | Set bit 4 to 1 and other bits to 0                                                                                                                                               |

| Clock gen   | erator                | Processor clock control register (PCC) | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

|             |                       | System clock control register (SCC)    | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

| Interrupt   |                       | Interrupt request flag (IRQxxx)        | Reset (0)                                                                                                                                                                        | Reset (0)                                                                                                                                                                        |

|             |                       | Interrupt enable flag (IExxx)          | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

|             |                       | Priority specification flag (IPS)      | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

|             |                       | INT0/INT1 mode register (IM0, IM1)     | 0, 0                                                                                                                                                                             | 0, 0                                                                                                                                                                             |

| Digital po  | rt                    | Output buffer                          | Off                                                                                                                                                                              | Off                                                                                                                                                                              |

|             |                       | Output latch                           | Cleared (0)                                                                                                                                                                      | Cleared (0)                                                                                                                                                                      |

|             |                       | I/O mode register (PMGA, PMGB)         | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

| PORT H      |                       | Output latch                           | Retained                                                                                                                                                                         | Undefined                                                                                                                                                                        |

| FIP contro  | oller/driver          | Display mode register (DSPM)           | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

|             |                       | Digit selection register (DIGS)        | 1000B                                                                                                                                                                            | 1000B                                                                                                                                                                            |

|             |                       | Dimmer selection register (DIMS)       | 0                                                                                                                                                                                | 0                                                                                                                                                                                |

|             |                       | Display data memory                    | Retained                                                                                                                                                                         | Undefined                                                                                                                                                                        |

|             |                       | Output buffer                          | Off                                                                                                                                                                              | Off                                                                                                                                                                              |

Note Data from address 0F8H to address 0FDH in the data memory becomes undefined by RESET input.

## 9. INSTRUCTION SET

#### (1) Representation format and description method of operands

An operand is described in the operand field of each instruction according to the description method corresponding to the operand representation format of the instruction (refer to "RA75X Assembler Package User's Manual, Language" (EEU-1363) for details). When two or more elements are described in the description method field, select one of them. Uppercase letters, a plus sign (+), and a minus sign (-) are keywords, so they can be used without alteration.

Specify an appropriate numeric value or label for immediate data.

| Representa-<br>tion format | Description method                                 |  |

|----------------------------|----------------------------------------------------|--|

| reg                        | X, A, B, C, D, E, H, L                             |  |

| reg1                       | X, B, C, D, E, H, L                                |  |

| rp                         | XA, BC, DE, HL                                     |  |

| rp1                        | BC, DE, HL                                         |  |

| rp2                        | BC, DE                                             |  |

| rp'                        | XA, BC, DE, HL, XA', BC', DE', HL'                 |  |

| rp'1                       | BC, DE, HL, XA', BC', DE', HL'                     |  |

| rpa                        | HL, HL+, HL-, DE, DL                               |  |

| rpa1                       | DE, DL                                             |  |

| n4                         | 4-bit immediate data or label                      |  |

| n8                         | 8-bit immediate data or label                      |  |

| mem                        | 8-bit immediate data or label <sup>Note</sup>      |  |

| bit                        | 2-bit immediate data or label                      |  |

| fmem                       | FB0H-FBFH/FF0H-FFFH immediate data or label        |  |

| pmem                       | FC0H-FFFH immediate data or label                  |  |

| addr1                      | 0000H-7F7FH immediate data or label                |  |

| addr                       | 0000H-3F7FH immediate data or label                |  |

| caddr                      | 12-bit immediate data or label                     |  |

| faddr                      | 11-bit immediate data or label                     |  |

| taddr                      | 20H-7FH immediate data (bit 0 = 0) or label        |  |

| PORTn                      | PORT0-PORT6                                        |  |

| IExxx                      | IEBT, IESIO, IET0, IETPG, IE0, IE1, IEKS, IEW, IE4 |  |

| RBn                        | RB0-RB3                                            |  |

| MBn                        | MB0, MB1, MB2, MB3, MB15                           |  |

Note Only even addresses can be specified for 8-bit data processing.

#### (2) Legend

Α : A register, 4-bit accumulator В : B register, 4-bit accumulator С : C register, 4-bit accumulator D : D register, 4-bit accumulator Ε : E register, 4-bit accumulator Н : H register, 4-bit accumulator L : L register, 4-bit accumulator Χ : X register, 4-bit accumulator

XA : Register pair (XA), 8-bit accumulator

BC : Register pair (BC), 8-bit accumulator

DE : Register pair (DE), 8-bit accumulator

HL : Register pair (HL), 8-bit accumulator

XA' : Extended register pair (XA')

BC' : Extended register pair (BC')

DE' : Extended register pair (DE')

HL' : Extended register pair (HL')

PC : Program counter SP : Stack pointer

CY : Carry flag, bit accumulatorPSW : Program status wordMBE : Memory bank enable flagRBE : Register bank enable flag

PORTn: Port n (n = 0 to 6)

IME : Interrupt master enable flag

IPS : Interrupt priority specification register

IExxx : Interrupt enable flag

RBS : Register bank select register

MBS : Memory bank select register

PCC : Processor clock control register

: Address/bit delimiter(xx): Contents addressed by xx

××H : Hexadecimal data

## (3) Explanation of the symbols in the addressing area field

| *1  | MB = MBE•MBS                                           | <b> </b>               |

|-----|--------------------------------------------------------|------------------------|

|     | (MBS = 0, 1, 2, 3, or 15)                              |                        |

| *2  | MB = 0                                                 |                        |

| *3  | MBE = 0: MB = 0 (00H-7FH)                              | Data maman             |

|     | MB = 15 (80H-FFH)                                      | Data memory addressing |

|     | MBE = 1: MB = MBS (MBS = 0, 1, 2, 3, or 15)            | addressing             |

| *4  | MB = 15, fmem = FB0H-FBFH or                           |                        |

|     | FF0H-FFFH                                              |                        |

| *5  | MB = 15, pmem = FC0H-FFFH                              | <b> </b>               |

| *6  | addr = 0000H-3F7FH                                     | <b>A</b>               |

| *7  | addr = (Current PC) - 15 to (Current PC) - 1 or        |                        |

|     | (Current PC) + 2 to (Current PC) + 16                  |                        |

| *8  | caddr = 0000H-0FFFH (PC <sub>14,13,12</sub> = 000B) or |                        |

|     | 1000H-1FFFH (PC <sub>14,13,12</sub> = 001B) or         |                        |

|     | 2000H-2FFFH (PC <sub>14,13,12</sub> = 010B) or         | Program                |

|     | 3000H-3FFFH (PC <sub>14,13,12</sub> = 011B) or         | memory                 |

|     | 4000H-4FFFH (PC <sub>14,13,12</sub> = 100B) or         | addressing             |

|     | 5000H-5FFFH (PC <sub>14,13,12</sub> = 101B) or         |                        |

|     | $6000H-6FFFH (PC_{14,13,12} = 110B) \text{ or}$        |                        |

|     | 7000H-7F7FH (PC <sub>14,13,12</sub> = 111B)            |                        |

| *9  | faddr = 0000H-07FFH                                    |                        |

| *10 | taddr = 0020H-007FH                                    |                        |

| *11 | addr1 = 0000H-7F7FH                                    | <b></b>                |

Remarks 1. MB indicates an accessible memory bank.

- 2. For \*2, MB is always 0 irrespective of MBE and MBS.

- 3. For \*4 and \*5, MB is always 15 irrespective of MBE and MBS.

- 4. \*6 to \*11 indicate each addressable area.

## (4) Explanation of the machine cycle column

S represents the number of machine cycles required when a skip instruction with the skip function performs a skip operation. S assumes one of the following values:

• When no skip operation is performed : S = 0

• When a 1-byte instruction or 2-byte instruction is skipped: S = 1

• When a 3-byte instruction is skipped : S = 2

# Caution The GETI instruction is skipped in one machine cycle.

One machine cycle is equal to one cycle of the CPU clock  $\Phi$  (= tcy), and three types of times are available for selection according to the PCC setting.

| Instruction | Mnemonic | Operand   | Number of bytes | Machine cycle | Operation                                           | Address-<br>ing area | Skip<br>condition |

|-------------|----------|-----------|-----------------|---------------|-----------------------------------------------------|----------------------|-------------------|

| Transfer    | MOV      | A,#n4     | 1               | 1             | A ← n4                                              |                      | String effect A   |

|             |          | reg1,#n4  | 2               | 2             | reg1 ← n4                                           |                      |                   |

|             |          | XA,#n8    | 2               | 2             | XA ← n8                                             |                      | String effect A   |

|             |          | HL,#n8    | 2               | 2             | HL ← n8                                             |                      | String effect B   |

|             |          | rp2,#n8   | 2               | 2             | rp2 ← n8                                            |                      |                   |

|             |          | A,@HL     | 1               | 1             | $A \leftarrow (HL)$                                 | *1                   |                   |

|             |          | A,@HL+    | 1               | 2 + S         | $A \leftarrow (HL)$ , then $L \leftarrow L + 1$     | *1                   | L = 0             |

|             |          | A,@HL-    | 1               | 2 + S         | $A \leftarrow$ (HL), then $L \leftarrow L - 1$      | *1                   | L = FH            |

|             |          | A,@rpa1   | 1               | 1             | A ← (rpa1)                                          | *2                   |                   |

|             |          | XA,@HL    | 2               | 2             | $XA \leftarrow (HL)$                                | *1                   |                   |

|             |          | @HL,A     | 1               | 1             | (HL) ← A                                            | *1                   |                   |

|             |          | @HL,XA    | 2               | 2             | (HL) ← XA                                           | *1                   |                   |

|             |          | A,mem     | 2               | 2             | A ← (mem)                                           | *3                   |                   |

|             |          | XA,mem    | 2               | 2             | XA ← (mem)                                          | *3                   |                   |

|             |          | mem,A     | 2               | 2             | (mem) ← A                                           | *3                   |                   |

|             |          | mem,XA    | 2               | 2             | (mem) ← XA                                          | *3                   |                   |

|             |          | A,reg     | 2               | 2             | $A \leftarrow reg$                                  |                      |                   |

|             |          | XA,rp'    | 2               | 2             | $XA \leftarrow rp'$                                 |                      |                   |

|             |          | reg1,A    | 2               | 2             | reg1 ← A                                            |                      |                   |

|             |          | rp'1,XA   | 2               | 2             | rp′1 ← XA                                           |                      |                   |

|             | XCH      | A,@HL     | 1               | 1             | $A \leftrightarrow (HL)$                            | *1                   |                   |

|             |          | A,@HL+    | 1               | 2 + S         | $A \leftrightarrow$ (HL), then L $\leftarrow$ L + 1 | *1                   | L = 0             |

|             |          | A,@HL-    | 1               | 2 + S         | A $\leftrightarrow$ (HL), then L $\leftarrow$ L - 1 | *1                   | L = FH            |

|             |          | A,@rpa1   | 1               | 1             | $A \leftrightarrow (rpa1)$                          | *2                   |                   |

|             |          | XA,@HL    | 2               | 2             | $XA \leftrightarrow (HL)$                           | *1                   |                   |

|             |          | A,mem     | 2               | 2             | $A \leftrightarrow (mem)$                           | *3                   |                   |

|             |          | XA,mem    | 2               | 2             | $XA \leftrightarrow (mem)$                          | *3                   |                   |

|             |          | A,reg1    | 1               | 1             | $A \leftrightarrow reg1$                            |                      |                   |

|             |          | XA,rp'    | 2               | 2             | $XA \leftrightarrow rp'$                            |                      |                   |

| Table       | MOVT     | XA,@PCDE  | 1               | 3             | XA ← (PC <sub>14-8</sub> +DE) <sub>ROM</sub>        |                      |                   |

| reference   |          | XA,@PCXA  | 1               | 3             | $XA \leftarrow (PC_{14-8} + XA)_{ROM}$              |                      |                   |

|             |          | XA, @BCDE | 1               | 3             | XA ← (BCDE)ROM                                      | *11                  |                   |

|             |          | XA, @BCXA | 1               | 3             | $XA \leftarrow (BCXA)_{ROM}$                        | *11                  |                   |