# Regarding the change of names mentioned in the document, such as Hitachi Electric and Hitachi XX, to Renesas Technology Corp.

The semiconductor operations of Mitsubishi Electric and Hitachi were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Hitachi, Hitachi, Ltd., Hitachi Semiconductors, and other Hitachi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Renesas Technology Home Page: http://www.renesas.com

Renesas Technology Corp. Customer Support Dept. April 1, 2003

#### Cautions

Keep safety first in your circuit designs!

1. Renesas Technology Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage.

Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of nonflammable material or (iii) prevention against any malfunction or mishap.

Notes regarding these materials

- These materials are intended as a reference to assist our customers in the selection of the Renesas Technology Corporation

product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any

other rights, belonging to Renesas Technology Corporation or a third party.

- 2. Renesas Technology Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- 3. All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Renesas Technology Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors.

Renesas Technology Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Renesas Technology Corporation by various means, including the Renesas Technology Corporation Semiconductor home page (http://www.renesas.com).

- 4. When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Renesas Technology Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- 5. Renesas Technology Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Renesas Technology Corporation or an authorized Renesas Technology Corporation product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- 6. The prior written approval of Renesas Technology Corporation is necessary to reprint or reproduce in whole or in part these materials.

- If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination. Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

- 8. Please contact Renesas Technology Corporation for further details on these materials or the products contained therein.

## AS Microcomputer Incorporating a DTMF Generator Circuit

## RENESAS

ADE-202-048D Rev.5.0 Sept. 1999

### Description

The HD404629R Series is part of the HMCS400-Series microcomputers designed to increase program productivity and also incorporate large-capacity memory. Each microcomputer has a high precision dual-tone multifrequency (DTMF) generator, LCD controller/driver, A/D converter, input capture circuit, 32-kHz oscillator for clock, and four low-power dissipation modes.

The HD404629R Series includes four chips: the HD404628R with 8-kword ROM; the HD4046212R with 12-kword ROM; the HD404629R with 16-kword ROM; the HD4074629 with 16-kword PROM.

A program can be written to the PROM by a PROM writer, which can dramatically shorten system development periods and smooth the process from debugging to mass production.

#### Features

- 1,876-digit × 4-bit RAM

- 44 I/O pins, including 10 high-current pins (15 mA, max.) and 20 pins multiplexed with LCD segment pins

5

- Four timer/counters

- 8-bit input capture circuit

- Three timer outputs (including two PWM out-puts)

- Two event counter inputs (including one double-edge function)

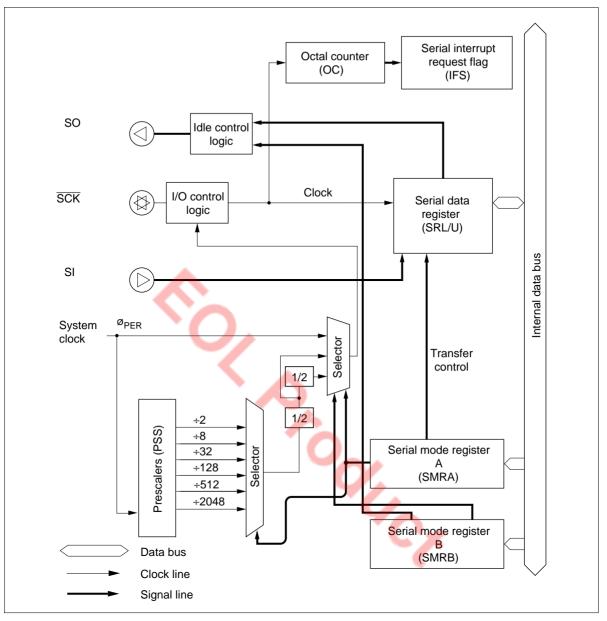

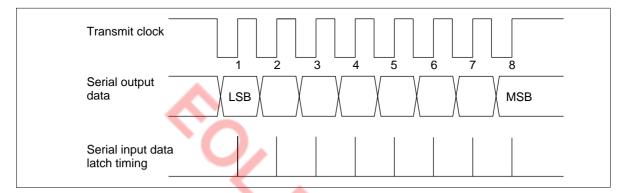

- Clock-synchronous 8-bit serial interface

- A/D converter (4 channels × 8 bits)

- LCD controller/driver (52 segments × 4 commons)

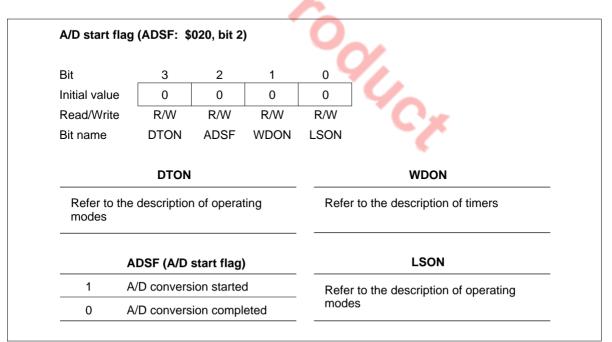

- On-chip DTMF generator

- Built-in oscillators

- Main clock: 4-MHz ceramic (an external clock is also possible)

- Subclock: 32.768-kHz crystal

- Eleven interrupt sources

- Five by external sources, including three double-edge functions

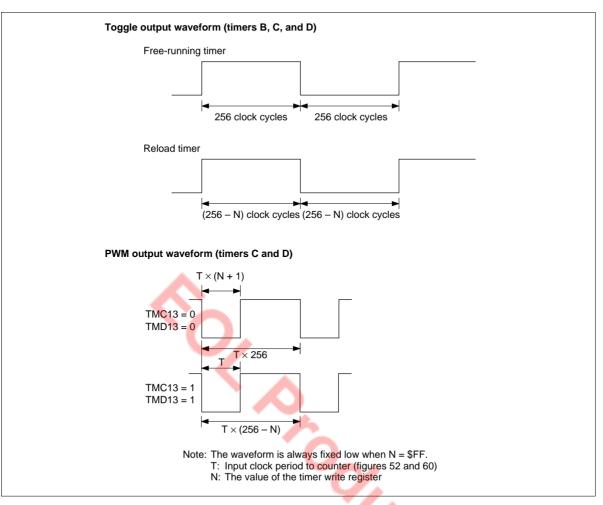

- Six by internal sources

- Subroutine stack up to 16 levels, including interrupts

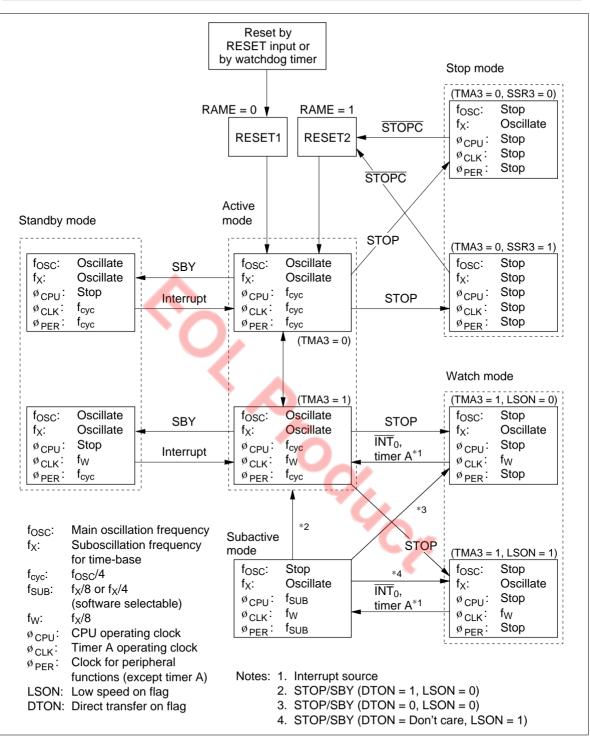

- Four low-power dissipation modes

- Subactive mode

- Standby mode

- Watch mode

- Stop mode

- One external input for transition from stop mode to active mode .

- Instruction cycle time (min.): 1  $\mu$ s (f<sub>OSC</sub> = 4 MHz)

- Operation voltage •

$V_{CC} = 2.7 \text{ V}$  to 6.0 V (HD404629R)

V<sub>CC</sub> = 2.7 V to 5.5 V (HD4074629)

- Two operating modes •

- MCU mode

- MCU/PROM mode (HD4074629 only)

J4074.

| Туре              | Product Name | Model Name   | ROM (Words) | Package                            |

|-------------------|--------------|--------------|-------------|------------------------------------|

| Mask ROM          | HD404628R    | HD404628RH   | 8,192       | 100-pin plastic QFP<br>(FP-100B)   |

|                   |              | HD404628RFS  | _           | 100-pin plastic QFP<br>(FP-100A)   |

|                   |              | HD404628RTF  | _           | 100-pin plastic TQFP<br>(TFP-100B) |

|                   | HD4046212R   | HD4046212RH  | 12,288      | 100-pin plastic QFP<br>(FP-100B)   |

|                   |              | HD4046212RFS | _           | 100-pin plastic QFP<br>(FP-100A)   |

|                   |              | HD4046212RTF | _           | 100-pin plastic TQFP<br>(TFP-100B) |

|                   | HD404629R    | HD404629RH   | 16,384      | 100-pin plastic QFP<br>(FP-100B)   |

|                   |              | HD404629RFS  | _           | 100-pin plastic QFP<br>(FP-100A)   |

|                   |              | HD404629RTF  | _           | 100-pin plastic TQFP<br>(TFP-100B) |

| ZTAT <sup>™</sup> | HD4074629    | HD4074629H   | 16,384      | 100-pin plastic QFP<br>(FP-100B)   |

|                   |              | HD4074629FS  | 0,          | 100-pin plastic QFP<br>(FP-100A)   |

|                   |              | HD4074629TF  | 40          | 100-pin plastic TQFP<br>(TFP-100B) |

#### **Ordering Information**

#### **Cautions about operaton!**

Like the ZTAT<sup>TM</sup> HD4074629 and the HD404629 Series, the HD404629R Series has been verified to fully meet the standard electrical characteristics described in the data sheet or other related documents. However, due to differences in the manufacturing process, the type of built-in ROMs used, and internal wiring patterns, the HD404629R Series has different power factors, operating margins, and noise margins.

Therefore, you should test both of your systems incorporating the  $ZTAT^{TM}$  and mask ROM versions. When your system is modified to use an HD404629R Series in place of a conventional chip, you should also perform a similar evaluation test to verify performance of your new system.

## List of Functions

| Product name           | Product name         |                                  | HD4046212R          | HD404629R | HD4074629   |  |  |  |

|------------------------|----------------------|----------------------------------|---------------------|-----------|-------------|--|--|--|

| ROM (Words)            |                      | 8,192                            | 12,288              | 16,384    | 16,384 PROM |  |  |  |

| RAM (Digits)           |                      | 1,876                            | 1,876               |           |             |  |  |  |

| I/O                    | I/O                  |                                  |                     |           |             |  |  |  |

| Large-curre            | ent I/O pins         | 10 (Sink 15 mA                   | ( max)              |           |             |  |  |  |

| LCD segme              | ent multiplexed pins | 20                               |                     |           |             |  |  |  |

| Timer / Counter        |                      | 4                                |                     |           |             |  |  |  |

| Input captu            | ire                  | 8 bit × 1                        |                     |           |             |  |  |  |

| Timer outp             | ut                   | 3 (PWM output                    | possible for 2)     |           |             |  |  |  |

| Event input            | t                    | 2 (edge selecti                  | on possible for 1)  |           |             |  |  |  |

| Serial interface       |                      | 1 (8-bit syncror                 | nous)               |           |             |  |  |  |

| DTMF generation        | on circuit           | Available                        |                     |           |             |  |  |  |

| A/D converter          |                      | 8 bit × 4 chann                  | 8 bit × 4 channels  |           |             |  |  |  |

| LCD controller /       | driver circuit       | Max. 52 seg $	imes$              | Max. 52 seg × 4 com |           |             |  |  |  |

| Interrupts             | External             | 5 (edge selecti                  | on possible for 3)  |           |             |  |  |  |

|                        | Internal             | 6                                |                     |           |             |  |  |  |

| Low-Power Diss         | sipation Mode        | 4                                |                     |           |             |  |  |  |

| Stop mode              |                      | Available                        |                     |           |             |  |  |  |

| Watch mod              | le                   | Available                        |                     |           |             |  |  |  |

| Standby m              | ode                  | Available                        |                     |           |             |  |  |  |

| Subactive I            | mode                 | Available                        |                     |           |             |  |  |  |

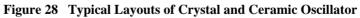

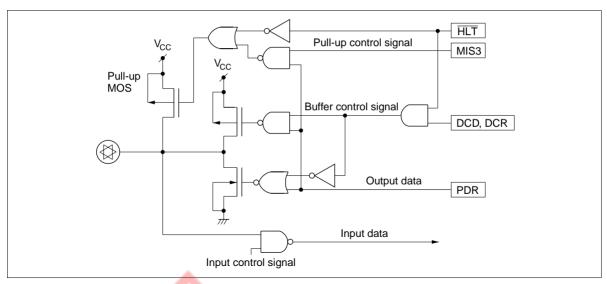

| Main Oscillator        | Ceramic oscillation  | 400 kHz, 800 k                   | Hz, 2 MHz, 4 MH     | Z         |             |  |  |  |

|                        | Crystal oscillation  | 400 kHz, 800 kHz, 2 MHz, 4 MHz — |                     |           |             |  |  |  |

| Sub oscillator         | Crystal oscillation  | 32.768 kHz                       |                     |           |             |  |  |  |

| Minimum instruc        | ction execution time | 1 μs (f <sub>OSC</sub> = 4 MHz)  |                     |           |             |  |  |  |

| Operating voltag       | ge (V)               | 2.7 to 6.0 2.7 to 5.5            |                     |           |             |  |  |  |

| Package                |                      | 100-pin plastic                  | QFP (FP-100B)       |           |             |  |  |  |

|                        |                      | 100-pin plastic                  | QFP (FP-100A)       |           |             |  |  |  |

|                        |                      | 100-pin plastic TQFP (TFP-100B)  |                     |           |             |  |  |  |

| Guaranteed ope<br>(°C) | eration temperature  | -20 to +75                       |                     |           |             |  |  |  |

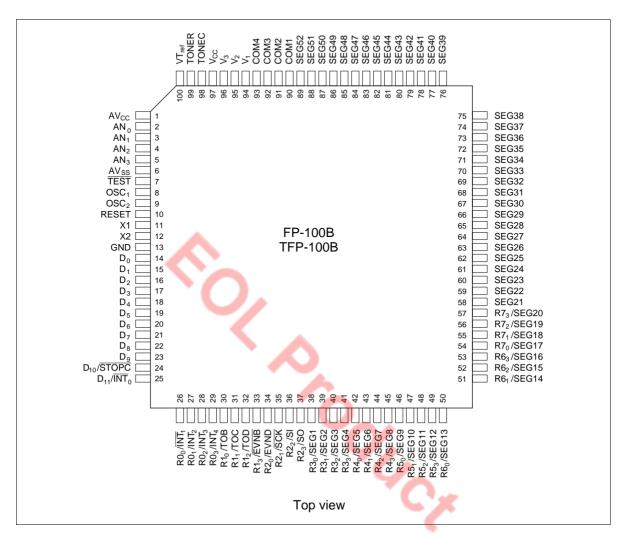

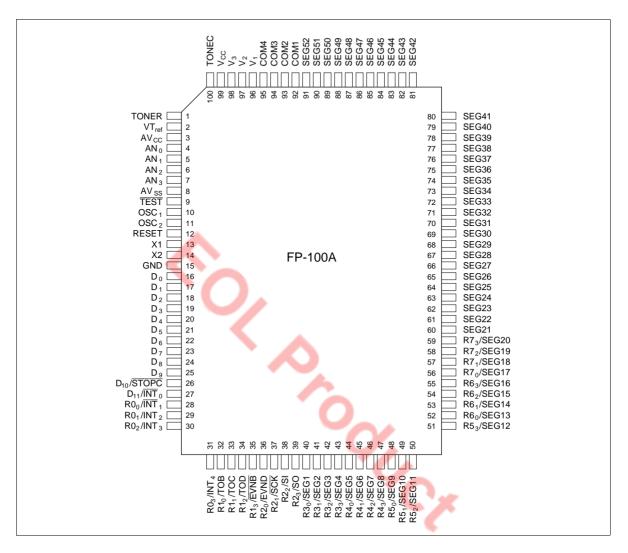

#### **Pin Arrangement**

#### **Pin Arrangement**

## **Pin Description**

|                |                                                          | Pin Numbe           | r       |          |                                                                                                                                                                                                                    |

|----------------|----------------------------------------------------------|---------------------|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Item           | Symbol                                                   | FP-100B<br>TFP-100B | FP-100A | -<br>I/O | Function                                                                                                                                                                                                           |

| Power          | V <sub>cc</sub>                                          | 97                  | 99      |          | Applies power voltage                                                                                                                                                                                              |

| supply         | GND                                                      | 13                  | 15      |          | Connected to ground                                                                                                                                                                                                |

| Test           | TEST                                                     | 7                   | 9       | Ι        | Used for factory testing only: Connect this pin to $\rm V_{\rm cc}$                                                                                                                                                |

| Reset          | RESET                                                    | 10                  | 12      | Ι        | Resets the MCU                                                                                                                                                                                                     |

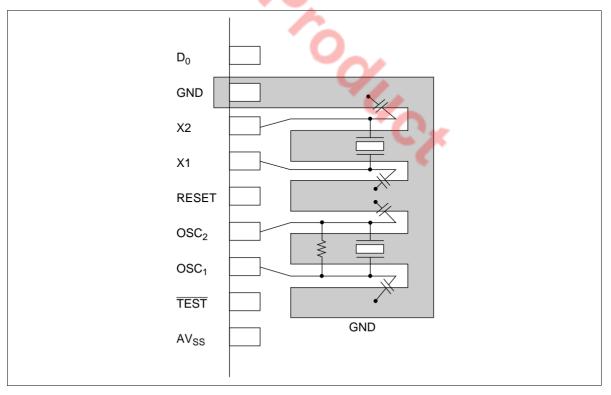

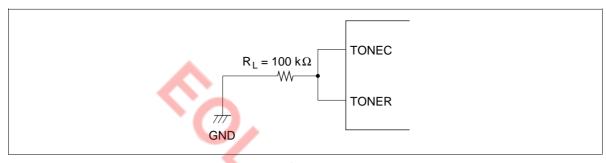

| Oscillato<br>r | OSC <sub>1</sub>                                         | 8                   | 10      | Ι        | Input/output pins for the internal oscillator circuit:                                                                                                                                                             |

|                | OSC <sub>2</sub>                                         | 9                   | 11      | 0        | Connect them to a ceramic oscillator ,crystal<br>oscillator or connect OSC <sub>1</sub> to an external<br>oscillator<br>curcuit                                                                                    |

|                | X1                                                       | 11                  | 13      | I        | Used for a 32.768-kHz crystal for clock purposes.                                                                                                                                                                  |

|                | X2                                                       | 12                  | 14      | 0        | If not to be used, fix the X1 pin to V <sub>cc</sub> and leave the X2 pin open.                                                                                                                                    |

| Port           | D <sub>0</sub> –D <sub>9</sub>                           | 14–23               | 16–25   | I/O      | Input/output pins addressed by individual bits; pins $D_0$ - $D_9$ are high-current pins that can each supply up to 15 mA                                                                                          |

|                | D <sub>10</sub> , D <sub>11</sub>                        | 24, 25              | 26, 27  |          | Input pins addressable by individual bits                                                                                                                                                                          |

|                | R0 <sub>0</sub> –R7 <sub>3</sub>                         | 26–57               | 28–59   | I/O      | Input/output pins addressable in 4-bit units                                                                                                                                                                       |

| Interrupt      | $\overline{INT}_0, \overline{INT}_1,$<br>$INT_2 - INT_4$ | 25–29               | 27–31   | I        | Input pins for external interrupts                                                                                                                                                                                 |

| Stop clear     | STOPC                                                    | 24                  | 26      | I        | Input pin for transition from stop mode to active mode                                                                                                                                                             |

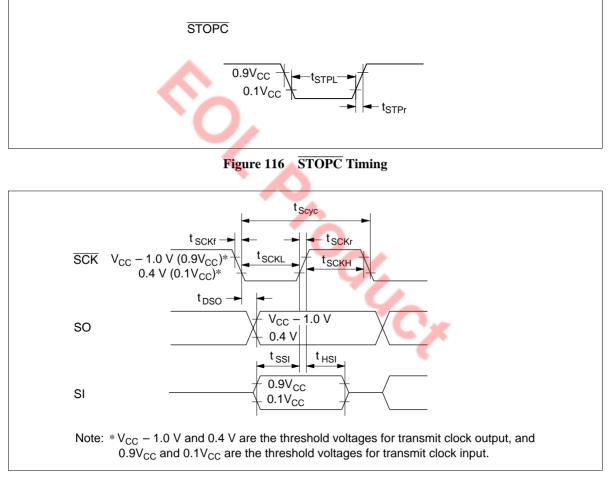

| Serial         | SCK                                                      | 35                  | 37      | I/O      | Serial interface clock input/output pin                                                                                                                                                                            |

| interface      | SI                                                       | 36                  | 38      | I        | Serial interface receive data input pin                                                                                                                                                                            |

|                | SO                                                       | 37                  | 39      | 0        | Serial interface transmit data output pin                                                                                                                                                                          |

| Timer          | TOB, TOC,<br>TOD                                         | 30–32               | 32–34   | 0        | Timer output pins                                                                                                                                                                                                  |

|                | EVNB, EVND                                               | 33, 34              | 35, 36  | I        | Event count input pins                                                                                                                                                                                             |

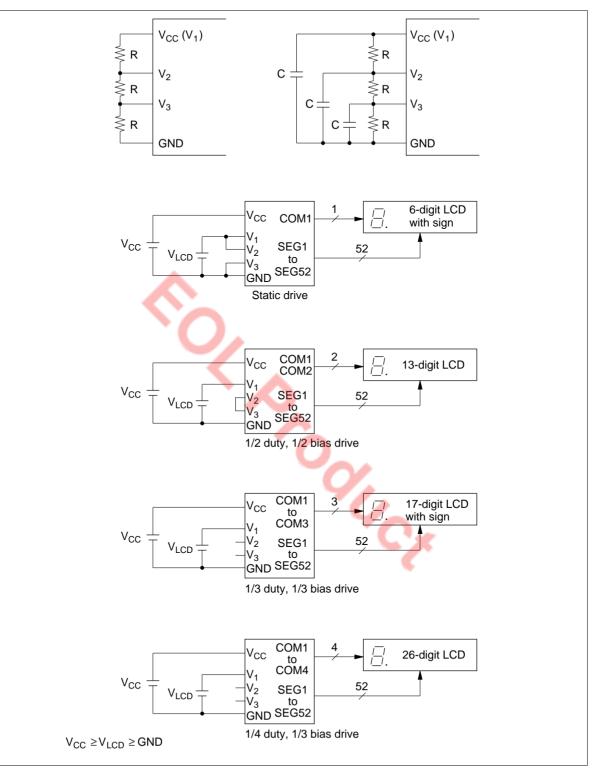

| LCD            | V <sub>1</sub> , V <sub>2</sub> , V <sub>3</sub>         | 94–96               | 96–98   |          | Power pins for LCD controller/driver; may be left<br>open during operation since they are connected by<br>internal voltage division resistors.<br>Voltage conditions are: $V_{CC} \ge V_1 \ge V_2 \ge V_3 \ge GND$ |

|                | COM1–COM4                                                | 90–93               | 92–95   | 0        | Common signal pins for LCD                                                                                                                                                                                         |

|                | SEG1-SEG52                                               | 38–89               | 40–91   | 0        | Segment signal pins for LCD                                                                                                                                                                                        |

|                                  | Pin Number                                                                                 |                                                                                                                                                                                                                 | _                                                                                                                                                                                                                                                            |                                                                                                                                         |

|----------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Symbol                           | FP-100B<br>TFP-100B                                                                        | FP-100A                                                                                                                                                                                                         | I/O                                                                                                                                                                                                                                                          | Function                                                                                                                                |

| AV <sub>cc</sub>                 | 1                                                                                          | 3                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              | Power pin for A/D converter: Connect it to the same potential as $V_{\rm CC}$ , as physically close to the $V_{\rm CC}$ pin as possible |

| AV <sub>SS</sub>                 | 6                                                                                          | 8                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              | Ground for $AV_{cc}$ : Connect it to the same potential as GND, as physically close to the GND pin as possible                          |

| AN <sub>0</sub> -AN <sub>3</sub> | 2–5                                                                                        | 4–7                                                                                                                                                                                                             | I                                                                                                                                                                                                                                                            | Analog input pins for A/D converter                                                                                                     |

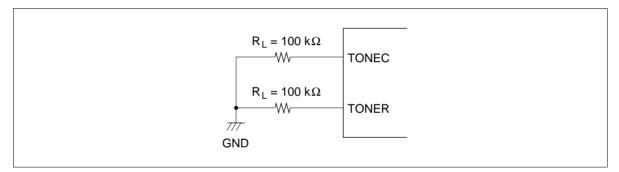

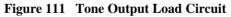

| TONER                            | 99                                                                                         | 1                                                                                                                                                                                                               | 0                                                                                                                                                                                                                                                            | Output pin for DTMF row signals                                                                                                         |

| TONEC                            | 98                                                                                         | 100                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                            | Output pin for DTMF column signals                                                                                                      |

| VT <sub>ref</sub>                | 100                                                                                        | 2                                                                                                                                                                                                               |                                                                                                                                                                                                                                                              | Reference voltage pin for DTMF signals. Voltage conditions are: $V_{CC} \ge VT_{ref} \ge GND$                                           |

|                                  |                                                                                            |                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                              |                                                                                                                                         |

|                                  | AV <sub>cc</sub><br>AV <sub>ss</sub><br>AN <sub>0</sub> -AN <sub>3</sub><br>TONER<br>TONEC | Symbol         TFP-100B           AV <sub>cc</sub> 1           AV <sub>ss</sub> 6           AN <sub>o</sub> -AN <sub>3</sub> 2–5           TONER         99           TONEC         98           VT         100 | Symbol         TFP-100B         FP-100A           AV <sub>cc</sub> 1         3           AV <sub>ss</sub> 6         8           AN <sub>o</sub> -AN <sub>3</sub> 2–5         4–7           TONER         99         1           TONEC         98         100 | Symbol         TFP-100B         FP-100A         I/O           AV <sub>CC</sub> 1         3                                              |

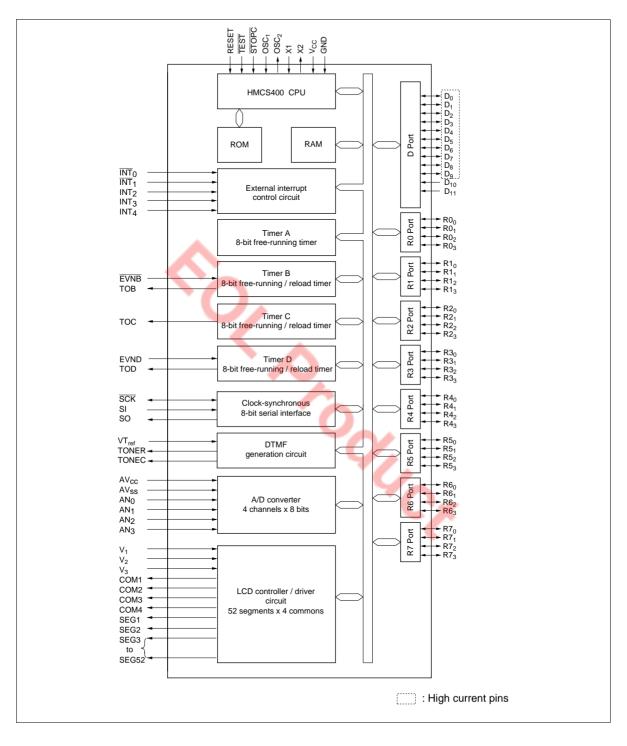

## **Block Diagram**

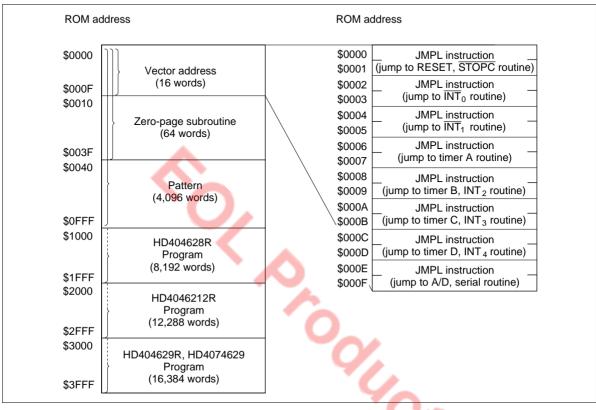

## **Memory Map**

#### **ROM Memory Map**

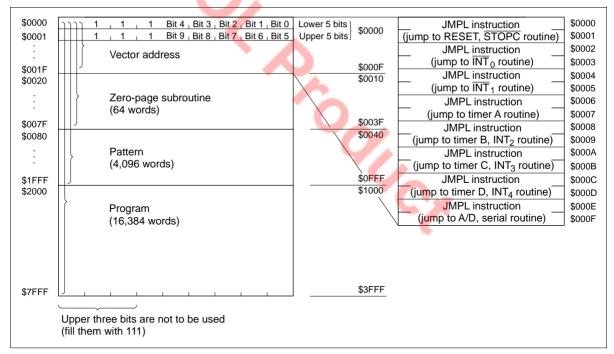

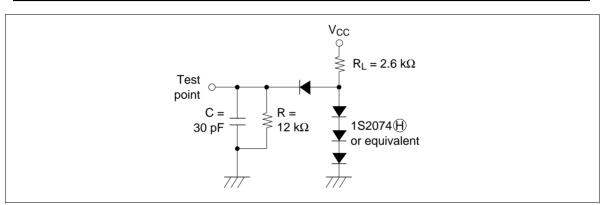

The ROM memory map is shown in figure 1 and described below.

Figure 1 ROM Memory Map

**Vector Address Area (\$0000–\$000F):** Reserved for JMPL instructions that branch to the start addresses of the reset and interrupt routines. After MCU reset or an interrupt, program execution continues from the vector address.

**Zero-Page Subroutine Area (\$0000-\$003F):** Reserved for subroutines. The program branches to a subroutine in this area in response to the CAL instruction.

Pattern Area (\$0000-\$0FFF): Contains ROM data that can be referenced with the P instruction.

**Program Area (\$0000-\$1FFF: HD404628R; \$0000-\$2FFF: HD4046212R; \$0000-\$3FFF; HD404629R, HD4074629):** Used for program coding.

#### **RAM Memory Map**

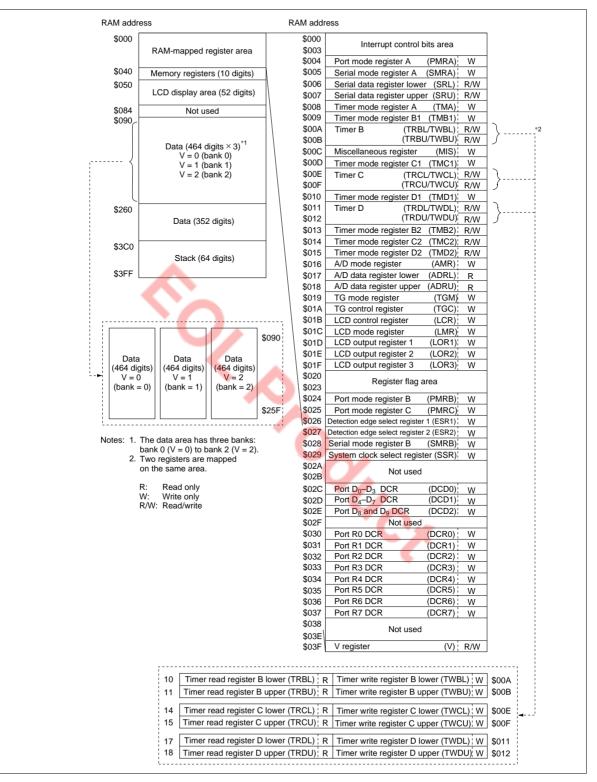

The MCU contains a 1,876-digit  $\times$  4-bit RAM area consisting of a memory register area, an LCD data area, a data area, and a stack area. In addition, an interrupt control bits area, special register area, and register flag area are mapped onto the same RAM memory space as a RAM-mapped register area outside the above areas. The RAM memory map is shown in figure 2 and described below.

#### RAM-Mapped Register Area (\$000-\$03F):

• Interrupt Control Bits Area (\$000–\$003)

This area is used for interrupt control bits (figure 3). These bits can be accessed only by RAM bit manipulation instructions (SEM/SEMD, REM/REMD, and TM/TMD). However, note that not all the instructions can be used for each bit. Limitations on using the instructions are shown in figure 4.

• Special Function Register Area (\$004–\$01F, \$024–\$03F)

This area is used as mode registers and data registers for external interrupts, serial interface, timer/counters, LCD, A/D converter, and as data control registers for I/O ports. The structure is shown in figures 2 and 5. These registers can be classified into three types: write-only (W), read-only (R), and read/write (R/W). The SEM, SEMD, REM, and REMD instructions can be used for the LCD control register (LCR: \$01B), but RAM bit manipulation instructions cannot be used for other registers.

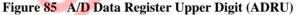

- Register Flag Area (\$020–\$023)

- This area is used for the DTON, WDON, and other register flags and interrupt control bits (figure 3). These bits can be accessed only by RAM bit manipulation instructions (SEM/SEMD, REM/REMD, and TM/TMD). However, note that not all the instructions can be used for each bit. Limitations on using the instructions are shown in figure 4.

Figure 2 RAM Memory Map

|       | Bit 3                                | Bit 2                            | Bit 1                                    | Bit 0                                  |

|-------|--------------------------------------|----------------------------------|------------------------------------------|----------------------------------------|

| \$000 | IM0<br>(IM of INT <sub>0</sub> )     | IF0<br>(IF of INT <sub>0</sub> ) | RSP<br>(Reset SP bit)                    | IE<br>(Interrupt<br>enable flag)       |

| \$001 | IMTA<br>(IM of timer A)              | IFTA<br>(IF of timer A)          | IM <u>1</u><br>(IM of INT <sub>1</sub> ) | IF1<br>(IF of INT <sub>1</sub> )       |

| \$002 | IMTC<br>(IM of timer C)              | IFTC<br>(IF of timer C)          | IMTB<br>(IM of timer B)                  | IFTB<br>(IF of timer B)                |

| \$003 | IMAD<br>(IM of A/D)                  | IFAD<br>(IF of A/D)              | IMTD<br>(IM of timer D)                  | IFTD<br>(IF of timer D)                |

|       |                                      | Interrupt con                    | trol bits area                           |                                        |

|       | Bit 3                                | Bit 2                            | Bit 1                                    | Bit 0                                  |

| \$020 | DTON<br>(Direct transfer<br>on flag) | ADSF<br>(A/D start flag)         | WDON<br>(Watchdog<br>on flag)            | LSON<br>(Low speed<br>on flag)         |

| \$021 | RAME<br>(RAM enable<br>flag)         | Not used                         | ICEF<br>(Input capture<br>error flag)    | ICSF<br>(Input capture<br>status flag) |

|       |                                      |                                  |                                          |                                        |

IF3

(IF of INT<sub>3</sub>)

IFS

(IF of serial

interface)

Register flag area

IM3

(IM of INT<sub>3</sub>)

IMS

(IM of serial

interface)

\$022

\$023

IF: Interrupt request flag

IM: Interrupt mask

IE: Interrupt enable flag

SP: Stack pointer

#### Figure 3 Configuration of Interrupt Control Bits and Register Flag Areas

IF2

(IF of INT<sub>2</sub>)

IF4

(IF of INT₄)

IM<sub>2</sub>

(IM of INT<sub>2</sub>)

IM4

(IM of  $INT_4$ )

|          | SEM/SEMD                    | REM/REMD     | TM/TMD    |  |

|----------|-----------------------------|--------------|-----------|--|

| IE       |                             |              |           |  |

| IM       | Allowed                     | Allowed      | Allowed   |  |

| LSON     |                             |              |           |  |

| IF       |                             |              |           |  |

| ICSF     | Not executed                | d Allowed    | Allowed   |  |

| ICEF     | Not executed                |              |           |  |

| RAME     |                             |              |           |  |

| RSP      | Not executed                | Allowed      | Inhibited |  |

| WDON     | Allowed                     | Not executed | Inhibited |  |

| ADSF     | Allowed                     | Inhibited    | Allowed   |  |

| DTON     | Not executed in active mode | Allowed      | Allowed   |  |

| DTON     | Used in subactive mode      | Allowed      | Allowed   |  |

| Not used | Not executed                | Not executed | Inhibited |  |

Note: WDON is reset by MCU reset or by STOPC enable for stop mode cancellation. The REM or REMD instuction must not be executed for ADSF during A/D conversion. DTON is always reset in active mode. If the TM or TMD instruction is executed for the inhibited bits or non-existing bits,

the value in ST becomes invalid.

Figure 4 Usage Limitations of RAM Bit Manipulation Instructions

| RAM address                        |                                                                                                                                |                                                           |                                                                            |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------|

| RAW address                        | Bit 3 Bit 2                                                                                                                    | Bit 1 Bit 0                                               |                                                                            |

| \$000                              |                                                                                                                                |                                                           |                                                                            |

| \$003                              | Interrupt o                                                                                                                    | ontrol bits area                                          |                                                                            |

| PMRA \$004                         | Not used Not used                                                                                                              | R2 <sub>2</sub> /SI R2 <sub>3</sub> /SO                   |                                                                            |

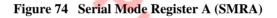

| SMRA \$005                         | R2 <sub>1</sub> /SCK Serial tra                                                                                                | ansmit clock speed selection                              |                                                                            |

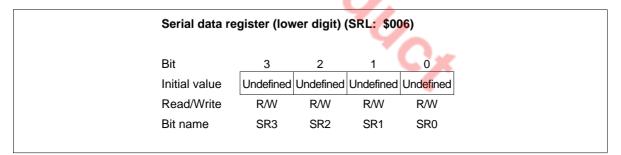

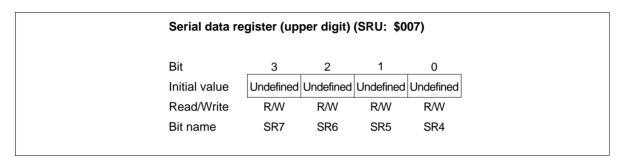

| SRL \$006                          | Serial data re                                                                                                                 | gister (lower digit)                                      |                                                                            |

| SRU \$007                          | Serial data re                                                                                                                 | gister (upper digit)                                      |                                                                            |

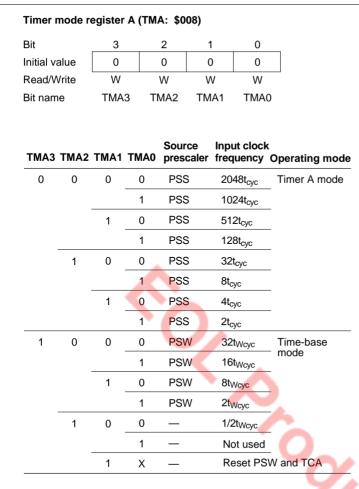

| TMA \$008                          | *1 Cloc                                                                                                                        | source setting (timer A)                                  |                                                                            |

| TMB1 \$009                         | *2 Cloc                                                                                                                        | source setting (timer B)                                  |                                                                            |

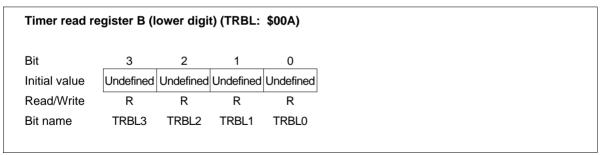

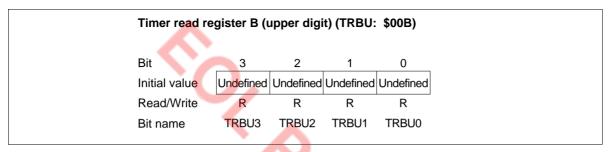

| TRBL/TWBL \$00A                    |                                                                                                                                | ister (lower digit)                                       |                                                                            |

| TRBU/TWBU \$00B                    |                                                                                                                                | ister (upper digit)                                       |                                                                            |

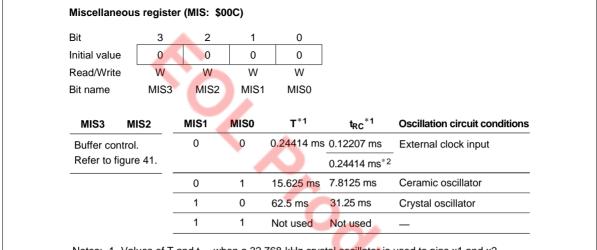

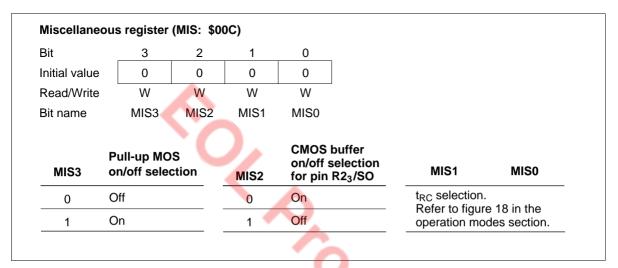

| MIS \$00C                          |                                                                                                                                | trol Interrupt frame period select                        |                                                                            |

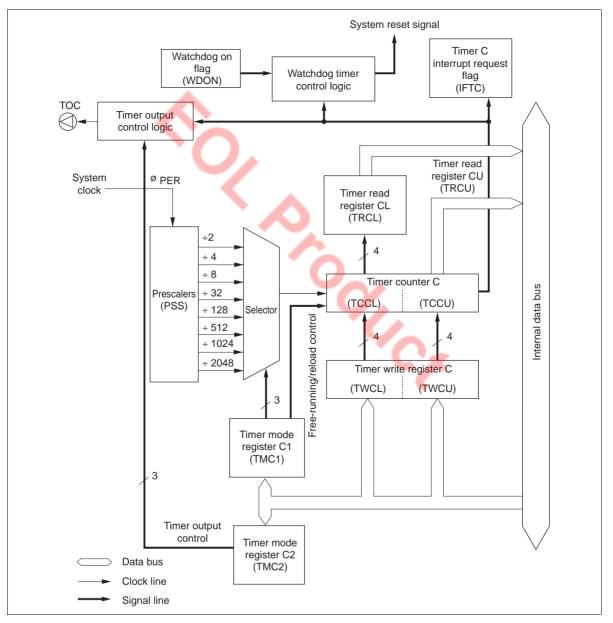

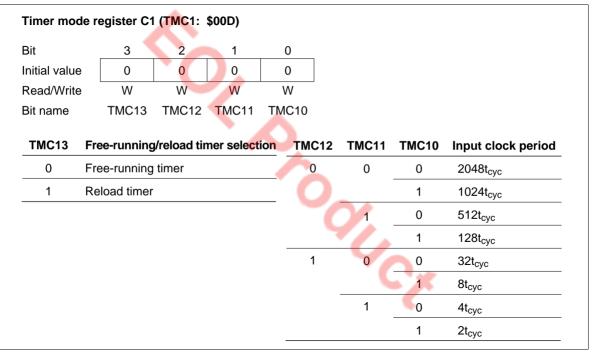

| TMCI \$00D                         | · · · · · · · · · · · · · · · · · · ·                                                                                          | source setting (timer C)                                  |                                                                            |

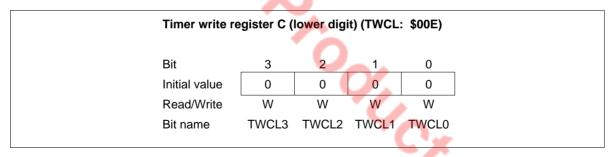

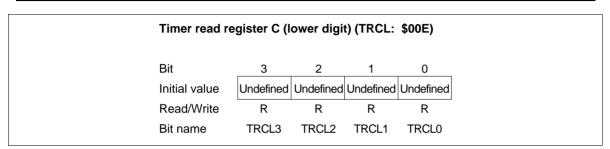

| TRCL/TWCL \$00E                    |                                                                                                                                | ister (lower digit)                                       | _                                                                          |

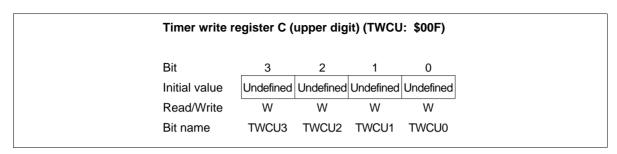

| TRCU/TWCU \$00F                    |                                                                                                                                | ister (upper digit)                                       |                                                                            |

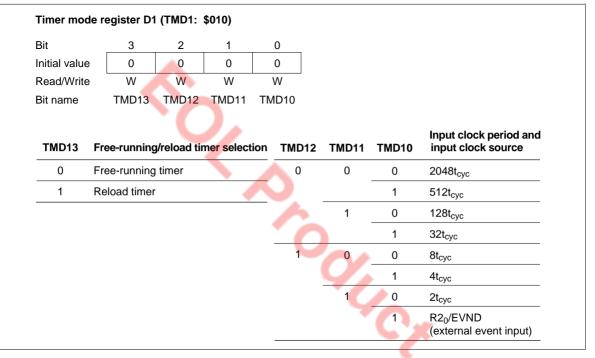

| TMDI \$010                         |                                                                                                                                | source setting (timer D) ister (lower digit)              | -                                                                          |

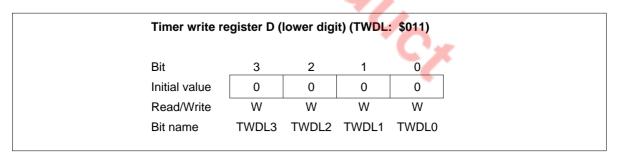

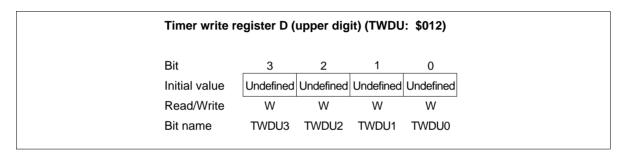

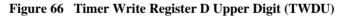

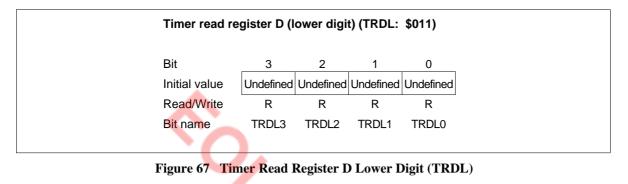

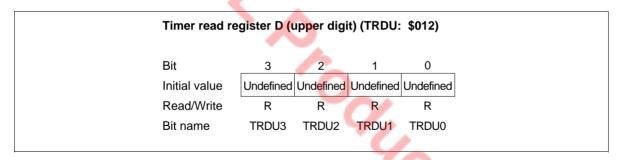

| TRDL/TWDL \$011<br>TRDU/TWDU \$012 | -                                                                                                                              | ister (upper digit)                                       | -                                                                          |

| TMB2 \$013                         | Not used Not used                                                                                                              | Timer-B output mode select                                |                                                                            |

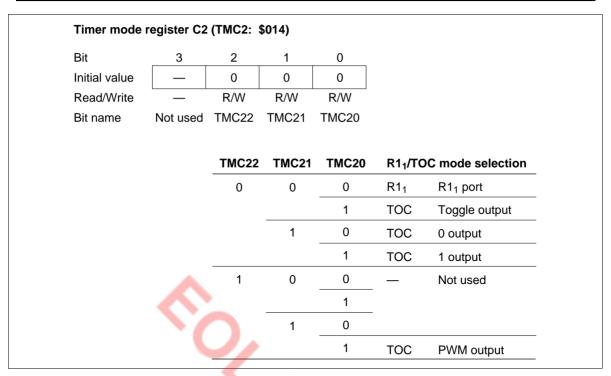

| TMC2 \$013                         |                                                                                                                                | er-C output mode setting                                  |                                                                            |

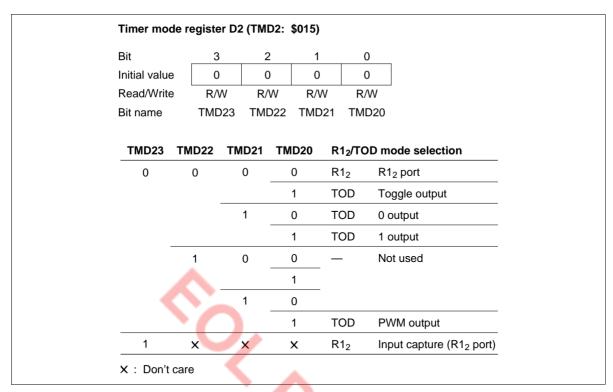

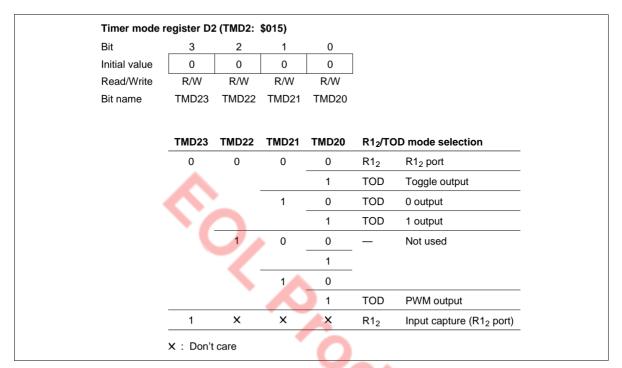

| TMD2 \$015                         |                                                                                                                                | er-D output mode setting                                  |                                                                            |

| AMR \$016                          | Analog channel selection                                                                                                       |                                                           | _                                                                          |

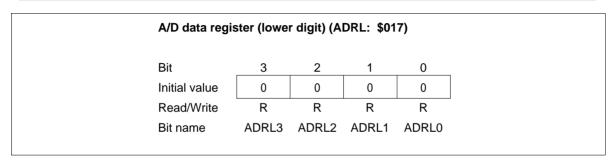

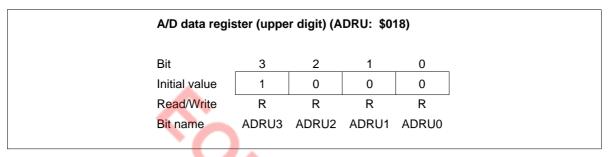

| ADRL \$017                         |                                                                                                                                | jister (lower digit)                                      | _                                                                          |

| ADRU \$018                         |                                                                                                                                | ister (upper digit)                                       |                                                                            |

| TGM \$019                          | TONEC output frequency                                                                                                         |                                                           | · ·                                                                        |

| TGC \$01A                          | *6 *7                                                                                                                          | DTMF enable Not use                                       |                                                                            |

| LCR \$01B                          | Not used *8                                                                                                                    | *9 *10                                                    |                                                                            |

| LMR \$01C                          | LCD input clock source selecti                                                                                                 | on LCD duty cycle selectio                                |                                                                            |

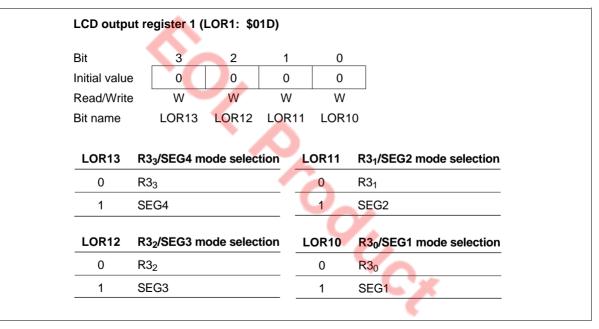

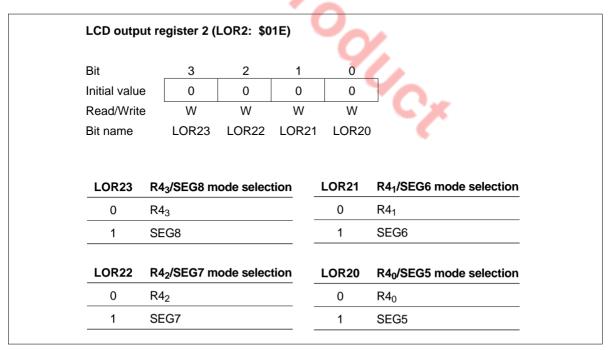

| LOR1 \$01D                         | R3 <sub>3</sub> /SEG4 R3 <sub>2</sub> /SEG3                                                                                    | R3 <sub>1</sub> /SEG2 R3 <sub>0</sub> /SEG                |                                                                            |

| LOR2 \$01E                         | R4 <sub>3</sub> /SEG8 R4 <sub>2</sub> /SEG7                                                                                    | R4 <sub>1</sub> /SEG6 R4 <sub>0</sub> /SEG                |                                                                            |

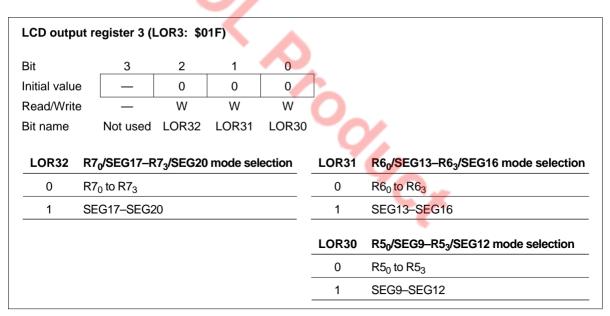

| LOR3 \$01F                         | Not used R7/SEG17-                                                                                                             | 20 R6/SEG13-16 R5/SEG9-                                   | 2                                                                          |

| \$020                              |                                                                                                                                |                                                           |                                                                            |

| ¢000                               | Regisi                                                                                                                         | er flag area                                              |                                                                            |

| \$023<br>PMRB \$024                |                                                                                                                                | R01/INT2 R00/INT                                          |                                                                            |

| PMRC \$025                         | R0 <sub>3</sub> /INT <sub>4</sub> R0 <sub>2</sub> /INT <sub>3</sub><br>D <sub>11</sub> /INT <sub>0</sub> D <sub>10</sub> /STOP |                                                           |                                                                            |

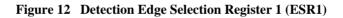

| ESR1 \$026                         | INT <sub>3</sub> detection edge selection                                                                                      | - · · ·                                                   |                                                                            |

| ESR2 \$027                         | EVND detection edge selection                                                                                                  |                                                           |                                                                            |

| SMRB \$028                         | Not used Not used                                                                                                              | *11 *12                                                   |                                                                            |

| SSR \$029                          | *13 *14                                                                                                                        | Clock select                                              |                                                                            |

|                                    |                                                                                                                                | ot used                                                   | on<br>on                                                                   |

|                                    |                                                                                                                                |                                                           | _                                                                          |

| DCD0 \$02C                         |                                                                                                                                | R Port D <sub>1</sub> DCR Port D <sub>0</sub> D           |                                                                            |

| DCD1 \$02D                         |                                                                                                                                | R Port D <sub>5</sub> DCR Port D <sub>4</sub> D           |                                                                            |

| DCD2 \$02E                         | Not used Not used                                                                                                              | Port D <sub>9</sub> DCR Port D <sub>8</sub> D0<br>ot used |                                                                            |

| DCR0 \$030                         |                                                                                                                                | R Port R01 DCR Port R00 D                                 | Notes: 1. Timer-A/time-base                                                |

| DCR1 \$031                         |                                                                                                                                | $\frac{1}{10000000000000000000000000000000000$            | 2. / 10/01/01/01/                                                          |

| DCR2 \$032                         | *                                                                                                                              | R Port R21 DCR Port R20 D                                 | <ol> <li>Input capture selection</li> </ol>                                |

| DCR3 \$033                         |                                                                                                                                | R Port R31 DCR Port R30 D                                 | 5. A/D conversion time                                                     |

| DCR4 \$034                         | ×                                                                                                                              | R Port R4 <sub>1</sub> DCR Port R4 <sub>0</sub> D         |                                                                            |

| DCR5 \$035                         |                                                                                                                                | R Port R5 <sub>1</sub> DCR Port R5 <sub>0</sub> D         | 8. Display on/off in watch mode                                            |

| DCR6 \$036                         | Port R6 <sub>3</sub> DCR Port R6 <sub>2</sub> DC                                                                               |                                                           | - 9 I CD nower switch                                                      |

| DCR7 \$037                         | · · · · · · · · · · · · · · · · · · ·                                                                                          | R Port R71 DCR Port R70 D                                 | R 11. SO idle H/L setting                                                  |

|                                    | N                                                                                                                              | ot used                                                   | 12. Transmit clock source selection<br>13. 32-kHz oscillation stop setting |

| V \$03F                            | Not used Not used                                                                                                              | Bank 0 to bank 2 selection                                | 14. 32-kHz oscillation division ratio                                      |

| ν φυση                             |                                                                                                                                |                                                           |                                                                            |

Figure 5 Special Function Register Area

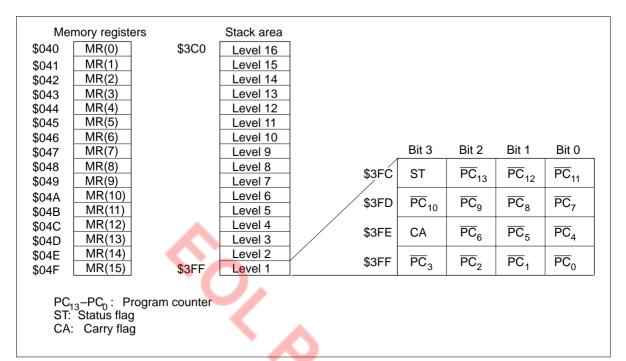

**Memory Register (MR) Area (\$040–\$04F):** Consisting of 16 addresses, this area (MR0–MR15) can be accessed by register-register instructions (LAMR and XMRA). The structure is shown in figure 6.

Figure 6 Configuration of Memory Registers and Stack Area, and Stack Position

LCD Data Area (\$050-\$083): Used for storing 52-digit LCD data which is automatically output to LCD segments as display data. Data 1 lights the corresponding LCD segment; data 0 extinguishes it. Refer to the LCD description for details.

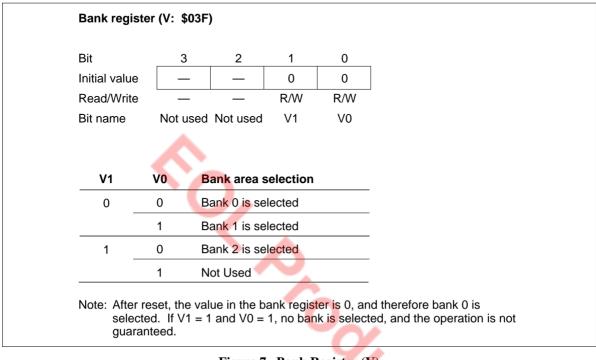

**Data Area (\$090–\$3BF):** 464 digits from \$090 to \$25F have three banks, which can be selected by setting the bank register (V: \$03F). Before accessing this area, set the bank register to the required value (figure 7). The area from \$260 to \$3BF is accessed without setting the bank register.

Figure 7 Bank Register (V)

**Stack Area (\$3C0-\$3FF):** Used for saving the contents of the program counter (PC), status flag (ST), and carry flag (CA) at subroutine call (CAL or CALL instruction) and for interrupts. This area can be used as a 16-level nesting subroutine stack in which one level requires four digits. The data to be saved and the save conditions are shown in figure 6.

The program counter is restored by either the RTN or RTNI instruction, but the status and carry flags can only be restored by the RTNI instruction. Any unused space in this area is used for data storage.

## **Functional Description**

#### **Registers and Flags**

The MCU has nine registers and two flags for CPU operations. They are shown in figure 8 and described below.

| Accumulator                                                 | Initial value: Undefined, R/W                                           | 3 0<br>(A)   |

|-------------------------------------------------------------|-------------------------------------------------------------------------|--------------|

| B register                                                  | Initial value: Undefined, R/W                                           | 3 0<br>(B)   |

| W register                                                  | Initial value: Undefined, R/W                                           | 1 0<br>(W)   |

| X register                                                  | Initial value: Undefined, R/W                                           | 3 0<br>(X)   |

| Y register                                                  | Initial value: Undefined, R/W                                           | 3 0<br>(Y)   |

| SPX register                                                | Initial value: Undefined, R/W                                           | 3 0<br>(SPX) |

| SPY register                                                | Initial value: Undefined, R/W                                           | 3 0<br>(SPY) |

| Carry                                                       | Initial value: Undefined, R/W                                           | 0<br>(CA)    |

| Status                                                      | Initial value: 1, R/W not possible                                      | 0<br>(ST)    |

| Program counter<br>Initial value: \$000<br>R/W not possible | 13<br>0, (PC)                                                           | 0            |

| Stack pointer                                               | 9         5           7, R/W not possible         1         1         1 | 0<br>(SP)    |

#### Figure 8 Registers and Flags

Accumulator (A) and B Register (B): A and B are 4-bit registers, and are used to hold the results of ALU (arithmetic and logical unit) operations and to transfer data between memory, I/O ports, and other registers.

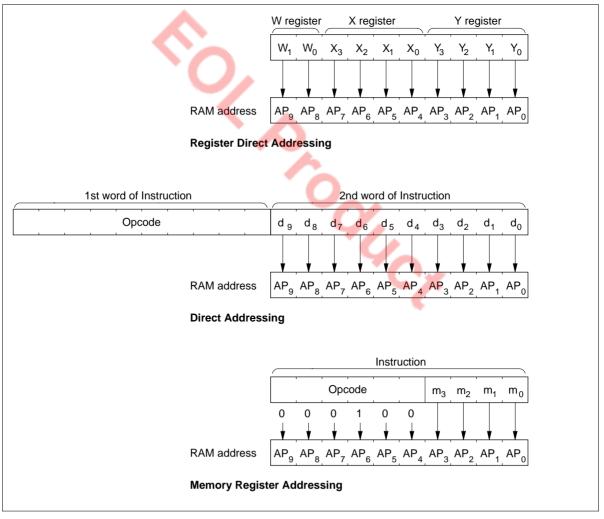

W Register (W), X Register (X), and Y Register (Y): W is a 2-bit register and X and Y are 4-bit registers. These registers are used in RAM register indirect addressing. The Y register is also used in D port addressing.

**SPX Register (SPX) and SPY Register (SPY):** The SPX and SPY registers are 4-bit registers used to supplement the X and Y registers.

**Carry Flag (CA):** CA is a 1-bit flag that stores ALU overflow generated by an arithmetic operation. CA is set to 1 when an overflow is generated, and is cleared to 0 after operations in which no overflow occurred. CA is also affected by the carry set/carry clear instructions (SEC and REC), and by the rotate with carry instructions (ROTL and ROTR).

During interrupt handling, CA is saved on the stack, and is restored from the stack by the RTNI instruction.

**Status Flag (ST):** ST is a 1-bit flag that stores the results of arithmetic instructions, compare instructions, and bit test instructions, and is used as the branch condition for the BR, BRL, CAL, and CALL conditional branch instructions.

The contents of the ST flag are held until the next arithmetic, compare, bit test, or conditional branch instruction is executed. After the execution of a conditional branch instruction, the value of ST is set to 1 without regard to the condition.

During interrupt handling, ST is saved on the stack, and is restored from the stack by the RTNI instruction.

**Program Counter (PC):** The PC is a 14-bit counter that indicates the ROM address of the next instruction the CPU will execute.

**Stack Pointer (SP):** The SP is a 10-bit register that indicates the RAM address of the next stack frame in the stack area.

The SP is initialized to \$3FF by a reset. The SP is decremented by 4 by a subroutine call or by interrupt handling, and is incremented by 4 when the saved data has been restored by a return instruction.

The upper 4 bits of the SP are fixed at 1111; the maximum number of stack levels is thus 16.

In addition to the reset method described above, the SP can also be initialized to \$3FF by clearing the reset stack pointer (RSP) in the interrupt control bits area with a RAM bit manipulation instruction, i.e., REM or REMD.

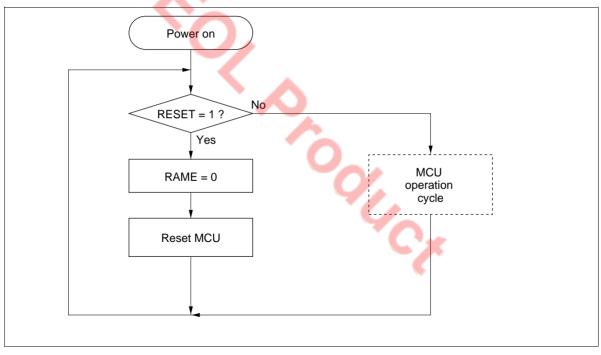

#### Reset

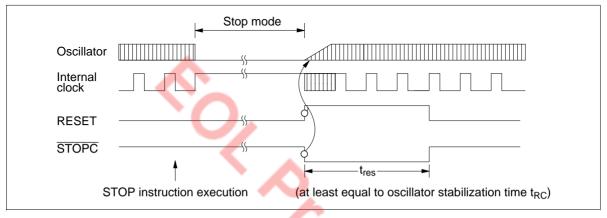

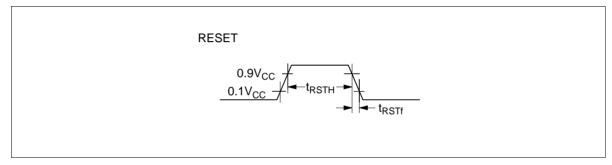

The MCU is reset by inputting a high-level voltage to the RESET pin. At power-on or when stop mode is cancelled, RESET must be high for at least one  $t_{RC}$  to enable the oscillator to stabilize. During operation, RESET must be high for at least two instruction cycles.

Initial values after MCU reset are listed in table 1.

#### Table 1 Initial Values After MCU Reset

| Item               |                                   | Abbr.                       | Initial<br>Value | Contents                                                            |

|--------------------|-----------------------------------|-----------------------------|------------------|---------------------------------------------------------------------|

| Program<br>counter |                                   | (PC)                        | \$0000           | Indicates program execution point from start<br>address of ROM area |

| Status flag        |                                   | (ST)                        | 1                | Enables conditional branching                                       |

| Stack pointer      |                                   | (SP)                        | \$3FF            | Stack level 0                                                       |

| Interrupt          | Interrupt enable flag             | (IE)                        | 0                | Inhibits all interrupts                                             |

| flags/mask         | Interrupt request flag            | (IF)                        | 0                | Indicates there is no interrupt request                             |

|                    | Interrupt mask                    | (IM)                        | 1                | Prevents (masks) interrupt requests                                 |

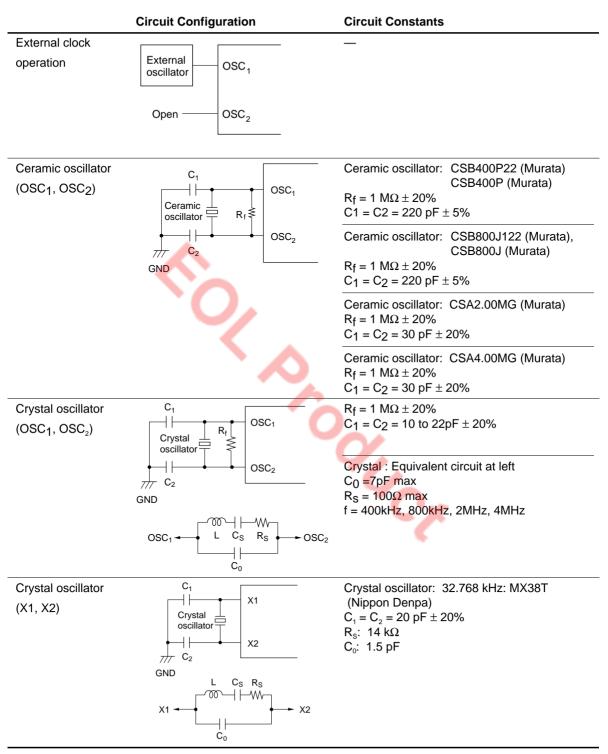

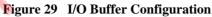

| I/O                | Port data register                | (PDR)                       | All bits 1       | Enables output at level 1                                           |

|                    | Data control register             | (DCD0,<br>DCD1)             | All bits 0       | Turns output buffer off (to high impedance)                         |

|                    |                                   | (DCD2)                      | 00               | -                                                                   |

|                    |                                   | (DCR0,<br>-DCR7)            | All bits 0       | -                                                                   |

|                    | Port mode register A              | (PMRA)                      | 00               | Refer to description of port mode register A                        |

|                    | Port mode register B              | (PMRB)                      | 0000             | Refer to description of port mode register B                        |

|                    | Port mode register C bits 3, 1, 0 | (PMRC3,<br>PMRC1,<br>PMRC0) | 000              | Refer to description of port mode register C                        |

|                    | Detection edge select register 1  | (ESR1)                      | 0000             | Disables edge detection                                             |

|                    | Detection edge select register 2  | (ESR2)                      | 0000             | Disables edge detection                                             |

| Timer/             | Timer mode register A             | (TMA)                       | 0000             | Refer to description of timer mode register A                       |

| counters,          | Timer mode register B1            | (TMB1)                      | 0000             | Refer to description of timer mode register B1                      |

| serial             | Timer mode register B2            | (TMB2)                      | 00               | Refer to description of timer mode register B2                      |

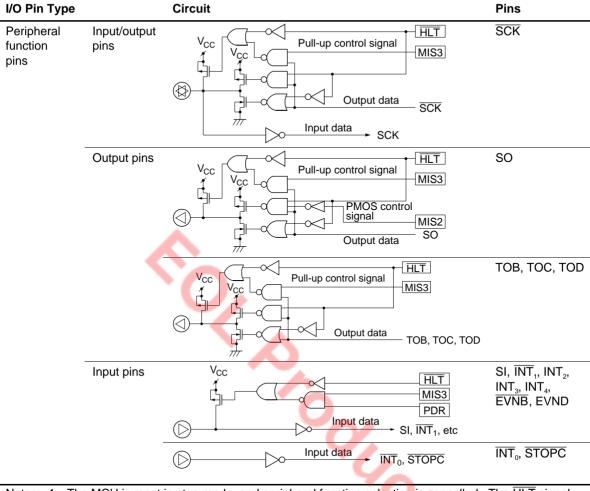

| interface          | Timer mode register C1            | (TMC1)                      | 0000             | Refer to description of timer mode register C1                      |

|                    | Timer mode register C2            | (TMC2)                      | - 000            | Refer to description of timer mode register C2                      |

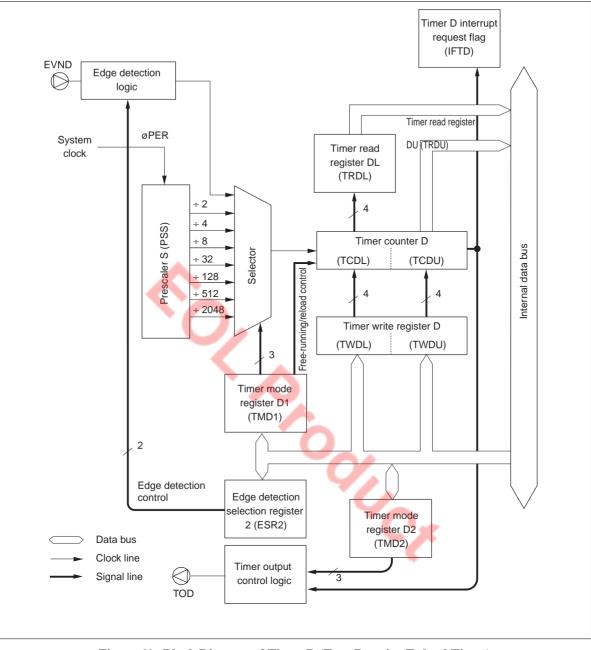

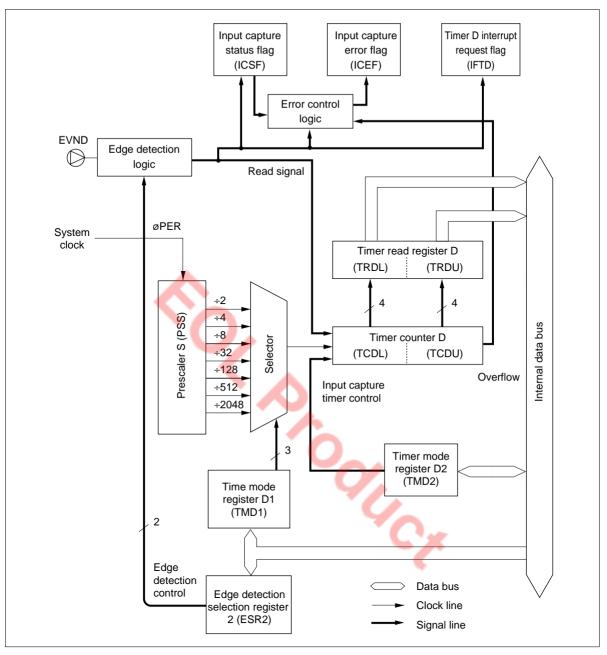

|                    | Timer mode register D1            | (TMD1)                      | 0000             | Refer to description of timer mode register D1                      |

|                    | Timer mode register D2            | (TMD2)                      | 0000             | Refer to description of timer mode register D2                      |

|                    | Serial mode register A            | (SMRA)                      | 0000             | Refer to description of serial mode register A                      |

|                    | Serial mode register B            | (SMRB)                      | X0               | Refer to description of serial mode register B                      |

|                    | Prescaler S                       | (PSS)                       | \$000            | —                                                                   |

|                    | Prescaler W                       | (PSW)                       | \$00             |                                                                     |

|                    | Timer counter A                   | (TCA)                       | \$00             | _                                                                   |

|                    | Timer counter B                   | (TCB)                       | \$00             | _                                                                   |

|                    | Timer counter C                   | (TCC)                       | \$00             | -                                                                   |

|                    | Timer counter D                   | (TCD)                       | \$00             | _                                                                   |

#### Table 1 Initial Values After MCU Reset (cont)

| Item                |                                 | Abbr.           | Initial<br>Value | Contents                                                                          |

|---------------------|---------------------------------|-----------------|------------------|-----------------------------------------------------------------------------------|

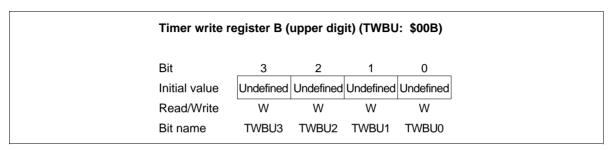

| Timer/<br>counters, | Timer write register B          | (TWBU,<br>TWBL) | \$X0             | _                                                                                 |

| serial<br>interface | Timer write register C          | (TWCU,<br>TWCL) | \$X0             | _                                                                                 |

|                     | Timer write register D          | (TWDU,<br>TWDL) | \$X0             | _                                                                                 |

|                     | Octal counter                   | (OC)            | 000              | —                                                                                 |

| A/D                 | A/D mode register               | (AMR)           | 00 - 0           | Refer to description of A/D mode register                                         |

|                     | A/D data register               | (ADRL,<br>ADRU) | \$80             | Refer to description of A/D data register                                         |

| LCD                 | LCD control register            | (LCR)           | - 000            | Refer to description of LCD control register                                      |

|                     | LCD mode register               | (LMR)           | 0000             | Refer to description of LCD duty-cycle/clock control register                     |

|                     | LCD output register 1           | (LOR1)          | 0000             | Sets R-port/LCD segment pins to R port mode                                       |

|                     | LCD output register 2           | (LOR2)          | 0000             |                                                                                   |

|                     | LCD output register 3           | (LOR3)          | - 000            |                                                                                   |

| DTMF                | Tone generator mode<br>register | (TGM)           | 0000             | Refer to description of tone generator mode register                              |

|                     | Tone generator control register | (TGC)           | 000 - 000        | Refer to description of tone generator control register                           |

| Bit registers       | Low speed on flag               | (LSON)          | 0                | Refer to description of operating modes                                           |

|                     | Watchdog timer on flag          | (WDON)          | 0                | Refer to description of timer C                                                   |

|                     | A/D start flag                  | (ADSF)          | 0                | Refer to description of A/D converter                                             |

|                     | Direct transfer on flag         | (DTON)          | 0                | Refer to description of operating modes                                           |

|                     | Input capture status flag       | (ICSF)          | 0                | Refer to description of timer D                                                   |

|                     | Input capture error flag        | (ICEF)          | 0                | Refer to description of timer D                                                   |

| Others              | Miscellaneous register          | (MIS)           | 0000             | Refer to description of operating modes, I/O, and serial interface                |

|                     | System clock select register    | (SSR)           | 0000             | Refer to description of operating modes, oscillation circuits, and DTMF generator |

|                     | Bank register                   | (V)             | 00               | Refer to description of RAM memory map                                            |

Notes: 1. The statuses of other registers and flags after MCU reset are shown in the following table.

2. X indicates invalid value. - indicates that the bit does not exist.

| Item                               | Abbr.      | Status After Cancel-<br>lation of Stop Mode by<br>STOPC Input | Status After Cancel-<br>lation of Stop Mode by<br>RESET Input | Status After all Other Types<br>of Reset |

|------------------------------------|------------|---------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------|

| Carry flag                         | (CA)       | Pre-stop-mode values are                                      | e not guaranteed;                                             | Pre-MCU-reset values                     |

| Accumulator                        | (A)        | values must be initialized                                    | by program                                                    | are not guaranteed; val-                 |

| B register                         | (B)        |                                                               |                                                               | ues must be initialized by               |

| W register                         | (W)        | -                                                             |                                                               | program                                  |

| X/SPX register                     | (X/SPX)    | -                                                             |                                                               |                                          |

| Y/SPY register                     | (Y/SPY)    | -                                                             |                                                               |                                          |

| Serial data register               | (SRL, SRU) | -                                                             |                                                               |                                          |

| RAM                                |            | Pre-stop-mode values are                                      | e retained                                                    | -                                        |

| RAM enable flag                    | (RAME)     | 1                                                             | 0                                                             | 0                                        |

| Port mode<br>register C bit 2      | (PMRC2)    | Pre-stop-mode<br>values are retained                          | 0                                                             | 0                                        |

| System clock select register bit 3 | (SSR3)     |                                                               |                                                               |                                          |

#### Interrupts

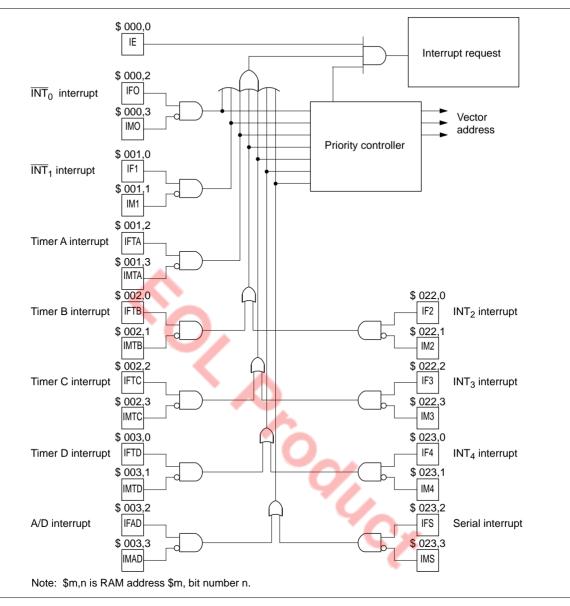

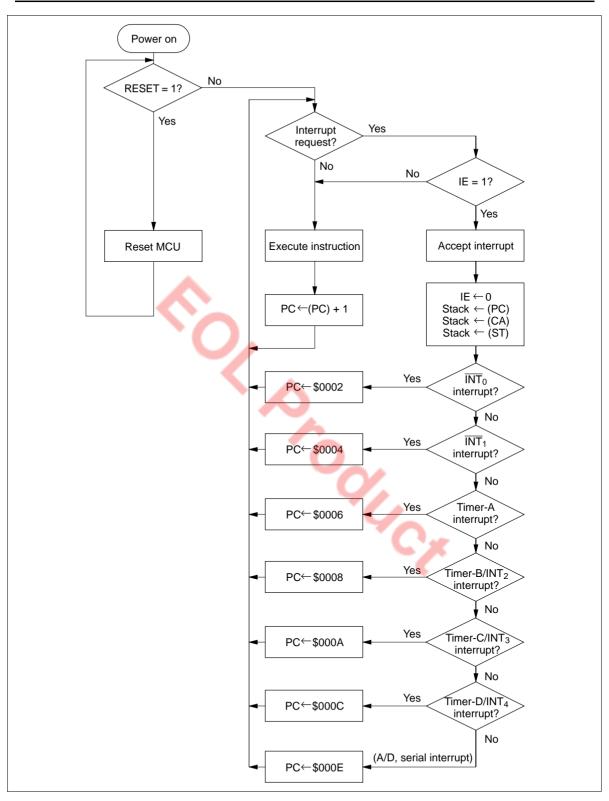

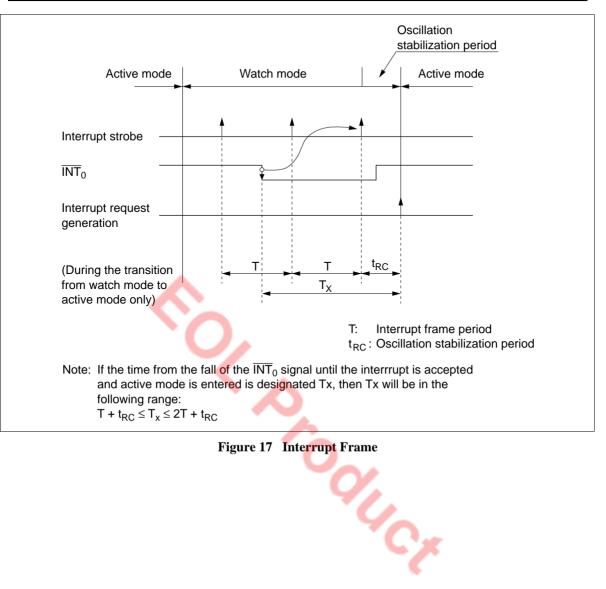

The MCU has 11 interrupt sources: five external signals ( $\overline{INT}_0$ ,  $\overline{INT}_1$ ,  $INT_2$ -INT<sub>4</sub>), four timer/ counters (timers A, B, C, and D), serial interface, and A/D converter.

An interrupt request flag (IF), interrupt mask (IM), and vector address are provided for each interrupt source, and an interrupt enable flag (IE) controls the entire interrupt process.

Some vector addresses are shared by two different interrupts. They are timer B and  $INT_2$ , timer C and  $INT_3$ , timer D and  $INT_4$ , and A/D converter and serial interface interrupts. So the type of request that has occurred must be checked at the beginning of interrupt processing.

**Interrupt Control Bits and Interrupt Processing:** Locations \$000 to \$003 and \$022 to \$023 in RAM are reserved for the interrupt control bits which can be accessed by RAM bit manipulation instructions.

The interrupt request flag (IF) cannot be set by software. MCU reset initializes the interrupt enable flag (IE) and the IF to 0 and the interrupt mask (IM) to 1.

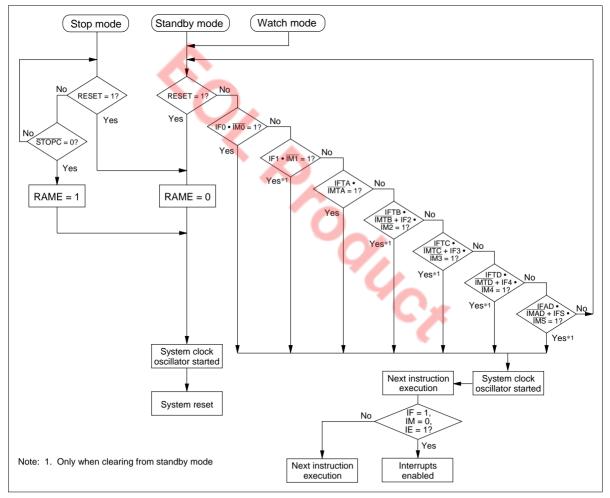

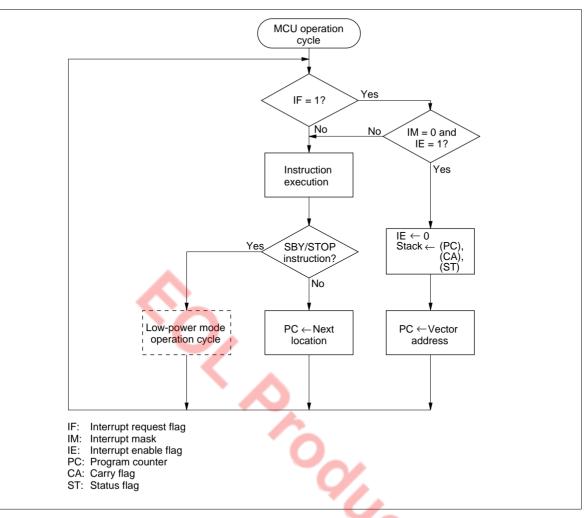

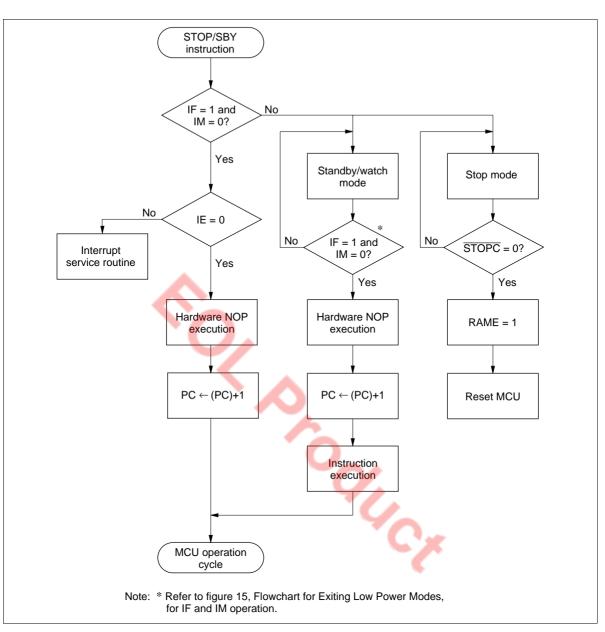

A block diagram of the interrupt control circuit is shown in figure 9, interrupt priorities and vector addresses are listed in table 2, and interrupt processing conditions for the 11 interrupt sources are listed in table 3.

An interrupt request occurs when the IF is set to 1 and the IM is set to 0. If the IE is 1 at that point, the interrupt is processed. A priority programmable logic array (PLA) generates the vector address assigned to that interrupt source.

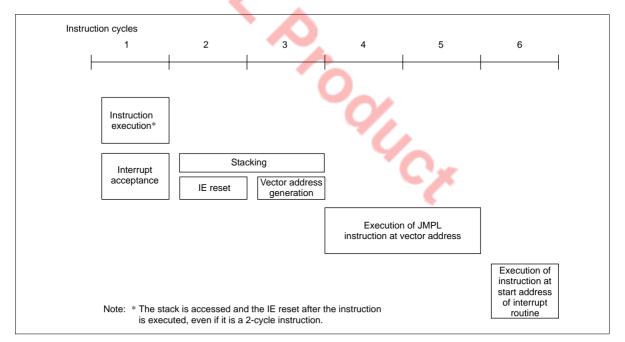

The interrupt processing sequence is shown in figure 10 and an interrupt processing flowchart is shown in figure 11. After an interrupt is acknowledged, the previous instruction is completed in the first cycle. The IE is reset in the second cycle, the carry, status, and program counter values are pushed onto the stack

during the second and third cycles, and the program jumps to the vector address to execute the instruction in the third cycle.

Program the JMPL instruction at each vector address, to branch the program to the start address of the interrupt program, and reset the IF by a software instruction within the interrupt program.

| Reset/Interrupt  | Priority | Vector Address |

|------------------|----------|----------------|

| RESET, STOPC*    | _        | \$0000         |

| ĪNT <sub>o</sub> | 1        | \$0002         |

| ĪNT <sub>1</sub> | 2        | \$0004         |

| Timer A          | 3        | \$0006         |

| Timer B, INT2    | 4        | \$0008         |

| Timer C, INT3    | 5        | \$000A         |

| Timer D, INT4    | 6        | \$000C         |

| A/D, Serial      | 7        | \$000E         |

Table 2 Vector Addresses and Interrupt Priorities

Note: \* The STOPC interrupt request is valid only in stop mode.

Figure 9 Interrupt Control Circuit

|                                   | Interrupt Source |                  |         |                                |                                |                                |                  |

|-----------------------------------|------------------|------------------|---------|--------------------------------|--------------------------------|--------------------------------|------------------|

| Interrupt<br>Cuntrol Bit          | ĪNT <sub>0</sub> | INT <sub>1</sub> | Timer A | Timer B or<br>INT <sub>2</sub> | Timer C or<br>INT <sub>3</sub> | Timer D or<br>INT <sub>4</sub> | A/D or<br>Serial |

| IE                                | 1                | 1                | 1       | 1                              | 1                              | 1                              | 1                |

| IF0 · IMO                         | 1                | 0                | 0       | 0                              | 0                              | 0                              | 0                |

| IF1 · IM1                         | *                | 1                | 0       | 0                              | 0                              | 0                              | 0                |

| IFTA · ĪMTĀ                       | *                | *                | 1       | 0                              | 0                              | 0                              | 0                |

| IFTB · IMTB<br>+ IF2 · IM2        | *                | *                | *       | 1                              | 0                              | 0                              | 0                |

| IFTC · <u>IMTC</u><br>+ IF3 · IM3 | *                | *                | *       | *                              | 1                              | 0                              | 0                |

| IFTD · <u>IMTD</u><br>+ IF4 · IM4 | *                | *                | *       | *                              | *                              | 1                              | 0                |

| IFAD · IMAD<br>+ IFS · IMS        | *                |                  | *       | *                              | *                              | *                              | 1                |

#### Table 3 Interrupt Processing and Activation Conditions

Note: Bits marked \* can be either 0 or 1. Their values have no effect on operation.

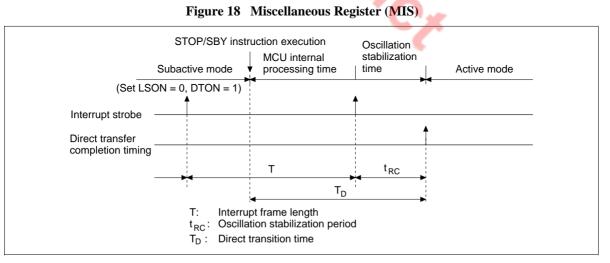

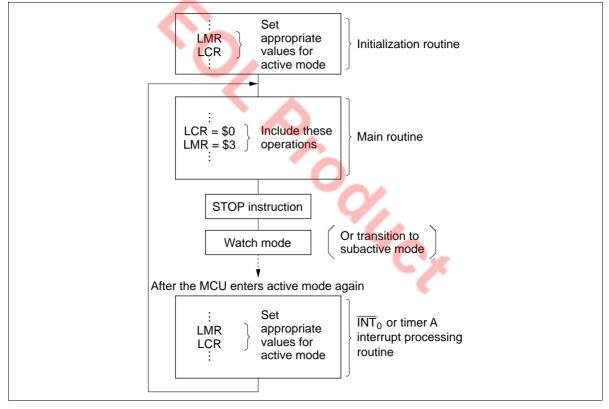

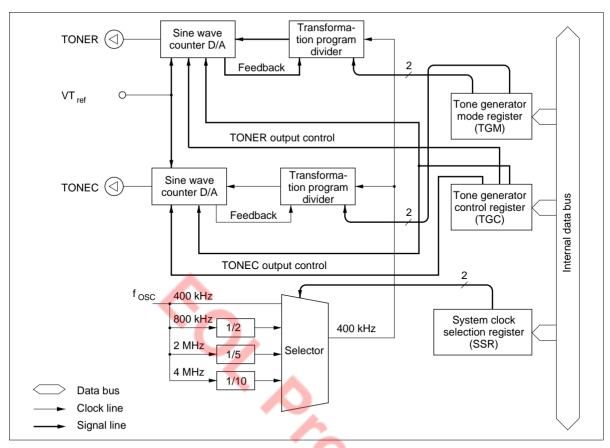

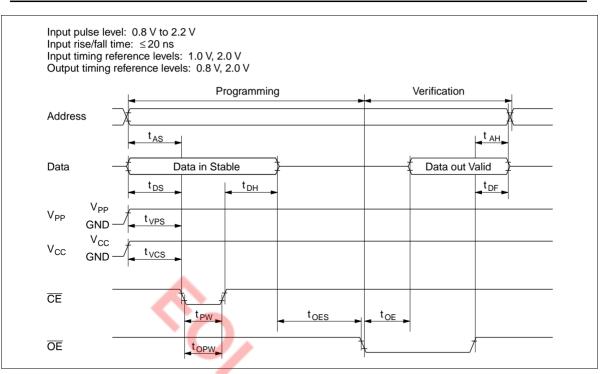

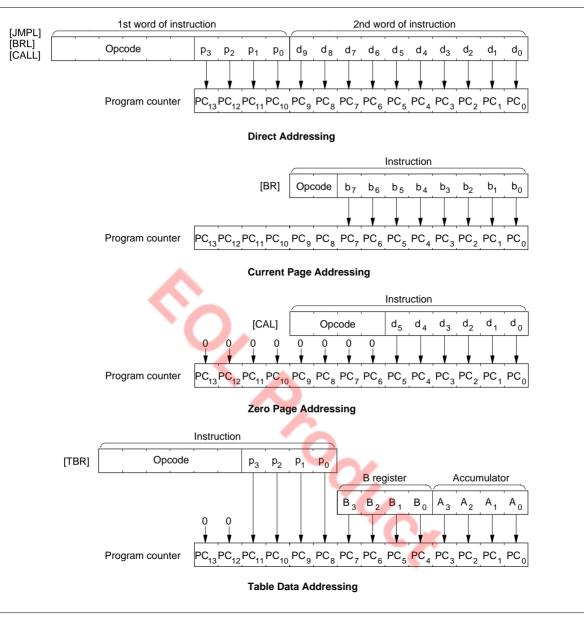

Figure 10 Interrupt Processing Sequence