### Description

The Edge629 is a monolithic timing delay and signal fanout solution manufactured in a high-performance bipolar process. In Automatic Test Equipment (ATE) applications, the Edge629 buffers, distributes, and aligns timing signals across multiple channels (typically found inside Memory Test Systems). It is also suitable for per pin deskew in Logic Testers.

#### The Edge629 supports:

- Minimum pulse width = 330 ps with Falling Edge Adjust disabled, 500 ps with Falling Edge Adjust enabled

- Net usable delay span ≥ 4.0 ns

- Falling Edge Adjust ± 250 ps

- On Board DACs to generate 5 ps resolution

With a maximum operating frequency of 1 GHz, the Edge629 is optimized for extremely high speed, high accuracy testers, particularly those aimed to test memory devices.

The Edge629 solves several difficult problems associated with aligning multiple timing signals because it can:

- delay very narrow pulses over a long timing span

- adjust the falling edge independently from the overall propagation delay

- maintain extreme timing accuracy for very narrow (sub-ns) pulses

- maintain tight timing accuracy over changes in frequency, duty cycle, and pattern.

### **Applications**

- Memory Test Equipment

- Data Fanout

- Channel Deskew

- Logic Testers

- Per Pin Deskew

- Clock / Signal Fanout

#### **Features**

- Fmax ≥ 1 GHz

- Independent Falling Edge Adjust

- Small Footprint (10 mm x 10 mm)

- Excellent Timing Accuracy

- Very Stable Timing Delays

- 5 ps Resolution

- ECL, CMOS Compatible Inputs

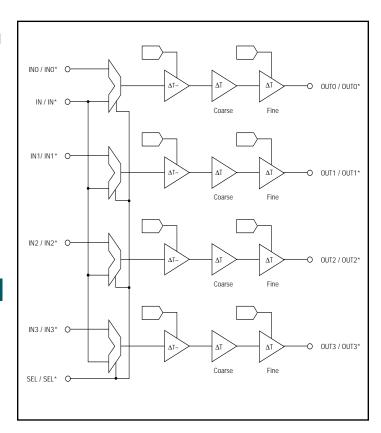

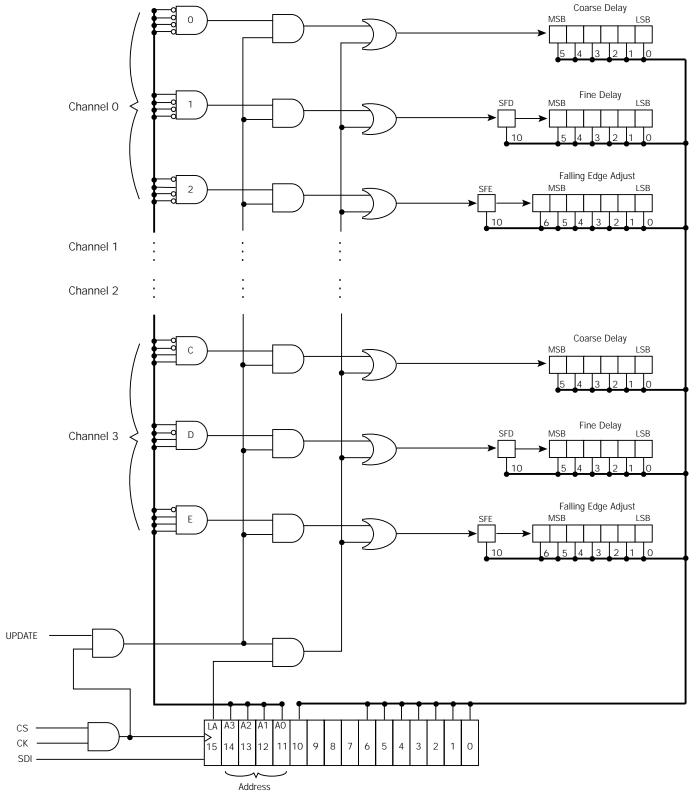

### Functional Block Diagram

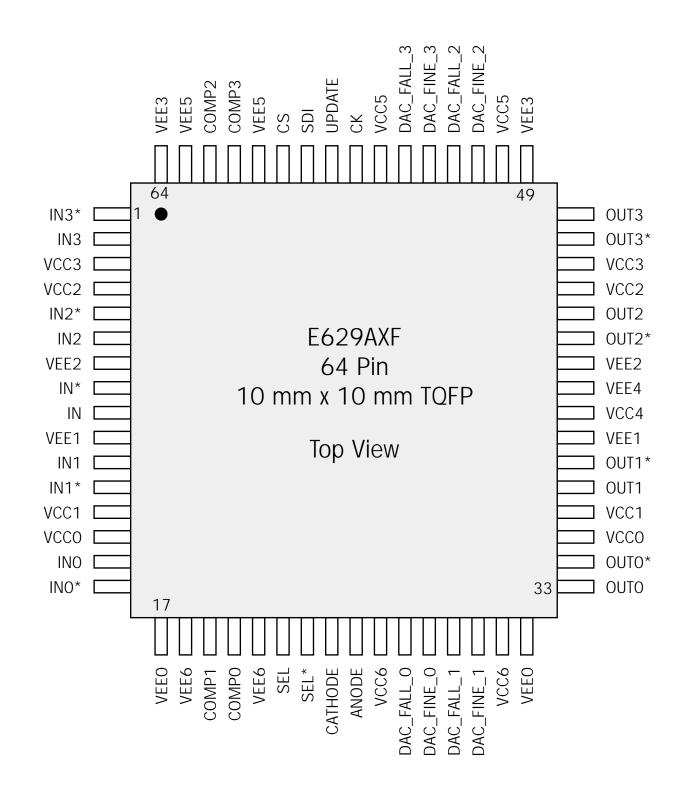

# PIN Description

| Pin Name                                             | Pin #                                                   | Description                                                                                         |

|------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| IN/IN*                                               | 9, 8                                                    | Differential input signal used for 1:4 signal fanout.                                               |

| INO, INO*<br>IN1/IN1*<br>IN2/IN2*<br>IN3/IN3*        | 15, 16<br>11, 12<br>6, 5<br>2, 1                        | Differential input signals used for 1:1 signal fanout.                                              |

| OUTO/OUTO*<br>OUT1/OUT1*<br>OUT2/OUT2*<br>OUT3/OUT3* | 33, 34<br>37, 38<br>44, 43<br>48, 47                    | Differential output signals.                                                                        |

| SEL/SEL*                                             | 22, 23                                                  | Differential input signals used to select the input signal source.                                  |

| SDI                                                  | 58                                                      | Serial data input.                                                                                  |

| СК                                                   | 56                                                      | Clock used to latch in SDI.                                                                         |

| CS                                                   | 59                                                      | Chip select.                                                                                        |

| UPDATE                                               | 57                                                      | Digital input which loads the delay registers.                                                      |

| CATHODE, ANODE                                       | 24, 25                                                  | Terminals of an on-chip thermal diode string.                                                       |

| COMPO-3                                              | 20, 19, 62, 61                                          | External op amp compensation pins.                                                                  |

| DAC_FALL_(0-3)                                       | 27, 29, 52, 54                                          | Falling edge adjust DAC outputs. For test purposes only; nothing should be connected to these pins. |

| DAC_FINE_(0-3)                                       | 28, 30, 51, 53                                          | Fine delay DAC outputs. For test purposes only; nothing should be connected to these pins.          |

| VCC                                                  | 3, 4, 13, 14, 26,<br>31, 35, 36, 40, 45,<br>46, 50, 55  | Positive power supply.                                                                              |

| VEE                                                  | 7, 10, 17, 18, 21,<br>32, 39, 41, 42, 49,<br>60, 63, 64 | Negative power supply.                                                                              |

PIN Description (continued)

### Circuit Description

#### Introduction

The Edge629 is a quad channel delay element with 2 basic operating modes:

- 1) Fanout 1 signal in, 4 signals out

- 2) Pass Through 4 signals in, 4 signals out

In all modes, each channel supports 3 delay functions:

- 1) Coarse timing delay

- 2) Fine timing delay

- 3) Falling edge adjust

All 3 delay functions are independent of each other, and independent for each channel.

The programming of the delay functions is done using a 16 bit register, loaded serially, which contains both a delay and an address value.

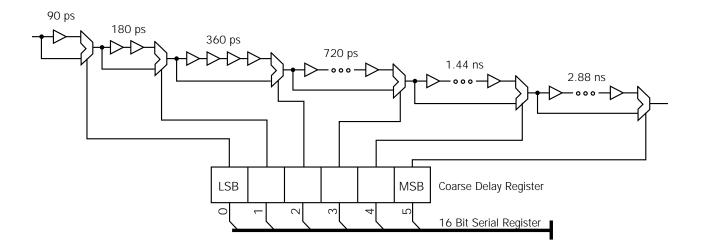

#### **Coarse Delay**

Coarse propagation delay adjustment is accomplished using a series of gate delays and multiplexers (see Figure 1). Coarse delay provides a total delay span of:

1 Coarse LSB = 90 ps

2 Coarse LSB = 180 ps

4 Coarse LSB = 360 ps

8 Coarse LSB = 720 ps

16 Coarse LSB = 1.44 ns

32 Coarse LSB = 2.88 ns

$0 \text{ ns} \leq \text{Coarse Delay Range} \leq 5.67 \text{ ns}$

Each channel has its own unique coarse delay setting and may be programmed independently from all other channels. The coarse delay of any channel will not affect the fine delay of that channel, nor will it affect the overall delay of any other channel.

The propagation delay of a rising edge and falling edge will track each other over the entire coarse delay span. (Adding or subtracting coarse delay does not cause pulse width distortion.)

| Delay Code |               |         |

|------------|---------------|---------|

| 000000     | Minimum Delay | 0.0 ns  |

| 111111     | Maximum Delay | 5.67 ns |

Figure 1. Coarse Delay Architecture

# Circuit Description (continued)

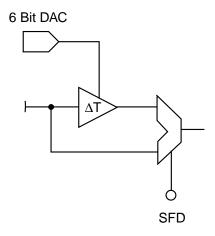

#### **Fine Delay**

Fine delay is accomplished using an analog delay cell and an on-chip 6 bit DAC (see Figure 2). The fine delay range is designed to be ~2X the coarse delay resolution.

Fine delay provides a total delay span of:

| LSB 1 Fine LSB  | = | 2.5 ps (see note) |

|-----------------|---|-------------------|

| 2 Fine LSB      | = | 5 ps              |

| 4 Fine LSB      | = | 10 ps             |

| 8 Fine LSB      | = | 20 ps             |

| 16 Fine LSB     | = | 40 ps             |

| MSP 32 Fine LSB | = | 80 ps             |

|                 | _ |                   |

$0 \text{ ns} \leq \text{ Fine Delay Range} \leq 157.5 \text{ ps.}$

*Note:* Because the transfer function is non-linear, some LSB steps could be as large as 5 ps.

Each channel has its own unique delay setting and may be programmed independently from all other channels. The fine delay of any channel will not affect the coarse delay of that channel, nor will it affect the overall delay of any other channel.

The propagation delay of a rising and falling edge will track each other over the entire span of fine delay. (Adding or subtracting fine delay will not cause pulse width distortion.)

#### **Fine Delay Select**

The fine delay section may be selected or bypassed by a multiplexer (see Figure 2). If SFD (Select Fine Delay) is high, Fine Delay will be used. If SFD is low, Fine Delay will be bypassed.

| DAC Code | SFD | Delay                  |

|----------|-----|------------------------|

| XXXXXX   | 0   | Fine Delay Bypassed    |

| 000000   | 1   | Minimum Delay (0.0 ns) |

| 111111   | 1   | Maximum Delay (157 ps) |

#### **Fine Delay DAC Outputs**

DAC\_FINE\_(0-3) are analog voltage outputs from the onboard DACs which program the fine delay elements of each channel.

DAC\_FINE\_(0-3) pins are for test purposes only. Nothing should be connected to these pins.

Figure 2. Fine Delay Architecture

### Circuit Description (continued)

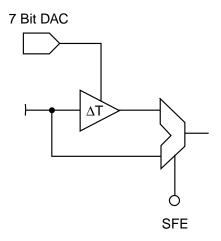

#### Falling Edge Adjustment

The falling edge of a signal may be adjusted to compensate for any system level pulse width distortion that may occur. Falling edge adjust (FEA) is accomplished using an analog delay cell and an on-chip 7 bit DAC (see Figure 3).

FEA may be bypassed completely by a multiplexer. Also, FEA affects only the propagation delay of the falling edge. It has no effect on the propagation delay of a rising edge.

Each channel has its own unique FEA setting and may be programmed independently from all other channels. The FEA of any channel will not affect the propagation delay of any other channel, nor will FEA affect the propagation delay of a rising edge.

| SFE | DAC Code           | Falling Edge<br>Delay | Resolution       |

|-----|--------------------|-----------------------|------------------|

| 0   | XXXXXXX            | FEA Bypassed          | N/A              |

| 1   | 0000000<br>1111111 | –250 ps<br>+250 ps    | 2.5 ps<br>2.5 ps |

Figure 3. Falling Edge Adjust Architecture

There is a limitation on FEA range vs. pulse width.

| Input Pulse Width | FEA Range |

|-------------------|-----------|

| 1.0 ns            | ±250 ps   |

| 900 ps            | ±250 ps   |

| 800 ps            | ±250 ps   |

| 700 ps            | ±250 ps   |

| 600 ps            | ±200 ps   |

| 500 ps            | ±100 ps   |

#### Falling Edge Adjust DAC Outputs

DAC\_FALL\_(0-3) are analog voltage outputs from the onboard DACs which program the falling edge delay elements of each channel.

DAC\_FALL\_(0-3) pins are for test purposes only. Nothing should be connected to these pins.

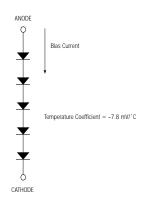

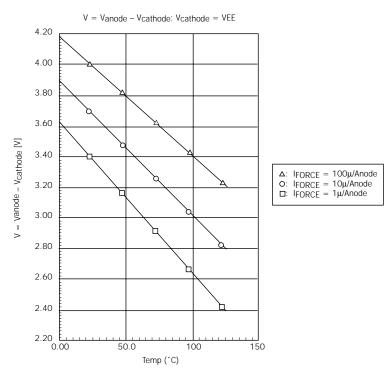

#### Thermal Monitor

The Edge629 features a thermal diode string consisting of 5 diodes as shown in Figure 4 below. This string allows accurate die temperature measurements.

Figure 4. Thermal Diode String

When an external bias current of up to  $100~\mu A$  is injected through the string, the voltage measured across the ANODE and CATHODE pins maps directly to the Edge629 junction temperature (see Figure 5).

# Circuit Description (continued)

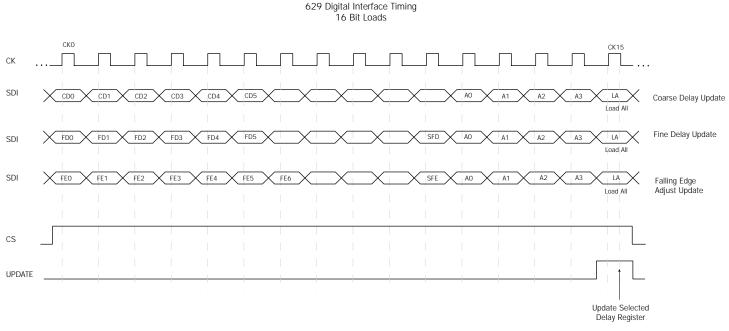

#### **Programming**

The Edge629 is programmed serially with 3 control lines:

SDI – serial data input CS – chip select UPDATE – register update

which are all synchronous with CK. With CS valid (high), rising edge of CK will load SDI into the 16 bit shift register.

With CS valid and UPDATE valid (high), CK high will make the selected latch go transparent. The falling edge of CK will then latch the data (see Figures 6 and 7).

Data and address information are combined in the 16 bit word. Bits 0–6 are used for data, bits 11–15 for address. Bits 11–14 select 1 of 16 destinations, bit 15, if high, selects all 16 locations to be loaded simultaneously (useful for preloading all registers to a default state).

| Bit       | 15 | 14 | 13 | 12 | 11 | 10 |                                |

|-----------|----|----|----|----|----|----|--------------------------------|

| Ad-<br>dr | LA | А3 | A2 | A1 | АО |    | Delay Function                 |

| 0         | 0  | 0  | 0  | 0  | 0  | Х  | Channel O, Coarse Delay        |

| 1         | 0  | 0  | 0  | 0  | 1  | 1  | Channel O, Fine Delay          |

| 2         | 0  | 0  | 0  | 1  | 0  | 1  | Channel O, Falling Edge Adjust |

| 3         | 0  | 0  | 0  | 1  | 1  | Х  | Not Used                       |

| 4         | 0  | 0  | 1  | 0  | 0  | Χ  | Channel 1, Coarse Delay        |

| 5         | 0  | 0  | 1  | 0  | 1  | 1  | Channel 1, Fine Delay          |

| 6         | 0  | 0  | 1  | 1  | 0  | 1  | Channel 1, Falling Edge Adjust |

| 7         | 0  | 0  | 1  | 1  | 1  | Х  | Not Used                       |

| 8         | 0  | 1  | 0  | 0  | 0  | Х  | Channel 2, Coarse Delay        |

| 9         | 0  | 1  | 0  | 0  | 1  | 1  | Channel 2, Fine Delay          |

| Α         | 0  | 1  | 0  | 1  | 0  | 1  | Channel 2, Falling Edge Adjust |

| В         | 0  | 1  | 0  | 1  | 1  | Х  | Not Used                       |

| С         | 0  | 1  | 1  | 0  | 0  | Χ  | Channel 3, Coarse Delay        |

| D         | 0  | 1  | 1  | 0  | 1  | 1  | Channel 3, Fine Delay          |

| Е         | 0  | 1  | 1  | 1  | 0  | 1  | Channel 3, Falling Edge Adjust |

| F         | 0  | 1  | 1  | 1  | 1  | Х  | Not Used                       |

| Х         | 1  | Х  | Χ  | Х  | Х  | 0  | All Channels, Coarse Delay     |

| Х         | 1  | Х  | Χ  | Х  | Х  | 1  | All Channels, All Functions    |

Figure 5. Voltage vs. Temperature for Thermal Diode String

### Circuit Description (continued)

Figure 6. Synchronous Loading

### Circuit Description (continued)

Figure 7. Data Interface

# Circuit Description (continued)

#### **Timing Inputs**

IN/IN\* and INO/INO\* – IN3/IN3\* are high speed differential inputs which require >300 mV of differential input voltage for reliable switching.

These inputs may receive differential input signals with amplitudes up to 3.3V. This wide range input voltage compliance allows CMOS signals to drive the Edge629 directly.

The inputs may go all the way up to VCC and still not cause any saturation. The Edge629 will operate at full performance under these input conditions.

Do not leave any differential inputs floating as they will be in an indeterminate state. All unused inputs must be tied to either a high or low level. Connecting unused timing inputs to VCC is an acceptable method to make an input high. However, to make an input low, it must be connected to VEE  $\pm 2.0$ V or higher.

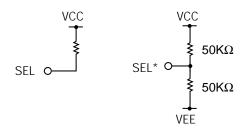

#### Input Mux Select

Each delay channel can select its input from one of two sources. If Mux Select is high (SEL > SEL\*), IN/IN\* will be selected for all four channels. If Mux Select is low (SEL < SEL\*), INO/INO\* - IN3/IN3\* will be selected for each channel.

| SEL/SEL* | Input Source        | Mode         |

|----------|---------------------|--------------|

| 0        | INO/INO* – IN3/IN3* | Pass Through |

| 1        | IN/IN*              | Fanout       |

SEL/SEL\* have internal pull-up/pull-down resistors which, when left floating, place the chip in fanout mode.

#### **Data Interface Digital Inputs**

All data digital inputs are standard, single ended ECL inputs with  $V_{\mbox{\tiny bb}} = -1.3 \mbox{V}$  relative to VCC. However, all digital inputs may receive input signals anywhere between VCC and VEE. This wide input voltage compliance allows CMOS signals to program the Edge629 without causing saturation problems.

# All digital interface inputs are "3.3V rail to rail" CMOS compatible provided VCC = +3.3V and VEE = -2V.

CK, SDI, and UPDATE all have an internal pull-down resistor network to establish a default condition of a logical 0 when left floating. CS has a large ( $\sim 50~\text{K}\Omega$ ) internal pullup resistor to VCC to establish a default condition of a logical 1 when left floating.

For optimal performance, all data interface digital inputs should be static when the Edge 629 is actively delaying signals. (However, it is acceptable if CK continues to run.)

#### **Timing Outputs**

OUTO/OUTO\* – OUT3/OUT3\* are standard differential ECL open emitter outputs.

#### **Compensation Pins**

COMPO, COMP1, COMP2, and COMP3 are op amp compensation pins requiring external 100 pF capacitors to VEE.

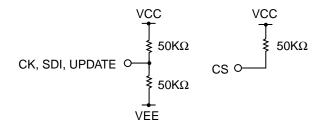

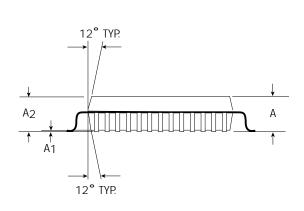

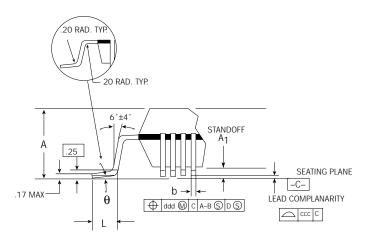

### Package Information

#### 64-Pin TQFP 10 mm x 10 mm x 1.4 mm

Top View

#### Notes:

- 1. All dimensions in millimeters.

- 2. Dimensions shown are nominal with tolerances as indicated.

- 3. L/F: EFTEC 64T copper or equivalent, 0.127mm (.005") or 0.15mm (.006") thick.

- 4. Foot length "L" is measured at gage plane, at 0.25 above the seating plane.

| Dims.             | Tolerance | Value              |

|-------------------|-----------|--------------------|

| A                 | MAX.      | 1.60               |

| A1                |           | .05 min. / .15 max |

| A2                | ±.05      | 1.40               |

| D                 | ±.20      | 12.00              |

| D1                | ±.10      | 10.00              |

| E                 | ±.20      | 12.00              |

| E1                | ±.10      | 10.00              |

| L                 | +.15 /10  | .60                |

| е                 | BASIC     | .50                |

| b                 | ±.05      | .22                |

| θ                 |           | 0° - 7°            |

| ddd               | MAX.      | .08                |

| CCC               | MAX.      | .08                |

| Package Thickness |           | 1.40               |

| Footprint         |           | Body + 2 mm        |

# Recommended Operating Conditions

| Parameter            | Symbol    | Min | Тур | Max  | Units |

|----------------------|-----------|-----|-----|------|-------|

| Total Power Supply   | VCC – VEE | 4.2 | 5.2 | +5.5 | V     |

| Junction Temperature | TJ        | 0   |     | +100 | °C    |

# Absolute Maximum Ratings

| Parameter                                               | Symbol          | Min       | Тур | Max       | Units |

|---------------------------------------------------------|-----------------|-----------|-----|-----------|-------|

| Power Supply                                            | VCC – VEE       | 0         |     | 7.0       | V     |

| Voltage on any Digital Input Pin                        |                 | VEE - 0.5 |     | VCC + 0.5 | V     |

| Voltage on any Analog Input Pin                         |                 | VEE - 0.5 |     | VCC + 0.5 | V     |

| Output Current                                          |                 | -50       |     |           | mA    |

| Storage Temperature                                     | TS              | -65       |     | +150      | °C    |

| Junction Temperature                                    | TJ              |           |     | +150      | °C    |

| Soldering Temperature<br>(5 seconds, .25" from the pin) | TSOL            |           |     | +260      | °C    |

| $\theta_{JC}$ (to top of case)                          | θЈС             |           | 1.5 |           | °C    |

| θ <sub>JA</sub> (@ still air)                           | θ <sub>JA</sub> |           | 28  |           | °C    |

| θ <sub>JA</sub> (@ 400 LFPM)                            | θJA             |           | 21  |           | °C    |

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these, or any other conditions beyond those listed, is not implied. Exposure to absolute maximum conditions for extended periods may affect device reliability.

# DC Characteristics

| Parameter                                      | Symbol          | Min       | Тур       | Max       | Units |

|------------------------------------------------|-----------------|-----------|-----------|-----------|-------|

| Timing Inputs<br>(IN/IN*, INO/INO* – IN3/IN3*) |                 |           |           |           |       |

| Differential Input Voltage                     | IN – IN*        | .3        |           | VCC – VEE | V     |

| Input High Voltage Range                       | VIH             | VEE + 2.0 |           | VCC       | V     |

| Input Low Voltage Range                        | VIL             | VEE + 2.0 |           | VIH – .3  | V     |

| Input High Current                             | IIH             | -100      |           | +100      | μΑ    |

| Input Low Current                              | IIL             | -100      |           | +100      | μΑ    |

| Select Input (SEL/SEL*)                        |                 |           |           |           |       |

| Input High Voltage                             | SEL – SEL*      | .3        |           | VCC – VEE | V     |

| Input Low Voltage                              | SEL* – SEL      | .3        |           | VCC – VEE | V     |

| Input High Common Mode Range                   | VIH             | VEE + 2.0 |           | VCC       | V     |

| Input Low Common Mode Range                    | VIL             | VEE + 2.0 |           | VIH – .3  | V     |

| Input High Current                             | IIH             |           |           | 250       | μΑ    |

| Input Low Current                              | IIL             |           |           | 250       | μΑ    |

| Programming Inputs (CK, UPDATE, CS, SDI)       |                 |           |           |           |       |

| Input High Voltage                             | VIH             | VCC - 1.1 |           | VCC       | V     |

| Input Low Voltage                              | VIL             | VEE + 2.0 |           | VCC - 1.5 | V     |

| Input High Current                             | IIH             |           |           | 250       | μΑ    |

| Input Low Current                              | IIL             |           |           | 250       | μΑ    |

| Digital Outputs                                |                 |           |           |           |       |

| Digital Output High Voltage                    | OUT – OUT*      | 600       | 690       |           | mV    |

| Digital Output Low Voltage                     | OUT* – OUT      | 600       | 690       |           | mV    |

| Output Common Mode Range                       | OUT + OUT*<br>2 | VCC - 1.5 | VCC - 1.3 | VCC - 1.1 | V     |

| Output Current                                 | lout            |           |           | 30        | mA    |

| Power Supply Current                           |                 |           |           |           |       |

| VCC - VEE = 4.2V                               | IEE             |           | 561       | 900       | mA    |

| VCC – VEE = 5.2V                               | IEE             |           | 604       | 900       | mA    |

| VCC - VEE = 5.5V                               | IEE             |           | 613       | 900       | mA    |

# AC Characteristics

| Parameter                                                                                                                                                                                            | Symbol                                  | Min               | Тур                          | Max                                       | Units                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------|------------------------------|-------------------------------------------|----------------------------------------------------|

| Timing Inputs/Outputs                                                                                                                                                                                |                                         |                   |                              |                                           |                                                    |

| Minimum Propagation Delay (Note 2) IN to OUT (0,3) INO, 3 to OUT (0,3) ΔTpd, FD Disabled to FD=0 ΔTpd, FEA Disabled to FEA=0                                                                         | Tpd Min<br>Tpd Min<br>∆Tpd<br>∆Tpd      | 1.282<br>1.406    | 1.357<br>1.481<br>320<br>950 | 1.432<br>1.556                            | ns<br>ns<br>ps<br>ps                               |

| Rising Edge/Falling Edge Propagation<br>Delay Difference (FEA disabled)                                                                                                                              | Tpd+ - Tpd-                             |                   | 3                            | 10                                        | ps                                                 |

| Channel-to-Channel Skew (Note 2) IN to OUT (0,3) (Fanout Mode) IN (0,3) to OUT (0,3)                                                                                                                 | Tskew1<br>Tskew2                        |                   | 10<br>15                     | 45<br>50                                  | ps<br>ps                                           |

| Programmable Delay (Note 2) Coarse Delay Fine Delay                                                                                                                                                  | Tspan_Coarse<br>Tspan_Fine              | 5.5<br>110        | 6.0<br>150                   | 6.5<br>180                                | ns<br>ps                                           |

| Falling Edge Adjust (SFE = 1) (Note 1)                                                                                                                                                               | FEA                                     | ±200              | ±250                         | ±300                                      | ps                                                 |

| Programmable Delay Step Size (Note 3) Coarse Delay Fine Delay Falling Edge Adjust                                                                                                                    | Tstep_Coarse<br>Tstep_Fine<br>Tstep_FEA | 1.0<br>1.0<br>1.0 | 95<br>5<br>5                 | 110<br>7<br>7                             | ps<br>ps<br>ps                                     |

| Maximum Operating Frequency (FEA Enabled)                                                                                                                                                            | Fmax                                    | 1.0               |                              |                                           | GHz                                                |

| Maximum Operating Frequency (FEA Disabled)                                                                                                                                                           | Fmax                                    | 1.3               |                              |                                           | GHz                                                |

| Minimum Pulse Width (at outputs)                                                                                                                                                                     | PW min                                  | 350               |                              |                                           | ps                                                 |

| Output Rise and Fall Times (20% - 80%)                                                                                                                                                               | Tr/Tf                                   |                   | 110                          | 150                                       | ps                                                 |

| Temperature Coefficient (vs. Die Temp)  CD = Min, FD & FEA Disabled  CD = Max, FD & FEA Disabled  CD & FD = Min, FEA Disabled  CD & FD = Max, FEA Disabled  CD, FD, & FEA = Min  CD, FD, & FEA = Max | ΔΤpd/ΔΤ                                 |                   |                              | 2.4<br>13.3<br>3.3<br>15.1<br>5.2<br>18.8 | ps/°C<br>ps/°C<br>ps/°C<br>ps/°C<br>ps/°C<br>ps/°C |

| Total Timing Error                                                                                                                                                                                   |                                         |                   |                              |                                           |                                                    |

| ΔTpd vs. Frequency Channel-to-Channel Crosstalk ΔTpd vs. Duty Cycle Jitter @ Minimum Delay Jitter @ Maximum Delay                                                                                    |                                         |                   | 20<br>2<br>20                | 10<br>1<br>5                              | ps<br>ps<br>ps<br>ps                               |

Test Conditions (unless otherwise specified): "Recommended Operating Conditions."

### AC Characteristics (continued)

Test Conditions (unless otherwise specified): "Recommended Operating Conditions."

- Note 1: Tested with an input pulse = 50 ns. This parameter is guaranteed by characterization for input pulse widths  $\geq 700$  ps.

- Note 2: Coarse Delay = 0, Fine Delay and Falling Edge Adjust disabled. Case Temperature = 50°C.

- Note 3: Coarse Delay is monotonic. Fine Delay is Monotonic. Since the fine delay spans close to 2 LSBs of coarse delay, the summation of digital codes for coarse and fine delays is not monotonic. Proper binary searching using both the coarse and fine delays is achieved first with the coarse (with SFD=1), and then with the fine delays as separate searches.

| Parameter                 | Symbol | Min | Тур | Max | Units |

|---------------------------|--------|-----|-----|-----|-------|

| Data Interface            |        |     |     |     |       |

| Set Up Time               |        |     |     |     |       |

| SDI to CK ↑               | Tsu    | 10  |     |     | ns    |

| CS to CK ↑                | Tsu    | 10  |     |     | ns    |

| UPDATE to CK $\downarrow$ | Tsu    | 20  |     |     | ns    |

| Hold Time                 |        |     |     |     |       |

| CK ↑ to SDI               | Th     | 4   |     |     | ns    |

| CK ↑ to CS                | Th     | 4   |     |     | ns    |

| CK ↓ to UPDATE            | Th     | 4   |     |     | ns    |

| Minimum Pulse Widths      |        |     |     |     |       |

| CK High                   |        | 13  |     |     | ns    |

| CK Low                    |        | 13  |     |     | ns    |

| CK Period                 | T      | 30  |     |     | ns    |

| DAC Settling Time         |        |     |     | 1   | μs    |

Test Conditions (unless otherwise specified): "Recommended Operating Conditions."

AC Characteristics are guaranteed by design and characterization. Not production tested.

# Ordering Infor mation

| Model Number | Package                                           |  |  |

|--------------|---------------------------------------------------|--|--|

| E629AXF      | 10 x 10 x 1.4mm TQFP<br>w/Exposed Heatsink on Top |  |  |

| EVM629AXF    | Edge629 Evaluation Board                          |  |  |

# Contact Infor mation

Semtech Corporation

Test and Measurement Division

10021 Willow Creek Rd., San Diego, CA 92131

Phone: (858)695-1808 FAX (858)695-2633