# Regarding the change of names mentioned in the document, such as Mitsubishi Electric and Mitsubishi XX, to Renesas Technology Corp.

The semiconductor operations of Hitachi and Mitsubishi Electric were transferred to Renesas Technology Corporation on April 1st 2003. These operations include microcomputer, logic, analog and discrete devices, and memory chips other than DRAMs (flash memory, SRAMs etc.) Accordingly, although Mitsubishi Electric, Mitsubishi Electric Corporation, Mitsubishi Semiconductors, and other Mitsubishi brand names are mentioned in the document, these names have in fact all been changed to Renesas Technology Corp. Thank you for your understanding. Except for our corporate trademark, logo and corporate statement, no changes whatsoever have been made to the contents of the document, and these changes do not constitute any alteration to the contents of the document itself.

Note: Mitsubishi Electric will continue the business operations of high frequency & optical devices and power devices.

Renesas Technology Corp. Customer Support Dept. April 1, 2003

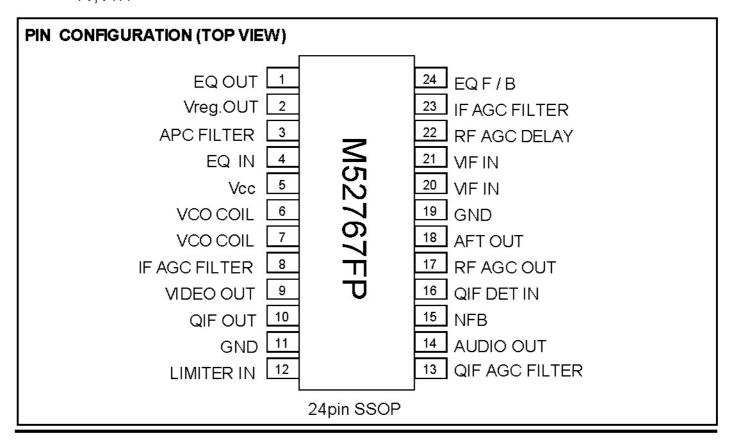

PLL-SPLIT VIF/SIF

#### DESCRIPTION

M52767FP is a semiconductor integrated circuit consisting of VIF/SIF signal processing for CTVs and VCRs. M52767FP provide low cost and high performance system with the coil-less AFT.

#### **FEATURES**

- ■Coil-less AFT.

- ■PLL FM demodulation for Audio. No external parts and adjustment.

- ■The PLL-SPLIT system provides good sound sensitivity and reduces buzz.

- ■Video output is 1.3Vp-p through EQ AMP.

- Easy to add Buzz canceler.

- ■Hi speed IF AGC.

- ■Built-in QIF AGC.

- ■Improve over modulation characteristics and Vcc ripple rejection.

## RECOMMENDED OPERATING CONDITIONS

Supply Voltage Range (Vcc) • • • • • • 4.7 to 5.3 V Rated Supply Voltage (Vcc) • • • • • • 5.0 V

#### APPLICATION

TV,VTR

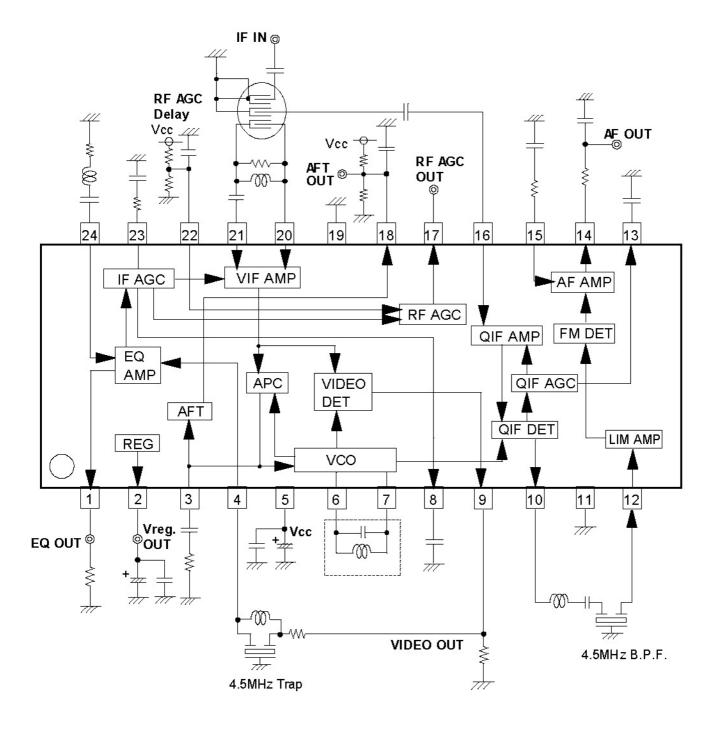

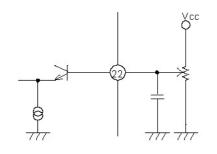

## **BLOCK DIAGRAM and PERIPHERAL CIRCUIT**

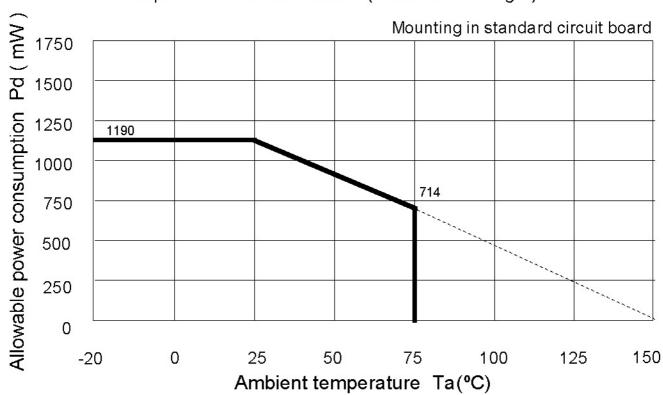

## **ABSOLUTE MAXIMUM RATINGS**

(Ta = 25°C, unless otherwise noted)

| Parameter                | Symbol | Ratings     | Unit | Note |

|--------------------------|--------|-------------|------|------|

| Supply<br>Voltage 1      | Vcc    | 6.0         | >    |      |

| Power<br>Consumption     | Pd     | 1190        | mW   |      |

| Operating<br>Temperature | Topr   | -20 to +75  | °C   |      |

| Storage<br>Temperature   | Tstg   | -40 to +150 | °C   |      |

## Temperature Characteristics ( maximum ratings )

PLL-SPLIT VIF/SIF

# **ELECTRICAL CHARACTERISTICS**

**VIF Section**

(Vcc=5V,Ta=25°C unless otherwise noted)

|     |                             |              | Tart            | T a at        | Innut          |             | Measurement                                       | Limits |     |      |      |      |

|-----|-----------------------------|--------------|-----------------|---------------|----------------|-------------|---------------------------------------------------|--------|-----|------|------|------|

| No. | Parameter                   | Symbol       | Test<br>Circuit | Test<br>Point | Input<br>Point | Input<br>SG | switches set to position 1 unless otherwise noted | MIN    | TYP | MAX  | Unit | Note |

| 1   | Circuit Current 1<br>Vcc=5V | lcc1         | 1               | Α             | _              | -           | SW5=2                                             | 36     | 45  | 54   | mA   |      |

| 2   | Vreg.<br>Output Voltage     | Vreg.        | 1               | TP2           | (-)            | -11         |                                                   | 3.2    | 3.5 | 3.8  | V    |      |

| 3   | Video Output<br>Voltage 9   | Vo det9      | 1               | TP9           | VIF<br>IN      | SG1         |                                                   | 0.46   | 0.6 | 0.74 | Vp-p |      |

| 4   | Video Output<br>Voltage 1   | Vo det       | 1               | TP1A          | VIF<br>IN      | SG1         |                                                   | 1.0    | 1.3 | 1.6  | Vp-p |      |

| 5   | Video S/N                   | Video<br>S/N | 1               | TP1B          | VIF<br>IN      | SG2         | SW1=2                                             | 51     | 56  | _    | dB   | 1    |

| 6   | Video Band Width            | BW           | 1               | TP1A          | VIF<br>IN      | SG3         | SW8=2<br>V8=Variable                              | 5.0    | 7.0 | _    | MHz  | 2    |

| 7   | Input Sensitiv ity          | VIN<br>MIN   | 1               | TP1A          | VIF<br>IN      | SG4         |                                                   | _      | 48  | 52   | dΒμ  | 3    |

| 8   | Maximum Allowable<br>Input  | VIN<br>MAX   | 1               | TP1A          | VIF<br>IN      | SG5         |                                                   | 104    | 110 | _    | dΒμ  | 4    |

| 9   | AGC Control<br>Range Input  | GR           | -               | =             | -              | -           |                                                   | 55     | 62  | _    | dB   | 5    |

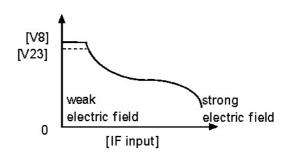

| 10  | IF AGC Voltage 1            | V8           | 1               | TP8           | VIF<br>IN      | SG6         |                                                   | 2.8    | 3.1 | 3.4  | ٧    |      |

| 11  | IF AGC Voltage 2            | V23          | 1               | TP23          | VIF<br>IN      | SG6         |                                                   | 2.8    | 3.1 | 3.4  | ٧    |      |

| 12  | Maximum RF AGC<br>Voltage   | V17H         | 1               | TP17          | VIF<br>IN      | SG6         |                                                   | 4.1    | 4.7 | -    | ٧    |      |

| 13  | Minimum RF AGC<br>Voltage   | V17L         | 1               | TP17          | VIF<br>IN      | SG7         |                                                   | -      | 0.1 | 0.5  | ٧    |      |

| 14  | RF AGC<br>Delay Point       | V17          | 1               | TP17          | VIF<br>IN      | SG8         |                                                   | 86     | 89  | 92   | dΒμ  | 6    |

| 15  | Capture Range<br>U          | CL-U         | 1               | TP1A          | VIF<br>IN      | SG9         |                                                   | 1.0    | 1.5 | =    | MHz  | 7    |

| 16  | Capture Range<br>L          | CL-L         | 1               | TP1A          | VIF<br>IN      | SG9         |                                                   | 1.4    | 2.0 | _    | MHz  | 8    |

| 17  | Capture Range<br>T          | CL-T         | -               | =1            | -              | _           |                                                   | 2.7    | 3.5 | _    | MHz  | 9    |

## PLL-SPLIT VIF/SIF

|     |                        |              | Toot            | Test | Innut          | Immust      | Measurement                                       | Limits     |      |     |            |      |

|-----|------------------------|--------------|-----------------|------|----------------|-------------|---------------------------------------------------|------------|------|-----|------------|------|

| No. | Parameter              | Symbol       | Test<br>Circuit |      | Input<br>Point | Input<br>SG | switches set to position 1 unless otherwise noted | MIN        | TYP  | мах | Unit       | Note |

| 18  | AFT Sensitivity        | μ            | 1               | TP18 | VIF<br>IN      | SG10        |                                                   | 20         | 30   | 70  | mV/<br>kHz | 10   |

| 19  | AFT Maximum<br>Voltage | V18H         | 1               | TP18 | VIF<br>IN      | SG10        |                                                   | 3.85       | 4.15 | -   | V          | 10   |

| 20  | AFT Minimum<br>Voltage | V18L         | 1               | TP18 | VIF<br>IN      | SG10        |                                                   | <b>—</b> p | 0.7  | 1.2 | V          | 10   |

| 21  | AFT defeat             | AFT<br>def 1 | 1               | TP18 | VIF<br>IN      | -           |                                                   | 2.2        | 2.5  | 2.8 | V          |      |

| 22  | Inter Modulation       | IM           | 1               | TP1A | VIF<br>IN      | SG11        | SW8=2<br>V8=Variable                              | 35         | 40   | L   | dB         | 11   |

| 23  | Differential<br>Gain   | DG           | 1               | TP1A | VIF<br>IN      | SG12        |                                                   | _          | 2    | 5   | %          |      |

| 24  | Differential<br>Phase  | DP           | 1               | TP1A | VIF<br>IN      | SG12        |                                                   | _          | 2    | 5   | deg        |      |

| 25  | Sync. tip level        | V1<br>SYNC   | 1               | TP1A | VIF<br>IN      | SG2         |                                                   | 0.8        | 1.1  | 1.4 | V          |      |

## PLL-SPLIT VIF/SIF

## SIF Section

# (Vcc=5V,Ta=25°C unless otherwise noted)

|     |                                  |             | T - 4           | Test | Input            | 1           | Measurement                                       |     | Limits |      |       |      |

|-----|----------------------------------|-------------|-----------------|------|------------------|-------------|---------------------------------------------------|-----|--------|------|-------|------|

| No. | Parameter                        | Symbol      | Test<br>Circuit |      | Input<br>Point   | Input<br>SG | switches set to position 1 unless otherwise noted | MIN | TYP    | MAX  | Unit  | Note |

| 26  | QIF Output<br>Voltage 1          | QIF1        | 1               | TP10 | VIF IN<br>QIF IN | SG2<br>SG13 |                                                   | 94  | 100    | 106  | dΒμ   |      |

| 27  | QIF Output<br>Voltage 2          | QIF2        | 1               | TP10 | VIF IN<br>QIF IN | SG2<br>SG14 |                                                   | 94  | 100    | 106  | dΒμ   |      |

| 28  | SIF Detection<br>Output          | Vos         | 1               | TP10 | VIF<br>IN        | SG15        |                                                   | 86  | 92     | 98   | dΒμ   |      |

| 29  | AF Output<br>(4.5MHz)            | VoAF<br>1   | 1               | TP14 | SIF<br>IN        | SG16        |                                                   | 460 | 680    | 1000 | mVrms |      |

| 30  | AFOutput Distortion<br>(4.5MHz)  | THD<br>AF 1 | 1               | TP14 | SIF<br>IN        | SG16        |                                                   | _   | 0.3    | 0.9  | %     |      |

| 31  | Limiting Sensitivity<br>(4.5MHz) | LIM<br>1    | 1               | TP14 | SIF<br>IN        | SG17        |                                                   | _   | 42     | 55   | dΒμ   | 12   |

| 32  | AM Rejection<br>(4.5MHz)         | AMR<br>1    | 1               | TP14 | SIF<br>IN        | SG18        |                                                   | 55  | 62     | _    | dB    | 13   |

| 33  | AF S/N (4.5MHz)                  | AF<br>S/N 1 | 1               | TP14 | SIF<br>IN        | SG19        |                                                   | 55  | 62     | E-   | dB    | 14   |

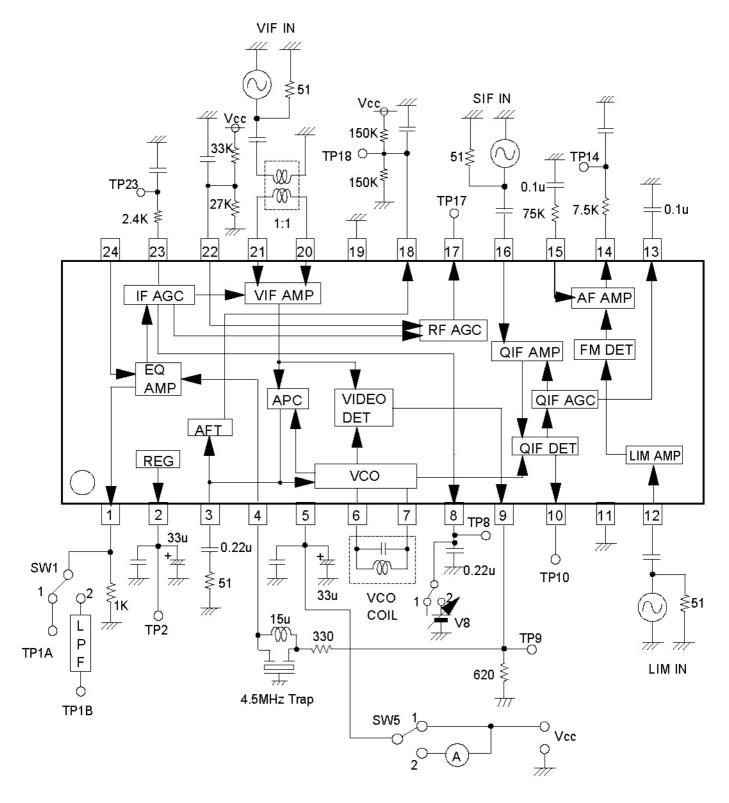

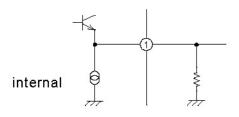

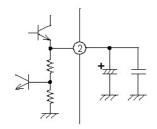

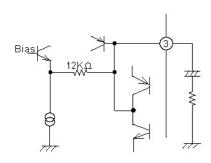

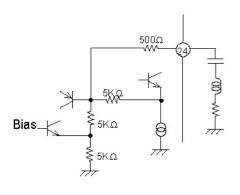

## **Measuring Circuit Diagram**

- Note 1) All the capacitors are 0.01µF, unless otherwise noted.

- 2) The Measuring Circuit is Mitsubishi standard evaluation fixture.

## PLL-SPLIT VIF/SIF

# **INPUT SIGNAL**

| SG | 50Ω Termination                                                                  |

|----|----------------------------------------------------------------------------------|

| 1  | fo = 45.75 MHz AM 20 KHz 77.8 % 90 dBµ                                           |

| 2  | fo = 45.75 MHz 90 dBµ Cw                                                         |

| 3  | f1 = 45.75 MHz 90 dBµ Cw f2 = Frequency Variable 70 dBµ Cw  Mixed Signal         |

| 4  | fo = 45.75 MHz AM 20 KHz 77.8% Level Variable                                    |

| 5  | fo = 45.75 MHz AM 20 KHz 14.0% Level Variable                                    |

| 6  | f0= 45.75 MHz 80 dBµ Cw                                                          |

| 7  | fo = 45.75 MHz 110 dBµ Cw                                                        |

| 8  | fo = 45.75 MHz Cw Level Variable                                                 |

| 9  | fo = Frequency Variable AM 20 KHz 77.8 % 90 dBµ                                  |

| 10 | f0 = Frequency Variable 90 dBµ Cw                                                |

| 11 | f1 = 45.75 MHz 90 dBµ Cw<br>f2 = 42.17 MHz 80 dBµ Cw<br>f3 = 41.25 MHz 80 dBµ Cw |

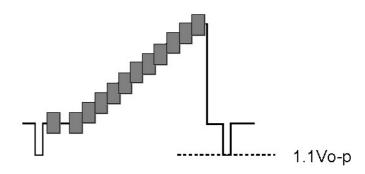

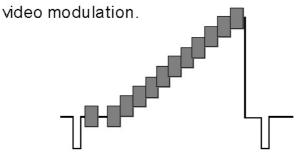

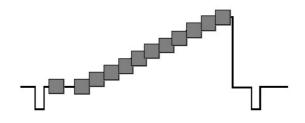

| 12 | f0 = 45.75 MHz 87.5 % TV modulation Ten-step waveform<br>Sync Tip Level 90 dBµ   |

| 13 | f1 = 41.25 MHz 95 dBµ Cw                                                         |

| 14 | f1 = 41.25 MHz 75 dBµ Cw                                                         |

| 15 | f1 = 45.75 MHz 90 dBµ Cw                                                         |

| 16 | fo = 4.5 MHz 90 dBµ FM 400 Hz ±25 KHzdev                                         |

| 17 | fo = 4.5 MHz Level Variable FM 400Hz ±25KHzdev                                   |

| 18 | fo = 4.5 MHz 90 dBµ AM 400 Hz 30 %                                               |

| 19 | fo = 4.5 MHz 90 dBµ Cw                                                           |

| 20 | fo = 4.5 MHz Level Variable Cw                                                   |

## **Notes**

#### 1. Video S/N

Input SG2 to VIF IN and measure the video out(Pin 1) noise in r.m.s at TP1B through a 5MHz (-3dB) L.P.F.

$$S/N=20 \log \left( \frac{0.7 \times Vo \det}{NOISE} \right)$$

[dB]

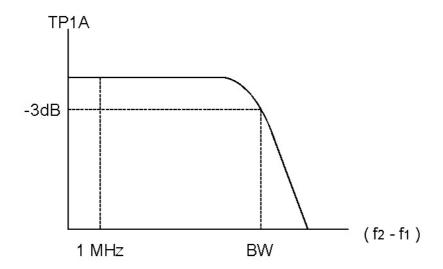

#### 2. Video Band Width: BW

- 1. Measure the 1MHz component level of Video output TP1A with a spectrum analyzer when SG3(f2=44.75MHz) is input to VIF IN. At that time, measure the voltage at TP8 with SW8, set to position 2, and then fix V8 at that voltage.

- 2. Reduce f2 and measure the value of (f2-f1) when the (f2-f1) component level reaches -3dB from the 1MHz component level as shown below.

#### 3. Input Sensitivity: VIN MIN

Input SG4 (Vi=90dB $\mu$ ) to VIF IN, and then gradually reduce Vi and measure the input level when the 20KHz component of Video output TP1A reaches - 3dB from Vo det level.

#### 4. Maximum Allowable Input: VIN MAX

- 1. Input SG5 (Vi=90dBµ) to VIF IN, and measure the level of the 20KHz component of Video output.

- 2. Gradually increase the Vi of SG and measure the input level when the output reaches -3dB.

5. AGC Control Range: GR

GR = VIN MAX - VIN MIN [dB]

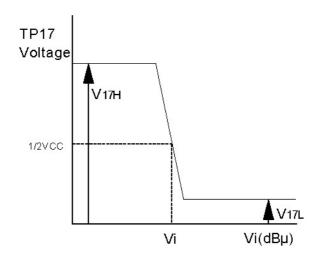

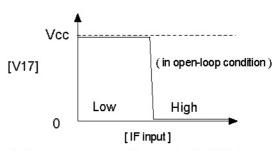

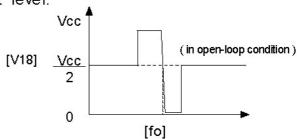

6. RF AGC Operating Voltage: V17

Input SG8 to VIF IN and gradually reduce Vi and then measure the input level when RF AGC output TP17 reaches 1/2 VCC, as shown below.

## 7. Capture range: CL - U

- 1. Increase the frequency of SG9 until the VCO is out of locked-oscillation.

- 2. And decrease the frequency of SG9 and measure the frequency fU when the VCO is locked.

# 8. Capture range: CL - L

- 1. Decrease the frequency of SG9 until the VCO is out of locked-oscillation.

- 2. And increase the frequency of SG9 and measure the frequency fL when the VCO is locked.

$$CL - L = 45.75 - fL$$

[MHz]

9. Capture range: CL - T

$$CL-T=CL-U+CL-L$$

[MHz]

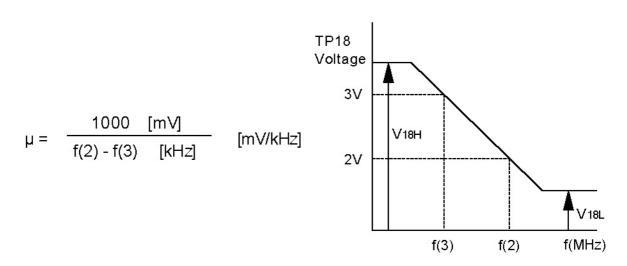

## 10. AFT sensitivity μ, Maximum AFT voltage V18H , Minimum AFT voltage V18L

- 1. Input SG10 to VIF IN, and set the frequency of SG10 so that the voltage of AFT output TP18 is 3[V]. This frequency is named f(3).

- 2. Set the frequency of SG10 so that the AFT output voltage is 2[V]. This frequency is named f(2)

- 3. IN the graph, maximum and minimum DC voltage are V18H and V18L, respectively.

## 11. Inter modulation: IM

- 1. Input SG11 to VIF IN, and measure video output TP9 with an oscilloscope.

- 2. Adjust AGC filter voltage V23 so that the minimum DC level of the output waveform is 1.5V.

- At this time, measure TP9 with a spectrum analyzer.

The inter modulation is defined as a difference between 0.92MHz and 3.58 MHz frequency components.

11

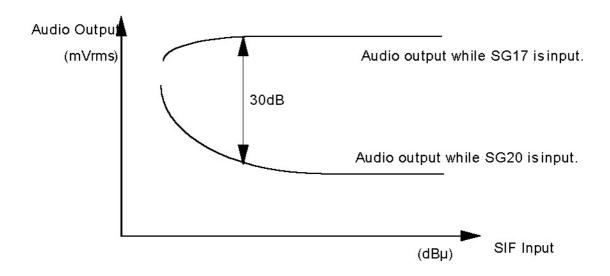

## 12. Limiting Sensitivity: LIM

- 1. Input SG17 to SIF IN, and measure the 400Hz component level of AF output TP14.

- 2. Input SG20 to SIF IN, and measure the 400Hz component level of AF output TP14.

- 3. The input limiting sensitivity is defined as the input level when a difference between each 400Hz components of audio output (TP14) is 30dB, as shown below.

## 13. AM Rejection: AMR

- 1. Input SG18 to SIF IN ,and measure the output level of Audio output (TP14). This level is named VAM.

- 2. AMR is;  $AMR = 20log \left( \frac{VoAF (mVr.m.s)}{VAM (mVr.m.s)} \right)$  [dB]

## 14. AF S/N: AF S/N

- 1. Input SG19 to SIF IN ,and measure the output noise level of Audio output (TP14). This level is named VN.

- 2. S/N is;  $S/N = 20log \left( \frac{VoAF (mVr.m.s)}{VN (mVr.m.s)} \right)$  [dB]

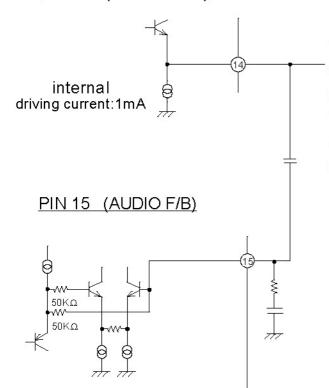

## Pin peripheral circuit explanation

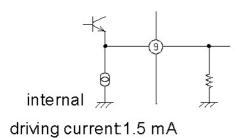

## Pin 1 (EQ OUTPUT)

driving current: 1mA

An output amplitude is positive 1.3Vp-p in case of 87.5% video modulation.

# Pin 2 (REG.OUTPUT)

It is a regulated 3.5V output which has current drive capability of approximately 5mA

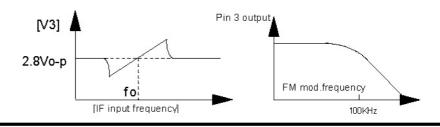

## Pin 3 (APC FILTER)

In the locked state, the cut-off frequency of the filter is adjusted effectively by an external resistor so that it will be in the range of around 30 to 200kHz.

In case the cut-off frequency is lower, the pull-in speed becomes slow. On the other hand, a higher cut-off frequency widen the pull-in range and band width, which results in a degradation in the S/N ratio. So, in the actual TV system design, the appropriate constant should be chosen for getting desirable performance considering above conditions.

#### PLL-SPLIT VIF/SIF

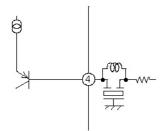

## PIN 4 (EQ INPUT)

The input is Open Base.

If DC information is not input to Pin 9,IF AGC dose not work normally.

Please pay attention.

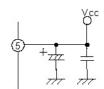

#### PIN 5 (Vcc)

It is Vcc pin (only one Vcc pin in this IC)

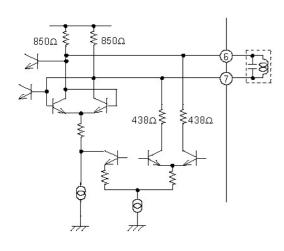

## PIN 6 and 7 (VCO COIL)

Connecting a tuning coil and capacitor to these pins enables an oscillation.

The oscillation frequency is tuned in f0.

In the actual adjustment, the coil is tuned so that the AFT voltage is reached to Vcc/2 with f0 as an input.

The printed pattern around these pins should be designed carefully to prevent an pull-in error of VCO, caused by the leakage interference from the large signal level oscillator to adjacent pins. The interconnection should be designed as short as possible.

In case the printed pattern has the interference problem, a capacitor of about 1pF is connected between pin 6 or 7 and GND so as to cancel the interference and keep enough pull-in range even in a low input level.

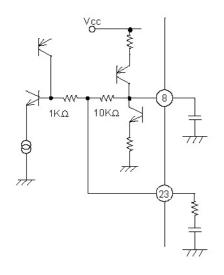

## PIN 8, PIN 23 (IF AGC FILTER)

2-pin filter characteristics are available by utilizing the dynamic AGC circuit.

And AGC speed can be changed, if pin-23 on the external resistors is variable.

## PIN 9 (VIDEO OUTPUT)

An output amplitude is positive 0.6Vp-p in case of 87.5%

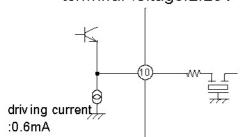

## PIN 10 (QIF OUTPUT)

terminal voltage: 2.25V

In the split system, the carrier signal to SIF provided from pin 10 through an emitter follower.

And, please open this pin, when it is used INTER.

## PIN 11 (GND)

This is GND of the SIF.

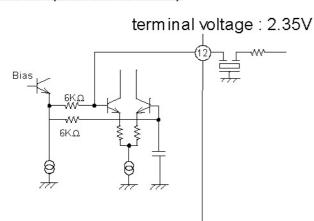

## PIN 12 (LIMITER INPUT)

The input impedance is  $6k\Omega$

## PIN 13 (QIF AGC FILTER)

AGC speed can be changed by this pin's external capacity.

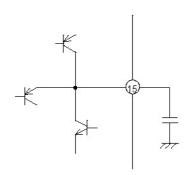

# PIN 14 (AF OUTPUT)

The FM detector can respond to several kinds of SIF signals without an adjustment and external components by adopting the PLL technique. The capacitor between pin 14 and 15, which fixes the deemphasis characteristics, can be determined considering the combination of an equivalent resistance of the IC and this capacitor itself.

Frequency characteristic of audio output is decided with 15-pin external capacitor value. And audio output amplitude can make it small when it connected 15-pin external capacitor and resistance in series.

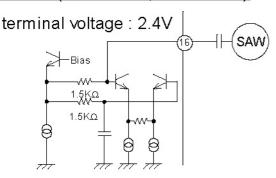

## PIN 16 (QIF INPUT, INTER SW)

The input impedance is  $1.5k\Omega$ .

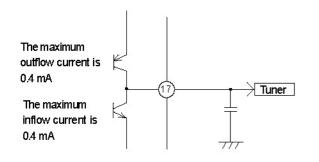

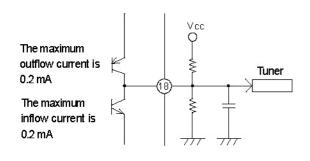

#### PIN 17 (RF AGC OUTPUT)

A current mode output is available in the reverse AGC operation.

Connecting a nonpolarity capacitor of 1 µF between pin 17 and pin 22 improves AGC operating speed.

In that case, the capacitors between pin17/pin22 and ground should be removed.

## PIN 18 (AFT OUTPUT)

Since an AFT output is provided by a high impedance source, the detection sensitivity can be set by an external resistor.

The muting operation will be on in following two cases;

- 1) the APC is out of locking,

- 2) the video output becomes small enough in a low input level.

note) AFT maximum voltage is about 4.2 V.RF AGC maximum voltage is about 4.7 V. Those do not increase it over. Please pay attention.

## PIN 19 (GND)

This is GND other than SIF part.

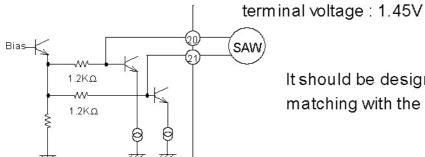

## PIN 20, PIN 21 (VIF INPUT)

(MV)

It should be designed considering careful impedance matching with the SAW filter.

## PIN 22 (RF AGC DELAY)

An applied voltage to the pin 22 is for changing a RF AGC delay point.

## PIN 24 (EQ F/B)

Both the external coil and capacitor determine the frequency response of EQ output.

The series connected resistor is for damping.

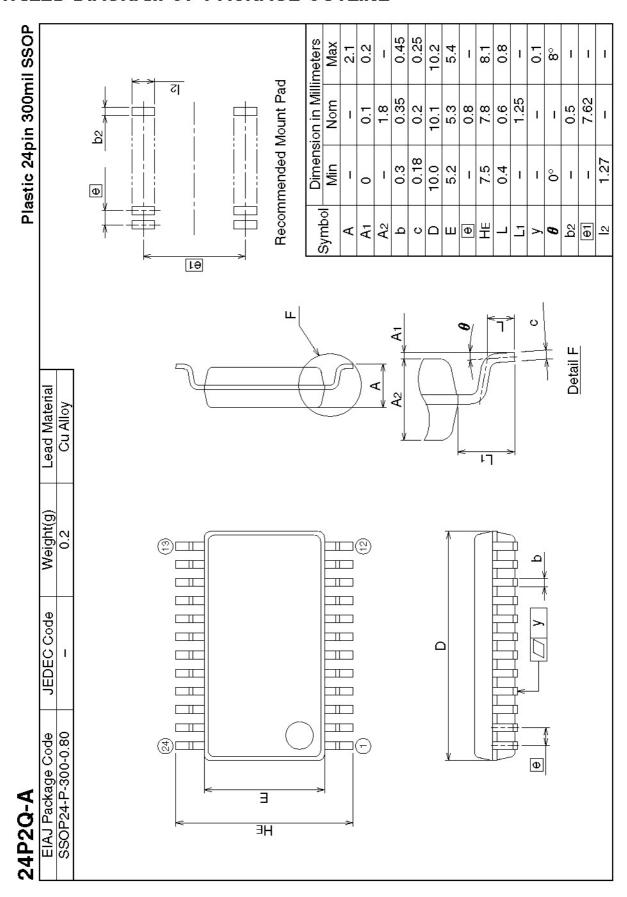

## **DETAILED DIAGRAM OF PACKAGE OUTLINE**

Keep safety first in your circuit designs!

•Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

#### Notes regarding these materials

- •These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.

- •Mitsubishi Electric Corporation assumes no responsibility for any damage, or infringement of any third-party's rights, originating in the use of any product data, diagrams, charts, programs, algorithms, or circuit application examples contained in these materials.

- •All information contained in these materials, including product data, diagrams, charts, programs and algorithms represents information on products at the time of publication of these materials, and are subject to change by Mitsubishi Electric Corporation without notice due to product improvements or other reasons. It is therefore recommended that customers contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for the latest product information before purchasing a product listed herein.

The information described here may contain technical inaccuracies or typographical errors. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability, or other loss rising from these inaccuracies or errors.

Please also pay attention to information published by Mitsubishi Electric Corporation by various means, including the Mitsubishi Semiconductor home page (http://www.mitsubishichips.com).

- •When using any or all of the information contained in these materials, including product data, diagrams, charts, programs, and algorithms, please be sure to evaluate all information as a total system before making a final decision on the applicability of the information and products. Mitsubishi Electric Corporation assumes no responsibility for any damage, liability or other loss resulting from the information contained herein.

- •Mitsubishi Electric Corporation semiconductors are not designed or manufactured for use in a device or system that is used under circumstances in which human life is potentially at stake. Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor when considering the use of a product contained herein for any specific purposes, such as apparatus or systems for transportation, vehicular, medical, aerospace, nuclear, or undersea repeater use.

- •The prior written approval of Mitsubishi Electric Corporation is necessary to reprint or reproduce in whole or in part these materials.

- •If these products or technologies are subject to the Japanese export control restrictions, they must be exported under a license from the Japanese government and cannot be imported into a country other than the approved destination.

Any diversion or reexport contrary to the export control laws and regulations of Japan and/or the country of destination is prohibited.

•Please contact Mitsubishi Electric Corporation or an authorized Mitsubishi Semiconductor product distributor for further details on these materials or the products contained therein.