# M65677FP

# Digital NTSC/PAL Encoder

REJ03F0189-0201 Rev.2.01 Mar 31, 2008

## **Description**

The M65677FP encodes CCIR601 or CCIR656 format Y/Cb/Cr data into analog NTSC and PAL video signals, including Digital Signal Processing functions such as Closed Caption encoding. Overlay OSD, Anti Video Copy Processing Note1 e.t.c. It also includes peripheral processing function such as 10 bit DAC e.t.c., so that low cost and compact system can be realized.

### **Features**

- Macrovision's video anti copy process Rev 7.01 supported Note1

- Overlay CGMS signal online 20/283 for 525/60 Note3

- Generate CRCC for CGMS Signal

- Overlay WSS signal online 23 for 625/50 Note4

- Color adjustment (TINT/color control)

- NTSC, B/G PAL or MPAL Video Outputs

- Component Y/C Video (S-Video) and CVBS or Y/U/V Outputs

- Supporting CCIR601 and CCIR656 format data

- Closed Caption Manager online 21/284 for NTSC

- Generate ODD parity for Closed Caption Manager

- H/V Sync and Composite generating

- Overlay Digital OSD Supporting Y/Cb/Cr 4:4:4

- Over sampling Filter

- 2 ch 10 bit DAC and 3 ch 6 dB Amp Note2

- 3.3 V I/O interface

- I<sup>2</sup>C Bus Interface for Controls

- Power down mode

- Notes: 1. This device is protected by U.S. patent numbers 4631603, 4577216 and 4819098 and other intellectual property rights. The use of Macrovision Corporation's copy protection technology in the device must be authorized by Macrovision and is intended for home and other limited pay-par-view uses only, unless otherwise authorized in writing by Macrovision. Reverse engineering or disassembly is prohibited.

- 2. 6 dB Amp max. output is 1.0 Vp-p

- 3. Copy Generation Management System-A (IEC1880)

- 4. Wide Screen Signaling (ETS300 294)

## **Application**

DVB, DVD, Digital CATV, Video CD

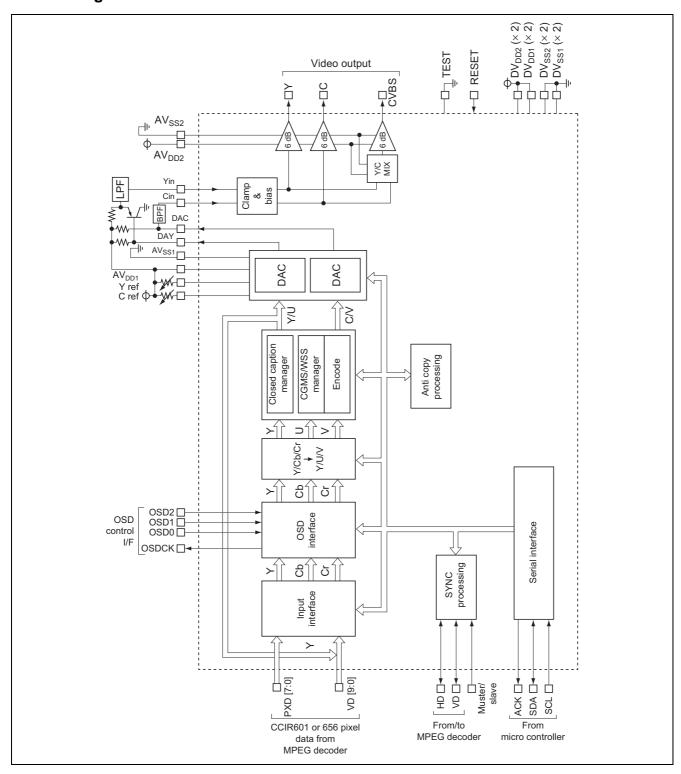

## **Block Diagram**

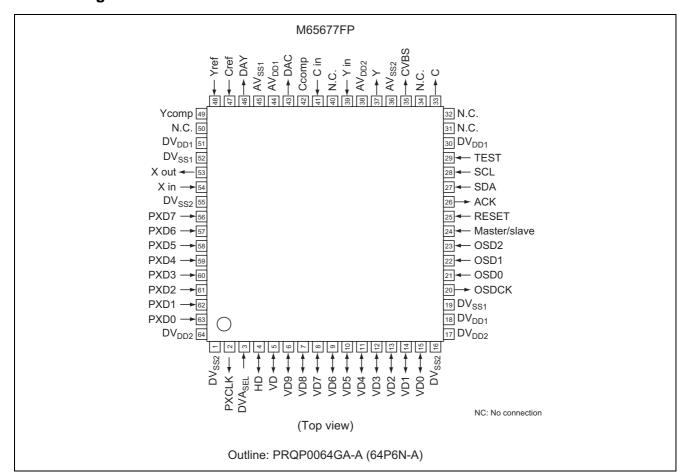

## **Pin Arrangement**

# **Pin Description**

| Pin No | Pin Name           | Туре   | Function                                                                                      |  |  |  |  |

|--------|--------------------|--------|-----------------------------------------------------------------------------------------------|--|--|--|--|

| 1      | DV <sub>SS2</sub>  | Supply | Digital ground for the I/O                                                                    |  |  |  |  |

| 2      | PXCLK              | 0      | Reference clock for input pixel data.                                                         |  |  |  |  |

|        |                    |        | The clock frequency is 27.0 MHz                                                               |  |  |  |  |

| 3      | DVA <sub>SEL</sub> | ı      | I <sup>2</sup> C slave address setting.                                                       |  |  |  |  |

|        |                    |        | "Low" is for the address of 40h, "High" is for the address of 42h.                            |  |  |  |  |

| 4      | HD                 | I/O    | Horizontal sync signal input or output.                                                       |  |  |  |  |

|        |                    |        | It is an input and output in the slave and master mode, respectively.                         |  |  |  |  |

| 5      | VD                 | I/O    | Vertical sync input or output. Or Odd Even signal output.                                     |  |  |  |  |

|        |                    |        | It is an input and output in the slave and master mode, respectively.                         |  |  |  |  |

| 6      | VD9                | I/O    | Video data outputs.                                                                           |  |  |  |  |

| 7      | VD8                |        | In the Y/U/V output mode, the output is the 10-bit digital luma signal with a                 |  |  |  |  |

| 8      | VD7                |        | composite sync.                                                                               |  |  |  |  |

| 9      | VD6                |        | composite sync.<br>VD9 is MSB and VD0 is LSB.                                                 |  |  |  |  |

| 10     | VD5                |        |                                                                                               |  |  |  |  |

| 11     | VD4                |        |                                                                                               |  |  |  |  |

| 12     | VD3                |        |                                                                                               |  |  |  |  |

| 13     | VD2                |        |                                                                                               |  |  |  |  |

| 14     | VD1                |        |                                                                                               |  |  |  |  |

| 15     | VD0                |        |                                                                                               |  |  |  |  |

| 16     | DV <sub>SS2</sub>  | Supply | Digital ground for the I/O.                                                                   |  |  |  |  |

| 17     | $DV_{DD2}$         | Supply | Digital supply for the I/O                                                                    |  |  |  |  |

| 18     | DV <sub>DD1</sub>  | Supply | Digital supply for the internal logic.                                                        |  |  |  |  |

| 19     | DV <sub>SS1</sub>  | Supply | Digital ground for the internal logic.                                                        |  |  |  |  |

| 20     | OSDCK              | 0      | The reference clock for an external OSD microcontroller.                                      |  |  |  |  |

|        |                    |        | The frequency is 13.5 MHz or 6.25 MHz, alternated by I <sup>2</sup> C bus control.            |  |  |  |  |

| 21     | OSD0               | 1      | The color look-up table address input.                                                        |  |  |  |  |

| 22     | OSD1               |        | MSB and LSB are OSD2 and OSD0, respectively.                                                  |  |  |  |  |

| 23     | OSD2               |        |                                                                                               |  |  |  |  |

| 24     | Master/Slave       | I      | Synchronizing mode selection.                                                                 |  |  |  |  |

|        |                    |        | "Low" is for the slave mode.                                                                  |  |  |  |  |

|        |                    |        | "High" is for the master mode.                                                                |  |  |  |  |

| 25     | RESET              | I      | Initializing reset. "Low" is active.                                                          |  |  |  |  |

| 26     | ACK                | 0      | Acknowledge line (Open drain output).                                                         |  |  |  |  |

| 27     | SDA                | I/O    | Serial data line/acknowledge line (Open drain output).                                        |  |  |  |  |

| 28     | SCL                | I      | Serial clock line.                                                                            |  |  |  |  |

| 29     | TEST               | I      | For testing.                                                                                  |  |  |  |  |

|        |                    |        | Is should be grounded during an actual use.                                                   |  |  |  |  |

| 30     | DV <sub>DD1</sub>  | Supply | Digital supply for the internal logic.                                                        |  |  |  |  |

| 31     | N.C.               | _      | No connection.                                                                                |  |  |  |  |

| 32     | N.C.               | _      | No connection.                                                                                |  |  |  |  |

| 33     | С                  | 0      | The analog chroma output from a 6 dB amplifier.                                               |  |  |  |  |

|        |                    |        | The output amplitude is 1.0 V <sub>P-P</sub> (Typ), while the input is 0.5 V <sub>P-P</sub> . |  |  |  |  |

| 34     | N.C.               |        | No connection.                                                                                |  |  |  |  |

| 35     | CVBS               | 0      | The analog composite video signal from a 6 dB amplifier.                                      |  |  |  |  |

|        |                    |        | The output amplitude is 1.24 V <sub>P-P</sub> (Typ).                                          |  |  |  |  |

| 36     | AV <sub>SS2</sub>  | Supply | Analog ground for 6 dB amplifiers.                                                            |  |  |  |  |

| 37     | Y                  | 0      | The analog luma output from a 6 dB amplifier.                                                 |  |  |  |  |

|        | A) (               |        | The output amplitude is 1.2 V <sub>P-P</sub> (Typ), while input is 0.6 V <sub>P-P</sub> .     |  |  |  |  |

| 38     | AV <sub>SS2</sub>  | Supply | Analog supply for 6 dB amplifiers.                                                            |  |  |  |  |

# Pin Description (cont.)

| Pin No | Pin Name          | Type   | Function                                                                              |

|--------|-------------------|--------|---------------------------------------------------------------------------------------|

| 39     | Yin               | I      | The analog luma input from an external LPF.                                           |

|        |                   |        | This input has bias circuit. The signal must input via a capacitor.                   |

| 40     | N.C.              | _      | No connection.                                                                        |

| 41     | Cin               | I      | The analog chroma input from an external LPF.                                         |

|        |                   |        | This input has bias circuit. The signal must input via a capacitor.                   |

| 42     | Ccomp             | I      | Phase compensation for chroma or V output DAC.                                        |

|        |                   |        | It should be connected to the analog ground via a capacitor.                          |

| 43     | DAC               | 0      | Chroma or V signal output.                                                            |

|        |                   |        | The DAC output should be connected to the analog supply via a load resistor $(R_L)$ . |

|        |                   |        | The output amplitude is set up by reference resistor (Rref) and RL.                   |

| 44     | AV <sub>DD1</sub> | Supply | Analog supply for DACs.                                                               |

| 45     | AV <sub>SS1</sub> | Supply | Analog ground for DACs.                                                               |

| 46     | DAY               | 0      | Luma or U signal output.                                                              |

|        |                   |        | It should be connected to the analog supply via a load resistor (R <sub>L</sub> ).    |

|        |                   |        | The output amplitude is set up by reference resistor (Rref) and R <sub>L</sub> .      |

| 47     | Cref              | I      | A reference current source for chroma or V signal output DAC.                         |

|        |                   |        | It should be connected to the analog supply via a reference resistor (Rref).          |

| 48     | Yrel              | I      | A reference current source for Y or U DAC.                                            |

|        |                   |        | It should be connected to the analog supply via a reference resistor (Rref).          |

| 49     | Ycomp             | I      | Phase compensation for Y or U DAC.                                                    |

|        |                   |        | It should be connected to the analog ground via a capacitor.                          |

| 50     | N.C.              | _      | No connection.                                                                        |

| 51     | DV <sub>DD1</sub> | Supply | Digital supply for the internal logic.                                                |

| 52     | DV <sub>SS1</sub> | Supply | Digital ground for the internal logic.                                                |

| 53     | Xout              | 0      | System clock output.                                                                  |

|        |                   |        | It must be in no connection except for a connection to a X'tal oscillator.            |

| 54     | Xin               | I      | System clock input.                                                                   |

|        |                   |        | The clock frequency is only 27.0 MHz.                                                 |

| 55     | DV <sub>SS2</sub> | Supply | Digital ground for the I/O.                                                           |

| 56     | PXD7              | I      | Pixel data inputs.                                                                    |

| 57     | PXD6              |        | The acceptable video data are;                                                        |

| 58     | PXD5              |        | Multiplexed video data (Y/Cb/Cr) including timing reference code of SAV               |

| 59     | PXD4              |        | and EAV, defined in CCIR Rec656                                                       |

| 60     | PXD3              |        | Multiplexed video data (Y/Cb/Cr) defined in CCIR Rec601                               |

| 61     | PXD2              |        | MSB and LSB are PXD7 and PXD0, respectively.                                          |

| 62     | PXD1              |        |                                                                                       |

| 63     | PXD0              |        |                                                                                       |

| 64     | $DV_{DD2}$        | Supply | Digital supply for the I/O.                                                           |

# **Absolute Maximum Ratings**

|                        |          | Limits |     |                       |      |  |

|------------------------|----------|--------|-----|-----------------------|------|--|

| ltem                   | Symbol   | Min    | Тур | Max                   | Unit |  |

| Supply voltage         | $V_{DD}$ | -0.3   | _   | 4.5                   | V    |  |

| Digital input voltage  | VI       | -0.3   | _   | V <sub>DD</sub> + 0.3 | V    |  |

| Digital output voltage | Vo       | -0.3   | _   | V <sub>DD</sub> + 0.3 | V    |  |

| Operating temperature  | Та       | -20    | +25 | +75                   | °C   |  |

| Storage temperature    | Tstg     | -40    | _   | +125                  | °C   |  |

# **Recommended Operating Condition**

$(Ta = 25^{\circ}C, DV_{DD} = AV_{DD} = 3.3 \text{ V}, DV_{SS} = AV_{SS} = 0 \text{ V}, \text{ unless otherwise noted})$

|                                  |                                  | Limits |      |             |      |                                                                               |

|----------------------------------|----------------------------------|--------|------|-------------|------|-------------------------------------------------------------------------------|

| Item                             | Symbol                           | Min    | Тур  | Max         | Unit | Test Conditions                                                               |

| Supply                           |                                  |        |      |             |      |                                                                               |

| Digital supply voltage           | $DV_{DDX}$                       | 3.0    | 3.3  | 3.6         | V    |                                                                               |

| Analog supply voltage            | $AV_{DDX}$                       | 3.15   | 3.3  | 3.45        | V    |                                                                               |

| Digital current consumption      | $DI_DD$                          | 0      | _    | 45          | mA   |                                                                               |

| Analog current consumption       | $AI_{DD}$                        | 0      | _    | 55          | mA   |                                                                               |

| Digital input                    |                                  |        |      |             |      |                                                                               |

| Input voltage                    | V <sub>IL</sub>                  | 0      | _    | 0.8         | V    | DV <sub>DD</sub> = 3.0 V                                                      |

|                                  | V <sub>IH</sub>                  | 2.5    | _    | 3.6         | V    | DV <sub>DD</sub> = 3.6 V                                                      |

| Input leakage current            | I <sub>IL</sub> /I <sub>IH</sub> | _      | _    | 15          | μА   | $DV_{DD} = 3.0 \text{ V},$<br>$V_{I} = 0 \text{ V or } V_{I} = 3.6 \text{ V}$ |

| Input capacitance                | Cı                               |        | 7    | 15          | pF   | f = 1 MHz, V <sub>DD</sub> = 0 V                                              |

| Digital output                   |                                  |        |      | •           |      |                                                                               |

| Output voltage                   | V <sub>OL</sub>                  | _      | _    | 0.05        | V    | DV <sub>DD</sub> = 3.3 V,  I <sub>O</sub>   < 1 A                             |

|                                  | VoH                              | 3.25   | _    | _           | V    |                                                                               |

| Output capacitance               | Co                               |        | 7    | 15          | pF   | f = 1 MHz, V <sub>DD</sub> = 0 V                                              |

| I <sup>2</sup> C Bus             |                                  |        |      |             |      |                                                                               |

| Output current                   | Io                               | 4.0    | _    | _           | mA   | DV <sub>DD</sub> = 3.0 V, V <sub>IL</sub> = 0.4 V                             |

| Output leakage current (off)     | l <sub>OZ</sub>                  |        | _    | 15          | μΑ   | $DV_{DD} = 3.6 \text{ V},$                                                    |

|                                  |                                  |        |      |             |      | $V_1 = 0 \text{ V or } V_1 = 3.6 \text{ V}$                                   |

| D/A converter                    |                                  |        |      |             |      |                                                                               |

| Resolution                       | Res                              |        | 10   | _           | Bit  |                                                                               |

| Integral non-linearity error     | INL                              |        | _    | 2.0         | LSB  |                                                                               |

| Differential non-linearity error | DNL                              |        | _    | 1.0         | LSB  |                                                                               |

| Maximum output amplitude         | Vfs <sub>MAX</sub>               | 1.5    | _    | _           | Vp-p |                                                                               |

| 6-dB amplifier                   |                                  |        |      |             |      |                                                                               |

| Bias resistor                    | Rbias                            | 7.5    | 10.0 | 11.5        | kΩ   |                                                                               |

| Output gain (Y/C)                | G <sub>V_YC</sub>                | 5.50   | 6.00 | 6.50        | dB   |                                                                               |

| Output Gain (CVBS)               | $G_{V\_CV}$                      | 5.10   | 6.00 | 6.85        | dB   |                                                                               |

| Input dynamic range              | DRin                             | 0.8    | _    | _           | Vp-p |                                                                               |

| Output dynamic range             | DRout                            | 1.6    | _    | _           | Vp-p |                                                                               |

| Yin clamp charge current         | lyich                            | -12    | -26  | <b>-</b> 50 | μΑ   |                                                                               |

| Yin clamp discharge current      | lyids                            | 0.26   | 0.65 | 1.80        | μΑ   |                                                                               |

| Yin clamp discharge current      | Ryicl                            | 20     | 0.65 | 70          | _    | $Ryicl = -\frac{Iyich}{Iyids}$                                                |

| Yin input clamp voltage          | Vyicl                            | 0.45   | 0.50 | 0.55        | V    |                                                                               |

| Yin output clamp voltage         | Vyocl                            | 0.40   | 0.50 | 0.60        | V    |                                                                               |

| CVBS output clamp voltage        | Vcvcl                            | 0.30   | 0.50 | 0.70        | V    |                                                                               |

| Cin input bias voltage           | Vcin                             | 0.95   | 1.00 | 1.05        | V    |                                                                               |

| C output bias voltage            | Vcob                             | 0.90   | 1.00 | 1.10        | V    |                                                                               |

| Output current                   | lamp                             | 1.00   |      | _           | mA   |                                                                               |

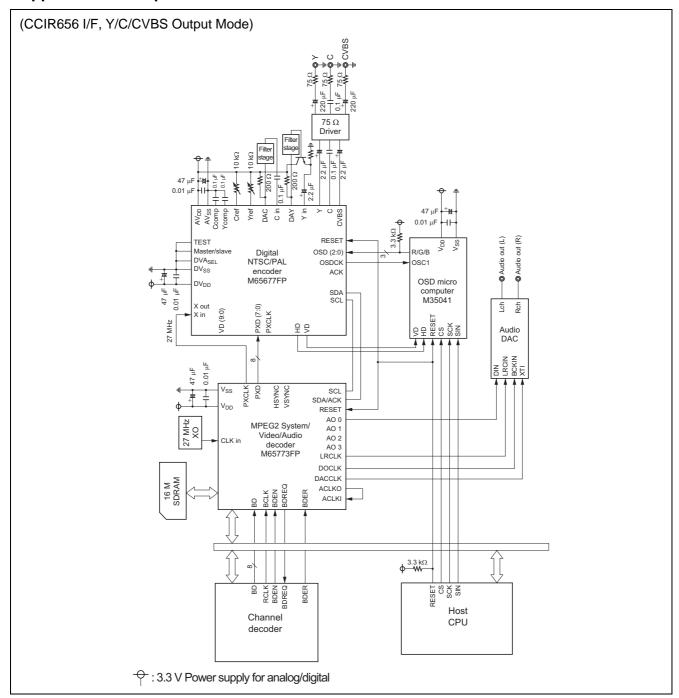

## **Application Example**

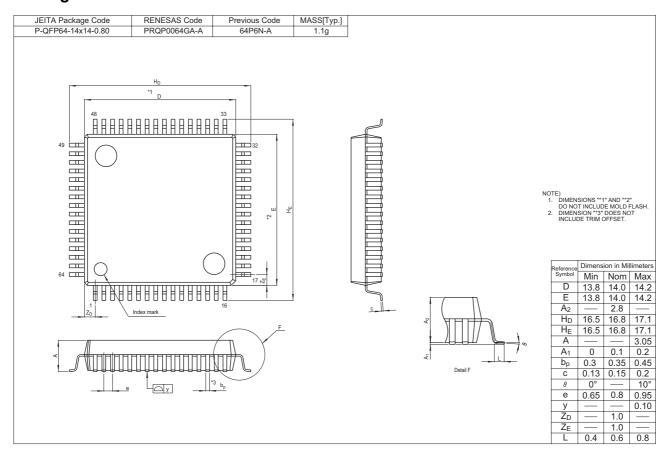

## **Package Dimensions**

### Renesas Technology Corp. sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan

- Renesas lechnology Corp. Sales Strategic Planning Div. Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Notes:

1. This document is provided for reference purposes only so that Renesas customers may select the appropriate Renesas products for their use. Renesas neither makes warrantes or representations with respect to the accuracy or completeness of the information in this document nor grants any license to any intellectual property girbs to any other rights of representations with respect to the information in this document in this document of the purpose of the respect to the information in this document in the product data, diagrams, charts, programs, algorithms, and application circuit examples.

3. You should not use the products of the technology described in this document for the purpose of military use. When exporting the products or technology described herein, you should follow the applicable export control laws and regulations, and procedures required by such laws and regulations, and procedures required to change without any plan notice. Before purchasing or using any Renesas products listed in this document, in the such procedure in the procedure of the description of the such and the procedure in th

### **RENESAS SALES OFFICES**

http://www.renesas.com

Refer to "http://www.renesas.com/en/network" for the latest and detailed information.

### Renesas Technology America, Inc.

450 Holger Way, San Jose, CA 95134-1368, U.S.A Tel: <1> (408) 382-7500, Fax: <1> (408) 382-7501

Renesas Technology Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K.

Tel: <44> (1628) 585-100, Fax: <44> (1628) 585-900

Renesas Technology (Shanghai) Co., Ltd.

Unit 204, 205, AZIACenter, No.1233 Lujiazui Ring Rd, Pudong District, Shanghai, China 200120 Tel: <86> (21) 5877-1818, Fax: <86> (21) 6887-7858/7898

Renesas Technology Hong Kong Ltd.

7th Floor, North Tower, World Finance Centre, Harbour City, Canton Road, Tsimshatsui, Kowloon, Hong Kong Tel: <852> 2265-6688, Fax: <852> 2377-3473

**Renesas Technology Taiwan Co., Ltd.** 10th Floor, No.99, Fushing North Road, Taipei, Taiwan Tel: <886> (2) 2715-2888, Fax: <886> (2) 3518-3399

Renesas Technology Singapore Pte. Ltd.

1 Harbour Front Avenue, #06-10, Keppel Bay Tower, Singapore 098632 Tel: <65> 6213-0200, Fax: <65> 6278-8001

Renesas Technology Korea Co., Ltd. Kukje Center Bldg. 18th Fl., 191, 2-ka, Hangang-ro, Yongsan-ku, Seoul 140-702, Korea Tel: <82> (2) 796-3115, Fax: <82> (2) 796-2145

Renesas Technology Malaysia Sdn. Bhd

Unit 906, Block B, Menara Amcorp, Amcorp Trade Centre, No.18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: <603> 7955-9390, Fax: <603> 7955-9510