### **General Description**

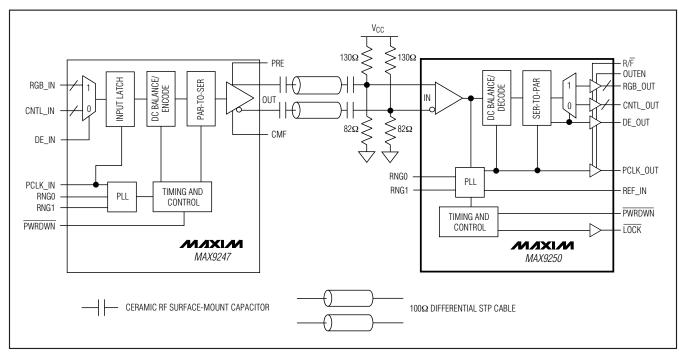

The MAX9248/MAX9250 digital video serial-to-parallel converters deserialize a total of 27 bits during data and control phases. In the data phase, the LVDS serial input is converted to 18 bits of parallel video data and in the control phase, the input is converted to 9 bits of parallel control data. The separate video and control phases take advantage of video timing to reduce the serial-data rate. The MAX9248/MAX9250 pair with the MAX9247 serializer to form a complete digital video transmission system. For operating frequencies less than 35MHz, the MAX9248/MAX9250 can also pair with the MAX9217 serializer.

The MAX9248 features spread-spectrum capability, allowing output data and clock to spread over a specified frequency range to reduce EMI. The data and clock outputs are programmable for a spectrum spread of  $\pm 4\%$  or  $\pm 2\%$ . The MAX9250 features output enable input control to allow data busing.

Proprietary data decoding reduces EMI and provides DC balance. The DC balance allows AC-coupling, providing isolation between the transmitting and receiving ends of the interface. The MAX9248/MAX9250 feature a selectable rising or falling output latch edge.

ESD tolerance is specified for ISO 10605 with  $\pm$ 10kV Contact Discharge and  $\pm$ 30kV Air-Gap Discharge.

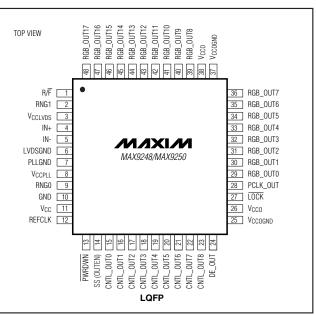

The MAX9248/MAX9250 operate from a +3.3V  $\pm$ 10% core supply and feature a separate output supply for interfacing to 1.8V to 3.3V logic-level inputs. These devices are available in a 48-lead LQFP package and are specified from -40°C to +85°C or -40°C to +105°C.

Navigation System Displays In-Vehicle Entertainment Systems Video Cameras LCD Displays

### **Applications**

Features

- Programmable ±4% or ±2% Spread-Spectrum Output for Reduced EMI (MAX9248)

- Proprietary Data Decoding for DC Balance and Reduced EMI

- Control Data Deserialized During Video Blanking

- Five Control Data Inputs are Single-Bit-Error Tolerant

- Output Transition Time is Scaled to Operating Frequency for Reduced EMI

- Staggered Output Switching Reduces EMI

- Output Enable Allows Busing of Outputs (MAX9250)

- Clock Pulse Stretch on Lock

- ♦ Wide ±2% Reference Clock Tolerance

- Synchronizes to MAX9247 Serializer Without External Control

- ISO 10605 and IEC 61000-4-2 Level 4 ESD Protection

- Separate Output Supply Allows Interface to 1.8V to 3.3V Logic

- +3.3V Core Power Supply

- Space-Saving LQFP Package

- ◆ -40°C to +85°C and -40°C to +105°C Operating Temperature Ranges

### **Ordering Information**

| PART          | TEMP RANGE      | PIN-PACKAGE |

|---------------|-----------------|-------------|

| MAX9248ECM+   | -40°C to +85°C  | 48 LQFP     |

| MAX9248ECM/V+ | -40°C to +85°C  | 48 LQFP     |

| MAX9248GCM+   | -40°C to +105°C | 48 LQFP     |

| MAX9248GCM/V+ | -40°C to +105°C | 48 LQFP     |

| MAX9250ECM+   | -40°C to +85°C  | 48 LQFP     |

| MAX9250ECM/V+ | -40°C to +85°C  | 48 LQFP     |

| MAX9250GCM+   | -40°C to +105°C | 48 LQFP     |

| MAX9250GCM/V+ | -40°C to +105°C | 48 LQFP     |

|               |                 |             |

+Denotes a lead(Pb)-free/RoHS-compliant package. /V denotes an automotive qualified part.

Pin Configuration appears at end of data sheet.

####

\_ Maxim Integrated Products 1

MAX9248/MAX9250

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>CC</sub> to _GND0.5V to +4.0V<br>Any Ground to Any Ground0.5V to +0.5V<br>IN+, IN- to LVDSGND0.5V to +4.0V<br>IN+, IN- Short Circuit to LVDSGND or V <sub>CCLVDS</sub> Continuous                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $\begin{array}{l} (R/\overline{F}, \mbox{ OUTEN, RNG_, REFCLK, SS} \\ \hline PWRDWN) \mbox{ to GND0.5V to (V_{CC} + 0.5V)} \\ (RGB_OUT[17:0], \mbox{ CNTL_OUT[8:0], DE_OUT, PCLK_OUT, } \\ \hline LOCK) \mbox{ to V}_{CCOGND} \\ \hline Continuous Power Dissipation (T_A = +70^{\circ}C) $ |  |

| 48-Lead LQFP (derate 21.7mW/°C above +70°C)1739mW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| ESD Protection<br>Machine Model ( $R_D = 0\Omega$ , $C_S = 200pF$ ) |

|---------------------------------------------------------------------|

| All Pins to GND±200V                                                |

| Human Body Model ( $R_D = 1.5 k\Omega$ , $C_S = 100 pF$ )           |

| All Pins to GND±2kV                                                 |

| ISO 10605 ( $R_D = 2k\Omega$ , $C_S = 330pF$ )                      |

| Contact Discharge (IN+, IN-) to GND±10kV                            |

| Air-Gap Discharge (IN+, IN-) to GND±30kV                            |

| IEC 61000-4-2 ( $R_D = 330\Omega$ , $C_S = 150pF$ )                 |

| Contact Discharge (IN+, IN-) to GND±10kV                            |

| Air-Gap Discharge (IN+, IN-) to GND±15kV                            |

| Storage Temperature Range65°C to +150°C                             |

| Junction Temperature+150°C                                          |

| Lead Temperature (soldering, 10s)+300°C                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0V \text{ to } +3.6V, \overline{PWRDWN} = \text{high}, \text{ differential input voltage } |V_{ID}| = 0.05V \text{ to } 1.2V, \text{ input common-mode voltage } V_{CM} = |V_{ID}/2|$ to  $V_{CC} - |V_{ID}/2|, T_A = -40^{\circ}\text{C}$  to  $+105^{\circ}\text{C}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3V, |V_{ID}| = 0.2V, V_{CM} = 1.2V, T_A = +25^{\circ}\text{C}.)$  (Notes 1, 2)

| PARAMETER                     | SYMBOL          |                          | CONDITIONS                                | MIN T                   | YP MAX         | UNITS |  |

|-------------------------------|-----------------|--------------------------|-------------------------------------------|-------------------------|----------------|-------|--|

| SINGLE-ENDED INPUTS (R/F, OU  | JTEN, RNG0,     | RNG1, REFC               | LK, PWRDWN, SS)                           |                         |                |       |  |

| High-Level Input Voltage      | VIH             |                          |                                           | 2.0                     | $V_{CC} + 0.3$ | V     |  |

| Low-Level Input Voltage       | VIL             |                          |                                           | -0.3                    | +0.8           | V     |  |

| Input Current                 | IIN             | PWRDWN =<br>high or low  |                                           | -100                    | +20            | μΑ    |  |

|                               |                 |                          | $V_{IN} = 0$ to ( $V_{CC} + 0.3V$ )       | -20                     | +20            | L .   |  |

| Input Clamp Voltage           |                 | -1.5                     | V                                         |                         |                |       |  |

| SINGLE-ENDED OUTPUTS (RGB     | _OUT[17:0],     | CNTL_OUT[8:              | 0], DE_OUT, PCLK_OUT, LO                  | CK)                     |                |       |  |

|                               |                 | I <sub>ОН</sub> = -100µА | l.                                        | V <sub>CCO</sub> - 0.1  |                |       |  |

| High-Level Output Voltage     | VOH             | $I_{OH} = -2mA$ ,        | RNG1 = high                               | V <sub>CCO</sub> - 0.35 |                | V     |  |

|                               |                 | $I_{OH} = -2mA$ ,        | RNG1 = low                                | V <sub>CCO</sub> - 0.4  |                |       |  |

|                               |                 | $I_{OL} = 100 \mu A$     |                                           |                         | 0.1            |       |  |

| Low-Level Output Voltage      | VOL             | $I_{OL} = 2mA, R$        | NG1 = high                                |                         | 0.3            | V     |  |

|                               |                 | I <sub>OL</sub> = 2mA, R | NG1 = low                                 |                         | 0.35           |       |  |

| High-Impedance Output Current | I <sub>OZ</sub> |                          | low or OUTEN = low,<br>$(V_{CCO} + 0.3V)$ | -10                     | +10            | μA    |  |

|                               | 1               | RNG1 = high              | , V <sub>O</sub> = 0                      | -10                     | -50            |       |  |

| Output Short-Circuit Current  | los             | RNG1 = low,              | $V_{O} = 0$                               | -7                      | -40            | mA    |  |

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, \overline{PWRDWN} = \text{high}, \text{differential input voltage } |V_{ID}| = 0.05V \text{ to } 1.2V, \text{input common-mode voltage } V_{CM} = |V_{ID}/2|$ to V<sub>CC</sub> -  $|V_{ID}/2|$ , T<sub>A</sub> = -40°C to +105°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +3.3V,  $|V_{ID}| = 0.2V$ , V<sub>CM</sub> = 1.2V, T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                         | SYMBOL                                |                                                                       | CONDITIONS                 |         | MIN | ТҮР | MAX | UNITS |

|-----------------------------------|---------------------------------------|-----------------------------------------------------------------------|----------------------------|---------|-----|-----|-----|-------|

| LVDS INPUT (IN+, IN-)             | •                                     |                                                                       |                            |         |     |     |     | •     |

| Differential Input High Threshold | V <sub>TH</sub>                       | (Note 3)                                                              |                            |         |     |     | 50  | mV    |

| Differential Input Low Threshold  | V <sub>TL</sub>                       | (Note 3)                                                              |                            |         | -50 |     |     | mV    |

| Input Current                     | I <sub>IN+</sub> , I <sub>IN-</sub>   | PWRDWN =                                                              | high or low (Note          | 3)      | -40 |     | +40 | μA    |

|                                   |                                       | PWRDWN =                                                              | MAX9248/MAX9               | 9250ECM | 42  | 60  | 78  |       |

|                                   |                                       | high or low                                                           | MAX9248/MAX9               | 9250GCM | 42  | 60  | 88  |       |

| Input Bias Resistor (Note 3)      | R <sub>IB</sub>                       | V <sub>CC</sub> =<br>0 or open,<br>PWRDWN =<br>0 or open,<br>Figure 1 | MAX9248/MAX                | 9250ECM | 42  | 60  | 78  | kΩ    |

|                                   |                                       |                                                                       | MAX9248/MAX                | 9250GCM | 42  | 60  | 88  |       |

| Power-Off Input Current           | I <sub>INO+</sub> , I <sub>INO-</sub> | $\frac{V_{CC} = 0 \text{ or } c}{PWRDWN} =$                           | open,<br>0 or open (Note 3 | 3)      | -60 |     | +60 | μA    |

| POWER SUPPLY                      |                                       |                                                                       |                            |         |     |     |     |       |

|                                   |                                       |                                                                       | RNG1 = low                 | 2.5MHz  |     |     | 19  |       |

|                                   |                                       |                                                                       | RNG0 = low                 | 5MHz    |     |     | 33  | -     |

|                                   |                                       | MAX9250                                                               | RNG1 = low                 | 5MHz    |     |     | 28  |       |

|                                   |                                       | C <sub>L</sub> = 8pF,<br>worst-case                                   | RNG0 = high                | 10MHz   |     |     | 49  |       |

|                                   |                                       | pattern,                                                              | RNG1 = high<br>RNG0 = low  | 10MHz   |     |     | 33  |       |

|                                   |                                       | Figure 2                                                              |                            | 20MHz   |     |     | 59  |       |

|                                   |                                       |                                                                       | RNG1 = high                | 20MHz   |     |     | 45  |       |

|                                   |                                       |                                                                       | RNG0 = high                | 42MHz   |     |     | 89  |       |

| Worst-Case Supply Current         |                                       |                                                                       | RNG1 = low                 | 2.5MHz  |     |     | 31  | mA    |

|                                   |                                       |                                                                       | RNG0 = low                 | 5MHz    |     |     | 48  |       |

|                                   |                                       | MAX9248                                                               | RNG1 = low                 | 5MHz    |     |     | 40  |       |

|                                   |                                       | $C_L = 8pF$ ,                                                         | RNG0 = high                | 10MHz   |     |     | 70  | ]     |

|                                   |                                       | worst-case                                                            | RNG1 = high                | 10MHz   |     |     | 49  | ]     |

|                                   |                                       | pattern,                                                              | RNG0 = low                 | 20MHz   |     |     | 87  | ]     |

|                                   |                                       | Figure 2                                                              |                            | 20MHz   |     |     | 68  |       |

|                                   |                                       |                                                                       | RNG1 = high<br>RNG0 = high | 35MHz   |     |     | 100 |       |

|                                   |                                       |                                                                       |                            | 42MHz   |     |     | 120 |       |

| Power-Down Supply Current         | ICCZ                                  | (Note 4)                                                              |                            |         |     |     | 50  | μA    |

### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0V \text{ to } +3.6V, C_L = 8pF, PWRDWN = high, differential input voltage <math>|V_{ID}| = 0.1V \text{ to } 1.2V$ , input common-mode voltage  $V_{CM} = |V_{ID}/2|$  to  $V_{CC} - |V_{ID}/2|$ ,  $T_A = -40^{\circ}C$  to  $+105^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3V$ ,  $|V_{ID}| = 0.2V$ ,  $V_{CM} = 1.2V$ ,  $T_A = +25^{\circ}C$ .) (Notes 3, 5)

| PARAMETER                  | SYMBOL              |           | CO         | NDITIO              | NS                     | MIN                     | ТҮР                      | MAX                     | UNITS |  |

|----------------------------|---------------------|-----------|------------|---------------------|------------------------|-------------------------|--------------------------|-------------------------|-------|--|

| REFCLK TIMING REQUIREME    | NTS                 |           |            |                     |                        |                         |                          |                         |       |  |

|                            |                     | MAX9248   | /MAX925    | 50ECM               |                        | 23.8                    |                          | 400.0                   |       |  |

| Period                     | tT                  | MAX9248   | /MAX925    | 50GCM               |                        | 28.6                    |                          | 400.0                   | ns    |  |

| _                          |                     | MAX9248   | /MAX92     | 50ECM               |                        | 2.5                     |                          | 42.0                    |       |  |

| Frequency                  | fCLK                | MAX9248,  | /MAX92     | 50GCM               |                        | 2.5                     |                          | 35.0                    | MHz   |  |

| Frequency Variation        | Δf <sub>CLK</sub>   | REFCLK to | o serializ | zer PCL             | K_IN                   | -2.0                    |                          | +2.0                    | %     |  |

| Duty Cycle                 | DC                  |           |            |                     |                        | 40                      | 50                       | 60                      | %     |  |

| Transition Time            | t <sub>TRAN</sub>   | 20% to 80 | )%         |                     |                        |                         |                          | 6                       | ns    |  |

| SWITCHING CHARACTERISTI    |                     |           |            |                     |                        |                         |                          |                         |       |  |

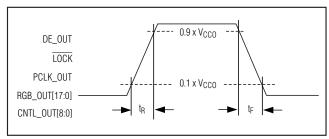

|                            |                     |           |            |                     | MAX9248/<br>MAX9250ECM | 2.2                     |                          | 4.6                     |       |  |

| Output Direct Times        |                     | Figure 3  | RNG1       | = high              | MAX9248/<br>MAX9250GCM | 2.2                     |                          | 4.9                     |       |  |

| Output Rise Time           | tR                  |           | DNIGA      |                     | MAX9248/<br>MAX9250ECM | 2.8                     |                          | 5.2                     | ns    |  |

|                            |                     |           | RNG1       | = IOW               | MAX9248/<br>MAX9250GCM | 2.8                     |                          | 6.1                     |       |  |

|                            |                     |           | RNG1       | = high              | MAX9248/<br>MAX9250ECM | 1.9                     |                          | 4.0                     |       |  |

| Output Fall Time           | t <sub>R</sub>      | Figure 3  |            |                     | MAX9248/<br>MAX9250ECM | 2.3                     |                          | 4.3                     | ns    |  |

|                            |                     |           | RNG1 = low |                     | MAX9248/<br>MAX9250GCM | 2.3                     |                          | 5.2                     |       |  |

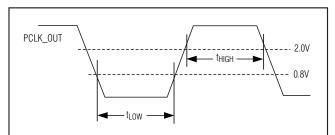

| PCLK_OUT High Time         | thigh               | Figure 4  |            |                     |                        | 0.4 x<br>t <sub>T</sub> | 0.45 x<br>t <sub>T</sub> | 0.6 x<br>t <sub>T</sub> | ns    |  |

| PCLK_OUT Low Time          | tLOW                | Figure 4  |            |                     |                        | 0.4 x<br>t <sub>T</sub> | 0.45 x<br>t <sub>T</sub> | 0.6 x<br>t <sub>T</sub> | ns    |  |

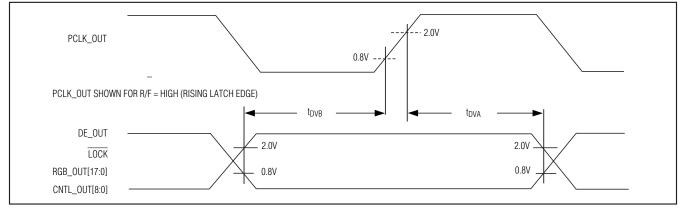

| Data Valid Before PCLK_OUT | t <sub>DVB</sub>    | Figure 5  |            |                     |                        | 0.35 x t <sub>T</sub>   | 0.4 x t <sub>T</sub>     |                         | ns    |  |

| Data Valid After PCLK_OUT  | tdva                | Figure 5  |            |                     |                        | 0.35 x t <sub>T</sub>   | 0.4 x t <sub>T</sub>     |                         | ns    |  |

| 511 1 1 5 5 5 5 1 V        |                     | MAX9248   | , Figure   | 8                   |                        |                         | 33                       | 3,600 x t <sub>T</sub>  |       |  |

| PLL Lock to REFCLK         | <sup>t</sup> PLLREF | MAX9250   | , Figure   | 7                   |                        |                         | 16                       | 6,928 x t <sub>T</sub>  | ns    |  |

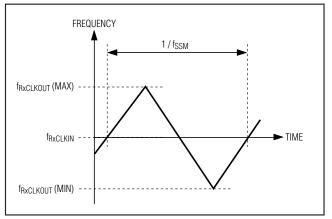

|                            |                     | SS = high |            | /laximur<br>requenc | n output<br>Sy         |                         | frefclk<br>+ 4.0%        |                         | MHz   |  |

| Spread-Spectrum Output     |                     | Figure 11 | Ν          |                     | n output               | frefclk<br>- 4.4%       | frefclk<br>- 4.0%        | frefclk<br>- 3.6%       |       |  |

| Frequency (MAX9248)        | fpclk_out           | SS = low. |            | /laximur<br>requenc | n output<br>cy         | frefclk<br>+ 1.8%       | frefclk<br>+ 2.0%        | fREFCLK<br>+ 2.2%       |       |  |

|                            |                     | Figure 11 | Ν          | /linimum<br>requenc | n output<br>Cy         | fREFCLK<br>- 2.2%       | frefclk<br>- 2.0%        | frefclk<br>- 1.8%       |       |  |

### AC ELECTRICAL CHARACTERISTICS (continued)

$(V_{CC} = +3.0V \text{ to } +3.6V, C_{L} = 8pF, \overline{PWRDWN} = \text{high, differential input voltage } |V_{ID}| = 0.1V \text{ to } 1.2V, \text{ input common-mode voltage } V_{CM} = |V_{ID}/2| \text{ to } V_{CC} - |V_{ID}/2|, T_{A} = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.3V, |V_{ID}| = 0.2V, V_{CM} = 1.2V, T_{A} = +25^{\circ}\text{C}.) (Notes 3, 5)$

| PARAMETER                               | SYMBOL       | CONDITIONS         | MIN | TYP             | MAX                        | UNITS |

|-----------------------------------------|--------------|--------------------|-----|-----------------|----------------------------|-------|

| Spread-Spectrum Modulation<br>Frequency | fssm         | Figure 11          |     | frefclk<br>1024 | /                          | kHz   |

| Power-Down Delay                        | <b>t</b> PDD | Figures 7, 8       |     |                 | 100                        | ns    |

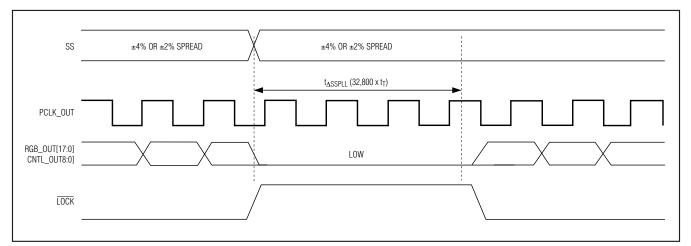

| SS Change Delay                         | t∆SSPLL      | MAX9248, Figure 17 |     |                 | 32,800<br>x t <sub>T</sub> | ns    |

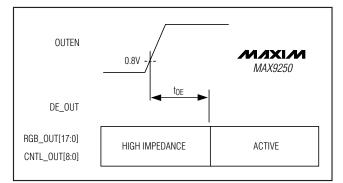

| Output Enable Time                      | toe          | MAX9250, Figure 8  |     | 10              | 30                         | ns    |

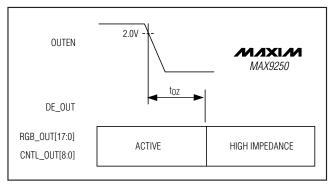

| Output Disable Time                     | toz          | MAX9250, Figure 9  |     | 10              | 30                         | ns    |

Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground except V<sub>TH</sub> and V<sub>TL</sub>.

Note 2: Maximum and minimum limits over temperature are guaranteed by design and characterization. Devices are production tested at  $T_A = +25^{\circ}C$ .

**Note 3:** Parameters are guaranteed by design and characterization, and are not production tested. Limits are set at ±6 sigma.

Note 4: All LVTTL/LVCMOS inputs, except PWRDWN at ≤ 0.3V or ≥ V<sub>CC</sub> - 0.3V. PWRDWN is ≤ 0.3V, REFCLK is static.

Note 5: CL includes probe and test jig capacitance.

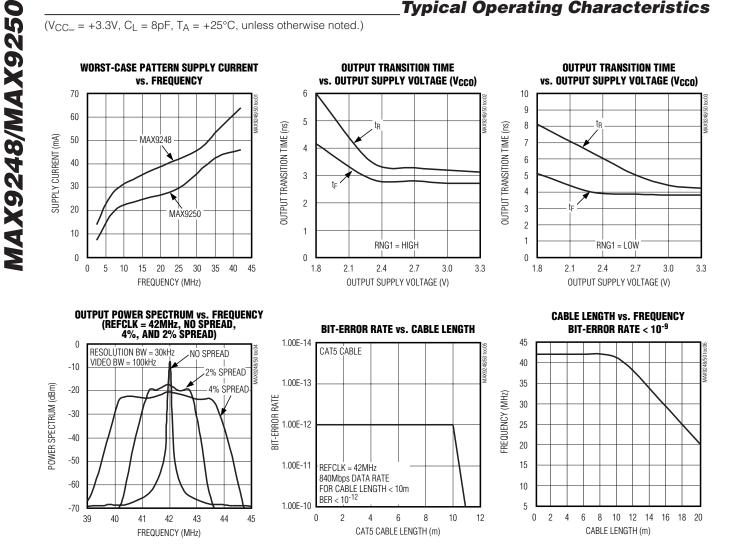

(V<sub>CC</sub> = +3.3V, C<sub>L</sub> = 8pF,  $T_A$  = +25°C, unless otherwise noted.)

**Typical Operating Characteristics**

### \_Pin Description

| P       | N       |                         |                                                                                                                                                                                                                                                                      |

|---------|---------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX9248 | MAX9250 | NAME                    | FUNCTION                                                                                                                                                                                                                                                             |

| 1       | 1       | R/F                     | Rising or Falling Latch Edge Select. LVTTL/LVCMOS input. Selects the edge of PCLK_OUT for latching data into the next chip. Set $R/\overline{F}$ = high for a rising latch edge. Set $R/\overline{F}$ = low for a falling latch edge. Internally pulled down to GND. |

| 2       | 2       | RNG1                    | LVTTL/LVCMOS Range Select Input. Set to the range that includes the serializer parallel clock input frequency. Internally pulled down to GND.                                                                                                                        |

| 3       | 3       | VCCLVDS                 | LVDS Supply Voltage. Bypass to LVDSGND with $0.1\mu$ F and $0.001\mu$ F capacitors in parallel as close to the device as possible, with the smallest value capacitor closest to the supply pin.                                                                      |

| 4       | 4       | IN+                     | Noninverting LVDS Serial-Data Input                                                                                                                                                                                                                                  |

| 5       | 5       | IN-                     | Inverting LVDS Serial-Data Input                                                                                                                                                                                                                                     |

| 6       | 6       | LVDSGND                 | LVDS Supply Ground                                                                                                                                                                                                                                                   |

| 7       | 7       | PLLGND                  | PLL Supply Ground                                                                                                                                                                                                                                                    |

| 8       | 8       | VCCPLL                  | PLL Supply Voltage. Bypass to PLLGND with $0.1\mu$ F and $0.001\mu$ F capacitors in parallel as close to the device as possible with the smallest value capacitor closest to the supply pin.                                                                         |

| 9       | 9       | RNG0                    | LVTTL/LVCMOS Range Select Input. Set to the range that includes the serializer parallel clock input frequency. Internal pulldown to GND.                                                                                                                             |

| 10      | 10      | GND                     | Digital Supply Ground                                                                                                                                                                                                                                                |

| 11      | 11      | V <sub>CC</sub>         | Digital Supply Voltage. Supply for LVTTL/LVCMOS inputs and digital circuits. Bypass to GND with $0.1\mu$ F and $0.001\mu$ F capacitors in parallel as close to the device as possible with the smallest value capacitor closest to the supply pin.                   |

| 12      | 12      | REFCLK                  | LVTTL/LVCMOS Reference Clock Input. Apply a reference clock that is within ±2% of the serializer PCLK_IN frequency. Internally pulled down to GND.                                                                                                                   |

| 13      | 13      | PWRDWN                  | LVTTL/LVCMOS Power-Down Input. Internally pulled down to GND.                                                                                                                                                                                                        |

| 14      | _       | SS                      | LVTTL/LVCMOS Spread-Spectrum Input. SS selects the frequency spread of PCLK_OUT and output data relative to PCLK_IN. Drive SS high for 4% spread and pull low for 2% spread.                                                                                         |

| 15–23   | 15–23   | CNTL_OUT0-<br>CNTL_OUT8 | LVTTL/LVCMOS Control Data Outputs. CNTL_OUT[8:0] are latched into the next chip on the rising or falling edge of PCLK_OUT as selected by R/F when DE_OUT is low, and are held at the last state when DE_OUT is high.                                                 |

| 24      | 24      | DE_OUT                  | LVTTL/LVCMOS Data-Enable Output. High indicates RGB_OUT[17:0] are active. Low indicates CNTL_OUT[8:0] are active.                                                                                                                                                    |

| 25, 37  | 25, 37  | VCCOGND                 | Output Supply Ground                                                                                                                                                                                                                                                 |

| 26, 38  | 26, 38  | Vcco                    | Output Supply Voltage. Bypass to GND with 0.1µF and 0.001µF capacitors in parallel as close to the device as possible with the smallest value capacitor closest to the supply pin.                                                                                   |

### Pin Description (continued)

| P               | N               | NAME                                             | FUNCTION                                                                                                                                                                                                                   |

|-----------------|-----------------|--------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX9248         | MAX9250         | NAME                                             | FUNCTION                                                                                                                                                                                                                   |

| 27              | 27              | LOCK                                             | LVTTL/LVCMOS Lock Indicator Output. Outputs are valid when LOCK is low.                                                                                                                                                    |

| 28              | 28              | PCLK_OUT                                         | LVTTL/LVCMOS Parallel Clock Output. Latches data into the next chip on the edge selected by $R/\overline{F}$ .                                                                                                             |

| 29–36,<br>39–48 | 29–36,<br>39–48 | RGB_OUT0-<br>RBG_OUT7,<br>RGB_OUT8-<br>RGB_OUT17 | LVTTL/LVCMOS Red, Green, and Blue Digital Video Data Outputs. RGB_OUT[17:0] are latched into the next chip on the edge of PCLK_OUT selected by R/F when DE_OUT is high, and are held at the last state when DE_OUT is low. |

|                 | 14              | OUTEN                                            | LVTTL/LVCMOS Output Enable Input. High activates the single-ended outputs. Driving low places the single-ended outputs in high impedance except LOCK. Internally pulled down to GND.                                       |

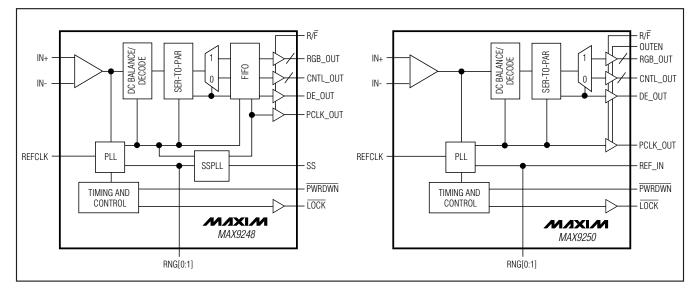

### **Functional Diagram**

Figure 2. Worst-Case Output Pattern

Figure 4. High and Low Times

Figure 5. Synchronous Output Timing

9

Figure 3. Output Rise and Fall Times

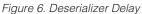

Figure 7. PLL Lock to REFCLK and Power-Down Delay for MAX9250

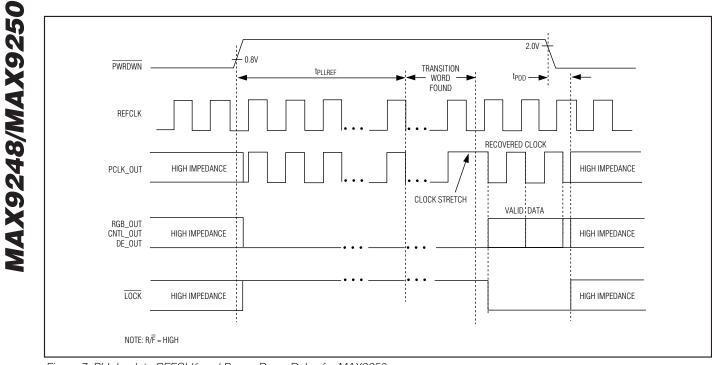

Figure 8. PLL Lock to REFCLK and Power-Down Delay for MAX9248

M/IXI/M

Figure 9. Output Enable Time

Figure 11. Simplified Modulation Profile

Figure 10. Output Disable Time

### **Detailed Description**

The MAX9248/MAX9250 DC-balanced deserializers operate at a 2.5MHz-to-42MHz parallel clock frequency, deserializing video data to the RGB\_OUT[17:0] outputs when the data-enable output DE\_OUT is high, or control data to the CNTL\_OUT[8:0] outputs when DE\_OUT is low. The outputs on the MAX9248 are programmable for  $\pm 2\%$  or  $\pm 4\%$  spread relative to the LVDS input clock frequency, while the MAX9250 has no spread, but has an output-enable input that allows output busing. The video phase words are decoded using two overhead bits, EN0 and EN1. Control phase words are decoded with one overhead bit, EN0. Encoding, performed by the MAX9247 serializer, reduces EMI and maintains DC balance across the serial cable. The serial-input word formats are shown in Tables 1 and 2.

Control data inputs C0 to C4, each repeated over three serial bit times by the serializer, are decoded using majority voting. Two or three bits at the same state determine the state of the recovered bit, providing single bit-error tolerance for C0 to C4. The state of C5 to C8 is determined by the level of the bit itself (no voting is used).

#### **AC-Coupling Benefits**

AC-coupling increases the input voltage of the LVDS receiver to the voltage rating of the capacitor. Two capacitors are sufficient for isolation, but four capacitors—two at the serializer output and two at the deserializer input—provide protection if either end of the cable is shorted to a high voltage. AC-coupling blocks low-frequency ground shifts and common-mode noise.

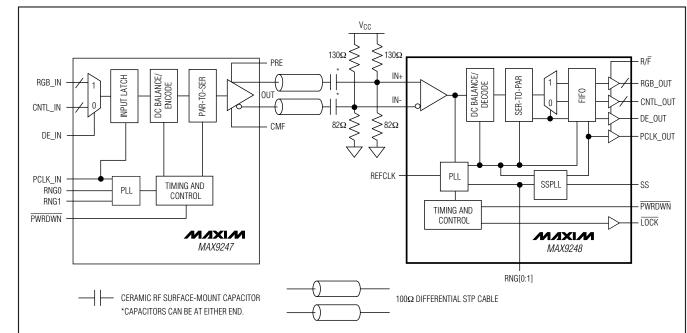

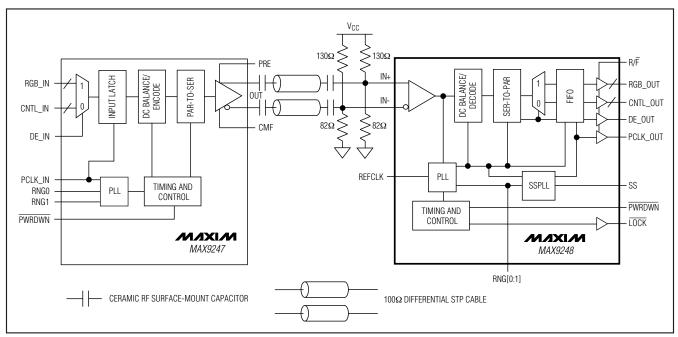

The MAX9247 serializer can also be DC-coupled to the MAX9248/MAX9250 deserializers. Figures 12 and 14 show the AC-coupled serializer and deserializer with two capacitors per link, and Figures 13 and 15 show the AC-coupled serializer and deserializer with four capacitors per link.

### \_Applications Information

#### **Selection of AC-Coupling Capacitors**

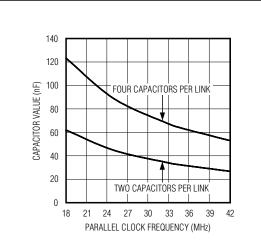

See Figure 16 for calculating the capacitor values for AC-coupling depending on the parallel clock frequency. The plot shows capacitor values for two- and four-capacitor-per-link systems. For applications using less than 18MHz clock frequency, use  $0.1\mu$ F capacitors.

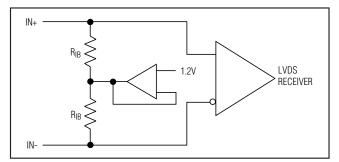

#### **Termination and Input Bias**

The IN+ and IN- LVDS inputs are internally connected to +1.2V through 42k $\Omega$  (min) to provide biasing for ACcoupling (Figure 1). Assuming 100 $\Omega$  interconnect, the LVDS input can be terminated with a 100 $\Omega$  resistor. Match the termination to the differential impedance of the interconnect.

Use a Thevenin termination, providing 1.2V bias, on an AC-coupled link in noisy environments. For interconnect with 100 $\Omega$  differential impedance, pull each LVDS line up to V<sub>CC</sub> with 130 $\Omega$  and down to ground with 82 $\Omega$  at the deserializer input (Figures 12 and 15). This termination provides both differential and common-mode termination. The impedance of the Thevenin termination should be half the differential impedance of the interconnect and provide a bias voltage of 1.2V.

#### **Table 1. Serial Video Phase Word Format**

| 0   | 1   | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12  | 13  | 14  | 15  | 16  | 17  | 18  | 19  |

|-----|-----|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|-----|

| EN0 | EN1 | S0 | S1 | S2 | S3 | S4 | S5 | S6 | S7 | S8 | S9 | S10 | S11 | S12 | S13 | S14 | S15 | S16 | S17 |

Bit 0 is the LSB and is deserialized first. EN[1:0] are encoding bits. S[17:0] are encoded symbols.

### **Table 2. Serial Control Phase Word Format**

| 0   | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 |

|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|

| EN0 | C0 | CO | CO | C1 | C1 | C1 | C2 | C2 | C2 | C3 | C3 | C3 | C4 | C4 | C4 | C5 | C6 | C7 | C8 |

Bit 0 is the LSB and is deserialized first. C[8:0] are the mapped control inputs.

Figure 12. AC-Coupled MAX9247 Serializer and MAX9250 Deserializer with Two Capacitors per Link

Figure 13. AC-Coupled MAX9247 Serializer and MAX9250 Deserializer with Four Capacitors per Link

Figure 14. AC-Coupled MAX9247 Serializer and MAX9248 Deserializer with Two Capacitors per Link

Figure 15. AC-Coupled MAX9247 Serializer and MAX9248 Deserializer with Four Capacitors per Link

M/IXI/M

#### **Input Frequency Detection**

A frequency-detection circuit detects when the LVDS input is not switching. When not switching, all outputs except LOCK are low, LOCK is high, and PCLK\_OUT follows REFCLK. This condition occurs, for example, if the serializer is not driving the interconnect or if the interconnect is open.

Frequency Range Setting (RNG[1:0])

The RNG[1:0] inputs select the operating frequency range of the MAX9248/MAX9250 and the transition time of the outputs. Select the frequency range that includes the MAX9247 serializer PCLK\_IN frequency. Table 3 shows the selectable frequency ranges and the corresponding data rates and output transition times.

| RNG1 | RNG0 | PARALLEL<br>CLOCK<br>(MHz) | SERIAL-<br>DATA RATE<br>(Mbps) | OUTPUT<br>TRANSITION<br>TIME |  |

|------|------|----------------------------|--------------------------------|------------------------------|--|

| 0    | 0    | 2.5 to 5.0                 | 50 to 100                      | Slow                         |  |

| 0    | 1    | 5 to 10                    | 100 to 200                     |                              |  |

| 1    | 0    | 10 to 20                   | 200 to 400                     | Fast                         |  |

| 1    | 1    | 20 to 42                   | 400 to 840                     | Tast                         |  |

#### **Power Down**

Driving PWRDWN low puts the outputs in high impedance and stops the PLL. With PWRDWN  $\leq$  0.3V and all LVTTL/LVCMOS inputs  $\leq$  0.3V or  $\geq$  V<sub>CC</sub> - 0.3V, the supply current is reduced to less than 50µA. Driving PWRDWN high initiates lock to the local reference clock (REFCLK) and afterwards to the serial input.

#### Lock and Loss-of-Lock (LOCK)

When PWRDWN is driven high, the PLL begins locking to REFCLK, drives LOCK from high impedance to high and the other outputs from high impedance to low, except PCLK\_OUT. PCLK\_OUT outputs REFCLK while the PLL is locking to REFCLK. Lock to REFCLK takes a maximum of 16,928 REFCLK cycles for the MAX9250. The MAX9248 has an additional spread-spectrum PLL (SSPLL) that also begins locking to REFCLK. Locking both PLLs to REFCLK takes a maximum of 33,600 REFCLK cycles for the MAX9248.

JCY (MHz) Jues vs. Clock Frequency

Figure 16. AC-Coupling Capacitor Values vs. Clock Frequency of 18MHz to 42MHz

When the MAX9248/MAX9250 complete their lock to REFCLK, the serial input is monitored for a transition word. When a transition word is found, LOCK output is driven low, indicating valid output data and the parallel rate clock recovered from the serial input is output on PCLK\_OUT. The MAX9248 SSPLL waits an additional 288 clock cycles after the transition word is found before LOCK is driven low and sequence takes effect. PCLK\_OUT is stretched on the change from REFCLK to recovered clock (or vice versa) at the time when the transition word is found.

If a transition word is not detected within 2<sup>22</sup> cycles of PCLK\_OUT, LOCK is driven high, the other outputs except PCLK\_OUT are driven low. REFCLK is output on PCLK\_OUT and the deserializer continues monitoring the serial input for a transition word. See Figure 7 for the MAX9250 and Figure 8 for the MAX9248 regarding the synchronization timing diagram.

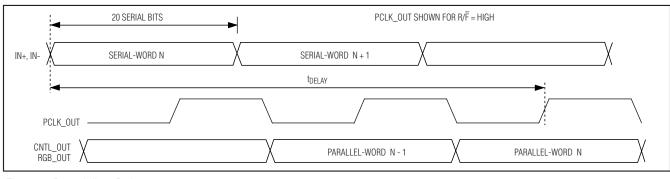

The MAX9248 input-to-output delay can be as low as  $(4.5t_T + 8.0)$ ns or as high as  $(36t_T + 16)$ ns due to spread-spectrum variations (see Figure 6).

The MAX9250 input-to-output delay can be as low as  $(3.575t_T + 8)$ ns or as high as  $(3.725t_T + 16)$ ns.

M/XI/M

#### **Spread-Spectrum Selection**

The MAX9248 single-ended data and clock outputs are programmable for a variation of  $\pm 2\%$  or  $\pm 4\%$  around the LVDS input clock frequency. The modulation rate of the frequency variation is 32kHz for a 33MHz LVDS clock input and scales linearly with the clock frequency (see Table 4). The output spread is controlled through the SS input (see Table 5). Driving SS high spreads all data and clock outputs by  $\pm 4\%$ , while pulling low spreads  $\pm 2\%$ .

#### **Table 4. Modulation Rate**

| fpclk_in | f <sub>M</sub> (kHz) = f <sub>PCLK_IN</sub> / 1024 |  |

|----------|----------------------------------------------------|--|

| 8        | 7.81                                               |  |

| 10       | 9.77                                               |  |

| 16       | 15.63                                              |  |

| 32       | 31.25                                              |  |

| 40       | 39.06                                              |  |

| 42       | 41.01                                              |  |

#### Table 5. SS Function

| SS INPUT LEVEL | OUTPUT SPREAD                                       |

|----------------|-----------------------------------------------------|

| High           | Data and clock output spread ±4% relative to REFCLK |

| Low            | Data and clock output spread ±2% relative to REFCLK |

Any spread change causes a delay time of 32,000 x t<sub>T</sub> before output data is valid. When the spread amount is changed from  $\pm 2\%$  to  $\pm 4\%$  or vice versa, the data outputs go low for one t<sub>ASSPLL</sub> delay (see Figure 17). The data outputs stay low, but are not valid when the spread amount is changed.

#### Output Enable (OUTEN) and Busing Outputs

The outputs of two MAX9250s can be bused to form a 2:1 mux with the outputs controlled by the output enable. Wait 30ns between disabling one deserializer (driving OUTEN low) and enabling the second one (driving OUTEN high) to avoid contention of the bused outputs. OUTEN controls all outputs except LOCK.

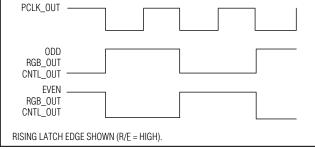

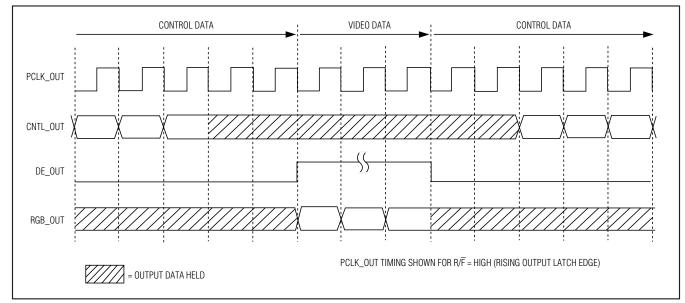

**Rising or Falling Output Latch Edge (R/F)** The MAX9248/MAX9250 have a selectable rising or falling output latch edge through a logic setting on R/F. Driving R/F high selects the rising output latch edge, which latches the parallel output data into the next chip on the rising edge of PCLK\_OUT. Driving R/F low selects the falling output latch edge, which latches the parallel output data into the next chip on the falling edge of PCLK\_OUT. The MAX9248/MAX9250 outputlatch-edge polarity does not need to match the MAX9247 serializer input-latch-edge polarity. Select the latch-edge polarity required by the chip being driven by the MAX9248/MAX9250.

Figure 18. Output Timing

#### Staggered and Transition Time Adjusted Outputs

RGB\_OUT[17:0] are grouped into three groups of six, with each group switching about 1ns apart in the video phase to reduce EMI and ground bounce. CNTL\_OUT[8:0] switch during the control phase. Output transition times are slower in the 2.5MHz to 5MHz and 5MHz to 10MHz ranges and faster in the 10MHz to 20MHz and 20MHz to 42MHz ranges.

#### Data-Enable Output (DE\_OUT)

The MAX9248/MAX9250 deserialize video and control data at different times. Control data is deserialized during the video blanking time. DE\_OUT high indicates that video data is being deserialized and output on RGB\_OUT[17:0]. DE\_OUT low indicates that control data is being deserialized and output on CNTL\_OUT[8:0]. When outputs are not being updated, the last data received is latched on the outputs. Figure 18 shows the DE\_OUT timing.

#### Power-Supply Sequencing of MAX9247 and MAX9248/MAX9250 Video Link

The MAX9247 and MAX9248/MAX9250 video link can be powered up in several ways. The best approach is to keep both MAX9247 and MAX9248 powered down while supplies are ramping up and PCLK\_IN of the MAX9247 and REFCLK of the MAX9248/MAX9250 are stabilizing. After all of the power supplies of the MAX9247 and MAX9248/MAX9250 are stable, including PCLK\_IN and REFCLK, do the following:

- Power up the MAX9247 first

- Wait for at least t<sub>LOCK</sub> of MAX9247 (or 17100 x t<sub>T</sub>) to get activity on the link

- Power up the MAX9248

**Power-Supply Circuits and Bypassing** There are separate on-chip power domains for digital circuits and LVTTL/LVCMOS inputs (V<sub>CC</sub> supply and GND), outputs (V<sub>CCO</sub> supply and V<sub>CCOGND</sub>), PLL (V<sub>CCPLL</sub> supply and PLLGND), and the LVDS input (V<sub>CCLVDS</sub> supply and LVDSGND). The grounds are isolated by diode connections. Bypass each V<sub>CC</sub>, V<sub>CCO</sub>, V<sub>CCPLL</sub>, and V<sub>CCLVDS</sub> pin with high-frequency, surface-mount ceramic 0.1µF and 0.001µF capacitors in parallel as close to the device as possible, with the smallest value capacitor closest to the supply pin. The outputs are powered from V<sub>CCO</sub>, which accepts a 1.71V to 3.6V supply, allowing direct interface to inputs with 1.8V to 3.3V logic levels.

#### **Cables and Connectors**

Interconnect for LVDS typically has a differential impedance of  $100\Omega$ . Use cables and connectors that have matched differential impedance to minimize impedance discontinuities.

Twisted-pair and shielded twisted-pair cables offer superior signal quality compared to ribbon cable and tend to generate less EMI due to magnetic field canceling effects. Balanced cables pick up noise as common mode, which is rejected by the LVDS receiver.

17

Figure 19. Human Body ESD Test Circuit

MAX9248/MAX9250

Figure 21. ISO 10605 Contact Discharge ESD Test Circuit

#### **Board Layout**

Separate the LVTTL/LVCMOS outputs and LVDS inputs to prevent crosstalk. A four-layer PCB with separate layers for power, ground, and signals is recommended.

#### **ESD** Protection

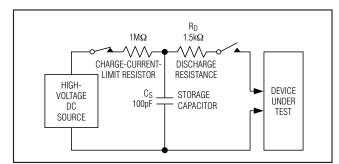

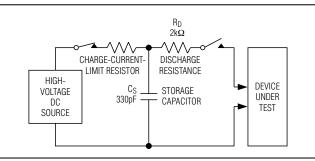

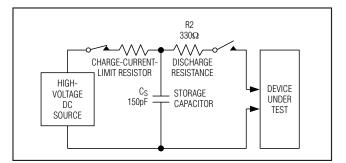

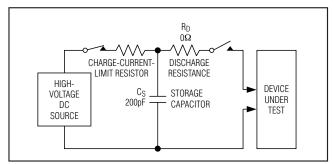

The MAX9248/MAX9250 ESD tolerance is rated for Human Body Model, Machine Model, IEC 61000-4-2 and ISO 10605. The ISO 10605 and IEC 61000-4-2 standards specify ESD tolerance for electronic systems. All LVDS inputs on the MAX9248/MAX9250 meet ISO 10605 ESD protection at ±30kV Air-Gap Discharge and ±10kV Contact Discharge and IEC 61000-4-2 ESD protection at ±15kV Air-Gap Discharge and ±10kV Contact Discharge. All other pins meet the Human Body Model ESD tolerance of ±2kV. The Human Body Model discharge components are Cs = 100pF and RD =  $1.5k\Omega$ (Figure 19). The IEC 61000-4-2 discharge components are Cs = 150pF and RD =  $330\Omega$  (see Figure 20). The ISO 10605 discharge components are  $C_S = 330 pF$  and  $R_D =$ 2kΩ (Figure 21). The Machine Model discharge components are  $C_S = 200 \text{pF}$  and  $R_D = 0 \Omega$  (Figure 22).

Figure 20. IEC 61000-4-2 Contact Discharge ESD Test Circuit

Figure 22. Machine Model ESD Test Circuit

### Pin Configuration

### Chip Information

PROCESS: CMOS

### \_Package Information

For the latest package outline information and land patterns, go to **www.maxim-ic.com/packages**.

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO.   |

|--------------|--------------|----------------|

| 48 LQFP      | C48+3        | <u>21-0054</u> |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                  | PAGES<br>CHANGED |

|--------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2                  | 5/08             | Replaced TQFP and TQFN packages with LQFP package, changed temperature limits for +105°C part, and added Machines Model ESD text and diagram | 1–5, 7, 16–19    |

| 3                  | 4/09             | Added /V parts in the Ordering Information table and added new Power-<br>Supply Sequencing of MAX9247 and MAX9248/MAX9250 Video Link section | 1, 17            |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2009 Maxim Integrated Products

Maxim is a registered trademark of Maxim Integrated Products, Inc.