# **DATA SHEET**

# **2GB Fully Buffered DIMM**

# **EBE21FE8ACWR**

# **Specifications**

Density: 2GBOrganization

— 256M words × 72 bits, 2 ranks

Mounting 18 pieces of 1G bits DDR2 SDRAM sealed in FBGA

Package

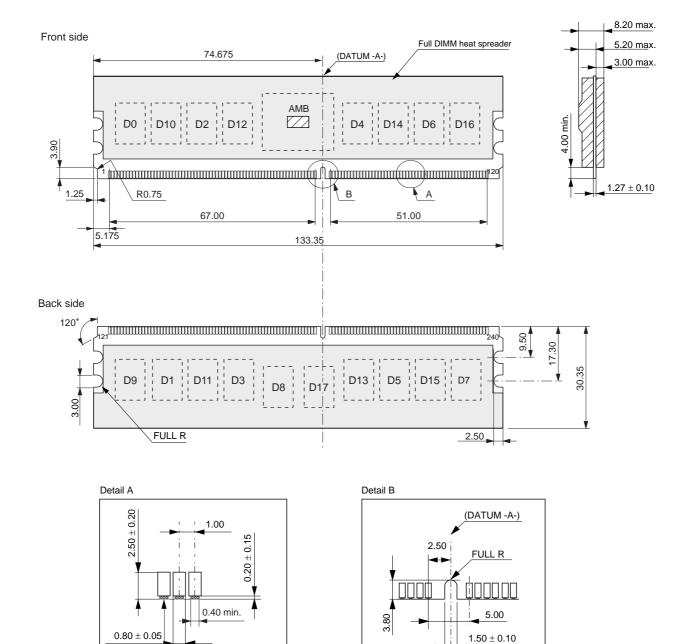

240-pin fully buffered, socket type dual in line memory module (FB-DIMM)

PCB height: 30.35mm Lead pitch: 1.00mm

— Advanced Memory Buffer (AMB): 655-ball FCBGA

Lead-free (RoHS compliant)

Power supply

— DDR2 SDRAM:  $VDD = 1.8V \pm 0.1V$ — AMB: VCC = 1.5V + 0.075V/ -0.045V

• Data rate: 667Mbps (max.)

Eight internal banks for concurrent operation (components)

Interface: SSTL\_18Burst lengths (BL): 4, 8

/CAS Latency (CL): 3, 4, 5

Precharge: auto precharge option for each burst access

Refresh: auto-refresh, self-refreshRefresh cycles: 8192 cycles/64ms

Average refresh period

7.8μs at 0°C ≤ TC ≤ +85°C

3.9μs at +85°C < TC ≤ +95°C</li>

• Operating case temperature range

— TC =  $0^{\circ}$ C to  $+95^{\circ}$ C

#### **Features**

- JEDEC standard Raw Card B Design

- Industry Standard Advanced Memory Buffer (AMB)

- High-speed differential point-to-point link interface at 1.5V (JEDEC spec)

- 14 north-bound (NB) high speed serial lanes

- 10 south-bound (SB) high speed serial lanes

- Various features/modes:

- MemBIST and IBIST test functions

- Transparent mode and direct access mode for DRAM testing

- Interface for a thermal sensor and status indicator

- · Channel error detection and reporting

- Automatic DDR2 SDRAM bus and channel calibration

- SPD (serial presence detect) with 1piece of 256 byte serial EEPROM

Note: Warranty void if removed DIMM heat spreader.

#### **Performance**

|                        | FB-DIMM     |                         |                        | DDR2 SDRAM       |               |

|------------------------|-------------|-------------------------|------------------------|------------------|---------------|

| System clock frequency | Speed grade | Peak channel throughput | FB-DIMM link data rate | Speed Grade      | DDR data rate |

| 167MHz                 | PC2-5300F   | 8.0GByte/s              | 4.0Gbps                | DDR2-667 (5-5-5) | 667Mbps       |

URL: http://www.elpida.com

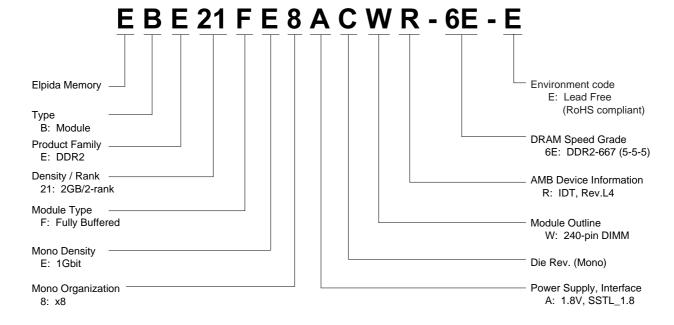

# **Ordering Information**

| Part number       | DIMM speed grade | Component JEDEC speed bin (CL-tRCD-tRP) | Mounted devices*1 | Mounted AMB*2 |

|-------------------|------------------|-----------------------------------------|-------------------|---------------|

| EBE21FE8ACWR-6E-E | PC2-5300F        | DDR2-667 (5-5-5)                        | EDE1108ACBG-8E-E  | IDT Rev. L4   |

- Notes: 1. Please refer to the EDE1104ACBG, EDE1108ACBG, EDE1116ACBG datasheet (E1173E) for detailed operation part and timing waveforms.

- 2. Please refer to the following documents for detailed operation part and timing waveforms.

Advanced Memory Buffer (AMB) specification

FB-DIMM Architecture and Protocol specification

#### **Part Number**

### **Advanced Memory Buffer Overview**

The Advanced Memory Buffer (AMB) reference design complies with the FB-DIMM Architecture and Protocol Specification. It supports DDR2 SDRAM main memory. The AMB allows buffering of memory traffic to support large memory capacities. All memory control for the DRAM resides in the host, including memory request initiation, timing, refresh, scrubbing, sparing, configuration access, and power management. The AMB interface is responsible for handling FB-DIMM channel and memory requests to and from the local DIMM and for forwarding requests to other DIMMs on the FB-DIMM channel.

The FB-DIMM provides a high memory bandwidth, large capacity channel solution that has a narrow host interface. FB-DIMMs use commodity DRAMs isolated from the channel behind a buffer on the DIMM. The memory capacity is 288 devices per channel and total memory capacity scales with DRAM bit density.

The AMB is the buffer that isolates the DRAMs from the channel.

### **Advanced Memory Buffer Functionality**

The AMB will perform the following FB-DIMM channel functions.

- Supports channel initialization procedures as defined in the initialization chapter of the FB-DIMM Architecture and Protocol Specification to align the clocks and the frame boundaries, verify channel connectivity, and identify AMB DIMM position.

- Supports the forwarding of southbound and northbound frames, servicing requests directed to a specific AMB or DIMM, as defined in the protocol chapter, and merging the return data into the northbound frames.

- If the AMB resides on the last DIMM in the channel, the AMB initializes northbound frames.

- Detects errors on the channel and reports them to the host memory controller.

- Support the FB-DIMM configuration register set as defined in the register chapters.

- · Acts as DRAM memory buffer for all read, write, and configuration accesses addressed to the DIMM.

- Provides a read buffer FIFO and a write buffer FIFO.

- Supports an SMBus protocol interface for access to the AMB configuration registers.

- Provides logic to support MemBIST and IBIST design for test functions.

- Provides a register interface for the thermal sensor and status indicator.

- Functions as a repeater to extend the maximum length of FB-DIMM links.

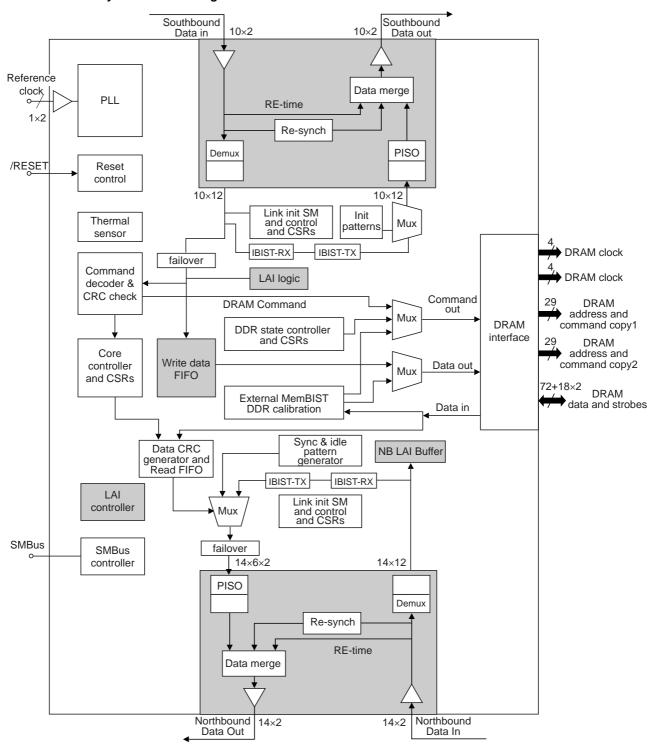

### **Advanced Memory Buffer Block Diagram**

Note: This figure is a conceptual block diagram of the AMB's data flow and clock domains.

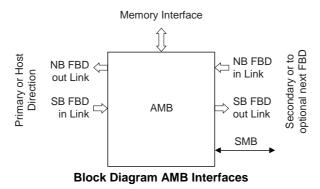

#### **Interfaces**

Figure Block Diagram AMB Interfaces shows the AMB and all of its interfaces. They consist of two FB-DIMM links, one DDR2 channel and an SMBus interface. Each FB-DIMM link connects the AMB to a host memory controller or an adjacent FB-DIMM. The DDR2 channel supports direct connection to the DDR2 SDRAMs on an FB-DIMM.

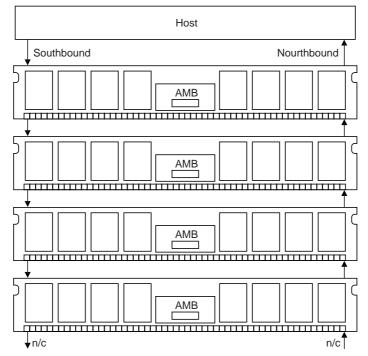

# **Interface Topology**

The FB-DIMM channel uses a daisy-chain topology to provide expansion from a single DIMM per channel to up to 8 DIMMs per channel. The host sends data on the southbound link to the first DIMM where it is received and redriven to the second DIMM. On the southbound data path each DIMM receives the data and again re-drives the data to the next DIMM until the last DIMM receives the data. The last DIMM in the chain initiates the transmission of data in the direction on the host (a.k.a. northbound). On the northbound data path each DIMM receives the data and re-drives the data to the next DIMM until the host is reached.

**Block Diagram FB-DIMM Channel Southbound and Northbound Paths**

#### High-Speed Differential Point-to-Point Link (at 1.5 V) Interfaces

The AMB supports one FB-DIMM channel consisting of two bidirectional link interfaces using high-speed differential point-to-point electrical signaling. The southbound input link is 10 lanes wide and carries commands and write data from the host memory controller or the adjacent DIMM in the host direction. The southbound output link forwards this same data to the next FB-DIMM. The northbound input link is 14 lanes wide and carries read return data or status information from the next FB-DIMM in the chain back towards the host. The northbound output link forwards this information back towards the host and multiplexes in any read return data or status information that is generated internally. Data and commands sent to the DRAMs travel southbound on 10 primary differential signal line pairs. Data received from the DRAMs and status information travel northbound on 14 primary differential pairs. Data and commands sent to the adjacent DIMM upstream are repeated and travel further southbound on 10 secondary differential pairs. Data and status information received from the adjacent DIMM upstream travel further northbound on 14 secondary differential pairs.

#### **DDR2 Channel**

The DDR2 channel on the AMB supports direct connection to DDR2 SDRAMs. The DDR2 channel supports two ranks of eight banks with 16 row/column request, 64 data, and eight check-bit signals. There are two copies of address and command signals to support DIMM routing and electrical requirements. Four transfer bursts are driven on the data and check-bit lines at 800MHz. Propagation delays between read data/check-bit strobe lanes on a given channel can differ. Each strobe can be calibrated by hardware state machines using write/read trial and error. Hardware aligns the read data and check-bits to a single core clock. The AMB provides four copies of the command clock phase references (CLK [3:0]) and write data/check-bit strobes (DQSs) for each DRAM nibble.

#### **SMBus Slave interface**

The AMB supports an SMBus interface to allow system access to configuration register independent of the FB-DIMM link. The AMB will never be a master on the SMBus, only a slave. Serial SMBus data transfer is supported at 100kHz. SMBus access to the AMB may be a requirement to boot and to set link strength, frequency and other parameters needed to insure robust configurations. It is also required for diagnostic support when the link is down. The SMBus address straps located on the DIMM connector are used by the unique ID.

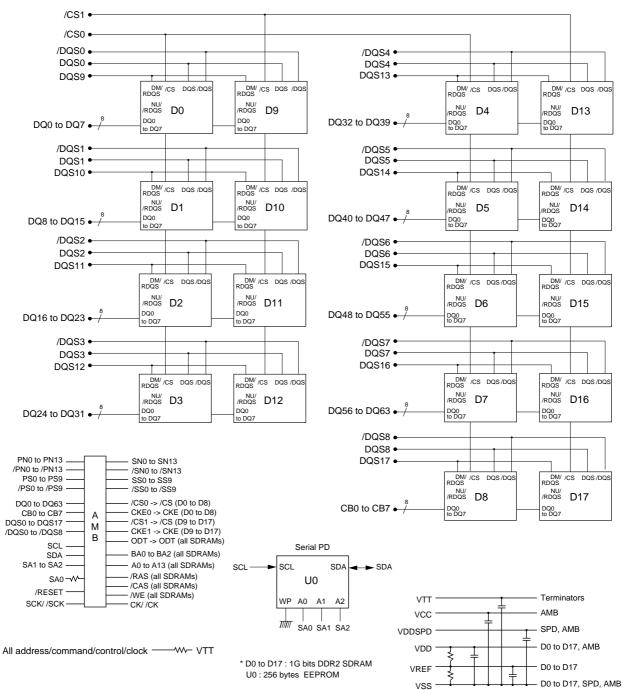

### **Block Diagram**

# Notes:

- 1. DQ wiring may be changed within a byte.

- 2. There are two physical copies of each address/command/control/clock

# **Pin Configurations**

|     |              |     |       |     |      | [ P     |           |

|-----|--------------|-----|-------|-----|------|---------|-----------|

|     |              |     |       |     |      |         | Back side |

|     | -1.1         |     |       |     |      |         |           |

| No. | side<br>Name | No. | Name  | No. | Name | No.     | Name      |

|     |              |     |       |     |      |         |           |

| 1   | VDD          | 36  | VSS   | 71  | /PS0 | 106     | NC        |

| 2   | VDD          | 37  | PN5   | 72  | VSS  | 107     | VSS       |

| 3   | VDD          | 38  | /PN5  | 73  | PS1  | 108     | VDD       |

| 4   | VSS          | 39  | VSS   | 74  | /PS1 | 109     | VDD       |

| 5   | VDD          | 40  | PN13  | 75  | VSS  | 110     | VSS       |

| 6   | VDD          | 41  | /PN13 | 76  | PS2  | 111     | VDD       |

| 7   | VDD          | 42  | VSS   | 77  | /PS2 | 112     | VDD       |

| 8   | VSS          | 43  | VSS   | 78  | VSS  | 113     | VDD       |

| 9   | VCC          | 44  | NC    | 79  | PS3  | 114     | VSS       |

| 10  | VCC          | 45  | NC    | 80  | /PS3 | 115     | VDD       |

| 11  | VSS          | 46  | VSS   | 81  | VSS  | 116     | VDD       |

| 12  | VCC          | 47  | VSS   | 82  | PS4  | 117     | VTT       |

| 13  | VCC          | 48  | PN12  | 83  | /PS4 | 118     | SA2       |

| 14  | VSS          | 49  | /PN12 | 84  | VSS  | 119     | SDA       |

| 15  | VTT          | 50  | VSS   | 85  | VSS  | 120     | SCL       |

| 16  | VID1         | 51  | PN6   | 86  | NC   |         |           |

| 17  | /RESET       | 52  | /PN6  | 87  | NC   | <u></u> |           |

| 18  | VSS          | 53  | VSS   | 88  | VSS  | <u></u> |           |

| 19  | NC           | 54  | PN7   | 89  | VSS  |         |           |

| 20  | NC           | 55  | /PN7  | 90  | PS9  | <u></u> |           |

| 21  | VSS          | 56  | VSS   | 91  | /PS9 | <u></u> |           |

| 22  | PN0          | 57  | PN8   | 92  | VSS  |         |           |

| 23  | /PN0         | 58  | /PN8  | 93  | PS5  |         |           |

| 24  | VSS          | 59  | VSS   | 94  | /PS5 |         |           |

| 25  | PN1          | 60  | PN9   | 95  | VSS  |         |           |

| 26  | /PN1         | 61  | /PN9  | 96  | PS6  | _       |           |

| 27  | VSS          | 62  | VSS   | 97  | /PS6 |         |           |

| 28  | PN2          | 63  | PN10  | 98  | VSS  |         |           |

|     |              |     |       |     |      |         |           |

PS7

/PS7

VSS

PS8

/PS8

VSS

NC

| Back | side   |     |       |     |      |          |        |

|------|--------|-----|-------|-----|------|----------|--------|

| No.  | Name   | No. | Name  | No. | Name | No.      | Name   |

| 121  | VDD    | 156 | VSS   | 191 | /SS0 | 226      | NC     |

| 122  | VDD    | 157 | SN5   | 192 | VSS  | 227      | VSS    |

| 123  | VDD    | 158 | /SN5  | 193 | SS1  | 228      | SCK    |

| 124  | VSS    | 159 | VSS   | 194 | /SS1 | 229      | /SCK   |

| 125  | VDD    | 160 | SN13  | 195 | VSS  | 230      | VSS    |

| 126  | VDD    | 161 | /SN13 | 196 | SS2  | 231      | VDD    |

| 127  | VDD    | 162 | VSS   | 197 | /SS2 | 232      | VDD    |

| 128  | VSS    | 163 | VSS   | 198 | VSS  | 233      | VDD    |

| 129  | VCC    | 164 | NC    | 199 | SS3  | 234      | VSS    |

| 130  | VCC    | 165 | NC    | 200 | /SS3 | 235      | VDD    |

| 131  | VSS    | 166 | VSS   | 201 | VSS  | 236      | VDD    |

| 132  | VCC    | 167 | VSS   | 202 | SS4  | 237      | VTT    |

| 133  | VCC    | 168 | SN12  | 203 | /SS4 | 238      | VDDSPD |

| 134  | VSS    | 169 | /SN12 | 204 | VSS  | 239      | SA0    |

| 135  | VTT    | 170 | VSS   | 205 | VSS  | 240      | SA1    |

| 136  | VID0   | 171 | SN6   | 206 | NC   |          |        |

| 137  | M_TEST | 172 | /SN6  | 207 | NC   | -        |        |

| 138  | VSS    | 173 | VSS   | 208 | VSS  | -        |        |

| 139  | NC     | 174 | SN7   | 209 | VSS  | -        |        |

| 140  | NC     | 175 | /SN7  | 210 | SS9  | <u>-</u> |        |

| 141  | VSS    | 176 | VSS   | 211 | /SS9 | <u>-</u> |        |

| 142  | SN0    | 177 | SN8   | 212 | VSS  | <u>-</u> |        |

| 143  | /SN0   | 178 | /SN8  | 213 | SS5  | <u>-</u> |        |

| 144  | VSS    | 179 | VSS   | 214 | /SS5 | -        |        |

| 145  | SN1    | 180 | SN9   | 215 | VSS  | -        |        |

| 146  | /SN1   | 181 | /SN9  | 216 | SS6  | -        |        |

| 147  | VSS    | 182 | VSS   | 217 | /SS6 | -        |        |

| 148  | SN2    | 183 | SN10  | 218 | VSS  | -        |        |

| 149  | /SN2   | 184 | /SN10 | 219 | SS7  | -        |        |

| 150  | VSS    | 185 | VSS   | 220 | /SS7 | -        |        |

| 151  | SN3    | 186 | SN11  | 221 | VSS  | -        |        |

| 152  | /SN3   | 187 | /SN11 | 222 | SS8  | <u>-</u> |        |

| 153  | VSS    | 188 | VSS   | 223 | /SS8 | -        |        |

| 154  | SN4    | 189 | VSS   | 224 | VSS  | -        |        |

| 155  | /SN4   | 190 | SS0   | 225 | NC   | -        |        |

|      |        |     |       |     |      |          |        |

/PN2

VSS

PN3

/PN3

VSS

PN4

/PN4

64

65

66

67

68

69

70

/PN10 99

100

101

102

103

104

105

VSS

PN11

/PN11

VSS

VSS

PS0

29

30

31

32

33

34

35

# **Pin Description**

| Pin name                   | Pin Type       | Function                                                    |

|----------------------------|----------------|-------------------------------------------------------------|

| SCK, /SCK                  | Input          | System clock input                                          |

| PN0 to PN13, /PN0 to /PN13 | Output         | Primary northbound data                                     |

| PS0 to PS9, /PS0 to /PS9   | Input          | Primary southbound data                                     |

| SN0 to SN13, /SN0 to /SN13 | Input          | Secondary northbound data                                   |

| SS0 to SS9, /SS0 to /SS9   | Output         | Secondary southbound data                                   |

| SCL                        | Input          | Serial presence detect (SPD) clock input                    |

| SDA                        | Input / Output | SPD data and AMB SMBus address/data                         |

| SA0 to SA2*1               | Input          | SPD address inputs                                          |

| VID0 to VID1*2             | Input          | Voltage ID                                                  |

| /RESET                     | Input          | AMB reset signal                                            |

| M_TEST*3                   | Input          | VREF margin test input                                      |

| NC                         | _              | No connection                                               |

| VCC                        | Power supply   | AMB core power and AMB channel interface power (1.5V)       |

| VDD                        | Power supply   | DRAM power and AMB DRAM I/O power (1.8V)                    |

| VTT                        | Power supply   | DRAM address, Command and clock termination voltage (VDD/2) |

| VDDSPD                     | Power supply   | SPD power (3.3V)                                            |

| VSS                        | _              | Ground                                                      |

Notes: 1. They are also used to select the DIMM number in the AMB.

- 2. These pins must be unconnected.

- 3. Don't connect in a system.

# **Electrical Specifications**

• All voltages are referenced to VSS (GND).

# **Absolute Maximum Ratings**

| Parameter                                    | Symbol   | Value         | Unit | Note |  |

|----------------------------------------------|----------|---------------|------|------|--|

| Voltage on any pin relative to VSS           | VIN/VOUT | -0.3 to +1.75 | V    |      |  |

| AMB core power voltage relative to VSS       | VCC      | -0.3 to +1.75 | V    |      |  |

| DRAM interface power voltage relative to VSS | VDD      | -0.5 to +2.30 | V    |      |  |

| Termination voltage relative to VSS          | VTT      | -0.5 to +2.30 | V    |      |  |

| Storage temperature                          | Tstg     | -55 to +100   | °C   |      |  |

#### Caution

Exposing the device to stress above those listed in Absolute Maximum Ratings could cause permanent damage. The device is not meant to be operated under conditions outside the limits described in the operational section of this specification. Exposure to Absolute Maximum Rating conditions for extended periods may affect device reliability.

# **Operating Temperature Conditions**

| Parameter                        | Symbol  | Value    | Unit | Note |

|----------------------------------|---------|----------|------|------|

| SDRAM component case temperature | TC_DRAM | 0 to +95 | °C   | 1    |

| AMB component case temperature   | TC_AMB  | 110      | °C   | _    |

Note: 1. Supporting 0°C to +85°C and being able to extend to +95°C with doubling auto-refresh commands in frequency to a 32ms period (tREFI =  $3.9\mu s$ ) and higher temperature self-refresh entry via the control of EMRS (2) bit A7 is required.

# **DC Operating Conditions**

| Parameter                 | Symbol   | min.       | typ.              | max.       | Unit | Note |

|---------------------------|----------|------------|-------------------|------------|------|------|

| AMB supply voltage        | VCC      | 1.455      | 1.50              | 1.575      | V    |      |

| DDR2 SDRAM supply voltage | VDD      | 1.7        | 1.8               | 1.9        | V    |      |

| Input termination voltage | VTT      | 0.48 × VDD | $0.50 \times VDD$ | 0.52 × VDD | V    |      |

| EEPROM supply voltage     | VDDSPD   | 3.0        | 3.3               | 3.6        | V    |      |

| SPD input high voltage    | VIH (DC) | 2.1        | _                 | VDDSPD     | V    | 1    |

| SPD input low voltage     | VIL (DC) | _          | _                 | 0.8        | V    | 1    |

| RESET input high voltage  | VIH (DC) | 1.0        | _                 | _          | V    | 2    |

| RESET input low voltage   | VIL (DC) | _          | _                 | 0.5        | V    | 2    |

| Leakage current (RESET)   | IL       | -90        | _                 | 90         | μΑ   | 2    |

| Leakage current (link)    | IL       | <b>-</b> 5 | _                 | 5          | μΑ   | 3    |

Notes: 1. Applies for SMB and SPD bus signals.

- 2. Applies for AMB CMOS signal /RESET.

- 3. For all other AMB related DC parameters, please refer to the high-speed differential link interface specification.

**ELPIDA**

# **AMB Component Timing**

For purposes of IDD testing, the following parameters are to be utilized.

| Parameter                       | Symbol           | min. | typ.  | max.     | Units  | Note |

|---------------------------------|------------------|------|-------|----------|--------|------|

| El Assertion pass-thru timing   | tEI<br>propagate | _    | _     | 4        | clks   |      |

| El deassertion pass-thru timing | tEID             | _    | _     | bit lock | clks   |      |

| El assertion duration           | tEI              | 100  | _     | _        | clks   |      |

| Resample pass-thru time         |                  | _    | 1.075 | _        | ns     |      |

| Resynch pass-thru time          |                  | _    | 2.075 | _        | ns     |      |

| Bit lock Interval               | tBitLock         | _    | _     | 119      | frames |      |

| Frame lock Interval             | tFrameLock       | _    | _     | 154      | frames |      |

Note: 1. The EI stands for "Electrical Idle".

# **Power Specification Parameter and Test Conditions**

|                                 |                |              | -6E                                                                         |      |                                                                                             |      |

|---------------------------------|----------------|--------------|-----------------------------------------------------------------------------|------|---------------------------------------------------------------------------------------------|------|

| Frequency (Mbps)                |                |              | 667                                                                         |      |                                                                                             |      |

| Parameter                       | Symbol         | Power Supply | max.                                                                        | Unit | Conditions                                                                                  | Note |

| Idle Current,                   |                | @1.5V        | 1.60                                                                        | Α    | L0 state, idle (0 BW)  — Primary channel enabled,                                           |      |

| single or last                  | Idd_Idle_0     | @1.8V        | 1.19                                                                        | Α    | Secondary channel disabled                                                                  |      |

| DIIVIIVI                        |                | Total        | 4.12                                                                        | W    | <ul> <li>CKE high. Command and address lines stable.</li> <li>DRAM clock active.</li> </ul> |      |

|                                 |                | @1.5V        | 2.30                                                                        | Α    | L0 state, idle (0 BW)                                                                       |      |

| Idle Current, first DIMM        | ldd_ldle_1     | @1.8V        | 1.19                                                                        | Α    | Primary and secondary channels enabled CKE high. Command and address lines stable.          |      |

|                                 |                | Total        | 5.23                                                                        | W    | DRAM clock active.                                                                          |      |

|                                 |                | @1.5V        | 2.90                                                                        | Α    | L0 state                                                                                    |      |

| Active Power                    | Idd_Active_1   | @1.8V        | 2.39                                                                        | Α    | 50% DRAM BW, 67% read, 33% write. Primary and secondary channels enabled.                   |      |

|                                 |                | Total        | 8.46                                                                        | W    | DRAM clock active, CKE high.                                                                |      |

|                                 |                | @1.5V        | 2.40                                                                        | Α    | L0 state<br>50% DRAM BW to downstream DIMM,                                                 |      |

| Active Power, data pass through | Idd_Active_2   | @1.8V        | 1.19                                                                        | Α    | 67% read, 33% write. Primary and secondary channels enabled.                                |      |

| , ,                             |                | Total        | 5.39                                                                        | W    | CKE high. Command and address lines stable.  DRAM clock active.                             |      |

|                                 | © 1.3 V 2.30 A |              | Primary and secondary channels enabled.  — 100% toggle on all channel lanes |      |                                                                                             |      |

| Training                        | (for AMB spec. | @1.8V        | 1.14                                                                        | Α    | DRAMs idle. 0 BW.                                                                           |      |

|                                 | Not in SPD)    | Total        | 5.13                                                                        | W    | <ul> <li>CKE high, Command and address lines stable.</li> <li>DRAM clock active.</li> </ul> |      |

# Reference Clock Input Specifications\*1

| Parameter                                                              | Symbol                                    | min.             | max.   | Units   | Notes                                                         |

|------------------------------------------------------------------------|-------------------------------------------|------------------|--------|---------|---------------------------------------------------------------|

| Reference clock frequency@ 4.0 Gb/s (nominal 166.67MHz)                | fRefclk-4.0                               | 158.33           | 166.75 | MHz     | 2, 3, 4                                                       |

| Single-ended maximum voltage                                           | Vmax                                      | _                | 1.15   | V       | 5, 7                                                          |

| Single-ended minimum voltage                                           | Vmin                                      | -0.3             | _      | V       | 5, 8                                                          |

| Differential voltage high                                              | VRefclk-diff-ih                           | 150              | _      | mV      | 6                                                             |

| Differential voltage low                                               | VRefclk-diff-il                           | _                | -150   | mV      | 6                                                             |

| Absolute crossing point                                                | VCross                                    | 250              | 550    | mV      | 5, 9, 10                                                      |

| VCross variation                                                       | VCross-delta                              | _                | 140    | mV      | 5, 9, 11                                                      |

| AC common mode                                                         | VSCK-cm-acp-p                             | _                | 225    | mV      | 12                                                            |

| Rising and falling edge rates                                          | ERRefclk-diff-Rise,<br>ERRefclk-diff-Fall | 0.6              | 4.0    | V/ns    | 6, 13                                                         |

| % Mismatch between rise and fall edge rates                            | ERRefclk-Match                            | _                | 20     | %       | 6, 14                                                         |

| Duty cycle of reference clock                                          | TRefclk-Dutycycle                         | 40               | 60     | %       | 6                                                             |

| Ringback voltage threshold                                             | VRB-diff                                  | -100             | 100    | mV      | 6, 15                                                         |

| Allowed time before ringback                                           | TStable                                   | 500              | _      | ps      | 6, 15                                                         |

| Clock leakage current                                                  | II_CK                                     | -10              | 10     | μΑ      | 16, 17                                                        |

| Clock input capacitance                                                | CI_CK                                     | 0.5              | 2.0    | pF      | 17                                                            |

| Clock input capacitance delta                                          | CI_CK (Δ)                                 | -0.25            | 0.25   | pF      | Difference between<br>RefClk and RefClk#<br>input capacitance |

| Transport delay                                                        | TD                                        | _                | 5      | ns      | 18, 19                                                        |

|                                                                        | NSAMPLE                                   | 10 <sup>12</sup> | _      | periods | 20                                                            |

| Reference clock jitter (rms), filtered                                 | TREF-JITTER-RMS                           | _                | 3.0    | ps      | 21, 22                                                        |

| Reference clock jitter (peak-to-peak) due to spectrum clocking effects | TREF-SSCp-p                               | _                | 30     | ps      |                                                               |

| Reference clock jitter difference between adjacent AMB                 | TREF-JITTER-<br>DELTA                     | _                | 0.75   | ps      | 23                                                            |

Notes: 1. For details, refer to the JEDEC specification "FB-DIMM High Speed Differential PTP Link at 1.5V".

- 2. The nominal reference clock frequency is determined by the data frequency of the link divided by 2 times the fixed PLL multiplication factor for the FB-DIMM channel (6:1). fdata = 2000MHz for a 4.0Gbps FB-DIMM channel and so on.

- 3. Measured with SSC disabled. Enabling SSC will reduce the reference clock frequency.

- 4. Not all FB-DIMM agents will support all frequencies; compliance to the frequency specifications is only required for those data rates that are supported by the device under test.

- 5. Measurement taken from single-ended waveform.

- 6. Measurement taken from differential waveform.

- 7. Defined as the maximum instantaneous voltage including overshoot.

- 8. Defined as the minimum instantaneous voltage including undershoot.

- 9. Measured at the crossing point where the instantaneous voltage value of the rising edge of REFCLK+ equals the falling edge of REFCLK-.

- 10. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement.

- 11. Defined as the total variation of all crossing voltages of rising REFCLK+ and falling REFCLK-. This is the maximum allowed variance in for any particular system.

- 12. The majority of the reference clock AC common mode occurs at high frequency (i.e., the reference clock frequency).

**ELPIDA**

- 13. Measured from -150mV to + 150mV on the differential waveform. The signal must be monotonic through the measurement region for rise and fall time. The 300mV measurement window is centered on the differential 0V crossing.

- 14. Edge rate matching applies to rising edge rate for REFCLK+ and falling edge rate for REFCLK-. It is measured using a ± 75mV window centered on the median cross point where REFCLK+ rising meets REFCLK- falling. The median crosspoint is used to calculate the voltage thresholds the oscilloscope uses for the edge rate calculations. The rising edge rate of REFCLK+ should be compared to the falling edge rate of REFCLK-. The maximum allowed difference should not exceed 20% of the slowest edge

- 15. Tstable is the time the differential clock must maintain a minimum ±150mV differential voltage after rising /falling edges before it is allowed to droop back into the ±100mV differential range.

- 16. Measured with a single-ended input voltage of 1V.

- 17. Applies to RefClk and RefClk#.

- 18. This parameter is not a direct clock output parameter but it indirectly determines the clock output parameter TREF-JITTER.

- 19. The net transport delay is the difference in time of flight between associated data and clock paths. The data path is defined from the reference clock source, through the TX, to data arrival at the data sampling point in the RX. The clock path is defined from the reference clock source to clock arrival at the same sampling point. The path delays are caused by copper trace routes, on-chip routing, on-chip buffering, etc. They include the time-of-flight of interpolators or other clock adjustment mechanisms. They do not include the phase delays caused by finite PLL loop bandwidth because these delays are modeled by the PLL transfer functions.

- 20. Direct measurement of phase jitter records over NSAMPLE periods may be impractical. It is expected that the jitter will be measured over a smaller, yet statistically significant, sample size and the total jitter at NSAMPLE samples extrapolated from an estimate of the sigma of the random jitter components.

- 21. Measured with SSC enabled on reference clock generator.

- 22. As "measured" after the phase jitter filter. This number is separate from the receiver jitter budget that is defined by the TRX-Total-MIN parameters.

- 23. This maximum value is below the noise floor of some test equipment.

**ELPIDA**

# Differential Transmitter Output Specifications\*1

| Enformatial peak-to-peak voltage swing         VTX-DIFFp.p.L.         900         1300         mV         VTX-DIFFp.p.P.≥ ×   VTX-DIF-P.P. + VTX-D.   Measured as note 2           Differential peak-to-peak output voltage for regular voltage swing         VTX-DIFFp.P.R.         800         —         mV         VTX-DIFFp.P.P.P.2 ×   VTX-D VTX-D.   Measured as note 2           DC common code output voltage for farge voltage swing         VTX-CM_L.         —         375         mV         VTX-DIFFp.P.P.P.P.2 ×   VTX-D VTX-D.   Measured as note 2           DC common code output voltage for farge voltage swing but voltage for small voltage swing         VTX-CM_S.         135         280         mV         VTX-DIFFp.P.P.P.P.P.2 ×   VTX-D VTX-D   VTX-D   VTX-D   VTX-D   VTX-D   VTX-D   VTX-CM_S.         135         280         mV         VTX-CM_B.D.C (avg) of   VTX-D. + VTX-D   VT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Parameter                              | Symbol           | min. | max. | Unit | Comments                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|------|------|------|---------------------------------------------------------------------------------------|

| output voltage for regular voltage sing         VTX-DIFFP-P_R         800         — mV         VTX-DIFFP-P = 2 ×   VTX-D+ - VTX-D-  Measured as note 2           Differential peak-to-peak voltage swing         VTX-DIFFP-P_S         520         — mV         VTX-DIFFP-P = 2 ×   VTX-D+ - VTX-D-  Measured as note 2           DC common code output voltage for large voltage swing         VTX-CM_L         — 375         mV         VTX-CM_B = DC (avg) of  VTX-D+ + VTX-D-  2 Measured as note 2           DC common code output voltage for small voltage swing         VTX-CM_S         135         280         mV         VTX-CM_B = DC (avg) of  VTX-D+ + VTX-D-  2 Measured as note 2           De-emphasized differential output voltage six for 3-5dB de-emphasis         VTX-DE-3.5-Ratio         —3.0         —4.0         dB         2, 4, 5           De-emphasized differential output voltage ratio for 3-6dB de-emphasis         VTX-DE-6.0-Ratio         —5.0         —7.0         dB         2, 4, 5           De-emphasized differential output voltage for large vTX-CM-ACp-p L         — 90         mV         VTX-CM-AC = Max   VTX-D- /2 - Min   VTX-D+ vTX-D- /2 - Min   VTX-D-                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | output voltage for large               | VTX-DIFFp-p_L    | 900  | 1300 | mV   |                                                                                       |

| output voltage for small voltage for small voltage swing         VTX-DIFFp-p_S         520         mV         VTX-DIFFp-P_S (a) (VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX-CP-VTX                                                          | output voltage for regular             | VTX-DIFFp-p_R    | 800  | _    | mV   |                                                                                       |

| DC common code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | output voltage for small               | VTX-DIFFp-p_S    | 520  | _    | mV   |                                                                                       |

| output voltage for small voltage swing         VTX-CM_S         135         280         mV         VTX-CM = DC (avg) of  VTX-D+ + VTX-D- /2 Measured as note 2. See also note 3           De-emphasized differential output voltage ratio for 3.3dB de-emphasis         VTX-DE-3.5-Ratio         -3.0         -4.0         dB         2, 4, 5           3.3dB de-emphasis         VTX-DE-6.0-Ratio         -5.0         -7.0         dB         2, 4, 5           AC peak-to-peak common mode output voltage for large vTX-CM-ACp-p L swing         -         90         mV         VTX-CM-AC = Max   VTX-D- /2 - Min   VTX-D+ vTX-D- /2 - Min   VTX-D- /2 - VTX-D- /2 -                                                                                                                                                                                                                                                                               | output voltage for large               | VTX-CM_L         | _    | 375  | mV   | VTX-CM = DC (avg) of  VTX-D+<br>+ VTX-D- /2                                           |

| output voltage ratio for 3.3.5H Ade de-emphasis         VTX-DE-3.5-Ratio         -3.0         -4.0         dB         2, 4, 5           -3.5dB de-emphasized differential output voltage ratio for 6dB de-emphasis         VTX-DE-6.0-Ratio         -5.0         -7.0         dB         2, 4, 5           AC peak-to-peak common mode output voltage for large         VTX-CM-ACp-pL         —         90         mV         VTX-CM-AC = Max  VTX-D+ + VTX-D- /2 - Min  VTX-D+ + VTX-D+ + VTX-D- /2 - Min  VTX-D- + VTX-D- /2 - Min  VT                                                                                                                                                                                                                 | output voltage for small voltage swing | VTX-CM_S         | 135  | 280  | mV   | VTX-CM = DC  (avg) of   VTX-D+ + VTX-D- /2                                            |

| output voltage ratio for -6dB de-emphasis         VTX-DE-6.0-Ratio         -5.0         -7.0         dB         2, 4, 5           AC peak-to-peak common mode output voltage for large swing         VTX-CM-ACp-p L         —         90         mV         VTX-CM-AC = Max   VTX-D- /2 - Min   VTX-D+ + VTX-D- /2 - Min   VTX-D+ + VTX-D- /2   Measured as note 2. See also note 6           AC peak-to-peak common mode output voltage for regular swing         VTX-CM-ACp-p R         —         80         mV         Max   VTX-D+ VTX-D- /2 - Min   VTX-D+ + VTX-D- /2 - Min   VTX-D+ + VTX-D- /2   Measured as note 2. See also note 6           AC peak-to-peak common mode output voltage for swill VTX-CM-ACp-p S swing         —         70         mV         Max   VTX-D+ VTX-D- /2 - Min   VTX-D+ + VTX-D- /2 - Min   VTX-D+ + VTX-D- /2   Measured as note 2. See also note 6           Maximum single-ended voltage in El condition, DC + AC         VTX-IDLE-SE         —         50         mV         7, 8         DEC + AC           Maximum single-ended voltage in El condition, DC only         VTX-IDLE-SE-DC         —         20         mV         7, 8, 9           DC only         Maximum peak-to-peak differential voltage in El condition, DC only         VTX-SE         —75         750         mV         2, 10           Minimum TX eye width         TTX-Eye-MIN         0.7         —         UI         2, 11, 12           Maximum TX deterministic jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | output voltage ratio for               | VTX-DE-3.5-Ratio | -3.0 | -4.0 | dB   | 2, 4, 5                                                                               |

| AC peak-to-peak common mode output voltage for large VTX-CM-ACp-p L — 90 mV    AC peak-to-peak common mode output voltage for large VTX-CM-ACp-p R — 80 mV    AC peak-to-peak common mode output voltage for regular swing    AC peak-to-peak common mode output voltage for regular swing    AC peak-to-peak common mode output voltage for small VTX-CM-ACp-p R — 70 mV    AC peak-to-peak common mode output voltage for small VTX-CM-ACp-p S — 70 mV    AC peak-to-peak common mode output voltage for small VTX-CM-ACp-p S — 70 mV    AC peak-to-peak common mode output voltage for small VTX-CM-ACp-p S — 70 mV    AC peak-to-peak common mode output voltage for small VTX-CM-ACp-p S — 70 mV    AC peak-to-peak common mode output voltage for small VTX-CM-ACp-p S — 70 mV    AX   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2 - Min   VTX-D+ + VTX-D- /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ VTX-D+ /2 - Min   VTX-D+ + VTX-D- /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2 - Min   VTX-D+ + VTX-D- /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2 - Min   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2 - Min   VTX-D+ /2 - Min   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2 - Min   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2 - Min   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2   Measured as note 2. See also note 6   VTX-CM-AC = Max   VTX-D+ /2   Min   VTX-D+ /2   Min | output voltage ratio for               | VTX-DE-6.0-Ratio | -5.0 | -7.0 | dB   | 2, 4, 5                                                                               |

| AC peak-to-peak common mode output voltage for regular swing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | mode output voltage for large          | VTX-CM-ACp-p L   | _    | 90   | mV   | Max  VTX-D+ + VTX-D- /2 - Min  VTX-D+ + VTX-D- /2 Measured as note 2. See also note 6 |

| AC peak-to-peak common mode output voltage for small VTX-CM-ACp-p S — 70 mV    Maximum single-ended voltage in El condition, DC + AC    Maximum single-ended voltage in El condition, DC + AC    Maximum single-ended voltage in El condition, VTX-IDLE-SE — 50 mV 7, 8    Maximum peak-to-peak differential voltage in El condition    Single-ended voltage in El condition    Single-ended voltage in El vTX-IDLE-DIFFp-p — 40 mV 8    Condition    Single-ended voltage    (w.r.t.VSS) on D+/D-    Minimum TX eye width    TTX-Eye-MIN     TTX-DJ-DD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mode output voltage for                | VTX-CM-ACp-p R   | _    | 80   | mV   | Max  VTX-D+ + VTX-D- /2 - Min  VTX-D+ + VTX-D- /2                                     |

| Maximum single-ended voltage in El condition, DC + AC  Maximum single-ended voltage in El condition, DC + AC  Maximum single-ended voltage in El condition, DC only  Maximum peak-to-peak differential voltage in El condition  Single-ended voltage (w.r.t.VSS) on D+/D-  Minimum TX eye width TTX-Eye-MIN 0.7 — UI 2, 11, 12  Maximum TX deterministic jitter TTX-DJ-DD — 0.2 UI 2, 11, 12, 13  Instantaneous pulse width TTX-PULSE 0.85 — UI 14  Differential TX output rise/fall TTX-RISE, time TTX-FALL 30 ps Given by 20%-80% voltage levels. Measured as note 2  Differential return loss RLTX-DIFF 8 — dB Measured over 0.1GHz to 2.4GHz. See also note 15  Common mode return loss RLTX-CM 6 — dB Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | mode output voltage for small          | I VTX-CM-ACp-p S | _    | 70   | mV   | VTX-CM-AC = Max  VTX-D+ + VTX-D- /2 - Min  VTX-D+ + VTX-D- /2                         |

| voltage in El condition, DC only  Maximum peak-to-peak differential voltage in El vTX-IDLE-DIFFp-p — 40 mV 8 condition  Single-ended voltage (w.r.t.VSS) on D+/D- VTX-SE —75 750 mV 2, 10  Minimum TX eye width TTX-Eye-MIN 0.7 — UI 2, 11, 12  Maximum TX deterministic jitter TTX-DJ-DD — 0.2 UI 2, 11, 12, 13  Instantaneous pulse width TTX-PULSE 0.85 — UI 14  Differential TX output rise/fall TTX-RISE, TM Given by 20%-80% voltage levels. Measured as note 2  Differential return loss RLTX-DIFF 8 — dB Measured over 0.1GHz to 2.4GHz.  Common mode return loss RLTX-CM 6 — dB Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | voltage in El condition,               | VTX-IDLE-SE      | _    | 50   | mV   |                                                                                       |

| differential voltage in EI vTX-IDLE-DIFFp-p — 40 mV 8 condition  Single-ended voltage (w.r.t.VSS) on D+/D- VTX-SE —75 750 mV 2, 10  Minimum TX eye width TTX-Eye-MIN 0.7 — UI 2, 11, 12  Maximum TX deterministic jitter TTX-DJ-DD — 0.2 UI 2, 11, 12, 13  Instantaneous pulse width TTX-PULSE 0.85 — UI 14  Differential TX output rise/fall TTX-RISE, time TTX-FALL 30 ps Given by 20%-80% voltage levels. Measured as note 2  Mismatch between rise and fall times TTX-RISE 8 — dB Measured over 0.1GHz to 2.4GHz. See also note 15  Common mode return loss RITX-CM 6 — dB Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | voltage in El condition,               | VTX-IDLE-SE-DC   | _    | 20   | mV   | 7, 8, 9                                                                               |

| (w.r.t.VSS) on D+/D-VTX-SE-75750mV2, 10Minimum TX eye widthTTX-Eye-MIN0.7—UI2, 11, 12Maximum TX deterministic<br>jitterTTX-DJ-DD—0.2UI2, 11, 12, 13Instantaneous pulse widthTTX-PULSE0.85—UI14Differential TX output rise/fall<br>timeTTX-RISE,<br>TTX-FALL3090psGiven by 20%-80% voltage levels.<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | differential voltage in El             | VTX-IDLE-DIFFp-p | _    | 40   | mV   | 8                                                                                     |

| Maximum TX deterministic jitter       TTX-DJ-DD       —       0.2       UI       2, 11, 12, 13         Instantaneous pulse width       TTX-PULSE       0.85       —       UI       14         Differential TX output rise/fall TTX-RISE, time       30       90       ps       Given by 20%-80% voltage levels. Measured as note 2         Mismatch between rise and fall times       TTX-RF-MISMATCH       —       20       ps         Differential return loss       RLTX-DIFF       8       —       dB       Measured over 0.1GHz to 2.4GHz. See also note 15         Common mode return loss       RLTX-CM       6       —       dB       Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -                                      | VTX-SE           | -75  | 750  | mV   | 2, 10                                                                                 |

| Instantaneous pulse width TTX-PULSE 0.85 — UI 14  Differential TX output rise/fall TTX-RISE, time TTX-FALL 30 90 ps Given by 20%-80% voltage levels. Measured as note 2  Mismatch between rise and fall times TTX-RF-MISMATCH — 20 ps  Differential return loss RLTX-DIFF 8 — dB Measured over 0.1GHz to 2.4GHz. See also note 15  Common mode return loss RLTX-CM 6 — dB Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ·                                      | TTX-Eye-MIN      | 0.7  | _    | UI   | 2, 11, 12                                                                             |

| Differential TX output rise/fall TTX-RISE, time TTX-FALL 30 90 ps Given by 20%-80% voltage levels. Measured as note 2  Mismatch between rise and fall times TTX-RF-MISMATCH — 20 ps  Differential return loss RLTX-DIFF 8 — dB Measured over 0.1GHz to 2.4GHz. See also note 15  Common mode return loss RLTX-CM 6 — dB Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                        | TTX-DJ-DD        | _    | 0.2  | UI   | 2, 11, 12, 13                                                                         |

| time TTX-FALL 30 90 ps Measured as note 2  Mismatch between rise and fall times TTX-RF-MISMATCH — 20 ps  Differential return loss RLTX-DIFF 8 — dB Measured over 0.1GHz to 2.4GHz. See also note 15  Common mode return loss RLTX-CM 6 — dB Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Instantaneous pulse width              | TTX-PULSE        | 0.85 | _    | UI   | 14                                                                                    |

| fall times  Differential return loss  RLTX-DIFF  8  Measured over 0.1GHz to 2.4GHz. See also note 15  Common mode return loss  RLTX-CM  6  Measured over 0.1GHz to 2.4GHz.  Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |                  | 30   | 90   | ps   |                                                                                       |

| Common mode return loss RLTX-DIFF 8 — dB See also note 15  Measured over 0.1GHz to 2.4GHz.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                        | TTX-RF-MISMATCH  |      | 20   | ps   |                                                                                       |