# **Precision Single and Dual Low Noise Operational Amplifiers**

### ISL28127, ISL28227

The ISL28127 and ISL28227 are very high precision amplifiers featuring very low noise, low offset voltage, low input bias current and low temperature drift making them the ideal choice for applications requiring both high DC accuracy and AC performance. The combination of precision, low noise, and small footprint provides the user with outstanding value and flexibility relative to similar competitive parts.

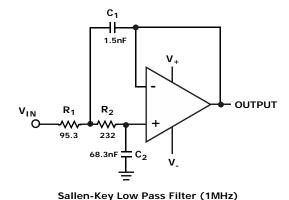

Applications for these amplifiers include precision active filters, medical and analytical instrumentation, precision power supply controls, and industrial controls.

The ISL28127 single and ISL28227 dual are available in an 8 Ld SOIC, TDFN and MSOP packages. All devices are offered in standard pin configurations and operate over the extended temperature range to -40°C to +125°C.

#### **Features**

| • Very Low Voltage Noise 2.5nV/Hz                  |

|----------------------------------------------------|

| • Low Input Offset 70µV, Max.                      |

| • Superb Offset Drift 0.5 $\mu$ V/°C, Max.         |

| • Input Bias Current 10nA, Max.                    |

| • Wide Supply Range 4.5V to 40V                    |

| • Gain-bandwidth Product . 10MHz Unity Gain Stable |

#### · No Phase Reversal

### Applications\* (see page 20)

- · Precision Instruments

- Medical Instrumentation

- · Industrial Controls

- Active Filter Blocks

- · Data Acquisition

- · Power Supply Control

### Related Literature\* (see page 20)

• AN1508: ISL281X7SOICEVAL1Z Evaluation Board User's Guide

# **Typical Application**

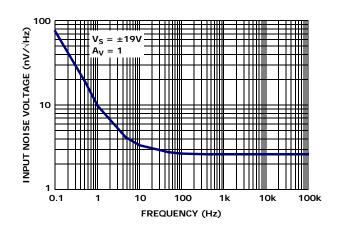

# **Input Noise Voltage Spectral Density**

### **Ordering Information**

| PART NUMBER<br>(Notes 3, 4)           | PART<br>MARKING  | V <sub>OS</sub> (MAX)<br>(μV) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|---------------------------------------|------------------|-------------------------------|----------------------|----------------|

| ISL28127FBZ (Note 1)                  | 28127 FBZ        | 70                            | 8 Ld SOIC            | M8.15E         |

| Coming Soon<br>ISL28127FRTBZ (Note 2) | 127Z             | TBD (B Grade)                 | 8 Ld TDFN            | L8.3x3A        |

| Coming Soon<br>ISL28127FRTZ (Note 2)  | -C 127Z          | 150 (C Grade)                 | 8 Ld TDFN            | L8.3x3A        |

| Coming Soon<br>ISL28127FUBZ (Note 2)  | 8127Z            | TBD (B Grade)                 | 8 Ld MSOP            | M8.118         |

| ISL28127FUZ (Note 2)                  | 8127Z -C         | 150 (C Grade)                 | 8 Ld MSOP            | M8.118         |

| ISL28227FBZ (Note 2)                  | 28227 FBZ        | 75                            | 8 Ld SOIC            | M8.15E         |

| Coming Soon<br>ISL28227FRTBZ (Note 2) | 227Z             | TBD (B Grade)                 | 8 Ld TDFN            | L8.3x3A        |

| Coming Soon<br>ISL28227FRTZ (Note 2)  | -C 227Z          | 150 (C Grade)                 | 8 Ld TDFN            | L8.3x3A        |

| Coming Soon<br>ISL28227FUBZ (Note 2)  | 8227Z            | TBD (B Grade)                 | 8 Ld MSOP            | M8.118         |

| Coming Soon<br>ISL28227FUZ (Note 2)   | 8227Z -C         | 150 (C Grade)                 | 8 Ld MSOP            | M8.118         |

| ISL28127SOICEVAL1Z                    | Evaluation Board | •                             | ,                    |                |

- 1. Add "-T7" or "-T13" suffix for tape and reel. Please refer to TB347 for details on reel specifications.

- 2. Add "-T13" suffix for tape and reel.Please refer to TB347 for details on reel specifications.

- 3. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 4. For Moisture Sensitivity Level (MSL), please see device information page for <u>ISL28127</u>. ISL28227. For more information on MSL please see techbrief <u>TB363</u>.

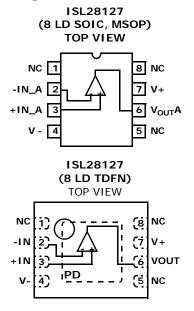

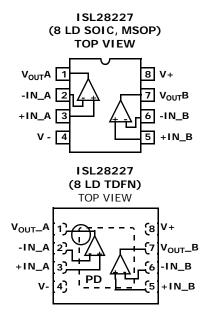

# **Pin Configurations**

# **Pin Descriptions**

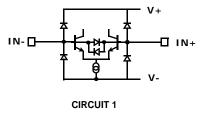

| ISL28127<br>(8 LD SOIC,<br>8 LD MSOP) | ISL28127<br>(8 LD TDFN) | ISL28227<br>(8 LD SOIC,<br>8 LD MSOP) | ISL28227<br>(8 LD TDFN) | PIN<br>NAME        | EQUIVALENT<br>CIRCUIT | DESCRIPTION                                                                    |

|---------------------------------------|-------------------------|---------------------------------------|-------------------------|--------------------|-----------------------|--------------------------------------------------------------------------------|

|                                       | 3                       |                                       |                         | + I N              | Circuit 1             | Amplifier non-inverting input                                                  |

| 3                                     |                         | 3                                     | 3                       | +IN_A              | Circuit 1             | Amplifier A non-inverting input                                                |

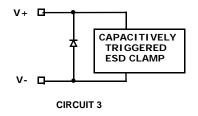

| 4                                     | 4                       | 4                                     | 4                       | V-                 | Circuit 3             | Negative power supply                                                          |

|                                       |                         | 5                                     | 5                       | + I N_B            | Circuit 1             | Amplifier B non-inverting input                                                |

|                                       | 2                       |                                       |                         | -IN                | Circuit 1             | Amplifier inverting input                                                      |

|                                       |                         | 6                                     | 6                       | -IN_B              | Circuit 1             | Amplifier B inverting input                                                    |

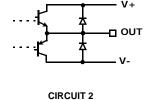

|                                       | 6                       |                                       |                         | V <sub>OUT</sub>   | Circuit 2             | Amplifier output                                                               |

|                                       |                         | 7                                     | 7                       | V <sub>OUT</sub> B | Circuit 2             | Amplifier B output                                                             |

| 7                                     | 7                       | 8                                     | 8                       | V +                | Circuit 3             | Positive power supply                                                          |

| 6                                     |                         | 1                                     | 1                       | V <sub>OUT</sub> A | Circuit 2             | Amplifier A output                                                             |

| 2                                     |                         | 2                                     | 2                       | -IN_A              | Circuit 1             | Amplifier A inverting input                                                    |

| 1, 5, 8                               | 1, 5, 8                 |                                       |                         | NC                 | -                     | Not Connected – This pin is not electrically connected internally.             |

|                                       | PD                      |                                       |                         | PD                 | -                     | Thermal Pad. Pad should be connecte to lowest potential source in the circuit. |

3

#### **Absolute Maximum Ratings**

| Maximum Supply Voltage                               |

|------------------------------------------------------|

| Maximum Differential Input Current20mA               |

| Maximum Differential Input Voltage                   |

| Min/Max Input Voltage V 0.5V to V+ + 0.5V            |

| Max/Min Input Current for                            |

| Input Voltage >V+ or <v±20ma< td=""></v±20ma<>       |

| Output Short-Circuit Duration                        |

| (1 Output at a Time) Indefinite                      |

| ESD Tolerance                                        |

| Human Body Model (Tested per JESD22-A114F)           |

| ISL281274.0kV                                        |

| ISL282276.0kV                                        |

| Machine Model (Tested per EIA/JESD22-A115-A) 500V    |

| Charged Device Model (Tested per JESD22-C101D) 1.5kV |

| Di-electrically Isolated PR40 process Latch-up free  |

#### **Thermal Information**

| Thermal Resistance (Typical)       | $\theta_{JA}$ (°C/W) | $\theta_{JC}$ (°C/W) |

|------------------------------------|----------------------|----------------------|

| 8 Ld SOIC (Note 5, 7)              |                      |                      |

| ISL28127                           | 120                  | 60                   |

| ISL28227                           | 110                  | 55                   |

| 8 Ld TDFN (Notes 5, 6)             |                      |                      |

| ISL28127                           | 48                   | 7                    |

| ISL28227                           | 47                   | 6                    |

| 8 Ld MSOP (Note 5, 7)              |                      |                      |

| ISL28127                           | 155                  | 50                   |

| ISL28227                           | 150                  | 45                   |

| Storage Temperature Range          | 65°                  | C to +150°C          |

| Pb-Free Reflow Profile             | S                    | ee link below        |

| http://www.intersil.com/pbfree/Pb- | FreeReflow.          | asp                  |

#### **Operating Conditions**

Ambient Operating Temperature Range . . . -40 $^{\circ}$ C to +125 $^{\circ}$ C Maximum Operating Junction Temperature . . . . . . +150 $^{\circ}$ C

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES

- 5.  $\theta_{JA}$  is measured with the component mounted on a high effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

- 6. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 7. For  $\theta_{\text{JC}},$  the "case temp" location is taken at the package top center.

IMPORTANT NOTE: All parameters having Min/Max specifications are guaranteed. Typical values are for information purposes only. Unless otherwise noted, all tests are at the specified temperature and are pulsed tests, therefore:  $T_J = T_C = T_A$

# Electrical Specifications $V_S \pm 15V$ , $V_{CM} = 0$ , $V_O = 0V$ , $R_L = Open$ , $T_A = +25^{\circ}C$ , unless otherwise noted. Boldface limits apply over the operating temperature range, -40°C to +125°C. Temperature data established by characterization.

| PARAMETER         | DESCRIPTION                                  | CONDITIONS                       | MIN<br>(Note 8) | TYP | MAX<br>(Note 8) | UNIT  |

|-------------------|----------------------------------------------|----------------------------------|-----------------|-----|-----------------|-------|

| V <sub>OS</sub>   | Offset Voltage; SOIC Package                 | ISL28127                         | -70             | 10  | 70              | μV    |

|                   |                                              |                                  | -120            | -   | 120             | μV    |

|                   |                                              | ISL28227                         | -75             | 10  | 75              | μV    |

|                   |                                              |                                  | -150            | -   | 150             | μV    |

|                   | Offset Voltage;                              | ISL28127                         | -150            | 10  | 150             | μV    |

|                   | MSOP, TDFN Grade C Package                   | ISL28227                         | -250            | -   | 250             | μV    |

| TCV <sub>OS</sub> | Offset Voltage Drift;                        | ISL28127                         | -0.5            | 0.1 | 0.5             | μV/°C |

|                   | SOIC Pacakge                                 | ISL28227                         | -0.75           | 0.1 | 0.75            | μV/°C |

|                   | Offset Voltage Drift;<br>MSOP, TDFN, Grade C | ISL28127<br>ISL28227             | -1              | 0.1 | 1               | μV/°C |

| I <sub>OS</sub>   | Input Offset Current                         |                                  | -10             | 1   | 10              | nA    |

|                   |                                              |                                  | -12             | -   | 12              | nA    |

| I <sub>B</sub>    | Input Bias Current                           |                                  | -10             | 1   | 10              | nA    |

|                   |                                              |                                  | -12             | -   | 12              | nA    |

| V <sub>CM</sub>   | Input Voltage Range                          | Guaranteed by CMRR               | -13             | -   | 13              | V     |

|                   |                                              |                                  | -12             | -   | 12              | V     |

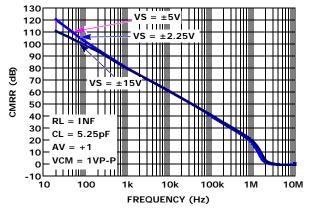

| CMRR              | Common-Mode Rejection Ratio                  | $V_{CM} = -13V \text{ to } +13V$ | 115             | 120 | -               | dB    |

|                   |                                              | $V_{CM} = -12V \text{ to } +12V$ | 115             | -   | -               | dB    |

Electrical Specifications  $V_S \pm 15V$ ,  $V_{CM} = 0$ ,  $V_O = 0V$ ,  $R_L = Open$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted. Boldface limits apply over the operating temperature range, -40°C to +125°C. Temperature data established by characterization. (Continued)

| PARAMETER                                         | DESCRIPTION                                                 | CONDITIONS                                                                                                                                                                     | MIN<br>(Note 8) | ТҮР     | MAX<br>(Note 8) | UNIT              |

|---------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------|-----------------|-------------------|

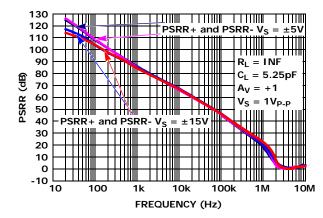

| PSRR                                              | Power Supply Rejection Ratio                                | $V_S = \pm 2.25V \text{ to } \pm 20V$                                                                                                                                          | 115             | 125     | -               | dB                |

|                                                   | ISL28127                                                    | $V_S = \pm 3V \text{ to } \pm 20V$                                                                                                                                             | 115             | -       | -               | dB                |

|                                                   | Power Supply Rejection Ratio                                | $V_S = \pm 2.25V \text{ to } \pm 20V$                                                                                                                                          | 110             | 117     | -               | dB                |

|                                                   | ISL28227                                                    | $V_S = \pm 3V \text{ to } \pm 20V$                                                                                                                                             | 110             | -       | -               | dB                |

| A <sub>VOL</sub>                                  | Open-Loop Gain                                              | $V_O = -13V$ to $+13V$<br>$R_L = 10k\Omega$ to ground                                                                                                                          | 1000            | 1500    | -               | V/mV              |

| V <sub>OH</sub>                                   | Output Voltage High                                         | $R_L = 10k\Omega$ to ground                                                                                                                                                    | 13.5            | 13.65   | -               | V                 |

|                                                   |                                                             |                                                                                                                                                                                | 13.2            | -       | -               | V                 |

|                                                   |                                                             | $R_L = 2k\Omega$ to ground                                                                                                                                                     | 13.4            | 13.5    | -               | V                 |

|                                                   |                                                             |                                                                                                                                                                                | 13.1            | -       | -               | V                 |

| V <sub>OL</sub>                                   | Output Voltage Low                                          | $R_L = 10k\Omega$ to ground                                                                                                                                                    | -               | -13.65  | -13.5           | V                 |

|                                                   |                                                             |                                                                                                                                                                                | -               | -       | -13.2           | V                 |

|                                                   |                                                             | $R_L = 2k\Omega$ to ground                                                                                                                                                     | -               | -13.5   | -13.4           | V                 |

|                                                   |                                                             |                                                                                                                                                                                | -               | -       | -13.1           | V                 |

| I <sub>S</sub>                                    | Supply Current/Amplifier                                    |                                                                                                                                                                                | -               | 2.2     | 2.8             | mA                |

| _                                                 |                                                             |                                                                                                                                                                                | -               | -       | 3.7             | mA                |

| I <sub>SC</sub>                                   | Short-Circuit                                               | $R_L = 0\Omega$ to ground                                                                                                                                                      | -               | ±45     | -               | mA                |

| V <sub>SUPPLY</sub>                               | Supply Voltage Range                                        | Guaranteed by PSRR                                                                                                                                                             | ±2.25           | -       | ±20             | V                 |

| C SPECIFICA                                       | ATIONS                                                      |                                                                                                                                                                                |                 |         |                 |                   |

| GBW                                               | Gain Bandwidth Product                                      |                                                                                                                                                                                |                 | 10      |                 | MHz               |

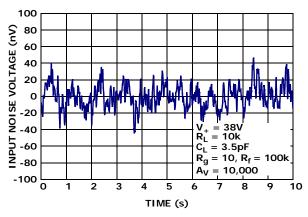

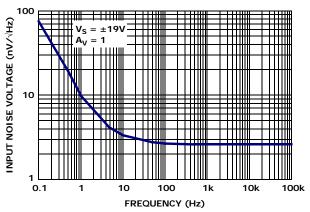

| e <sub>np-p</sub>                                 | Voltage Noise                                               | 0.1Hz to 10Hz                                                                                                                                                                  |                 | 85      |                 | nV <sub>P-P</sub> |

| e <sub>n</sub>                                    | Voltage Noise Density                                       | f = 10Hz                                                                                                                                                                       |                 | 3       |                 | nV <b>/</b> √Hz   |

| e <sub>n</sub>                                    | Voltage Noise Density                                       | f = 100Hz                                                                                                                                                                      |                 | 2.8     |                 | nV∕√Hz            |

| e <sub>n</sub>                                    | Voltage Noise Density                                       | f = 1kHz                                                                                                                                                                       |                 | 2.5     |                 | nV∕√Hz            |

| e <sub>n</sub>                                    | Voltage Noise Density                                       | f = 10kHz                                                                                                                                                                      |                 | 2.5     |                 | nV∕√Hz            |

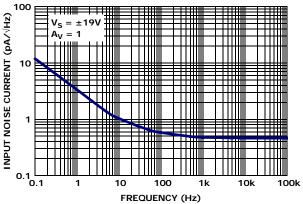

| in                                                | Current Noise Density                                       | f = 10kHz                                                                                                                                                                      |                 | 0.4     |                 | pA/√Hz            |

| THD + N                                           | Total Harmonic Distortion +<br>Noise                        | 1kHz, G = 1, $V_O = 3.5V_{RMS}$ , $R_L = 2k\Omega$                                                                                                                             |                 | 0.00022 |                 | %                 |

| RANSIENT F                                        | RESPONSE                                                    | 1                                                                                                                                                                              | I               |         |                 |                   |

| SR                                                | Slew Rate                                                   | $A_V = 10, R_L = 2k\Omega, V_O = 4V_{P-P}$                                                                                                                                     |                 | ±3.6    |                 | V/µs              |

| t <sub>r</sub> , t <sub>f</sub> , Small<br>Signal | Rise Time<br>10% to 90% of V <sub>OUT</sub>                 | $\begin{aligned} A_V &= \text{-1, V}_{OUT} = \text{100mV}_{P-P}, \\ R_f &= R_g = 2k\Omega, R_L = 2k\Omega \text{ to V}_{CM} \end{aligned}$                                     |                 | 36      |                 | ns                |

|                                                   | Fall Time<br>90% to 10% of V <sub>OUT</sub>                 | $\begin{aligned} &A_{V} = \text{-1, V}_{OUT} = 100\text{mV}_{P\text{-}P\text{,}} \\ &R_{f} = R_{g} = 2\text{k}\Omega, R_{L} = 2\text{k}\Omega \text{ to V}_{CM} \end{aligned}$ |                 | 38      |                 | ns                |

| t <sub>s</sub>                                    | Settling Time to 0.1%<br>10V Step; 10% to V <sub>OUT</sub>  | $A_V = -1 V_{OUT} = 10 V_{P-P}$ $R_g = R_f = 10 k, R_L = 2k\Omega \text{ to } V_{CM}$                                                                                          |                 | 3.4     |                 | μs                |

|                                                   | Settling Time to 0.01%<br>10V Step; 10% to V <sub>OUT</sub> | $\begin{aligned} A_V &= \text{-1, } V_{OUT} = \text{10V}_{P\text{-}P\text{-}} \\ R_L &= 2k\Omega \text{ to } V_{CM} \end{aligned}$                                             |                 | 3.8     |                 | μs                |

| t <sub>OL</sub>                                   | Output Overload Recovery Time                               | $A_V = 100, V_{IN} = 0.2V$<br>$R_L = 2k\Omega \text{ to } V_{CM}$                                                                                                              |                 | 1.7     |                 | μs                |

Electrical Specifications  $V_S \pm 5V$ ,  $V_{CM} = 0$ ,  $V_O = 0V$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted. Boldface limits apply over the operating temperature range, -40°C to +125°C. Temperature data established by characterization.

| PARAMETER                                         | DESCRIPTION                                 | CONDITIONS                                                                                                                                                                  | MIN<br>(Note 8) | TYP    | MAX<br>(Note 8) | UNIT  |

|---------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-----------------|-------|

| V <sub>OS</sub>                                   | Offset Voltage                              |                                                                                                                                                                             | -70             | 10     | 70              | μV    |

|                                                   |                                             |                                                                                                                                                                             | -120            | -      | 120             | μV    |

| V <sub>OS</sub> /T                                | Offset Voltage Drift                        |                                                                                                                                                                             | -0.5            | 0.1    | 0.5             | μV/°C |

| I <sub>OS</sub>                                   | Input Offset Current                        |                                                                                                                                                                             | -10             | 1      | 10              | nA    |

|                                                   |                                             |                                                                                                                                                                             | -12             | -      | 12              | nA    |

| I <sub>B</sub>                                    | Input Bias Current                          |                                                                                                                                                                             | 10              | 1      | 10              | nA    |

|                                                   |                                             |                                                                                                                                                                             | -12             | -      | 12              | nA    |

| $V_{CM}$                                          | Common Mode Input Voltage                   | Guaranteed by CMRR                                                                                                                                                          | -3              | -      | 3               | V     |

|                                                   | Range                                       |                                                                                                                                                                             | -2              | -      | 2               | V     |

| CMRR                                              | Common-Mode Rejection Ratio                 | $V_{CM} = -3V \text{ to } +3V$                                                                                                                                              | 115             | 120    | -               | dB    |

|                                                   |                                             | $V_{CM} = -2V \text{ to } +2V$                                                                                                                                              | 115             | -      | -               | dB    |

| PSRR                                              | Power Supply Rejection Ratio                | $V_S = \pm 2.25V \text{ to } \pm 5V$                                                                                                                                        | 115             | 125    | -               | dB    |

|                                                   |                                             | $V_S = \pm 3V$ to $\pm 5V$                                                                                                                                                  | 115             | -      | -               | dB    |

| A <sub>VOL</sub>                                  | Open-Loop Gain                              | $V_O = -3V \text{ to } +3V$<br>$R_L = 10k\Omega \text{ to ground}$                                                                                                          | 1000            | 1500   | -               | V/mV  |

| V <sub>OH</sub>                                   | Output Voltage High                         | $R_L = 10k\Omega$ to ground                                                                                                                                                 | 3.5             | 3.65   | -               | V     |

|                                                   |                                             |                                                                                                                                                                             | 3.2             | -      | -               | V     |

|                                                   |                                             | $R_L = 2k\Omega$ to ground                                                                                                                                                  | 3.4             | 3.5    | -               |       |

|                                                   |                                             |                                                                                                                                                                             | 3.1             | -      | -               | V     |

| V <sub>OL</sub>                                   | Output Voltage Low                          | $R_L = 10k\Omega$ to ground                                                                                                                                                 | -               | -3.65  | -3.5            | V     |

|                                                   |                                             |                                                                                                                                                                             | -               | -      | -3.2            | V     |

|                                                   |                                             | $R_L = 2k\Omega$ to ground                                                                                                                                                  | -               | -3.5   | -3.4            |       |

|                                                   |                                             |                                                                                                                                                                             | -               | -      | -3.1            | V     |

| I <sub>S</sub>                                    | Supply Current/Amplifier                    |                                                                                                                                                                             | -               | 2.2    | 2.8             | mA    |

|                                                   |                                             |                                                                                                                                                                             | -               | -      | 3.7             | mA    |

| I <sub>SC</sub>                                   | Short-Circuit                               |                                                                                                                                                                             | -               | ± 45   | -               | mA    |

| AC SPECIFIC                                       | ATIONS                                      |                                                                                                                                                                             |                 |        |                 |       |

| GBW                                               | Gain Bandwidth Product                      |                                                                                                                                                                             |                 | 10     |                 | MHz   |

| THD + N                                           | Total Harmonic Distortion +<br>Noise        | $1kHz$ , $G = 1$ , $Vo = 2.5V_{RMS}$ , $R_L = 2k\Omega$                                                                                                                     |                 | 0.0034 |                 | %     |

| TRANSIENT F                                       | RESPONSE                                    |                                                                                                                                                                             |                 |        |                 |       |

| SR                                                | Slew Rate                                   | $A_V = 10$ , $R_L = 2k\Omega$                                                                                                                                               |                 | ±3.6   |                 | V/µs  |

| t <sub>r</sub> , t <sub>f</sub> , Small<br>Signal | Rise Time<br>10% to 90% of V <sub>OUT</sub> | $\begin{aligned} A_V &= \text{-1, } V_{OUT} = 100 \text{mV}_{P\text{-}P\text{-}} \\ R_f &= R_g = 2 \text{k}\Omega, R_L = 2 \text{k}\Omega \text{ to } V_{CM} \end{aligned}$ |                 | 36     |                 | ns    |

|                                                   | Fall Time<br>90% to 10% of V <sub>OUT</sub> | $\begin{aligned} A_V &= \text{-1, } V_{OUT} = 100 \text{mV}_{P\text{-}P\text{-}} \\ R_f &= R_g = 2 \text{k}\Omega, R_L = 2 \text{k}\Omega \text{ to } V_{CM} \end{aligned}$ |                 | 38     |                 | ns    |

| $t_s$                                             | Settling Time to 0.1%                       | $\begin{aligned} A_V &= \text{-1, } V_{OUT} = 4V_{P\text{-P}}, \\ R_f &= R_g = 2k\Omega, R_L = 2k\Omega \text{ to } V_{CM} \end{aligned}$                                   |                 | 1.6    |                 | μs    |

|                                                   | Settling Time to 0.01%                      | $\begin{aligned} A_V &= \text{-1, } V_{OUT} = 4V_{P\text{-P}}, \\ R_f &= R_g = 2k\Omega, R_L = 2k\Omega \text{ to } V_{CM} \end{aligned}$                                   |                 | 4.2    |                 | μs    |

#### NOTE:

<sup>8.</sup> Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested.

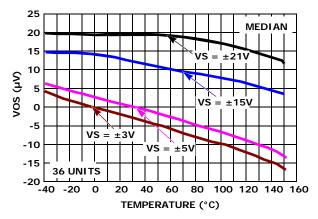

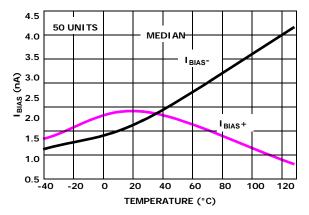

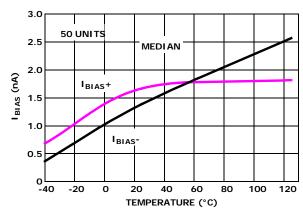

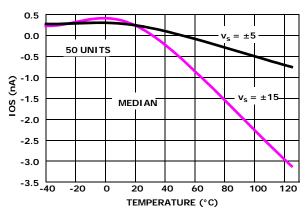

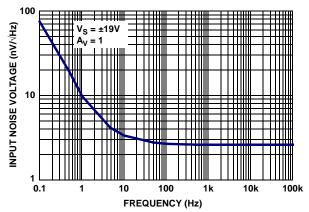

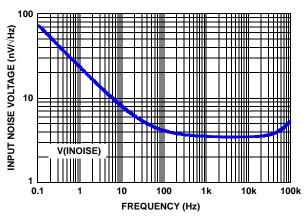

Typical Performance Curves  $V_S = \pm 15 V$ ,  $V_{CM} = 0 V$ ,  $R_L = Open$ , unless otherwise specified.

FIGURE 1. INPUT NOISE VOLTAGE 0.1Hz to 10Hz

FIGURE 3. INPUT NOISE CURRENT SPECTRAL DENSITY

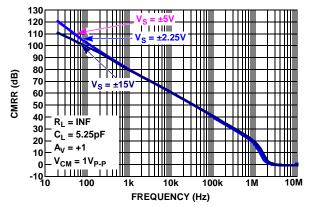

FIGURE 5. CMRR vs FREQUENCY,  $V_S = \pm 2.25, \pm 5V$ , ±15V

FIGURE 2. INPUT NOISE VOLTAGE SPECTRAL **DENSITY**

FIGURE 4. PSRR vs FREQUENCY,  $V_S = \pm 5V$ ,  $\pm 15V$

FIGURE 6. VOS VS TEMPERATURE VS VSUPPLY

# **Typical Performance Curves** $V_S = \pm 15V$ , $V_{CM} = 0V$ , $R_L = Open$ , unless otherwise specified. **(Continued)**

FIGURE 7.  $I_{IB}$  vs TEMPERATURE,  $V_S = \pm 15V$

FIGURE 8.  $I_{IB}$  vs TEMPERATURE,  $V_S = \pm 5V$

FIGURE 9. I<sub>OS</sub> vs TEMPERATURE vs SUPPLY

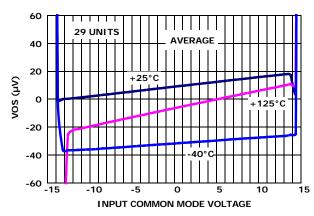

FIGURE 10. INPUT OFFSET VOLTAGE vs INPUT COMMON MODE VOLTAGE,  $V_S = \pm 15V$

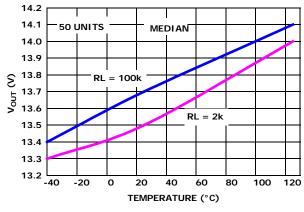

FIGURE 11.  $V_{OH}$  vs TEMPERATURE,  $V_S = \pm 15V$

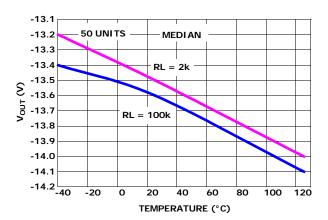

FIGURE 12.  $V_{OL}$  vs TEMPERATURE,  $V_S = \pm 15V$

# Typical Performance Curves $V_S = \pm 15 V$ , $V_{CM} = 0 V$ , $R_L = Open$ , unless otherwise

specified. (Continued)

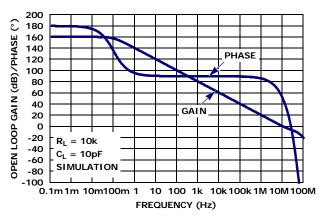

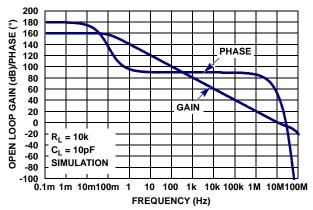

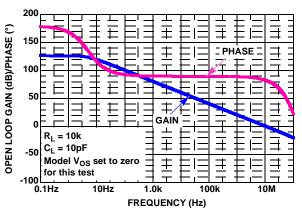

FIGURE 13. OPEN-LOOP GAIN, PHASE vs FREQUENCY,  $R_L = 10k\Omega$ ,  $C_L = 10pF$

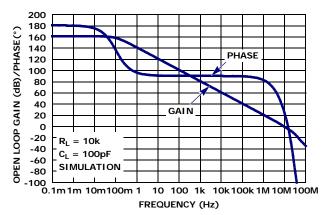

FIGURE 14. OPEN-LOOP GAIN, PHASE vs FREQUENCY,  $R_L = 10k\Omega$ ,  $C_L = 100pF$

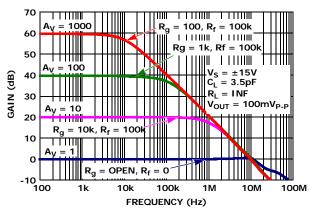

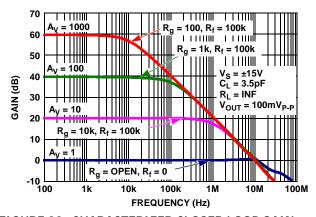

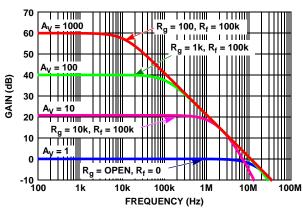

FIGURE 15. FREQUENCY RESPONSE vs CLOSED LOOP

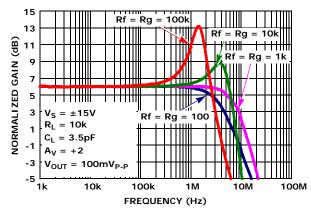

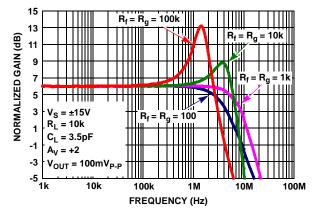

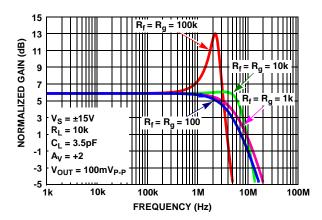

FIGURE 16. FREQUENCY RESPONSE vs FEEDBACK RESISTANCE R<sub>f</sub>/R<sub>q</sub>

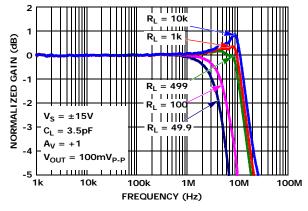

FIGURE 17. GAIN vs FREQUENCY vs R<sub>I</sub>

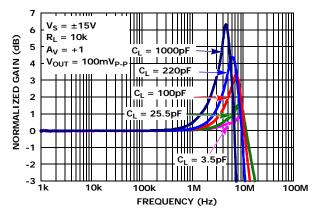

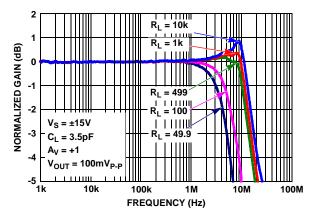

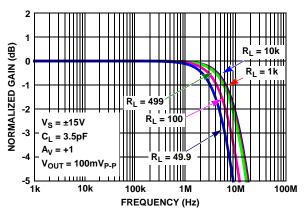

FIGURE 18. GAIN vs FREQUENCY vs C<sub>1</sub>

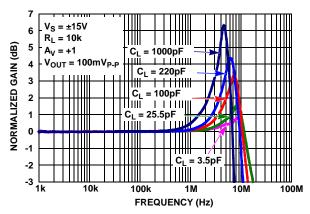

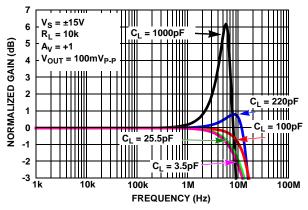

# **Typical Performance Curves** $V_S = \pm 15V$ , $V_{CM} = 0V$ , $R_L = Open$ , unless otherwise

specified. (Continued)

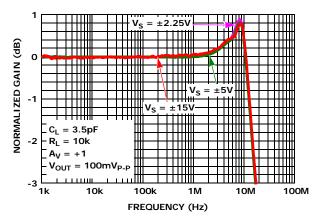

FIGURE 19. GAIN vs FREQUENCY vs SUPPLY **VOLTAGE**

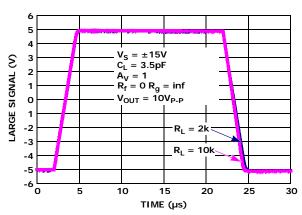

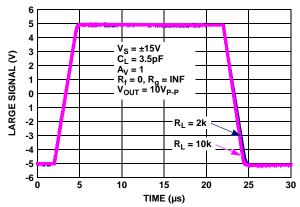

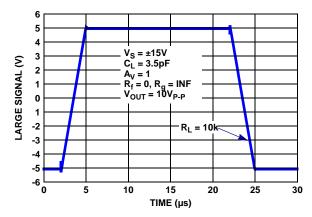

FIGURE 20. LARGE SIGNAL 10V STEP RESPONSE,  $V_S = \pm 15V$

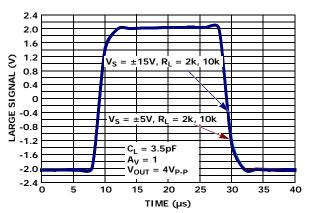

FIGURE 21. LARGE SIGNAL TRANSIENT RESPONSE vs  $R_L V_S = \pm 5V, \pm 15V$

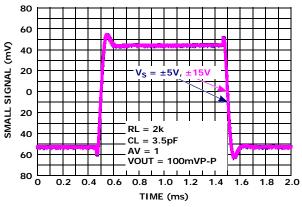

FIGURE 22. SMALL SIGNAL TRANSIENT RESPONSE,  $V_S = \pm 5V$ ,  $\pm 15V$

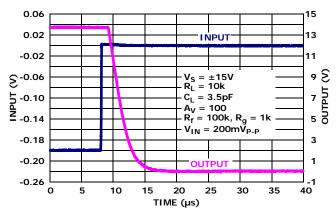

FIGURE 23. POSITIVE OUTPUT OVERLOAD RESPONSE TIME,  $V_S = \pm 15V$

FIGURE 24. NEGATIVE OUTPUT OVERLOAD RESPONSE TIME,  $V_S = \pm 15V$

# **Typical Performance Curves** $V_S = \pm 15V$ , $V_{CM} = 0V$ , $R_L = Open$ , unless otherwise specified. **(Continued)**

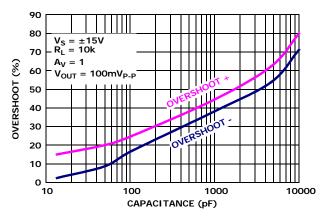

FIGURE 25. % OVERSHOOT vs LOAD CAPACITANCE,  $V_S = \pm 15V$

### **Applications Information**

#### **Functional Description**

The ISL28127 and ISL28227 are single and dual, low noise 10MHz BW precision op amps. Both devices are fabricated in a new precision 40V complementary bipolar DI process. A super-beta NPN input stage with input bias current cancellation provides low input bias current (1nA typical), low input offset voltage (10µV typ), low input noise voltage (3nV/ $\sqrt{\text{Hz}}$ ), and low 1/f noise corner frequency (5Hz). These amplifiers also feature high open loop gain (1500V/mV) for excellent CMRR (120dB) and THD+N performance (0.0002% @ 3.5V<sub>RMS</sub>, 1kHz into 2k $\Omega$ ). A complimentary bipolar output stage enables high capacitive load drive without external compensation.

#### **Operating Voltage Range**

The devices are designed to operate over the 4.5V  $(\pm 2.25\text{V})$  to 40V  $(\pm 20\text{V})$  range and are fully characterized at 10V  $(\pm 5\text{V})$  and 30V  $(\pm 15\text{V})$ . Parameter variation with operating voltage is shown in the "Typical Performance Curves" beginning on page 7.

#### **Input ESD Diode Protection**

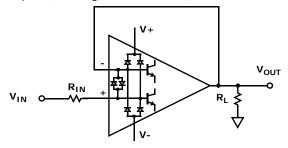

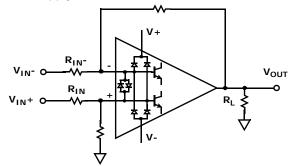

The input terminals (IN+ and IN-) have internal ESD protection diodes to the positive and negative supply rails, and an additional anti-parallel diode pair across the inputs (see Figures 26 and 27).

FIGURE 26. INPUT ESD DIODE CURRENT LIMITING-UNITY GAIN

For unity gain applications (see Figure 26) where the output is connected directly to the non-inverting input a current limiting resistor ( $R_{\rm IN}$ ) will be needed under the following conditions to protect the anti-parallel differential input protection diodes.

- The amplifier input is supplied from a low impedance source.

- The input voltage rate-of-rise (dV/dt) exceeds the maximum slew rate of the amplifier (±3.6V/µs).

If the output lags far enough behind the input, the anti-parallel input diodes can conduct. For example, if an input pulse ramps from 0V to  $\pm 10$ V in 1µs, then the output of the ISL28x27 will reach only  $\pm 3.6$ V (slew rate = 3.6V/µs) while the input is at 10V, The input differential voltage of 6.4V will force input ESD diodes to conduct, dumping the input current directly into the output stage and the load. The resulting current flow can cause permanent damage to the ESD diodes. The ESD diodes are rated to 20mA, and in the previous example, setting R\_{IN} to 1k resistor (see Figure 26) would limit the current to < 6.4mA, and provide additional protection up to  $\pm 20$ V at the input.

In applications where one or both amplifier input terminals are at risk of exposure to high voltage, current limiting resistors may be needed at each input terminal (see Figure 27  $R_{\mbox{\footnotesize{IN}}}^+$ ,  $R_{\mbox{\footnotesize{IN}}}^-$ ) to limit current through the power supply ESD diodes to 20mA.

FIGURE 27. INPUT ESD DIODE CURRENT LIMITING - DIFFERENTIAL INPUT

#### **Output Current Limiting**

The output current is internally limited to approximately  $\pm 45$ mA at +25°C and can withstand an short circuit to either rail as long as the power dissipation limits are not exceeded. This applies to only 1 amplifier at a time for the dual op amp. Continuous operation under these conditions may degrade long term reliability.

#### **Output Phase Reversal**

Output phase reversal is a change of polarity in the amplifier transfer function when the input voltage exceeds the supply voltage. The ISL28127 and ISL28227 are immune to output phase reversal, even when the input voltage is 1V beyond the supplies.

#### **Power Dissipation**

It is possible to exceed the  $+150^{\circ}\text{C}$  maximum junction temperatures under certain load and power supply conditions. It is therefore important to calculate the maximum junction temperature ( $T_{JMAX}$ ) for all applications to determine if power supply voltages, load conditions, or package type need to be modified to remain in the safe operating area. These parameters are related using Equation 1:

$$T_{JMAX} = T_{MAX} + \theta_{JA} x PD_{MAXTOTAL}$$

(EQ. 1)

#### where:

- P<sub>DMAXTOTAL</sub> is the sum of the maximum power dissipation of each amplifier in the package (PD<sub>MAX</sub>)

- PD<sub>MAX</sub> for each amplifier can be calculated using Equation 2:

$$PD_{MAX} = V_{S} \times I_{qMAX} + (V_{S} - V_{OUTMAX}) \times \frac{V_{OUTMAX}}{R_{L}}$$

(EQ.2)

#### where:

- T<sub>MAX</sub> = Maximum ambient temperature

- $\theta_{JA}$  = Thermal resistance of the package

- PD<sub>MAX</sub> = Maximum power dissipation of 1 amplifier

- V<sub>S</sub> = Total supply voltage

- I<sub>qMAX</sub> = Maximum quiescent supply current of 1 amplifier

- V<sub>OUTMAX</sub> = Maximum output voltage swing of the application

$R_I = Load resistance$

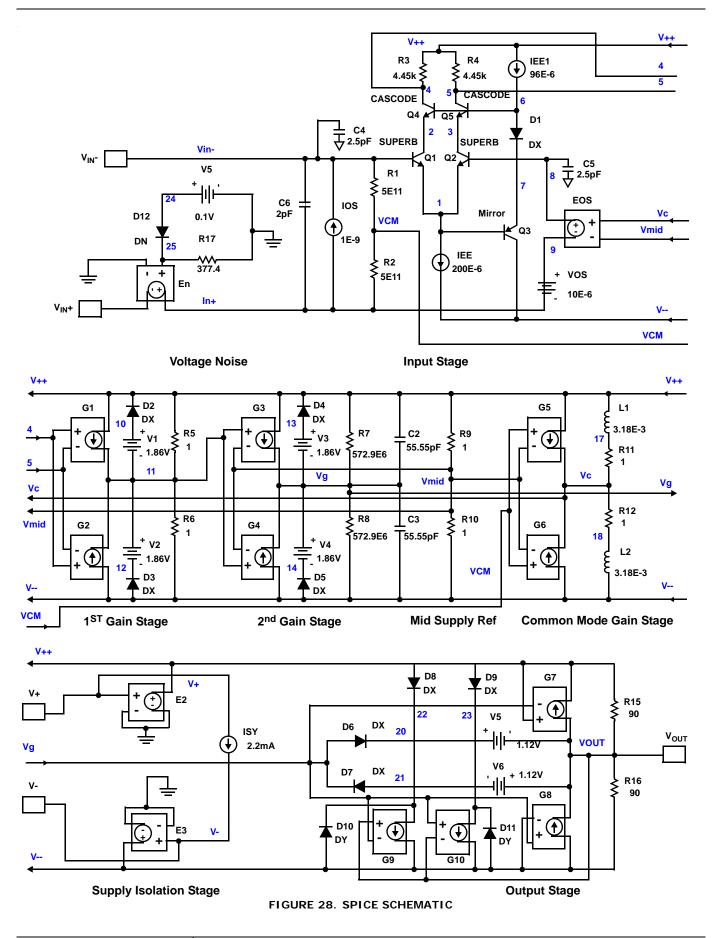

#### ISL28127 and ISL28227 SPICE Model

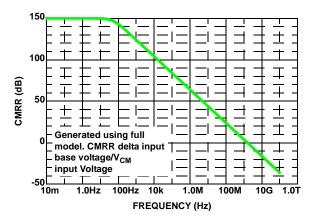

Figure 28 shows the SPICE model schematic and Figure 29 shows the net list for the ISL28127 and ISL28227 SPICE model. The model is a simplified version of the actual device and simulates important AC and DC parameters. AC parameters incorporated into the model are: 1/f and flatband noise, Slew Rate, CMRR, Gain and Phase. The DC parameters are VOS, IOS, total supply current and output voltage swing. The model does not model input bias current. The model uses typical parameters given in the "Electrical Specifications" Table beginning on page 4. The AVOL is adjusted for 128dB with the dominate pole at 5Hz. The CMRR is set higher than the "Electrical Specifications" Table to better match design simulations (150dB, f = 50Hz). The input stage models the actual device to present an accurate AC representation. The model is configured for ambient temperature of +25°C.

Figures 30 through 45 show the characterization vs simulation results for the Noise Voltage, Closed Loop Gain vs Frequency, Closed Loop Gain vs Rf/Rg, Closed Loop Gain vs RL, Closed Loop Gain vs CL, Large Signal 10V Step Response, Open Loop Gain Phase and Simulated CMRR vs Frequency.

#### LICENSE STATEMENT

The information in this SPICE model is protected under the United States copyright laws. Intersil Corporation hereby grants users of this macro-model hereto referred to as "Licensee", a nonexclusive, nontransferable licence to use this model as long as the Licensee abides by the terms of this agreement. Before using this macro-model, the Licensee should read this license. If the Licensee does not accept these terms, permission to use the model is not granted.

The Licensee may not sell, loan, rent, or license the macro-model, in whole, in part, or in modified form, to anyone outside the Licensee's company. The Licensee may modify the macro-model to suit his/her specific applications, and the Licensee may make copies of this macro-model for use within their company only.

This macro-model is provided "AS IS, WHERE IS, AND WITH NO WARRANTY OF ANY KIND EITHER EXPRESSED OR IMPLIED, INCLUDING BUY NOT LIMITED TO ANY IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE."

In no event will Intersil be liable for special, collateral, incidental, or consequential damages in connection with or arising out of the use of this macro-model. Intersil reserves the right to make changes to the product and the macro-model without prior notice.

```

* source ISL28127_SPICEmodel

R_R7

VG V++ 572.958E6 TC=0,0

* Revision C, August 8th 2009 LaFontaine

V-- VG 572.958E6 TC=0,0

R R8

C_C2

VG V++ 55.55e-12 TC=0,0

* Model for Noise, supply currents, 150dB f=50Hz

V-- VG 55.55e-12 TC=0,0

CMRR, *128dB f=5Hz AOL

C_C3

*Copyright 2009 by Intersil Corporation

D_D4

13 V++ DX

*Refer to data sheet "LICENSE STATEMENT" Use of

D_D5

V-- 14 DX

V V3

13 VG 1.86

*this model indicates your acceptance with the

VG 14 1.86

*terms and provisions in the License Statement.

V_V4

* Connections: +input

-input

*Mid supply Ref

+Vsupply

VMID V++ 1 TC=0,0

R_R9

-Vsupply

R_R10

V-- VMID 1 TC=0,0

output

V+ V- DC 2.2E-3

I_ISY

V++ 0 V+ 0 1

E E2

.subckt ISL28127subckt Vin+ Vin-V+ V- VOUT

E_E3

V-- 0 V- 0 1

* source ISL28127_SPICEMODEL_0_0

*Common Mode Gain Stage with Zero

*Voltage Noise

V++ VC VCM VMID 31.6228e-9

G G5

IN+ VIN+ 25 0 1

G_G6

V-- VC VCM VMID 31.6228e-9

R_R17

25 0 377.4 TC=0,0

R_R11

VC 17 1 TC=0,0

D_D12

24 25 DN

R_R12

18 VC 1 TC=0,0

V_V7

24 0 0.1

L_L1

17 V++ 3.183e-3

18 V-- 3.183e-3

L_L2

*Input Stage

I_IOS

IN+ VIN- DC 1e-9

*Output Stage with Correction Current Sources

IN+ VIN- 2E-12

C C6

VOUT V++ V++ VG 1.11e-2

G G7

R R1

VCM VIN- 5ell TC=0,0

V-- VOUT VG V-- 1.11e-2

G G8

IN+ VCM 5ell TC=0,0

R_R2

G_G9

22 V-- VOUT VG 1.11e-2

2 VIN- 1 SuperB

Q_Q1

23 V-- VG VOUT 1.11e-2

G_G10

3 8 1 SuperB

Q_Q2

VG 20 DX

D_D6

V-- 1 7 Mirror

Q_Q3

D D7

21 VG DX

0_04

4 6 2 Cascode

D_D8

V++ 22 DX

0 05

5 6 3 Cascode

D D9

V++ 23 DX

4 V++ 4.45e3 TC=0,0

R R3

V-- 22 DY

D D10

5 V++ 4.45e3 TC=0,0

R R4

V-- 23 DY

D_D11

C_C4 VIN- 0 2.5e-12

V_V5

20 VOUT 1.12

C_C5 8 0 2.5e-12

VOUT 21 1.12

V_V6

D D1

6 7 DX

R R15

VOUT V++ 9E1 TC=0,0

1 V-- DC 200e-6

I_IEE

R R16

V-- VOUT 9E1 TC=0,0

V++ 6 DC 96e-6

I_IEE1

V_VOS

9 IN+ 10e-6

.model SuperB npn

8 9 VC VMID 1

E_EOS

+ is=184E-15 bf=30e3 va=15 ik=70E-3 rb=50

+ re=0.065 rc=35 cje=1.5E-12 cjc=2E-12

*1st Gain Stage

+ kf=0 af=0

V++ 11 4 5 0.0487707

G G1

.model Cascode npn

G_G2

V-- 11 4 5 0.0487707

+ is=502E-18 bf=150 va=300 ik=17E-3 rb=140

R R5

11 V++ 1 TC=0,0

+ re=0.011 rc=900 cje=0.2E-12 cjc=0.16E-12f

V-- 11 1 TC=0,0

R_R6

+ kf=0 af=0

D D2

10 V++ DX

.model Mirror pnp

D D3

V-- 12 DX

+ is=4E-15 bf=150 va=50 ik=138E-3 rb=185

V_V1

10 11 1.86

+ re=0.101 rc=180 cje=1.34E-12 cjc=0.44E-12

V_V2

11 12 1.86

+ kf=0 af=0

.model DN D(KF=6.69e-9 AF=1)

*2nd Gain Stage

.MODEL DX D(IS=1E-12 Rs=0.1)

V++ VG 11 VMID 4.60767E-3

G G3

.MODEL DY D(IS=1E-15 BV=50 Rs=1)

V-- VG 11 VMID 4.60767E-3

G_G4

.ends ISL28127subckt

```

FIGURE 29. SPICE NET LIST

FN6633.3 March 18, 2010

#### Characterization vs Simulation Results

FIGURE 30. CHARACTERIZED INPUT NOISE VOLTAGE

FIGURE 31. SIMULATED INPUT NOISE VOLTAGE

FIGURE 32. CHARACTERIZED CLOSED LOOP GAIN vs FREQUENCY

FIGURE 33. SIMULATED CLOSED LOOP GAIN vs FREQUENCY

FIGURE 34. CHARACTERIZED CLOSED LOOP GAIN vs  $R_{f}/R_{\alpha}$

FIGURE 35. SIMULATED CLOSED LOOP GAIN vs  $\rm R_f/R_g$

#### Characterization vs Simulation Results (Continued)

FIGURE 36. CHARACTERIZED CLOSED LOOP GAIN vs  $\ensuremath{R_L}$

FIGURE 37. SIMULATED CLOSED LOOP GAIN vs  $R_{\mathsf{L}}$

FIGURE 38. CHARACTERIZED CLOSED LOOP GAIN vs  $C_L$

FIGURE 39. SIMULATED CLOSED LOOP GAIN vs C<sub>L</sub>

FIGURE 40. CHARACTERIZED LARGE SIGNAL 10V STEP RESPONSE

FIGURE 41. SIMULATED LARGE SIGNAL 10V STEP RESPONSE

#### Characterization vs Simulation Results (Continued)

FIGURE 42. SIMULATED OPEN-LOOP GAIN, PHASE vs FREQUENCY

FIGURE 43. SIMULATED OPEN-LOOP GAIN, PHASE vs FREQUENCY

FIGURE 44. CHARACTERIZED CMRR vs FREQUENCY

FIGURE 45. SIMULATED CMRR vs FREQUENCY

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev.

| REVISION | DATE    | CHANGE                                                                                                                                                                                                                                                                                          |                                     |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| FN6633.3 | 3/11/10 | PODs M8.118 and L8.3x3A - Updated to new intersil format and moving dimensions from table onto drawing.                                                                                                                                                                                         | t by adding land pattern            |

|          | 3/3/10  | Page 2:<br>Under "Ordering Information"<br>ISL28227FBZ: Changed Vos max from 80μV to 75μV                                                                                                                                                                                                       |                                     |

|          |         | Page 4:<br>Changed:<br>1. ISL28227 SOIC Room Temp limit for Vos from 80μV (MA<br>75μV (MAX) and -75μV (MIN).<br>2. ISL28227 SOIC Full Temp limit for Vos from 160μV (MAX)<br>150μV (MAX) and -150μV (MIN)<br>3. ISL28227 SOIC limit for TCVos from 0.8μV (MAX) and -<br>(MAX) and -0.75μV (MIN) | X) and -160μV (MIN) to              |

|          | 3/2/10  | HBM for ISL28227 changed from "4kV" to "6kV" Tjc values for ISL28227 changed: For MSOP from "50" to "45" For SOIC from "60" to "55"                                                                                                                                                             |                                     |

|          | 2/25/10 | On the ordering info (page 2):                                                                                                                                                                                                                                                                  |                                     |

|          |         | Part Number Part Marking ISL28127FRTBZ ISL28127FRTZ -C 127Z instead of 127Z C                                                                                                                                                                                                                   | Vos (Max) (uV)<br>TBD instead of 70 |

|          |         | ISL28127FUBZ                                                                                                                                                                                                                                                                                    | TBD instead of 7                    |

|          |         | ISL28127FUZ 8127Z -C instead of 8127Z<br>Removed "Coming Soon) for ISL28127FUZ package                                                                                                                                                                                                          | 150 instead of 7                    |

|          |         | ISL28227FBZ Removed "Coming Soon) for ISL28227FBZ package                                                                                                                                                                                                                                       | 80 instead of 7                     |

|          |         | ISL28227FRTBZ<br>ISL28227FRTZ -C 227Z instead of 227Z C                                                                                                                                                                                                                                         | TBD instead of 7                    |

|          |         | ISL28227FUZ 8227Z -C instead of 8227Z                                                                                                                                                                                                                                                           | 150 instead of 7                    |

|          |         | Added the following row of data ISL28227FUBZ 8227Z                                                                                                                                                                                                                                              | TBD                                 |

|          |         | On the Electrical specifications on page 4 and page 6 the made. The change applies to the same spec found on page                                                                                                                                                                               |                                     |

|          |         | VOS Offset Voltage; SOIC Package, ISL28127: Added -70 temp and -120 MIN across full temp                                                                                                                                                                                                        | to MIN across room                  |

|          |         | VOS Offset Voltage; SOIC Package, ISL28227: Added -80 temp and -160 MIN across full temp                                                                                                                                                                                                        |                                     |

|          |         | VOS Offset Voltage; MSOP and TDFN Package Grade C, IS Added -150 to MIN across room temp and -250 MIN acrost TCVOS Offset Voltage Drift; SOIC Package, ISL28127: Ad                                                                                                                             | ss full temp                        |

|          |         | full temp TCVOS Offset Voltage Drift; SOIC Package, ISL28227: Ad full temp                                                                                                                                                                                                                      | ded -0.8 to MIN acros               |

|          |         | TCVOS Offset Voltage Drift; MSOP and TDFN Package Gra<br>ISL28127/ISL28227: Added -1 to MIN across full temp                                                                                                                                                                                    |                                     |

|          |         | IOS Input Offset Current: Added -10 to MIN across room across full temp                                                                                                                                                                                                                         | •                                   |

|          |         | IB Input Bias Current : Added -10 to MIN across room temp full temp                                                                                                                                                                                                                             | o and - 12 to MIN across            |

|          | 2/19/10 | Added differentiated part numbers for B-grade and C-grade Added ESD and latch-up information. Broke out Theta JA to and added Theta JC.                                                                                                                                                         |                                     |

# **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest Rev. (Continued)

| REVISION | DATE    | CHANGE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FN6633.2 | 1/29/10 | Added license statement for P-Spice Model.  Updated Spice Schematic by adding capacitors  C4, C5 and C6  Updated Spice Net List as follows: From: Revision B, July 23 2009  To: Revision C, August 8th 2009 LaFontaine From: source ISL28127_SPICEMODEL_7_9  To: source ISL28127_SPICEMODEL_0_0 Added after I_IOS: C_C6                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| FN6633.1 | 9/14/09 | "Functional Description" on page 11. Corrected low 1/f noise corner frequency from 3Hz to 5Hz to match "Input Noise Voltage Spectral Density" on page 1. Corrected high open loop gain from 1400V/mV to 1500V/mV to match "Open-Loop Gain" on page 5 spec table.  "Operating Voltage Range" on page 11. Removed following 2 sentences since there are no graphs illustrating common mode voltage sensitivity vs temperature or VOS as a function of supply voltage and temperature:  "The input common mode voltage sensitivity to temperature is shown in Figure 3 (±15V). Figure 20 shows VOS as a function of supply voltage and temperature with the common mode voltage at 0V for split supply operation."  Added Theta JC in Thermal Information for TDFN package |

|          | 7/21/09 | Updated Features to show only key features and updated applications section. Added Typical Application Circuit and performance graph, Updated Ordering Information to match Intrepid and added POD's L8.3x3A and M8.118, also added MSL level as part of new format. Added TDFN pinouts, updated pin descriptions to include TDFN pinouts, Added Theta Ja in Thermal information for TDFN and MSOP packages. Added Revision History and Products Text with device info links. Added SPICE Model with referencing text and Net List.                                                                                                                                                                                                                                     |

| FN6633.0 | 5/28/09 | Techdocs Issued File Number FN6633. Initial release of Datasheet with file number FN6633 making this a Rev 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### ISL28127, ISL28227

#### **Products**

Intersil Corporation is a leader in the design and manufacture of high-performance analog semiconductors. The Company's products address some of the industry's fastest growing markets, such as, flat panel displays, cell phones, handheld products, and notebooks. Intersil's product families address power management and analog signal processing functions. Go to <a href="https://www.intersil.com/products">www.intersil.com/products</a> for a complete list of Intersil product families.

\*For a complete listing of Applications, Related Documentation and Related Parts, please see the respective device information page on intersil.com: <a href="ISL28127">ISL28127</a>, ISL28227</a>

To report errors or suggestions for this datasheet, please go to www.intersil.com/askourstaff

FITs are available from our website at <a href="http://rel.intersil.com/reports/search.php">http://rel.intersil.com/reports/search.php</a>

For additional products, see www.intersil.com/product tree

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at <a href="https://www.intersil.com/design/quality">www.intersil.com/design/quality</a>

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

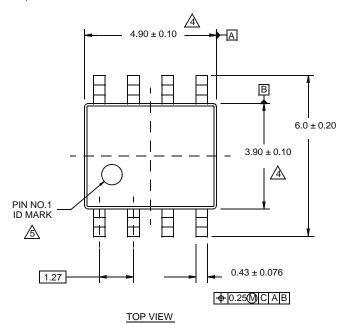

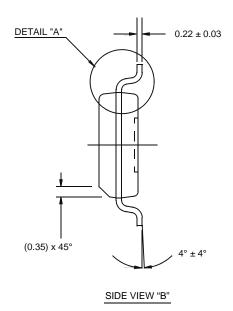

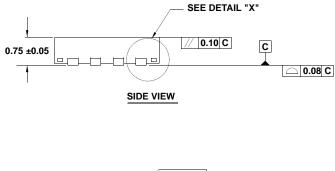

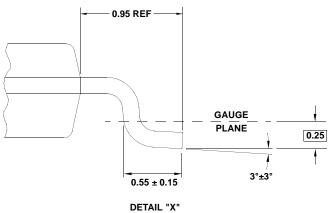

# **Package Outline Drawing**

M8.15E

8 LEAD NARROW BODY SMALL OUTLINE PLASTIC PACKAGE

Rev 0, 08/09

1.75 MAX

0.175 ± 0.075

SIDE VIEW "A

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- $2. \quad \hbox{Dimensioning and tolerancing conform to AMSE Y14.5m-1994}.$

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- Dimension does not include interlead flash or protrusions.

Interlead flash or protrusions shall not exceed 0.25mm per side.

- 5. The pin #1 identifier may be either a mold or mark feature.

- 6. Reference to JEDEC MS-012.

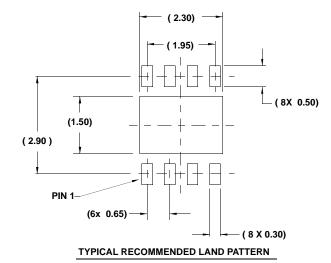

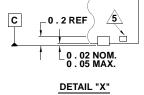

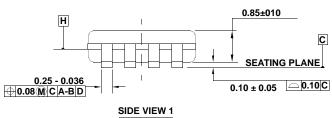

### **Package Outline Drawing**

L8.3x3A 8 LEAD THIN DUAL FLAT NO-LEAD PLASTIC PACKAGE Rev 4, 2/10

22

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to ASME Y14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- <u>4</u> Dimension applies to the metallized terminal and is measured between 0.15mm and 0.20mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Compliant to JEDEC MO-229 WEEC-2 except for the foot length.

FN6633.3

March 18, 2010

intersil

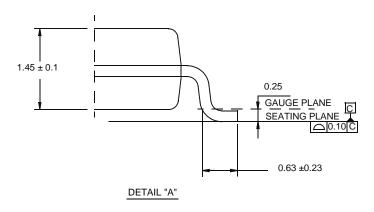

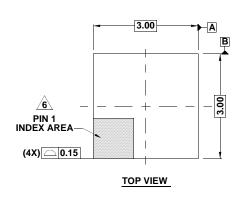

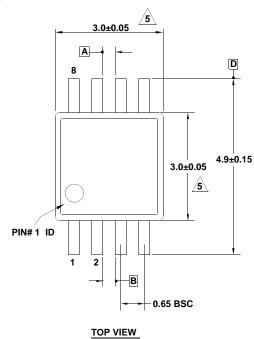

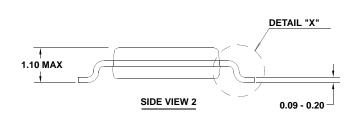

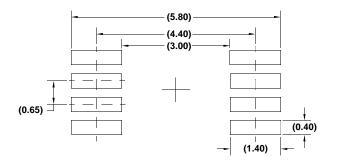

### **Package Outline Drawing**

M8.118

8 LEAD MINI SMALL OUTLINE PLASTIC PACKAGE

Rev 3, 3/10

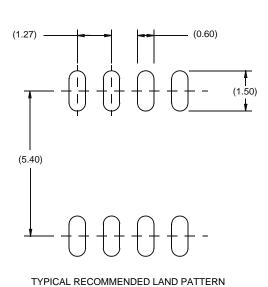

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- 1. Dimensions are in millimeters.

- Dimensioning and tolerancing conform to JEDEC MO-187-AA and AMSEY14.5m-1994.

- Plastic or metal protrusions of 0.15mm max per side are not included.

- 4. Plastic interlead protrusions of 0.15mm max per side are not included.

- 5. Dimensions are measured at Datum Plane "H".

- 6. Dimensions in ( ) are for reference only.

23 intersil