# 42-DL212

: A.007 Version

Issue Date : 2003/10/14

File Name: SP-DL212-A.007.doc

Total Pages : 6

# Optical Fiber Transmitting IC

9-7F-1, Prosperity Road I, Science Based Industrial Park,

Hsin-Chu, Taiwan 300, R.O.C.

Tel: 886-3-5645656 Fax: 886-3-5645626

# 42-DL212

# **OPTICAL FIBER TRANSMITTING IC**

#### GENERAL DESCRIPTION

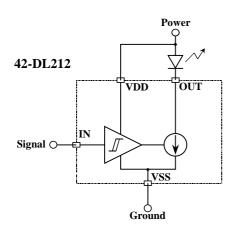

42-DL212 is a driver IC designed for the application of high-speed optical fiber transmission. It integrates the LED driver with constant current output to reduce the complexity and the cost of the transmission module. 42-DL212 can transmit with the speed up to 13Mb/s. 42-DL212 are fabricated by using CMOS technology with low power consumption purpose.

#### **FEATURES**

- 1. TTL interface compatible

- 2. High speed (up to 16Mb/s)

- 3. Uniform output waveform

- 4. Constant current output

- 5. Low power consumption

- 6. Wide range for Supply Voltage (2.7V-5.5V)

## **BLOCK DIAGRAM And APPLICATION CIRCUIT**

## **ABSOLUTE MAXIMUM RATINGS**

| Item                   | Symbol                    | Rating                       | Unit |

|------------------------|---------------------------|------------------------------|------|

| Supply Voltage         | $\mathbf{V}_{	extsf{DD}}$ | -0.5 to +7                   | V    |

| Input Voltage          | V <sub>IN</sub>           | -0.5 to V <sub>DD</sub> +0.5 | V    |

| Operating Temperature  | Topr                      | -40 to +85                   | °C   |

| Storage Temperature    | Tstg                      | -55 to +100                  | °C   |

| Electrostatic Damage   | ESD                       | 3.5                          | kV   |

| Output Sinking Current | Іоит                      | 50                           | mA   |

## RECOMMENDED OPERATING CONDITIONS

| ITEM                     | SYMBOL                    | MIN. | TYP. | MAX.     | UNIT |

|--------------------------|---------------------------|------|------|----------|------|

| Supply Voltage           | $\mathbf{V}_{	extsf{DD}}$ | 2.7  | -    | 5.5      | V    |

| High Level Input Voltage | $ m V_{IH}$               | 2.0  | -    | $V_{DD}$ | V    |

| Low Level Input Voltage  | $ m V_{IL}$               | 0    | -    | 0.8      | V    |

# ELECTRICAL CHARACTERISTICS ( $V_{DD}$ =5.0V, TA=25°C, if not mentioned)

| ITEM                            | SYMBOL                                                    | CONDITIONS                                                                                  | MIN. | TYP. | MAX.     | UNIT |

|---------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------|------|------|----------|------|

| High Level Input Voltage        | $V_{IH}$                                                  | V <sub>DD</sub> = 3V or 5V                                                                  | 2.0  | -    | $V_{DD}$ | V    |

| Low Level Input Voltage         | $\mathbf{V}_{\mathbf{IL}}$                                | V <sub>DD</sub> = 3V or 5V                                                                  | 0    | -    | 0.8      | V    |

| Input Leakage Current           | $I_{IN}$                                                  | VIN=VDD or VSS                                                                              | -    | -    | 1        | uA   |

| <b>Quiescent Supply Current</b> | $I_{\mathrm{DDQ}}$                                        | V <sub>IN</sub> =V <sub>SS</sub>                                                            | -    | 1    | 3        | mA   |

| Output Sinking Current          | IOUT_ON                                                   | V <sub>DD</sub> =3V or 5V,<br>V <sub>IN</sub> =V <sub>DD</sub> ,<br>V <sub>FLED</sub> =2.0V | 3.5  | 4.4  | 5.3      | mA   |

| Output Leakage Current          | Iout_off                                                  | V <sub>DD</sub> =3V or 5V,<br>V <sub>OUT</sub> =3V,<br>V <sub>IN</sub> =V <sub>SS</sub>     | -    | -    | 5        | uA   |

| Propagation Delay               | $\mathrm{T}_{\mathrm{PLH}}$ , $\mathrm{T}_{\mathrm{PHL}}$ | V <sub>DD</sub> =3V,<br>C <sub>LED</sub> =15pF,<br>V <sub>FLED</sub> =2.0V                  | -    | -    | 100      | ns   |

| Rise Time, Fall Time of IOUT    | $T_r, T_f$                                                | V <sub>DD</sub> =3 V,<br>C <sub>LED</sub> =15pF,<br>V <sub>FLED</sub> =2.0V                 | -    | -    | 10       | ns   |

| Pulse Width Distortion          | Δtw                                                       | CLED=15pF,<br>VFLED=2.0V                                                                    | - 25 | 0    | 25       | ns   |

| Jitter of Output Current        | Δtj                                                       | CLED=15pF,<br>VFLED=2.0V                                                                    |      | 1    | 25       | ns   |

| Data Rate                       | Fdata                                                     | NRZ Code,<br>Cled=15pF,<br>Vfled=2.0V                                                       | -    | -    | 16       | Mb/s |

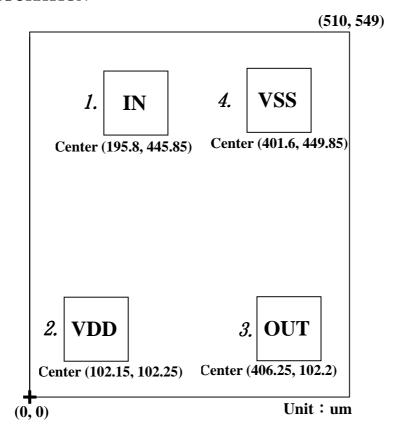

#### PAD DESCRIPTIONS

| PAD NO. | PAD NAME | DESCRIPTIONS                           |

|---------|----------|----------------------------------------|

| 1       | IN       | Input Pad(Active High )                |

| 2       | VDD      | Supply Voltage                         |

| 3       | OUT      | Output Pad Sinking Current(Active Low) |

| 4       | VSS      | Ground                                 |

## **DIE CONFIGURATION**

Die Size: 510um \* 549um Die Thickness: 12mil(=300um) Pad Size: 100um \* 100um

\* Note: SiTI reserves the right to improve the device geometry and manufacturing processes without prior notice. Though these improvements may result in slight geometry changes, they will not affect die electrical characteristics and pad layouts.

## REQUIREMENTS FOR WAFER DELIVERY

Material: Silicon with P-Substrate

Diameter : 6 inches(≒15cm)

Thickness : 12 mils(≒300um)

Malfunctioned die: Marked with red ink or equivalent marking

#### HANDLING RECOMMENDATION FOR STATIC ELECTRICITY PROTECTION

- (1) Avoid any circumstance that produce static electricity, e.g. rubbing against plastic, during moving, storing and processing 42-DL212.

- (2) Process 42-DL212 in a clean room with proper temperature and humidity.

- (3) Ground all working machines and workers wear anti-electrostatic ring to ground during processing.

- (4) Avoid contact 42-DL212with bare hands .If unavoided, wear anti-electrostatic ring and use anti-electrostatic tool to pick it up.

#### GUARANTED TEMPERATURE AND RETENTION CYCLE

(1) The device/wafer 42-DL212 should be stored in the nitrogenous chest. The conditions suggested are as follows:

Temperature =  $23\pm3^{\circ}$ C

Relative Humidity =  $50\pm10\%$

Minimum nitrogen inflow = 3 liters/minute

- (2) If the device/wafer, 42-DL212 is incidentally exposed to the air, use it for manufacturing as soon as possible.

- (3) Under the storage environment specified in item (1), six-month safe storage period is guaranteed.

The products listed herein are designed for ordinary electronic applications, such as electrical appliances, audio-visual equipment, communications devices and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

Silicon Touch Technology, Inc. will not take any responsibilities regarding the misusage of the products mentioned above. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. Silicon Touch Technology, Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.