# **SC4612H** 40V Synchronous Buck Controller

# POWER MANAGEMENT

### Features

- Wide input voltage range, 4.75V to 40V

- Internally regulated DRV

- 1.7A gate drive capability

- Low side RDS-ON sensing with hiccup OCP

- Programmable current limit

- Programmable frequency up to 1.2 MHz

- Overtemperature protected

- Pre-bias startup

- Reference accuracy ±1%

- Available in MLPD-12 4 x 3 and SOIC-14 Pb-free packages. This product is fully WEEE and RoHS compliant

# **Applications**

- Distributed power architectures

- Telecommunication equipment

- Servers/work stations

- Mixed signal applications

- Base station power management

- Point of use low voltage high current applications

# Description

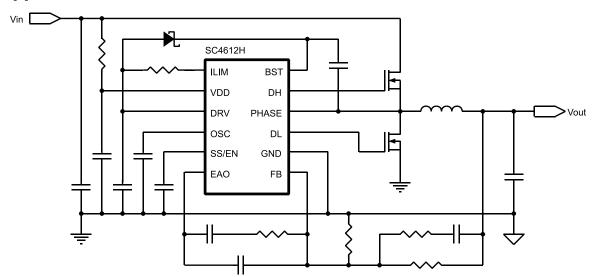

The SC4612H is a high performance synchronous buck controller that can be configured for a wide range of applications. The SC4612H utilizes synchronous rectified buck topology where high efficiency is the primary consideration. SC4612H can be used over a wide input voltage range with output voltage adjustable within limits set by the duty cycle boundaries.

SC4612H comes with a rich set of features such as regulated DRV supply, programmable soft-start, high current gate drivers, shoot through protection,  $R_{DS(ON)}$  sensing with hiccup over current protection.

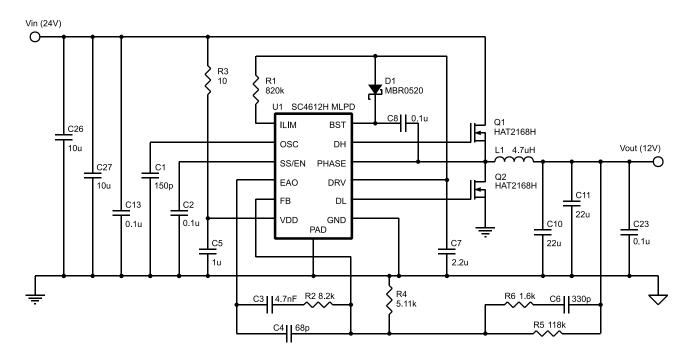

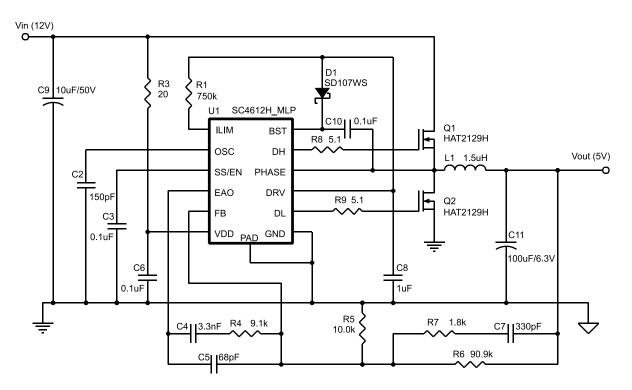

# Typical Application Circuit

# **Ordering Information**

| Part Number(3)            | Package <sup>(2)</sup> | Temp. Range (T <sub>.</sub> ) |  |  |  |

|---------------------------|------------------------|-------------------------------|--|--|--|

| SC4612HMLTRT              | MLPD-12 4 x3           | -40°C to +125°C               |  |  |  |

| SC4612HSTRT               | SOIC-14                | -40 C to +125 C               |  |  |  |

| SC4612HEVB <sup>(1)</sup> | EVALUATION BOARD       |                               |  |  |  |

Notes:

(1) When ordering please specify MLPD or SOIC package.

(2) Only available in tape and reel packaging. A reel contains 3000 devices for MLPD package and 2500 for SOIC package..

(3) Pb-free product. This product is fully WEEE and RoHS compliant.

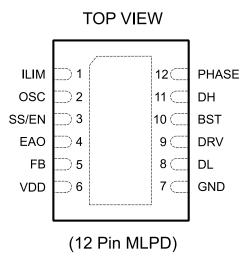

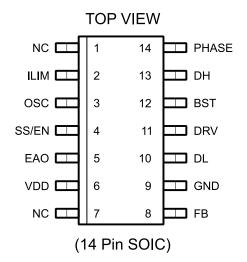

### **Pin Configuration**

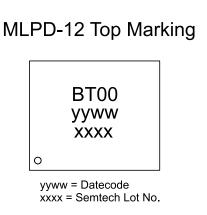

# **Marking Information**

# SOIC-14 Top Marking

# **Absolute Maximum Ratings**

| VDD (V)                                    |

|--------------------------------------------|

| PHASE to GND(V)0.3 to +55                  |

| EAO, SS/EN, FB, OSC(V)0.3 to +5            |

| Pin Voltage - All Other Pins (V)0.3 to +10 |

| DRV Source Current (peak) (mA)100          |

| ESD Protection Level <sup>(1)</sup> (kV)1  |

# **Recommended Operating Conditions**

Supply Voltage Range (VDD) (V) ...... 5 to +40

# **Thermal Information**

| R <sub>θja</sub> (SOIC) <sup>(2)</sup> (°C/W) 115 |

|---------------------------------------------------|

| R <sub>θja</sub> (MLPD) <sup>(2)</sup> (°C/W)     |

| R <sub>θjc</sub> (SOIC) (°C/W)                    |

| R <sub>θjc</sub> (MLPD) (°C/W) 11                 |

| Maximum Junction Temperature (°C)+125             |

| Storage Temperature Range (°C)65 to +150          |

| Ambient Temperature Range (°C)40 to +105          |

| Peak IR Reflow Temperature (10s to 30s) (°C)+260  |

Exceeding the Absolute Maximum Ratings may result in permanent damage to the device or device malfunction. Operation outside of the Recommended Operating Conditions is not recommended.

NOTES:

(1) Tested according to JEDEC standard JESD22-A114-B.

(2) Calculated from package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under the exposed pad per JESD51 standards.

#### **Electrical Characteristics** -

Unless otherwise specified,  $T_A = T_J = +25^{\circ}C$ ,  $V_{IN} = V_{VDD} = 12V$

| Parameter                       | Symbol                     | Conditions                                                                                                                                                               | Min  | Тур  | Max  | Units |  |  |  |

|---------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|--|--|--|

| Bias Supply                     |                            |                                                                                                                                                                          |      |      |      |       |  |  |  |

| Quiescent Current               | Ι <sub>Q</sub>             | $V_{VDD} = 40V$ , No load, $V_{SS/EN} = 0V$                                                                                                                              |      | 5    | 7    | mA    |  |  |  |

| VDD Undervoltage Lockout        |                            |                                                                                                                                                                          |      |      |      |       |  |  |  |

| Start Threshold                 | V <sub>UVLO</sub>          |                                                                                                                                                                          | 4.20 | 4.50 | 4.75 | V     |  |  |  |

| UVLO Hysteresis                 | V <sub>UVLO-HYST</sub>     |                                                                                                                                                                          |      | 400  |      | mV    |  |  |  |

| Drive Regulator                 |                            |                                                                                                                                                                          |      |      |      |       |  |  |  |

| DRV Output Voltage              | V <sub>DRV</sub>           | $10V \le V_{VDD} \le 40V, I_{DRV} \le 1mA$                                                                                                                               | 7.3  | 7.8  | 8.3  | V     |  |  |  |

| Load Regulation                 |                            | 1mA≤ I <sub>DRV</sub> ≤ 70mA                                                                                                                                             |      |      | 100  | mV    |  |  |  |

| Oscillator                      |                            |                                                                                                                                                                          |      |      |      |       |  |  |  |

| Operating Frequency Range       | ncy Range f <sub>osc</sub> |                                                                                                                                                                          | 100  |      | 1200 | kHz   |  |  |  |

| Initial Accuracy <sup>(1)</sup> |                            | C <sub>osc</sub> =160pF (Ref only)                                                                                                                                       | 540  | 600  | 660  | kHz   |  |  |  |

| Maximum Duty Cycle              |                            | V <sub>VDD</sub> =V <sub>DRV</sub> =8V; V <sub>OUT_NOM</sub> =5V; I <sub>OUT</sub> =0A; V <sub>VDD</sub> adjusted<br>down to V <sub>OUT</sub> =0.99*V <sub>OUT_NOM</sub> | 82   |      |      | %     |  |  |  |

| Ramp Peak to Valley $^{(1)}$    | V <sub>RAMP</sub>          |                                                                                                                                                                          |      | 850  |      | mV    |  |  |  |

| Oscillator Charge Current       | I <sub>osc</sub>           | V <sub>osc</sub> =1V                                                                                                                                                     |      |      | 110  | μA    |  |  |  |

# **Electrical Characteristics (continued)**

| Parameter                                     | Symbol              | Conditions                         | Min   | Тур   | Мах   | Units |

|-----------------------------------------------|---------------------|------------------------------------|-------|-------|-------|-------|

| Current Limit - Low Side R <sub>DS(ON)</sub>  | <u> </u>            |                                    | I     |       |       |       |

| Current Limit Threshold Voltage               | V <sub>CL</sub>     |                                    |       | 100   |       | mV    |

| Error Amplifier                               |                     |                                    |       |       |       |       |

|                                               |                     | T <sub>j</sub> =0 to +70°C         | 0.495 | 0.500 | 0.505 | V     |

| Feedback Voltage                              | V <sub>FB</sub>     | $T_{j}$ =-40 to + 85°C             | 0.492 | 0.500 | 0.508 | V     |

|                                               |                     | T <sub>j</sub> =-40 to +125°C      | 0.488 | 0.500 | 0.512 | V     |

| Input Bias Current                            | I <sub>FB</sub>     | V <sub>FB</sub> =0.5V              |       |       | 200   | nA    |

| Open Loop Gain <sup>(1)</sup>                 |                     |                                    |       | 60    |       | dB    |

| Unity Gain Bandwidth <sup>(1)</sup>           |                     |                                    | 7     | 10    |       | MHz   |

| Output Sink Current                           |                     | Open Loop; V <sub>FB</sub> =0V     |       | 900   |       | μA    |

| Output Source Current                         |                     | Open Loop; V <sub>FB</sub> =0.6V   |       | 1100  |       | μA    |

| Slew Rate <sup>(1)</sup>                      |                     |                                    |       | 1     |       | V/µs  |

| SS/EN                                         | <u> </u>            |                                    |       |       |       |       |

| Disable Threshold Voltage                     | V <sub>SS-DIS</sub> |                                    |       |       | 500   | mV    |

| Soft Start Charge Current                     | I <sub>ss</sub>     |                                    |       | 25    |       | μA    |

| Soft Start Discharge Current <sup>(1)</sup>   | I <sub>SSD</sub>    |                                    |       | 1     |       | μΑ    |

| Disable Low to Shut Down                      |                     |                                    |       | 50    |       | ns    |

| Hiccup                                        | · · ·               |                                    | ·     |       |       |       |

| Hiccup Duty Cycle                             |                     | CSS=0.1uF; current limit condition |       | 1     |       | %     |

| Gate Drive                                    |                     |                                    | i     |       |       | ,     |

| Gate Drive On Resistance (H) <sup>(2)</sup>   |                     | I <sub>SOURCE</sub> =100mA         |       | 3     | 4     | Ω     |

| Gate Drive On Resistance (H) <sup>(2)</sup>   |                     | I <sub>SINK</sub> =100mA           |       | 3     | 4     | Ω     |

| DL/DH Source/Sink Peak Current <sup>(2)</sup> |                     | C=2000pF                           | 1.4   | 1.7   |       | A     |

| DL/DH Rise/Fall Time <sup>(2)</sup>           |                     | C=2000pF                           |       | 20    |       | ns    |

| Minimum Non-Overlap <sup>(1)</sup>            | t <sub>DEAD</sub>   |                                    |       | 30    |       | ns    |

| Minimum On Time <sup>(2)</sup>                | t <sub>on-min</sub> |                                    |       |       | 110   | ns    |

| Thermal Shutdown                              | · ·                 |                                    |       |       |       |       |

| Shutdown Temperature <sup>(2)</sup>           |                     |                                    |       | 165   |       | °C    |

| Thermal Shutdown Hysteresis (2)               |                     |                                    |       | 15    |       | °C    |

NOTES:

(1) Guaranteed by design, not production tested.

(2) Guaranteed by characterization.

(2) This device is ESD sensitive, use of standard ESD handling precautions is required.

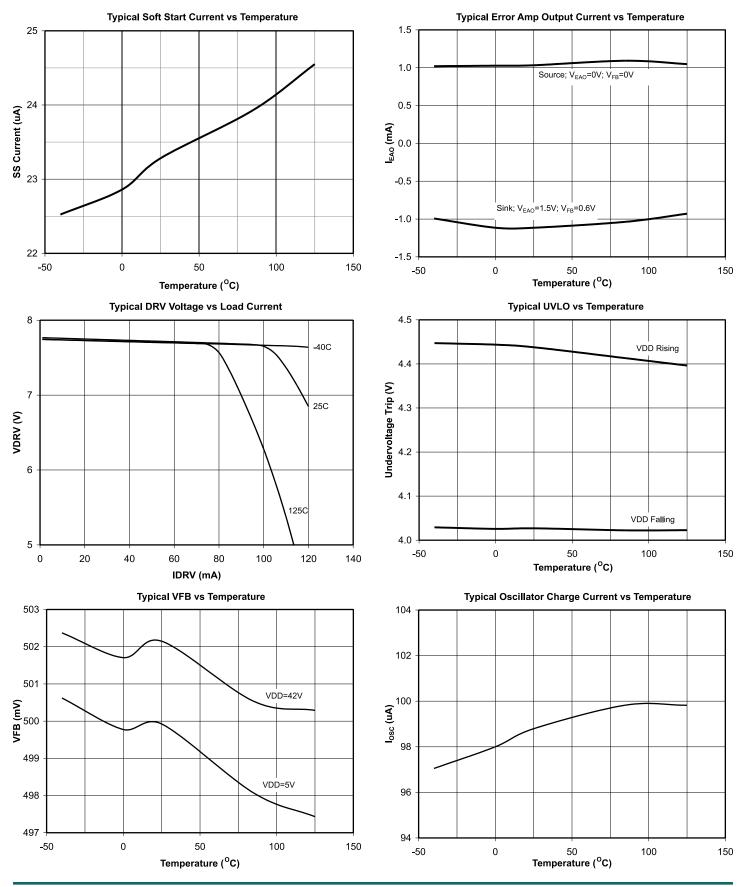

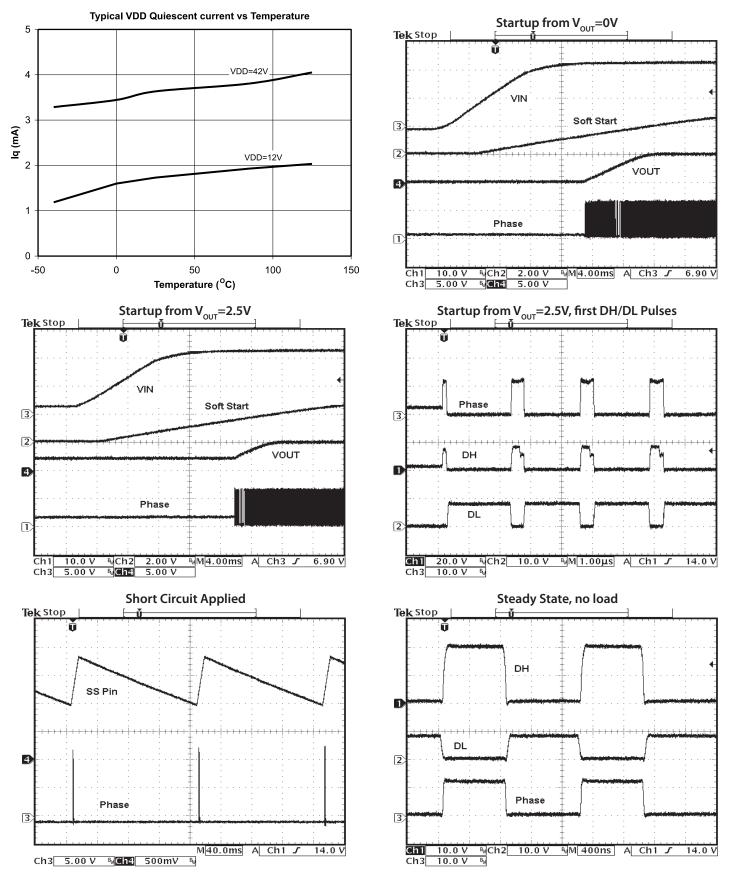

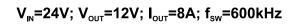

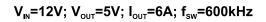

# **Typical Characteristics**

# **Typical Characteristics**

# **Pin Descriptions**

| Pin #<br>MLPD | Pin #<br>SOIC | Pin Name          | Pin Function                                                                                                                                                                                                                                                                                  |  |  |

|---------------|---------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|               | 1,7           | NC                | No Connection                                                                                                                                                                                                                                                                                 |  |  |

| 1             | 2             | ILIM              | This pin can be used to modify the current limit threshold for the low side MOSFET R <sub>DS(ON)</sub> sensing. Once the voltage drop across the bottom MOSFET is larger than the programmed value, current limit condition occurs, and the hiccup current limit protection is activated.     |  |  |

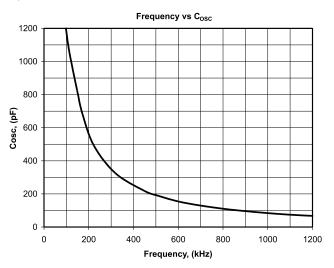

| 2             | 3             | OSC               | Oscillator Frequency set pin. An external capacitor to GND will program the oscillator frequency. See Table 1 "Frequency vs. C OSC" to determine oscillator frequency.                                                                                                                        |  |  |

| 3             | 4             | SS/EN             | Soft Start pin. Internal current source connected to a single external capacitor will deter-<br>mine the soft-start duration for the output. Inhibits the chip if pulled down.                                                                                                                |  |  |

| 4             | 5             | EAO               | Error Amplifier Output. A compensation network is connected from this pin to FB.                                                                                                                                                                                                              |  |  |

| 5             | 8             | FB                | The inverting input of the error amplifier, used to sense the output voltage via a resistive divider.                                                                                                                                                                                         |  |  |

| 6             | 6             | VDD               | Main IC supply.                                                                                                                                                                                                                                                                               |  |  |

| 7             | 9             | GND               | Ground.                                                                                                                                                                                                                                                                                       |  |  |

| 8             | 10            | DL                | Drive Low. Gate drive for the bottom MOSFET.                                                                                                                                                                                                                                                  |  |  |

| 9             | 11            | DRV               | DRV supplies the external MOSFETs gate drive and the some internal circuitry. This pin should be bypassed with a ceramic capacitor to GND. DRV is internally regulated from the external supply connected to VDD. If VDD is below10V, the supply should be directly connected to the DRV pin. |  |  |

| 10            | 12            | BST               | Supply for high side driver; can be directly connected to an external supply or to a boot-<br>strap circuit.                                                                                                                                                                                  |  |  |

| 11            | 13            | DH                | Drive High. Gate drive for the top MOSFET.                                                                                                                                                                                                                                                    |  |  |

| 12            | 14            | PHASE             | The return path for the high side gate drive, also used to sense the voltage at the phase node for adaptive gate drive protection and the low-side R <sub>DS(ON)</sub> current sensing.                                                                                                       |  |  |

| Х             | N/A           | THERMAL PAD (GND) | Pad for heatsinking purposes. Connect to ground plane using multiple vias.                                                                                                                                                                                                                    |  |  |

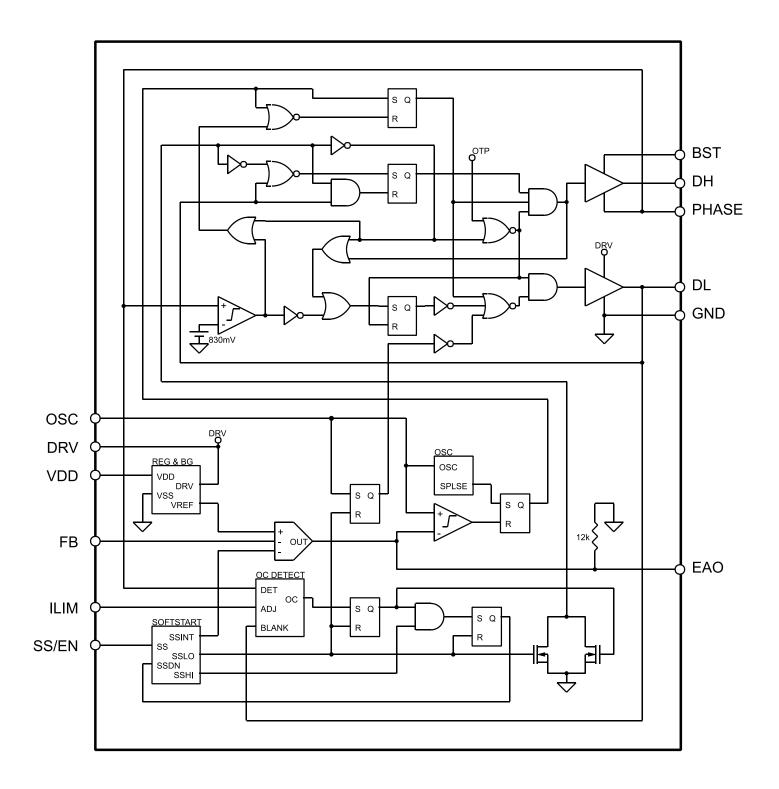

# **Block Diagram**

### **Applications Information**

#### **General Description**

The SC4612H is a versatile voltage mode synchronous rectified buck PWM convertor, with an input supply (VIN) ranging from 4.5V to 40V designed to control and drive N-channel MOSFETs.

The power dissipation is controlled by allowing high speed and integration with the high drive currents to ensure low MOSFET switching loss. The synchronous buck configuration also allows converter sinking current from load without losing output regulation.

The internal reference is trimmed to 500mV with  $\pm$  1% accuracy, and the output voltage can be adjusted by an external resistor divider.

A fixed oscillator frequency (up to 1.2MHz) can be programmed by an external capacitor for design optimization.

Other features of the SC4612H include:

Wide input power voltage range (from 4.5V to 40V), low output voltages, externally programmable softstart, hiccup over current protection, wide duty cycle range, thermal shutdown, and -40 to 125°C junction operating temperature range.

#### **Theory of Operation**

#### Supplies:

Two pins (VDD and DRV) are used to power up the SC4612H. If input supply (Vin) is less than 10V, tie DRV and VDD together. This DRV supply should be bypassed with a low ESR 2.2uF (or greater) ceramic capacitor directly at the DRV to GND pins of the SC4612H. The DRV supply also provides the bias for the low and the high side MOSFET gate drive. The maximum rating for DRV supply is 10V and for applications where input supply is below 10V, it should be connected directly to VDD. The internal pass transistor will regulate the DRV from an external supply connected to VDD to produce 7.8V typical at the DRV pin.

#### Soft Start / Shut down:

The SC4612H performs a "pre-bias" type startup. This ensures that a pre-charged output capacitor will not cause the SC4612H to turn on the bottom FET during startup to discharge it, as a normal synchronous buck controller would do. An external capacitor on the SS/ EN pin is used to set the Soft Start duration.

Startup is inhibited until VDD input reaches the UVLO threshold (typically 4.5V). Once VDD rises above UVLO, the external soft start capacitor begins to charge from an internal 25uA current source. When the SS/EN pin reaches approximately 0.8V, top side switching is enabled. However, a top side pulse will not occur until SS/EN has charged up to the level appropriate for the existing output voltage (a pre bias condition). Once the first top side gate pulse actually occurs, the bottom side driver is enabled and the remainder of the startup is fully synchronous. In the event of an over current during startup, the SC4612H behaves in the same manner as an over current in steady state (see Over Current Protection).

#### **Oscillator Frequency Selection:**

The internal oscillator sawtooth signal is generated by charging an external capacitor with an internal  $100\mu$ A current source.

#### **Under Voltage Lock Out**

Under Voltage Lock Out (UVLO) circuitry senses the VDD through a voltage divider. If this signal falls below 4.5V (typical) with a 400mV hysteresis (typical), the output drivers are disabled. During the thermal shutdown, the output drivers are disabled.

#### **Over Current Protection**

The SC4612H features low side MOSFET RDS(ON) current sensing and hiccup mode over current protection. The voltage across the bottom FET is sampled approximately 150ns after it is turned on to prevent false tripping due to ringing of the phase node.

The internally set over current threshold is 100mV typical. This can be adjusted up or down by connecting a resistor between ILIM and DRV or GND respectively. When programming with an external resistor, threshold set point accuracy will be degraded to 30%. The FET  $R_{DS(ON)}$  at temperature will typically be 150% or more of the room temperature value. Allowance should be made for these sources of error when programming a threshold value. When an over current event occurs, the SC4612H immediately disables both gate drives. The SS ramp continues to its final value, if not already there. Once at final value, the SS capacitor is discharged at approximately 1uA until SS low value is reached (approx 0.8V). The SS/ Hiccup cycle will then repeat until the fault condition is removed and the SC4612H starts up normally on the next SS cycle.

#### **Gate Drive/Control**

The SC4612H provides integrated high current drivers for fast switching of large MOSFETs. The higher gate current will reduce switching losses of the larger MOSFETs.

The low side gate drive is supplied directly from the DRV. The high side gate drive is bootstraped from the DRV pin. Cross conduction prevention circuitry ensures a non overlapping (30ns typical) gate drive between the top and bottom MOSFETs. This prevents shoot through losses which provides higher efficiency. Typical total minimum off time for the SC4612H is about 30ns.

#### **Error Amplifer Design**

The SC4612H is a voltage mode buck controller that utilizes an externally compensated high bandwidth error amplifier to regulate the output voltage. The power stage of the synchronous rectified buck converter control-to-output transfer function is as shown below.

$$G_{VD}(s) = \frac{V_{IN}}{V_R} \left( \frac{1 + sCR_{ESR}}{1 + s\frac{L}{R_L} + s^2 LC} \right) \qquad \dots \dots \dots (2)$$

where,

$V_{IN} = Input voltage$

L = Output inductance

$R_{ESR} = Output \ capacitor \ ESR$

$V_{R}$  = Peak to peak ramp voltage

$R_{L} = Load resistance$

C = Output capacitance

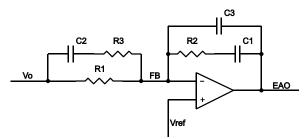

The classical Type III compensation network can be built around the error amplifier as shown below:

#### Fig 1. Type III compensation network

The transfer function of the compensation network is as follows:

$$G_{\text{COMP}}(s) = \frac{\omega_1}{s} \cdot \frac{\left(1 + \frac{s}{\omega_{z_1}}\right) \left(1 + \frac{s}{\omega_{z_2}}\right)}{\left(1 + \frac{s}{\omega_{P_1}}\right) \left(1 + \frac{s}{\omega_{P_2}}\right)} \qquad \dots \dots \dots (3)$$

where,

$$\omega_{Z1} = \frac{1}{R_2C_1}, \quad \omega_{Z2} = \frac{1}{(R_1 + R_3)C_2}$$

$$\omega_1 = \frac{1}{R_1(C_1 + C_3)}, \quad \omega_{P1} = \frac{1}{R_3C_2}$$

$$\omega_{P2} = \frac{1}{R_2\left(\frac{C_1C_3}{C_1 + C_3}\right)}$$

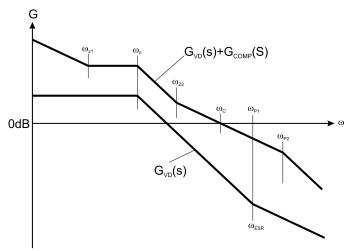

The design guidelines are as following:

1. Set the loop gain crossover frequency  $\omega_{\rm c}$  for given switching frequency.

2. Place an integrator at the origin to increase DC and low frequency gains.

3. Select  $\omega_{z_1}$  and  $\omega_{z_2}$  such that they are placed near  $\omega_0$  to dampen peaking; the loop gain should cross

0dB at a rate of -20dB/dec.

4. Cancel  $\omega_{ESR}$  with compensation pole  $\omega_{P1}$  ( $\omega_{P1}=\omega_{ESR}$ ). 5. Place a high frequency compensation pole  $\omega_{P2}$  at half the switching frequency to get the maximum attenuation of the switching ripple and the high frequency noise with adequate phase lag at  $\omega_c$ .

Fig2. Power stage and compensated loop gain.

#### **COMPONENT SELECTION:**

#### **SWITCHING SECTION**

OUTPUT CAPACITORS - Selection begins with the most critical component. Because of fast transient load current requirements in modern microprocessor core supplies, the output capacitors must supply all transient load current requirements until the current in the output inductor ramps up to the new level. Output capacitor ESR is therefore one of the most important criteria. The maximum ESR can be simply calculated from.

$$R_{ESR} \leq \frac{V_t}{I_t}$$

.....(4)

where,

$V_t$  = Maximum transient voltage excursion  $I_t$  = Transient current step

For example, to meet a 100mV transient limit with a 10A load step, the output capacitor ESR must be less than  $10m\Omega$ . To meet this kind of ESR level, there are four available capacitor technologies.

| Technology       | Each<br>Capacitor |             | Qty<br>Rqd. | Total     |             |  |

|------------------|-------------------|-------------|-------------|-----------|-------------|--|

|                  | C<br>(μF)         | ESR<br>(mΩ) |             | C<br>(μF) | ESR<br>(mΩ) |  |

| Ceramic          | 22                | 2-10        | 1           | 22 2-10   |             |  |

| SP Cap           | 220               | 7           | 1           | 220       | 7.0         |  |

| POS-CAP          | 680               | 18          | 2           | 1360      | 9.0         |  |

| Low ESR Aluminum | 1500              | 44          | 5           | 7500      | 8.8         |  |

The choice of which to use is simply a cost/ performance issue, with low ESR Aluminum being the cheapest, but taking up the most space.

INDUCTOR - Having decided on a suitable type and value of output capacitor, the maximum allowable value of inductor can be calculated. Too large an inductor will produce a slow current ramp rate and will cause the output capacitor to supply more of the transient load current for longer - leading to an output voltage sag below the ESR excursion calculated above.

The maximum inductor value may be calculated from:

The calculated maximum inductor value assumes 100% duty cycle, so some allowance must be made. Choosing an inductor value of 50 to 75% of the calculated maximum will guarantee that the inductor current will ramp fast enough to reduce the voltage dropped across the ESR at a faster rate than the capacitor sags, hence ensuring a good recovery from transient with no additional excursions. We must also be concerned with ripple current in the output inductor and a general rule of thumb has been to allow 10%-20% of maximum output current as ripple current. Note that most of the output voltage ripple is produced by the inductor ripple current flowing in the output capacitor ESR. Ripple current can be calculated from:

Ripple current allowance will define the minimum permitted inductor value.

POWER FETS - The FETs are chosen based on several criteria with probably the most important being power dissipation and power handling capability.

TOP FET - The power dissipation in the top FET is a combination of conduction losses, switching losses and bottom FET body diode recovery losses. a) Conduction losses are simply calculated as:

$$D = \text{Duty cycle} \approx \frac{V_{O}}{V_{IN}}$$

b) Switching losses can be estimated if the switching time is known or assumed:

$$\mathsf{P}_{\mathsf{SW}} = \frac{\mathsf{I}_{\mathsf{O}} \cdot \mathsf{V}_{\mathsf{IN}} \cdot (\mathsf{t}_{\mathsf{r}} + \mathsf{t}_{\mathsf{f}}) \cdot \mathsf{f}_{\mathsf{OSC}}}{2} \qquad \dots \dots \dots (8)$$

c) Body diode recovery losses are more difficult to estimate, but to a first approximation, it is reasonable to assume that the stored charge on the bottom FET body diode will be moved through the top FET as it starts to turn on. The resulting power dissipation in the top FET will be:

BOTTOM FET - Bottom FET losses are almost entirely due to conduction. The body diode is forced into conduction at the beginning and end of the bottom switch conduction period, so when the FET turns on and off, there is very little voltage across it resulting in very low switching losses. Conduction losses for the FET can be determined by:

INPUT CAPACITORS - Since the RMS ripple current in the input capacitors may be as high as 50% of the output current, suitable capacitors must be chosen accordingly. Also, during fast load transients, there may be restrictions on input di/dt. These restrictions require useable energy storage within the converter circuitry, either as extra output capacitance or, more usually, additional input capacitors. Choosing low ESR input capacitors will help maximize ripple rating for a given size.

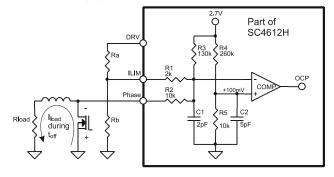

### Low Side $R_{DS(ON)}$ Current Limit

Fig3: Current Limit circuitry

1. Programming resistors Ra and Rb - Not installed:

$$\frac{2.75V - 100mV}{R_3} = \frac{100mV - V_{PH}}{R_2} \quad \dots \dots (11)$$

solving for:  $V_{PH} = -100 \text{mV}$ , the circuit will trip at  $R_{DS(ON)} \times I_{LOAD} = 100 \text{mV}$

2. To increase trip voltage - install Ra.

$$Ra = \frac{-772 - 20 \cdot V_{PH}}{1 + 10 \cdot V_{PH}} \qquad \dots \dots \dots \dots (12)$$

solving for double the current limit:  $V_{_{PH}}$  = -200mV. Ra = 768k $\Omega.$

3. To decrease trip voltage - install Rb

$$Rb = \frac{8 - 20 \cdot V_{PH}}{1 + 10 \cdot V_{PH}}$$

.....(13)

solving for half the current limit:  $V_{_{PH}} = -50$  mV. Rb =  $18 k\Omega$ .

NOTE: Allow for tempco and  $\rm R_{\rm DS(ON)}$  variation of the MOSFET- see the "Over Current Protection" section of the datasheet.

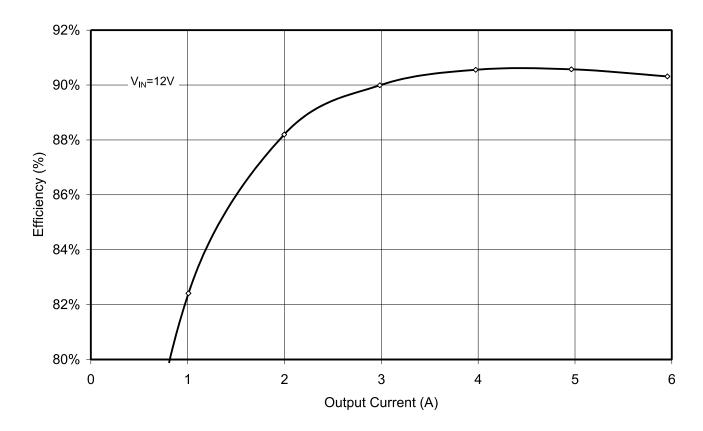

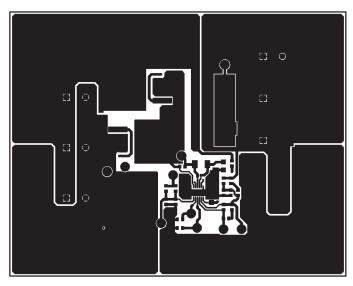

#### **PCB Layout Guidelines**

Careful attention to layout is necessary for successful implementation of the SC4612H PWM controller. High switching currents are present in the application and their effect on ground plane voltage differentials must be understood and minimized.

1) The high power section of the circuit should be laid out first. A ground plane should be used. The number and position of ground plane interruptions should not unnecessarily compromise ground plane integrity. Isolated or semi-isolated areas of the ground plane may be deliberately introduced to constrain ground currents to particular areas; for example, the input capacitor and bottom FET ground.

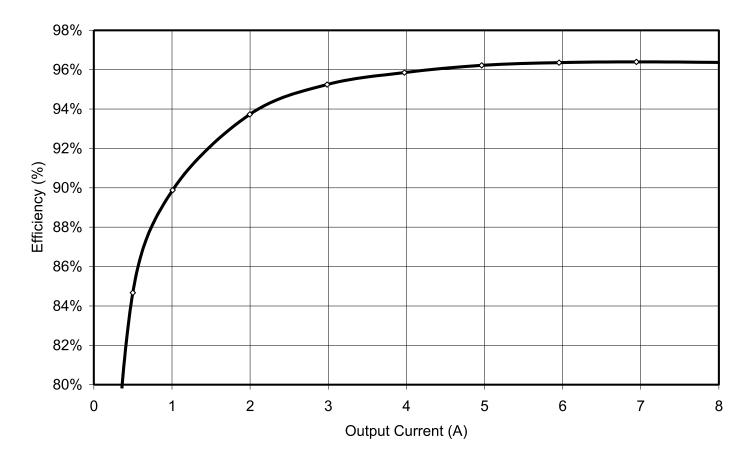

2) The loop formed by the Input Capacitor(s) (Cin), the Top FET (Q1), and the Bottom FET (Q2) must be kept as small as possible. This loop contains all the high current, fast transition switching. Connections should be as wide and as short as possible to minimize loop inductance. Minimizing this loop area will a) reduce EMI, b) lower ground injection currents, resulting in electrically "cleaner" grounds for the rest of the system and c) minimize source ringing, resulting in more reliable gate switching signals.

3) The connection between the junction of Q1, Q2 and the output inductor should be a wide trace or copper region. It should be as short as practical. Since this connection has fast voltage transitions, keeping this connection short will minimize EMI. Also keep the Phase connection to the IC short. Top FET gate charge currents flow in this trace.

4) The Output Capacitor(s) (Cout) should be located as close to the load as possible. Fast transient load currents are supplied by Cout only, and therefore, connections between Cout and the load must be short, wide copper areas to minimize inductance and resistance.

5) The SC4612H is best placed over a quiet ground plane area. Avoid pulse currents in the Cin, Q1, Q2 loop flowing in this area. GND should be returned to the ground plane close to the package and close to the ground side of (one of) the output capacitor(s). If this is not possible, the GND pin may be connected to the ground path between the Output Capacitor(s) and the Cin, Q1, Q2 loop. Under no circumstances should GND be returned to a ground inside the Cin, Q1, Q2 loop.

6) Allow adequate heat sinking area for the power components. If multiple layers will be used, provide sufficent vias for heat transfer.

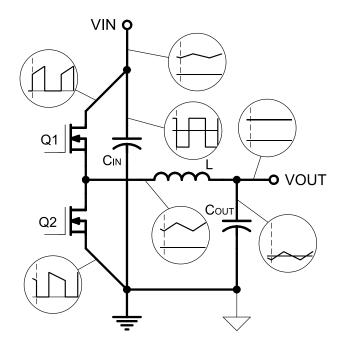

Fig4: Current waveforms of buck power stage.

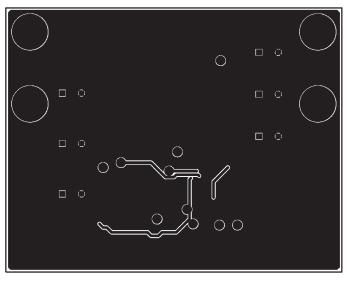

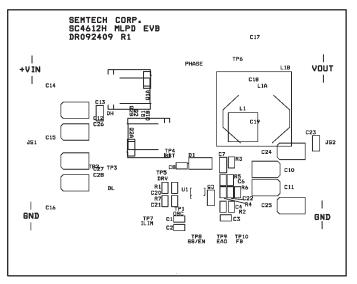

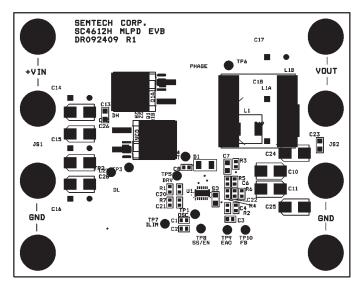

### **Typical EVB Layout**

**Top Copper**

Bottom Copper (viewed from top)

**Top Silk Screen**

**Top Assembly**

12

0.08

0.10

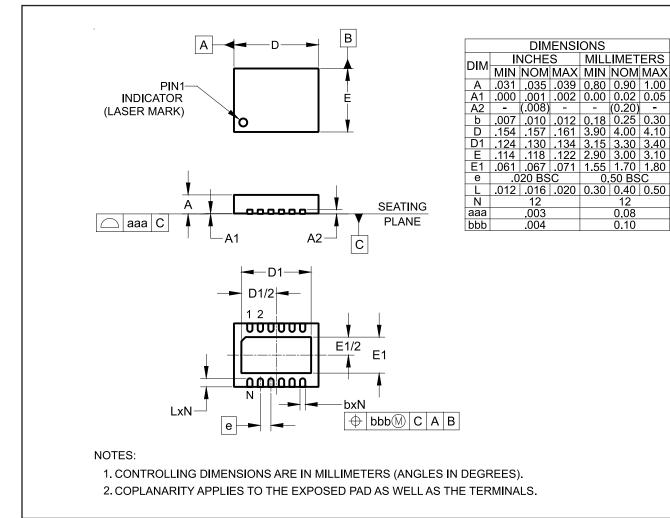

# **Outline Drawing — MLPD-12**

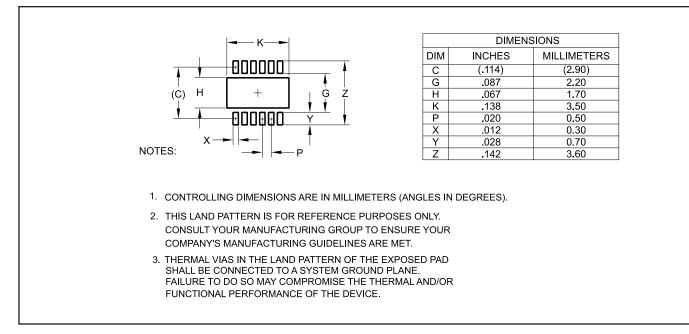

### Land Pattern — MLPD-12

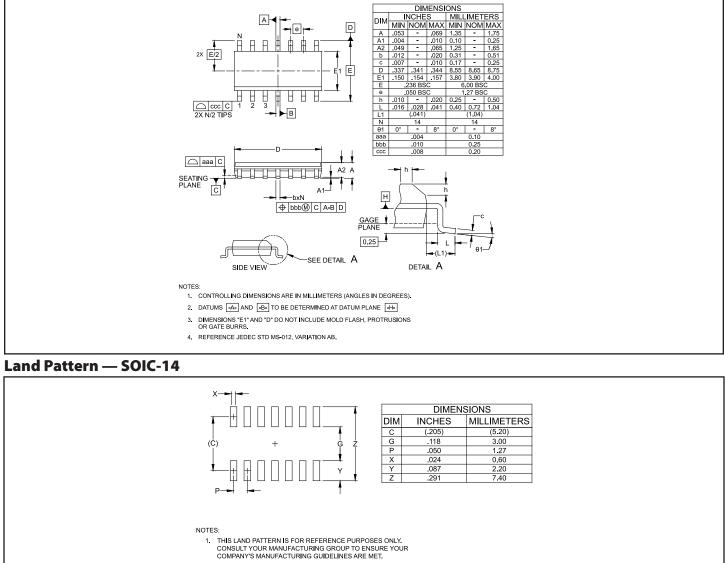

### **Outline Drawing — SOIC-14**

2. REFERENCE IPC-SM-782A, RLP NO. 302A.

**Contact Information**

Semtech Corporation **Power Management Products Division** 200 Flynn Road, Camarillo, CA 93012 Phone: (805) 498-2111 Fax: (805) 498-3804

www.semtech.com