## Intel<sup>®</sup> 810E Chipset: 82810E Graphics and Memory Controller Hub (GMCH)

**Datasheet**

September 2000

Order Number: 290676-002

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The Intel<sup>®</sup> 810E chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

$l^2C$  is a 2-wire communications bus/protocol developed by Philips. SMBus is a subset of the  $l^2C$  bus/protocol and was developed by Intel. Implementations of the  $l^2C$  bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Alert on LAN is a result of the Intel-IBM Advanced Manageability Alliance and a trademark of IBM

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature, may be obtained from:

Intel Corporation www.intel.com or call 1-800-548-4725

or call 1-800-548-4725

\*Third-party brands and names are the property of their respective owners.

Copyright © Intel Corporation 2000

# intel.

# Contents

| 1. | Overv | riew                                                             | 11 |  |  |  |  |

|----|-------|------------------------------------------------------------------|----|--|--|--|--|

|    | 1.1.  | The Intel® 810E Chipset System                                   | 11 |  |  |  |  |

|    | 1.2.  | GMCH Overview                                                    |    |  |  |  |  |

|    | 1.3.  | Host Interface                                                   |    |  |  |  |  |

|    | 1.4.  | System Memory Interface                                          |    |  |  |  |  |

|    | 1.5.  | Display Cache Interface                                          |    |  |  |  |  |

|    | 1.6.  | Hub Interface                                                    |    |  |  |  |  |

|    | 1.7.  | GMCH Graphics Support                                            |    |  |  |  |  |

|    |       | 1.7.1. Display, Digital Video Out, and LCD/Flat Panel            |    |  |  |  |  |

|    | 1.8.  | System Clocking                                                  |    |  |  |  |  |

|    | 1.9.  | References                                                       |    |  |  |  |  |

| 2. |       | l Description                                                    |    |  |  |  |  |

| ۷. | _     | •                                                                |    |  |  |  |  |

|    | 2.1.  | Host Interface Signals                                           |    |  |  |  |  |

|    | 2.2.  | System Memory Interface Signals                                  |    |  |  |  |  |

|    | 2.3.  | Display Cache Interface Signals                                  |    |  |  |  |  |

|    | 2.4.  | Hub Interface Signals                                            |    |  |  |  |  |

|    | 2.5.  | Display Interface Signals                                        |    |  |  |  |  |

|    | 2.6.  | Digital Video Output Signals/TV-Out Pins                         |    |  |  |  |  |

|    | 2.7.  | Power Signals                                                    |    |  |  |  |  |

|    | 2.8.  | Clock Signals                                                    | 23 |  |  |  |  |

|    | 2.9.  | Miscellaneous Interface Signals                                  | 24 |  |  |  |  |

|    | 2.10. | Power-Up/Reset Strap Options                                     | 24 |  |  |  |  |

| 3. | Confi | Configuration Registers                                          |    |  |  |  |  |

|    | 3.1.  | Register Nomenclature and Access Attributes                      | 25 |  |  |  |  |

|    | 3.2.  | PCI Configuration Space Access                                   | 26 |  |  |  |  |

|    |       | 3.2.1. PCI Bus Configuration Mechanism                           |    |  |  |  |  |

|    |       | 3.2.2. Logical PCI Bus #0 Configuration Mechanism                |    |  |  |  |  |

|    |       | 3.2.3. Primary PCI (PCI0) and Downstream Configuration Mechanism |    |  |  |  |  |

|    |       | 3.2.4. Internal Graphics Device Configuration Mechanism          |    |  |  |  |  |

|    | 2.2   | 3.2.5. GMCH Register Introduction                                |    |  |  |  |  |

|    | 3.3.  | I/O Mapped Registers                                             |    |  |  |  |  |

|    |       | 3.3.1. CONFIG_ADDRESS—Configuration Address Register             |    |  |  |  |  |

|    | 3.4.  | 3.3.2. CONFIG_DATA—Configuration Data Register                   |    |  |  |  |  |

|    | 5.4.  | 3.4.1. VID—Vendor Identification Register (Device 0)             |    |  |  |  |  |

|    |       | 3.4.2. DID—Device Identification Register (Device 0)             |    |  |  |  |  |

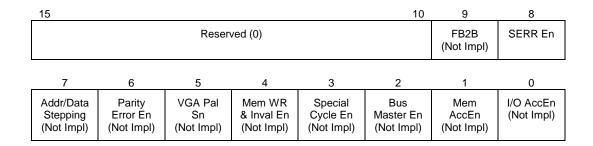

|    |       | 3.4.3. PCICMD—PCI Command Register (Device 0)                    |    |  |  |  |  |

|    |       | 3.4.4. PCISTS—PCI Status Register (Device 0)                     |    |  |  |  |  |

|    |       | 3.4.5. RID—Revision Identification Register (Device 0)           |    |  |  |  |  |

|    |       | 3.4.6. SUBC—Sub-Class Code Register (Device 0)                   |    |  |  |  |  |

|    |       | 3.4.7. BCC—Base Class Code Register (Device 0)                   |    |  |  |  |  |

|    |       | 3.4.8. MLT—Master Latency Timer Register (Device 0)              |    |  |  |  |  |

|    |       | 3.4.9. HDR—Header Type Register (Device 0)                       |    |  |  |  |  |

|    |       | 3.4.10. SVID—Subsystem Vendor Identification Register (Device 0) |    |  |  |  |  |

|    |       | 3.4.11. SID—Subsystem Identification Register (Device 0)         |    |  |  |  |  |

4.

|      | 3.4.12.       | CAPPTR—Capabilities Pointer (Device 0)                         | 36 |

|------|---------------|----------------------------------------------------------------|----|

|      | 3.4.13.       | GMCHCFG—GMCH Configuration Register (Device 0)                 | 37 |

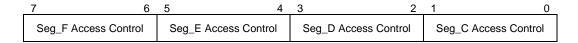

|      | 3.4.14.       | PAMR—Programmable Attributes Register (Device 0)               | 38 |

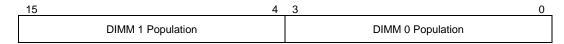

|      | 3.4.15.       | DRP—DRAM Row Population Register (Device 0)                    | 39 |

|      | 3.4.16.       | DRAMT—DRAM Timing Register (Device 0)                          |    |

|      | 3.4.17.       | FCHC—Fixed DRAM Hole Control Register (Device 0)               | 42 |

|      | 3.4.18.       | SMRAM—System Management RAM Control Register (Device 0)        |    |

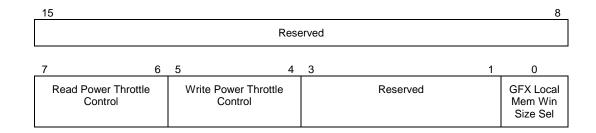

|      | 3.4.19.       | MISCC—Miscellaneous Control Register (Device 0)                |    |

|      | 3.4.20.       | MISCC2—Miscellaneous Control 2 Register (Device 0)             |    |

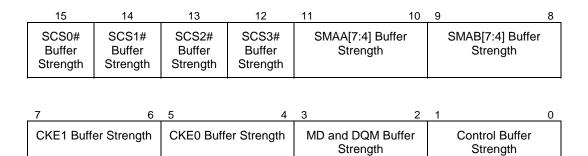

|      | 3.4.21.       | BUFF_SC—System Memory Buffer Strength Control Register (Device |    |

| 3.5. | Graphics      | Device Registers (Device 1)                                    |    |

|      | 3.5.1.        | VID—Vendor Identification Register (Device 1)                  | 50 |

|      | 3.5.2.        | DID—Device Identification Register (Device 1)                  |    |

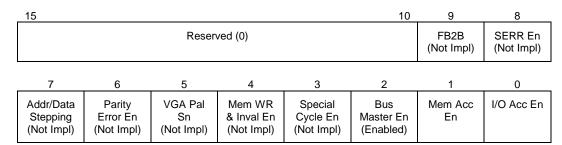

|      | 3.5.3.        | PCICMD—PCI Command Register (Device 1)                         |    |

|      | 3.5.4.        | PCISTS—PCI Status Register (Device 1)                          |    |

|      | 3.5.5.        | RID—Revision Identification Register (Device 1)                |    |

|      | 3.5.6.        | PI-Programming Interface Register (Device 1)                   |    |

|      | 3.5.7.        | SUBC1—Sub-Class Code Register (Device 1)                       | 53 |

|      | 3.5.8.        | BCC1—Base Class Code Register (Device 1)                       |    |

|      | 3.5.9.        | CLS—Cache Line Size Register (Device 1)                        |    |

|      | 3.5.10.       | MLT—Master Latency Timer Register (Device 1)                   |    |

|      | 3.5.11.       | HDR—Header Type Register (Device 1)                            |    |

|      | 3.5.12.       | BIST—Built In Self Test (BIST) Register (Device 1)             |    |

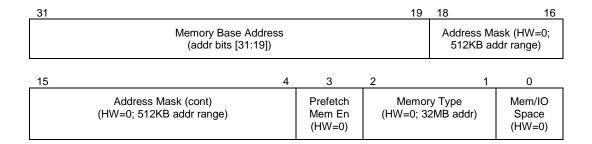

|      | 3.5.13.       | GMADR—Graphics Memory Range Address Register (Device 1)        |    |

|      | 3.5.14.       | MMADR—Memory Mapped Range Address Register (Device 1)          |    |

|      | 3.5.15.       | SVID—Subsystem Vendor Identification Register (Device 1)       |    |

|      | 3.5.16.       | SID—Subsystem Identification Register (Device 1)               |    |

|      | 3.5.17.       | ROMADR—Video BIOS ROM Base Address Registers (Device 1)        |    |

|      | 3.5.18.       | CAPPOINT—Capabilities Pointer Register (Device 1)              |    |

|      | 3.5.19.       | INTRLINE—Interrupt Line Register (Device 1)                    |    |

|      | 3.5.20.       | INTRPIN—Interrupt Pin Register (Device 1)                      |    |

|      | 3.5.21.       | MINGNT—Minimum Grant Register (Device 1)                       |    |

|      | 3.5.22.       | MAXLAT—Maximum Latency Register (Device 1)                     |    |

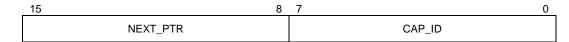

|      | 3.5.23.       | PM_CAPID—Power Management Capabilities ID Register (Device 1)  |    |

|      | 3.5.24.       | PM_CAP—Power Management Capabilities Register (Device 1)       |    |

|      | 3.5.25.       | PM_CS—Power Management Control/Status Register (Device 1)      |    |

| 3.6. |               | Cache Interface                                                |    |

|      |               | DRT—DRAM Row Type                                              |    |

|      | 3.6.2.        | DRAMCL—DRAM Control Low                                        |    |

|      | 3.6.3.        | DRAMCH—DRAM Control High                                       |    |

| 3.7. | Display C     | Cache Detect and Diagnostic Registers                          |    |

|      | 3.7.1.        | GRX—GRX Graphics Controller Index Register                     |    |

|      | 3.7.2.        | MSR—Miscellaneous Output                                       |    |

|      | 3.7.3.        | GR06—Miscellaneous Register                                    |    |

|      | 3.7.4.        | GR10—Address Mapping                                           |    |

|      | 3.7.5.        | GR11—Page Selector                                             |    |

|      |               |                                                                |    |

| Fun  | ctional Descr | iption                                                         | 69 |

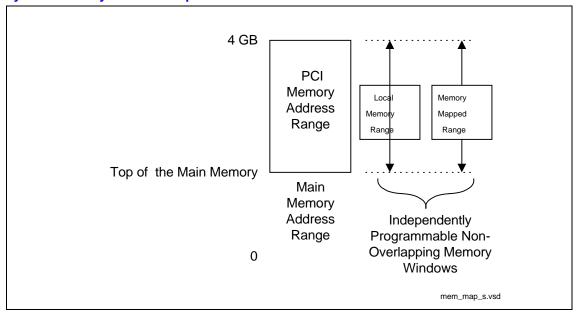

| 4.1. | System A      | Address Map                                                    | 69 |

|      | 4.1.1.        | Memory Address Ranges                                          |    |

|      | 4             | -1.1.1. Compatibility Area                                     |    |

|      | 4             | -1.1.2. Extended Memory Area                                   |    |

## intel.

|        | 4.1.1.3. System Management Mode (SMM) Memory                                                                   |     |

|--------|----------------------------------------------------------------------------------------------------------------|-----|

|        | 4.1.2. Memory Shadowing                                                                                        |     |

|        | 4.1.3. I/O Address Space                                                                                       |     |

| 4.0    | 4.1.4. GMCH Decode Rules and Cross-Bridge Address Ma                                                           |     |

| 4.2.   | Host Interface                                                                                                 |     |

|        | 4.2.1. Host Bus Device Support                                                                                 |     |

| 4.3.   | System Memory DRAM Interface                                                                                   |     |

| 4.5.   | 4.3.1. DRAM Organization and Configuration                                                                     |     |

|        | 4.3.1.1. Configuration Mechanism For DIMMs                                                                     |     |

|        | 4.3.1.2. DRAM Register Programming                                                                             |     |

|        | 4.3.2. DRAM Address Translation and Decoding                                                                   |     |

|        | 4.3.3. DRAM Array Connectivity                                                                                 |     |

|        | 4.3.4. SDRAMT Register Programming                                                                             | 85  |

|        | 4.3.5. SDRAM Paging Policy                                                                                     |     |

| 4.4.   | Intel® Dynamic Video Memory Technology (D.V.M.T.)                                                              | 86  |

| 4.5.   | Display Cache Interface                                                                                        | 86  |

|        | 4.5.1. Supported DRAM Types                                                                                    | 87  |

|        | 4.5.2. Memory Configurations                                                                                   | 87  |

|        | 4.5.3. Address Translation                                                                                     |     |

|        | 4.5.4. Display Cache Interface Timing                                                                          |     |

| 4.6.   | Internal Graphics Device                                                                                       |     |

|        | 4.6.1. 3D/2D Instruction Processing                                                                            |     |

|        | 4.6.2. 3D Engine                                                                                               |     |

|        | 4.6.3. Buffers                                                                                                 |     |

|        | 4.6.4. Setup                                                                                                   |     |

|        | 4.6.5. Texturing                                                                                               |     |

|        | <ul><li>4.6.6. 2D Operation</li><li>4.6.7. Fixed Blitter (BLT) and Stretch Blitter (STRBLT) Engineer</li></ul> |     |

|        | 4.6.7.1. Fixed BLT Engine                                                                                      |     |

|        | 4.6.7.2. Arithmetic Stretch BLT Engine                                                                         |     |

|        | 4.6.8. Hardware Motion Compensation                                                                            |     |

|        | 4.6.9. Hardware Cursor                                                                                         |     |

|        | 4.6.10. Overlay Engine                                                                                         |     |

|        | 4.6.11. Display                                                                                                |     |

|        | 4.6.12. Flat Panel Interface / 1.8V TV-Out Interface                                                           |     |

|        | 4.6.13. DDC (Display Data Channel)                                                                             |     |

| 4.7.   | System Reset for the GMCH                                                                                      |     |

| 4.8.   | System Clock Description                                                                                       | 101 |

| 4.9.   | Power Management                                                                                               | 101 |

|        | 4.9.1. Specifications Supported                                                                                |     |

| Dinout | and Package Information                                                                                        | 103 |

|        | 5                                                                                                              |     |

| 5.1.   | 82810E GMCH Pinout                                                                                             |     |

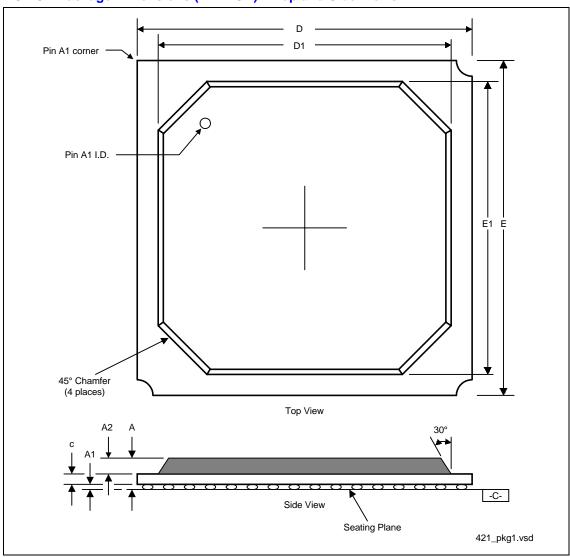

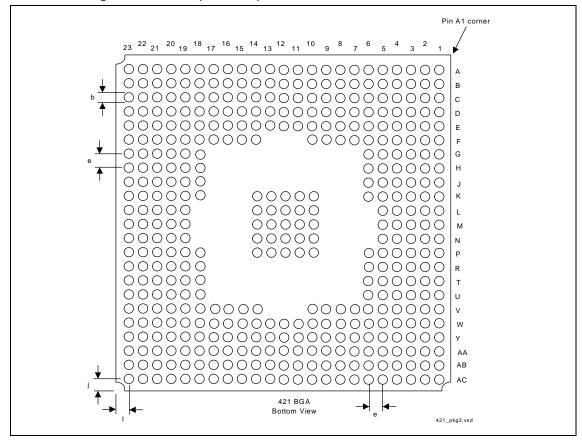

| 5.2.   | Package Dimensions                                                                                             | 109 |

| Testab | oility                                                                                                         | 111 |

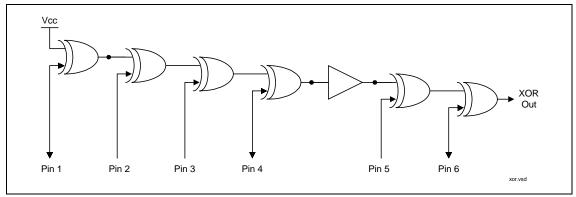

| 6.1.   | XOR TREE Testability Algorithm Example                                                                         | 112 |

|        | 6.1.1. Test Pattern Consideration for XOR Chain 7                                                              |     |

| 6.2.   | XOR Tree Initialization                                                                                        |     |

| 0.2.   |                                                                                                                |     |

| 0.2.   | 6.2.1. Chain [1:2, 4:7] Initialization                                                                         | 113 |

| 0.2.   | 6.2.1. Chain [1:2, 4:7] Initialization                                                                         |     |

5.

6.

## **Figures**

**Tables**

| @                                                                                  |      |

|------------------------------------------------------------------------------------|------|

| Figure 1. Intel® 810E Chipset System Block Diagram With Intel 82810E GMCH and ICH  | 12   |

| Figure 2. GMCH Block Diagram                                                       |      |

| Figure 3. System Memory Address Map                                                |      |

| Figure 4. Detailed Memory System Address Map                                       |      |

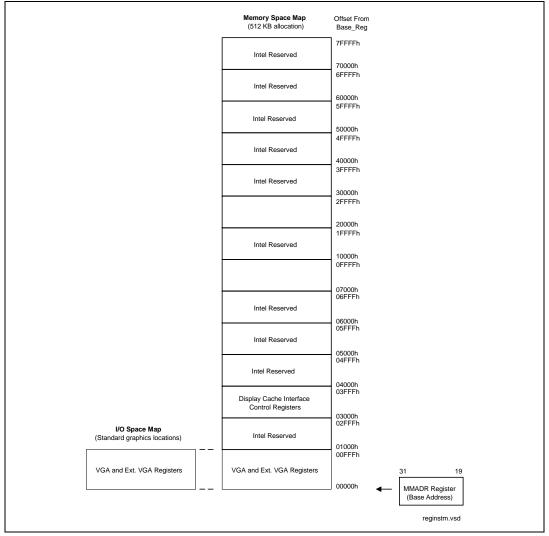

| Figure 5 GMCH's Graphics Register Memory Address Space                             | 74   |

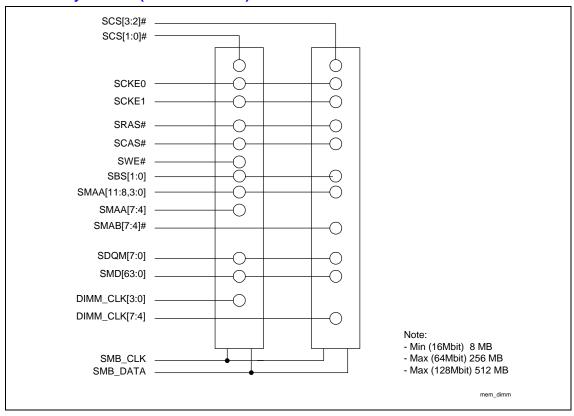

| Figure 6. DRAM Array Sockets (2 DIMM Sockets)                                      |      |

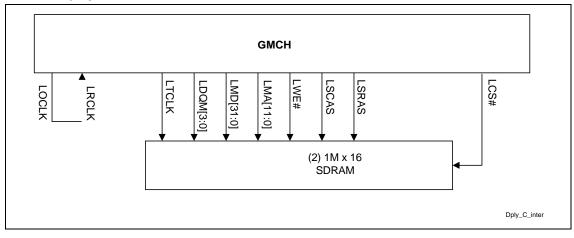

| Figure 7. GMCH Display Cache Interface to 4 MB                                     |      |

| Figure 8. 3D/2D Pipeline Preprocessor                                              | 89   |

| Figure 9. Data Flow for the 3D Pipeline                                            | 91   |

| Figure 10. GMCH Pinout (Top View—Left Side)                                        |      |

| Figure 11. GMCH Pinout (Top View—Right Side)                                       | 105  |

| Figure 12. GMCH Package Dimensions (421 BGA) – Top and Side Views                  |      |

| Figure 13. GMCH Package Dimensions (421 BGA) – Bottom View                         |      |

| Figure 14. XOR Tree Implementation                                                 | 111  |

|                                                                                    |      |

|                                                                                    |      |

|                                                                                    |      |

| Table 1. Power Up Options                                                          | 24   |

| Table 1. Fower op Options                                                          |      |

| Table 3. GMCH PCI Configuration Space (Device 0)                                   | 24   |

| Table 4. Programming DRAM Row Population Register Fields                           |      |

| Table 5. GMCH Configuration Space (Device 1)                                       | 40   |

|                                                                                    |      |

| Table 6 Memory Mapped Registers  Table 7. Memory Segments and their Attributes     | 02   |

| Table 8. Summay of Transactions Supported By GMCH                                  | / 2  |

| Table 9. Host Responses Supported by the GMCH                                      |      |

|                                                                                    |      |

| Table 10. Special Cycles                                                           |      |

| Table 11. Sample Of Possible Mix And Match Options For 4 Row/2 DIMM Configurations |      |

| Table 12. Data Bytes on DIMM Used for Programming DRAM Registers                   | 83   |

| Table 13. GMCH DRAM Address Mux Function                                           |      |

| Table 14. Programmable SDRAM Timing Parameters                                     |      |

| Table 15. Memory Size for Each Configuration                                       |      |

| Table 16. Partial List of Display Modes Supported                                  |      |

| Table 17. Partial List of Flat Panel Modes Supported                               |      |

| Table 18. Partial List of TV-Out Modes Supported                                   |      |

| Table 19. Alphabetical Pin Assignment                                              |      |

| Table 20. GMCH Package Dimensions (421 BGA)                                        | 110  |

| Table 21. XOR Test Pattern Example                                                 | 112  |

| Table 22. XOR Chain 1                                                              |      |

| Table 23. XOR Chain 2                                                              |      |

| Table 24. XOR Chain 3                                                              |      |

| Table 25. XOR Chain 4                                                              |      |

| Table 26. XOR Chain 5                                                              |      |

| Table 27. XOR Chain 6                                                              | .118 |

6 Datasheet

## **Revision History**

| Rev. | Description                                                                                                                        | Date           |

|------|------------------------------------------------------------------------------------------------------------------------------------|----------------|

| -001 | Initial Release                                                                                                                    | September 1999 |

| -002 | Added Table 17, "Overlay Modes Supported"                                                                                          | September 2000 |

|      | Added Section 4.9.2, "Resume From S3"                                                                                              |                |

|      | Updated BUFF_SC Register description (see Section 3.4.21, "BUFF_SC—<br>System Memory Buffer Strength Control Register (Device 0)") |                |

|      | Editorial changes throughout for clarity                                                                                           |                |

## Intel® 82810E GMCH

#### **Product Features**

- Processor/Host Bus Support

- Optimized for the Intel<sup>®</sup> Pentium® II processor, Intel<sup>®</sup> Pentium® III processor, and Intel<sup>®</sup> Celeron<sup>TM</sup> processor

- Supports processor 370-Pin Socket and SC242 connectors

- Supports 32-Bit System Bus Addressing

- 4 deep in-order queue; 4 or 1 deep request queue

- Supports Uni-processor systems only

- In-order and Dynamic Deferred Transaction Support

- 66/100/133 MHz System Bus Frequency

- AGTL+ I/O Buffer

- Integrated DRAM Controller

- 8 MB to 256 MB using 16Mb/64Mb technology (512 MB using 128Mb technology)

- Supports up to 2 double sided DIMM modules

- 64-bit data interface

- 100 MHz system memory bus frequency

- Support for Asymmetrical DRAM addressing only

- Support for x8, x16 and x32 DRAM device width

- Refresh Mechanism: CBR ONLY supported

- Enhanced Open page Arbitration SDRAM paging scheme

- Suspend to RAM support

- Integrated Graphics Controller

- 3D Hyper Pipelined Architecture

- - Parallel Data Processing (PDP)

- Precise Pixel Interpolation (PPI)

- Full 2D H/W Acceleration

- Motion Video Acceleration

- 3D Graphics Visual Enhancements

- Flat & Gouraud Shading

- Mip Maps with Bilinear and Anisotropic Filtering

- Fogging Atmospheric Effects

- Z Buffering

- 3D Pipe 2D Clipping

- Backface Culling

- 3D Graphics Texturing Enhancements

- Per Pixel Perspective Correction Texture Mapping

- Texture Compositing

- Texture Color Keying/Chroma Keying

- Digital Video Output

- 85 MHz Flat Panel Monitor Interface Or Digital Video Output for use with a external TV encoder

- Display

- Integrated 24-bit 230 MHz RAMDAC

- Gamma Corrected Video

- DDC2B Compliant

- 2D Graphics

- Up to 1600x1200 in 8-bit Color at 75 Hz Refresh

- Hardware Accelerated Functions

- 3 Operand Raster BitBLTs

- 64x64x3 Color Transparent Cursor

- Arithmetic Stretch Blitter Video

- H/W Motion Compensation Assistance for S/W MPEG2 Decode

- Software DVD at 30 fps

- Digital Video Out Port

- NTSC and PAL TV Out Support

- H/W Overlay Engine with Bilinear Filtering

- Independent gamma correction, saturation, brightness & contrast for overlay

- Integrated Graphics Memory Controller

- Intel<sup>®</sup> D.V.M. Technology

- Display Cache Interface

- 32-bit data interface

- 100/133 MHz SDRAM interface

- Support for 1Mx16, (4 MB Only)

- Arbitration Scheme and Concurrency

- Centralized Arbitration Model for Optimum Concurrency Support

- Concurrent operations of processor and system busses supported via dedicated arbitration and data buffering

- Data Buffering

- Distributed Data Buffering Model for optimum concurrency

- DRAM Write Buffer with read-around-write capability

- Dedicated processor -DRAM, hub interface-DRAM and Graphics-DRAM Read Buffers

- Power Management Functions

- SMRAM space remapping to A0000h (128 KB)

- Optional Extended SMRAM space above 256 MB, additional 512K/1MB TSEG from Top of Memory, cacheable

- Stop Clock Grant and Halt special cycle translation from the host to the hub interface

- ACPI Compliant power management

- APIC Buffer Management

- SMI, SCI, and SERR error indication

- Supporting I/O Bridge

- 241 Pin BGA I/O Controller Hub ICH

- Packaging/Power

- --- 421 BGA

- —1.8V core with 3.3V CMOS I/O

## intel.

intel

This page is intentionally left blank.

## 1. Overview

The Intel<sup>®</sup> 810E chipset is a high-integration chipset designed for the basic graphics/multimedia PC platform. The chipset consists of a Graphics and Memory Controller Hub (GMCH) Host Bridge and an I/O Controller Hub (ICH) Bridge for the I/O subsystem. The GMCH integrates a system memory DRAM controller that supports a 64-bit 100 MHz DRAM array. The DRAM controller is optimized for maximum efficiency.

The 82810E integrates a Display Cache DRAM controller that supports a 4 MB, 32-bit 100/133 MHz DRAM array for enhanced 2D and 3D performance.

Note: In this document the term "GMCH" refers to the 82810E, unless otherwise specified.

The Intel<sup>®</sup> 810E chipset may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

## 1.1. The Intel® 810E Chipset System

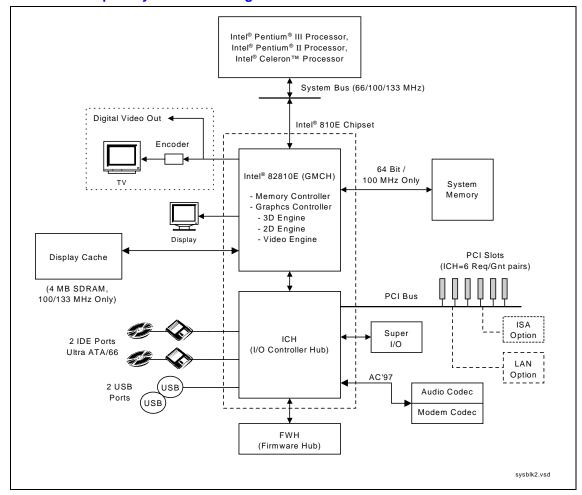

The Intel<sup>®</sup> 810E Chipset uses a hub architecture with the GMCH as the host bridge hub and the 82801AA I/O Controller Hub (ICH) as the I/O hub. The ICH is a highly integrated multifunctional I/O Controller Hub that provides the interface to the PCI Bus and integrates many of the functions needed in today's PC platforms. The GMCH and ICH communicate over a dedicated hub interface.

82801AA (ICH) functions and capabilities include:

- PCI Rev 2.2 compliant with support for 33 MHz PCI operations

- ICH supports up to 6 Req/Gnt pairs (PCI Slots)

- Power Management Logic Support

- Enhanced DMA Controller, Interrupt Controller & Timer Functions

- Integrated IDE controller; ICH supports Ultra ATA/66

- USB host interface with support for 2 USB ports

- System Management Bus (SMBus) compatible with most I<sup>2</sup>C devices

- AC'97 2.1 Compliant Link for Audio and Telephony CODECs

- Low Pin Count (LPC) interface

- Firmware Hub (FWH) interface support

- Alert On LAN\*

Figure 1 shows a block diagram of a typical platform based on the  $Intel^{@}$  810E Chipset. The GMCH supports processor bus frequencies of 66/100/133 MHz.

Figure 1. Intel® 810E Chipset System Block Diagram With Intel 82810E GMCH and ICH

## intel.

#### 1.2. GMCH Overview

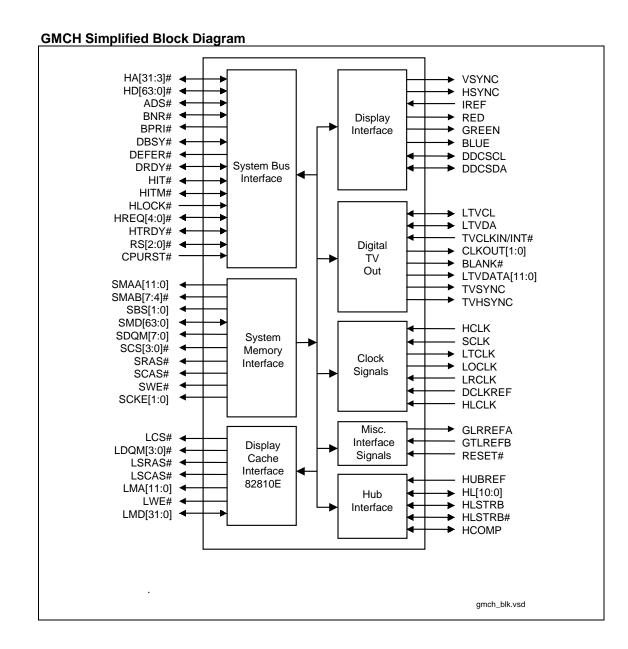

Figure 2 is a block diagram of the GMCH illustrating the various interfaces and integrated components of the GMCH chip. The GMCH functions and capabilities include:

- Support for a single processor configuration

- 64-bit AGTL+ based System Bus Interface at 66 MHz / 100 MHz / 133 MHz

- 32-bit Host Address Support

- 64-bit System Memory Interface with optimized support for SDRAM at 100 MHz

- Integrated 2D and 3D Graphics Engines

- Integrated H/W Motion Compensation Engine

- Integrated 230 MHz DAC

- Integrated Digital Video Out Port

- 4 MB Display Cache

Figure 2. GMCH Block Diagram

#### 1.3. Host Interface

The host interface of the GMCH is optimized to support the Intel<sup>®</sup> Pentium<sup>®</sup> III processor, Intel<sup>®</sup> Pentium<sup>®</sup> II processor, and Intel<sup>®</sup> Celeron<sup>TM</sup> processor. The GMCH implements the host address, control, and data bus interfaces within a single device. The GMCH supports a 4-deep in-order queue (i.e., supports pipelining of up to 4 outstanding transaction requests on the host bus). Host bus addresses are decoded by the GMCH for accesses to system memory, PCI memory and PCI I/O (via hub interface), PCI configuration space and Graphics memory. The GMCH takes advantage of the pipelined addressing capability of the processor to improve the overall system performance.

The GMCH supports the 370-pin socket and SC242 processor connectors.

- **370-pin socket** (PGA370). The zero insertion force (ZIF) socket that a processor in the PPGA package will use to interface with a system board.

- SC242—242-contact slot connector. A processor in a Single-Edge Processor Package (SEPP) or Single-Edge Contact Cartidge (SECC and SECC2) use this connector to interface with a system board.

### 1.4. System Memory Interface

The GMCH integrates a system memory DRAM controller that supports a 64-bit 100 MHz DRAM array. The DRAM type supported is industry standard Synchronous DRAM (SDRAM). The DRAM controller interface is fully configurable through a set of control registers. Complete descriptions of these registers are given in the Chapter 3, "Configuration Registers".

The GMCH supports industry standard 64-bit wide DIMM modules with SDRAM devices. The twelve multiplexed address lines, SMAA[11:0], along with the two bank select lines, SBS[1:0], allow the GMCH to support 2M, 4M, 8M, and 16M x64 DIMMs. Only asymmetric addressing is supported. The GMCH has four SCS# lines, enabling the support of up to four 64-bit rows of DRAM. The GMCH targets SDRAM with CL2 and CL3 and supports both single and double-sided DIMMs. Additionally, the GMCH also provides a seven deep refresh queue. The GMCH can be configured to keep multiple pages open within the memory array, pages can be kept open in any one row of memory.

SCKE[1:0] is used in configurations requiring powerdown mode for the SDRAM.

### 1.5. Display Cache Interface

The 82810E GMCH supports a Display Cache DRAM controller with a 32-bit 100/133 MHz DRAM array. The DRAM type supported is industry standard Synchronous DRAM (SDRAM) like that of the system memory. The local memory DRAM controller interface is fully configurable through a set of control registers. Complete descriptions of these registers are given in Chapter 3, "Configuration Registers".

### 1.6. Hub Interface

The hub interface is a private interconnect between the GMCH and the ICH.

## 1.7. GMCH Graphics Support

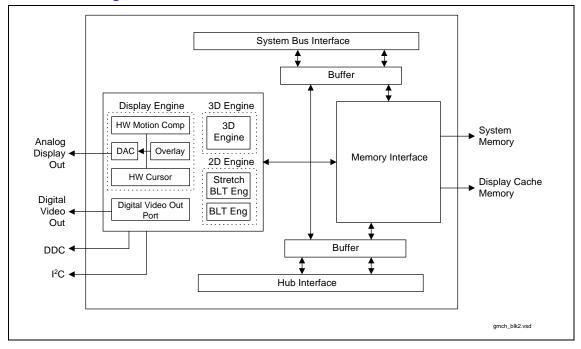

The Graphics and Memory Controller Hub (GMCH) includes a highly integrated graphics accelerator. Its architecture consists of dedicated multi-media engines executing in parallel to deliver high performance 3D, 2D and motion compensation video capabilities. The 3D and 2D engines are managed by a 3D/2D pipeline preprocessor allowing a sustained flow of graphics data to be rendered and displayed. The deeply pipelined 3D accelerator engine provides 3D graphics quality and performance via per-pixel 3D rendering and parallel data paths that allow each pipeline stage to simultaneously operate on different primitives or portions of the same primitive. The GMCH graphics accelerator engine supports perspective-correct texture mapping, bilinear and anisotropic Mip-Mapping, Gouraud shading, alphablending, fogging and Z-buffering. A rich set of 3D instructions permit these features to be independently enabled or disabled.

For the 82810E, a Display Cache (DC) can be used for Z-buffers (Textures and display buffer are located in system memory). If the display cache is not used, the Z-buffer is located in system memory.

The GMCH integrated graphics accelerator's 2D capabilities include BLT and arithmetic STRBLT engines, a hardware cursor and an extensive set of 2D registers and instructions. The high performance 64-bit BitBLT engine provides hardware acceleration for many common Windows operations.

In addition to its 2D/3D capabilities, the GMCH integrated graphics accelerator also supports full MPEG-2 motion compensation for software-assisted DVD video playback, a VESA DDC2B compliant display interface and a digital video out port that may support (via an external video encoder) NTSC and PAL broadcast standards.

#### 1.7.1. Display, Digital Video Out, and LCD/Flat Panel

The GMCH provides interfaces to a standard progressive scan monitor, TV-Out device, and LCD/Flat Panel transmitter.

- The GMCH directly drives a standard progressive scan monitor up to a resolution of 1600x1200.

- The GMCH provides a Digital Video Out interface to connect an external device to drive an autodetection of 1024x768 non-scalar DDP digital Flat Panel with appropriate EDID 1.x data. The interface has 1.8V signaling to allow it to operate at higher frequencies. This interface can also connect to a 1.8V TV-Out encoder.

## 1.8. System Clocking

The GMCH has a new type of clocking architecture. It has integrated SDRAM buffers that always run at 100 MHz, regardless of system bus frequency. The system bus frequency is selectable between 66 MHz, 100 MHz, or 133 MHz. The GMCH uses a copy of the USB clock as the DOT Clock input for the graphics pixel clock PLL.

#### 1.9. References

- Intel® 810E Chipset Design Guide. Contact your field sales representative.

- PC '99: Contact www.microsoft.com/hwdev

- AGTL+ I/O Specification: Contained in the Intel® Pentium® II Processor Databook

- PCI Local bus Specification 2.2: Contact www.pcisig.com

- Intel® 82801AA (ICH) I/O Controller Hub Datasheet

## 2. Signal Description

This section provides a detailed description of the GMCH signals. The signals are arranged in functional groups according to their associated interface. The states of all of the signals during reset are provided in the System Reset section.

The "#" symbol at the end of a signal name indicates that the active, or asserted state occurs when the signal is at a low voltage level. When "#" is not present after the signal name the signal is asserted when at the high voltage level.

The following notations are used to describe the signal type:

I Input pin

O Output pin

I/OD Input / Open Drain Output pin. This pin requires a pullup to the VCC of the processor

core

I/O Bi-directional Input/Output pin

The signal description also includes the type of buffer used for the particular signal:

**AGTL+** Open Drain AGTL+ interface signal. Refer to the AGTL+ I/O Specification for

complete details

**CMOS** The CMOS buffers are Low Voltage TTL compatible signals. These are 3.3V only.

**LVTTL** Low Voltage TTL compatible signals. There are 3.3V only.

**1.8V** 1.8V signals for the digital video interface

**Analog** Analog CRT Signals

Note that the processor address and data bus signals (Host Interface) are logically inverted signals (i.e., the actual values are inverted of what appears on the processor bus). This must be taken into account and the addresses and data bus signals must be inverted inside the GMCH. All processor control signals follow normal convention. A 0 indicates an active level (low voltage) if the signal is followed by # symbol and a 1 indicates an active level (high voltage) if the signal has no # suffix.

## 2.1. Host Interface Signals

| Signal Name | Туре         | Description                                                                                                                                                                                                                                                                                                                      |  |

|-------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CPURST#     | O<br>AGTL+   | <b>CPU Reset.</b> The GMCH asserts CPURST# while RESET# (PCIRST# from ICH) is asserted and for approximately 1 ms after RESET# is deasserted. The GMCH also pulses CPURST# for approximately 1ms when requested via a hub interface special cycle. The CPURST# allows the processor to begin execution in a known state.         |  |

| HA[31:3]#   | I/O<br>AGTL+ | Host Address Bus: HA[31:3]# connect to the processor address bus. During processor cycles, HA[31:3]# are inputs. The GMCH drives HA[31:3]# during snoop cycles on behalf of Primary PCI. Note that the address bus is inverted on the processor bus.                                                                             |  |

| HD[63:0]#   | I/O<br>AGTL+ | <b>Host Data:</b> These signals are connected to the processor data bus. Note that the data signals are inverted on the processor bus.                                                                                                                                                                                           |  |

| ADS#        | I/O<br>AGTL+ | <b>Address Strobe:</b> The processor bus owner asserts ADS# to indicate the first of two cycles of a <i>request phase</i> .                                                                                                                                                                                                      |  |

| BNR#        | I/O<br>AGTL+ | <b>Block Next Request:</b> Used to block the current request bus owner from issuing a new request. This signal is used to dynamically control the processor bus pipeline depth.                                                                                                                                                  |  |

| BPRI#       | O<br>AGTL+   | Priority Agent Bus Request: The GMCH is the only Priority Agent on the processor bus. It asserts this signal to obtain the ownership of the address bus. This signal has priority over symmetric bus requests and will cause the current symmetric owner to stop issuing new transactions unless the HLOCK# signal was asserted. |  |

| DBSY#       | I/O<br>AGTL+ | <b>Data Bus Busy:</b> Used by the data bus owner to hold the data bus for transfers requiring more than one cycle.                                                                                                                                                                                                               |  |

| DEFER#      | O<br>AGTL+   | <b>Defer:</b> The GMCH generates a deferred response as defined by the rules of the GMCH dynamic defer policy. The GMCH also uses the DEFER# signal to indicate a processor retry response.                                                                                                                                      |  |

| DRDY#       | I/O<br>AGTL+ | Data Ready: Asserted for each cycle that data is transferred.                                                                                                                                                                                                                                                                    |  |

| HIT#        | I/O<br>AGTL+ | <b>Hit:</b> Indicates that a caching agent holds an unmodified version of the requested line. Also driven in conjunction with HITM# by the target to extend the snoop window.                                                                                                                                                    |  |

| HITM#       | I/O<br>AGTL+ | Hit Modified: Indicates that a caching agent holds a modified version of the requested line and that this agent assumes responsibility for providing the line. HITM# is also driven in conjunction with HIT# to extend the snoop window.                                                                                         |  |

| HLOCK#      | I<br>AGTL+   | Host Lock: All processor bus cycles sampled with the assertion of HLOCK# and ADS#, until the negation of HLOCK# must be atomic (i.e., no hub interface or GMCH graphics snoopable access to DRAM is allowed when HLOCK# is asserted by the processor).                                                                           |  |

| HREQ[4:0]#  | I/O<br>AGTL+ | Host Request Command: Asserted during both clocks of request phase. In the first clock, the signals define the transaction type to a level of detail that is sufficient to begin a snoop request. In the second clock, the signals carry additional information to define the complete transaction type.                         |  |

|             |              | The transactions supported by the GMCH are defined in Section 4.21, "Host Interface".                                                                                                                                                                                                                                            |  |

| HTRDY#      | I/O<br>AGTL+ | <b>Host Target Ready:</b> Indicates that the target of the processor transaction is able to enter the data transfer phase.                                                                                                                                                                                                       |  |

| Signal Name | Туре  |          | Description                                           |

|-------------|-------|----------|-------------------------------------------------------|

| RS[2:0]#    | I/O   | Response | e Signals: Indicates type of response as shown below: |

|             | AGTL+ | RS[2:0]  | Response type                                         |

|             |       | 000      | Idle state                                            |

|             |       | 001      | Retry response                                        |

|             |       | 010      | Deferred response                                     |

|             |       | 011      | Reserved (not driven by the GMCH)                     |

|             |       | 100      | Hard Failure (not driven by the GMCH)                 |

|             |       | 101      | No data response                                      |

|             |       | 110      | Implicit Writeback                                    |

|             |       | 111      | Normal data response                                  |

## 2.2. System Memory Interface Signals

| Signal Name                          | Туре        | Description                                                                                                                                                         |

|--------------------------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMAA[11:0]<br>SMAB[7:4]#<br>SBS[1:0] | O<br>CMOS   | <b>Memory Address:</b> SMAA[11:0] and SMAB[7:4]# are used to provide the multiplexed row and column address to DRAM. SBS[1:0] provide the Bank Select.              |

| SMD[63:0]                            | I/O<br>CMOS | Memory Data: These signals are used to interface to the DRAM data bus.                                                                                              |

| SDQM[7:0]                            | O<br>CMOS   | Input/Output Data Mask: These pins act as synchronized output enables during read cycles and as a byte enables during write cycles.                                 |

| SCS[3:0]#                            | O<br>CMOS   | <b>Chip Select:</b> For the memory row configured with SDRAM, these pins perform the function of selecting the particular SDRAM components during the active state. |

| SRAS#                                | O<br>CMOS   | SDRAM Row Address Strobe: These signals drive the SDRAM array directly without any external buffers.                                                                |

| SCAS#                                | O<br>CMOS   | SDRAM Column Address Strobe: These signals drive the SDRAM array directly without any external buffers.                                                             |

| SWE#                                 | O<br>CMOS   | Write Enable Signal: SWE# is asserted during writes to DRAM.                                                                                                        |

| SCKE[1:0]                            | O<br>CMOS   | System Memory Clock Enable: SCKE SDRAM Clock Enable is used to signal a self-refresh or power-down command to an SDRAM array when entering system suspend.          |

## 2.3. Display Cache Interface Signals

| Signal Name | Туре        | Description                                                                                                                                                                                                                                 |

|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LCS#        | O<br>CMOS   | Chip Select: For the memory row configured with SDRAM, these pins perform the function of selecting the particular SDRAM components during the active state.                                                                                |

| LDQM[3:0]   | O<br>CMOS   | Input/Output Data Mask: These pins control the memory array and act as synchronized output enables during read cycles and as a byte enables during write cycles.                                                                            |

| LSRAS#      | O<br>CMOS   | SDRAM Row Address Strobe: The LSRAS# signal is used to generate SDRAM Command encoded on LSRAS#/LSCAS#/LWE# signals. When LRAS# is sampled active at the rising edge of the SDRAM clock, the row address is latched into the SDRAMs.        |

| LSCAS#      | O<br>CMOS   | SDRAM Column Address Strobe: The LSCAS# signal is used to generate SDRAM Command encoded on LSRAS#/LSCAS#/LWE# signals. When LSCAS# is sampled active at the rising edge of the SDRAM clock, the column address is latched into the SDRAMs. |

| LMA[11:0]   | O<br>CMOS   | Memory Address: LMA[11:0] is used to provide the multiplexed row and column address to DRAM.                                                                                                                                                |

| LWE#        | O<br>CMOS   | Write Enable Signal: LWE# is asserted during writes to DRAM.                                                                                                                                                                                |

| LMD[31:0]   | I/O<br>CMOS | <b>Memory Data:</b> These signals are used to interface to the DRAM data bus of DRAM array.                                                                                                                                                 |

## 2.4. Hub Interface Signals

| Signal Name | Туре     | Description                                                                                               |

|-------------|----------|-----------------------------------------------------------------------------------------------------------|

| HL[10:0]    | I/O      | Hub Interface Signals: Signals used for the hub interface.                                                |

| HLSTRB      | I/O      | Packet Strobe: One of two differential strobe signals used to transmit or receive packet data.            |

| HLSTRB#     | I/O      | Packet Strobe Compliment: One of two differential strobe signals used to transmit or receive packet data. |

| HUBREF      | l<br>Ref | HUB reference: Sets the differential voltage reference for the hub interface.                             |

| HCOMP       | I/O      | Hub Compensation Pad: Used to calibrate the hub interface buffers.                                        |

## 2.5. Display Interface Signals

| Signal Name | Туре         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSYNC       | O<br>3.3V    | <b>CRT Vertical Synchronization:</b> This signal is used as the vertical sync (polarity is programmable) or "Vsync Interval".                                                                                                                                                                                                                                                                                                                                                 |

| HSYNC       | O<br>3.3V    | <b>CRT Horizontal Synchronization:</b> This signal is used as the horizontal sync (polarity is programmable) or "Hsync Interval".                                                                                                                                                                                                                                                                                                                                             |

| IWASTE      | l<br>Ref     | Waste Reference: This signal must be tied to ground.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IREF        | l<br>Ref     | Set pointer resistor for the internal color palette DAC: A 174 ohm 1% resistor is recommended                                                                                                                                                                                                                                                                                                                                                                                 |

| RED         | O<br>Analog  | <b>CRT Analog video output from the internal color palette DAC:</b> The DAC is designed for a 37.5 ohm equivalent load on each pin (e.g. 75 ohm resistor on the board, in parallel with the 75 ohm CRT load)                                                                                                                                                                                                                                                                  |

| GREEN       | O<br>Analog  | <b>CRT Analog video output from the internal color palette DAC:</b> The DAC is designed for a 37.5 ohm equivalent load on each pin (e.g., 75 ohm resistor on the board, in parallel with the 75 ohm CRT load)                                                                                                                                                                                                                                                                 |

| BLUE        | O<br>Analog  | CRT Analog video output from the internal color palette DAC: The DAC is designed for a 37.5 ohm equivalent load on each pin (e.g., 75 ohm resistor on the board, in parallel with the 75 ohm CRT load)                                                                                                                                                                                                                                                                        |

| DDCSCL      | I/OD<br>CMOS | CRT Monitor DDC Interface Clock: (Also referred to as VESA <sup>TM</sup> "Display Data Channel", also referred to as the "Monitor Plug-n-Play" interface.) For DDC1, DDCSCL and DDCSDA provides a unidirectional channel for Extended Display ID. For DDC2, DDCSCL and DDCSDA it can be used to establish a bi-directional channel based on I <sup>2</sup> C protocol. The host can request Extended Display ID or Video Display Interface information over the DDC2 channel. |

| DDCSDA      | I/OD<br>CMOS | CRT Monitor DDC Interface Data:                                                                                                                                                                                                                                                                                                                                                                                                                                               |

## 2.6. Digital Video Output Signals/TV-Out Pins

| Signal Name   | Туре         | Description                                                                                                                                                                                                                                                                                                                                                             |

|---------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TVCLKIN/INT#  | I<br>1.8V    | Low Voltage TV Clock In (TV-Out Mode): In 1.8V TV-Out usage, the TVCLKIN pin functions as a pixel clock input to the GMCH from the TV encoder. The TVCLKIN frequency ranges from 20 MHz to 40 MHz depending on the mode (e.g., NTSC or PAL) and the overscan compensation values in the TV Encoder. CLKIN has a worse case duty cycle of 60%/40% coming in to the GMCH. |

|               |              | Flat Panel Interrupt (LCD Mode): In Flat Panel usage, the INT# pin is asserted to cause an interrupt (typically, to indicate a hot plug or unplug of a flat panel). In Flat Panel usage, this pin is connected internally to a pull-up resistor.                                                                                                                        |

| CLKOUT[1:0]   | O<br>1.8V    | LCD/TV Port Clock Out: These pins provide a differential pair reference clock that can run up to 85 MHz.                                                                                                                                                                                                                                                                |

| BLANK#        | O<br>1.8V    | Flicker Blank or Border Period Indication: BLANK# is a programmable output pin driven by the graphics control. When programmed as a blank period indication, this pin indicates active pixels excluding the border. When programmed as a border period indication, this pin indicates active pixel including the border pixels.                                         |

| LTVDATA[11:0] | O<br>1.8V    | LCD/TV Data: These signals are used to interface to the LCD/TV-out data bus.                                                                                                                                                                                                                                                                                            |

| TVVSYNC       | O<br>1.8V    | Vertical Sync: VSYNC signal for the LTV interface. The active polarity of the signal is programmable.                                                                                                                                                                                                                                                                   |

| TVHSYNC       | O<br>1.8V    | <b>Horizontal Sync:</b> HSYNC signal for the LTV interface. The active polarity of the signal is programmable.                                                                                                                                                                                                                                                          |

| LTVCL         | I/OD<br>CMOS | LCD/TV Clock: Clock pin for 2-wire interface.                                                                                                                                                                                                                                                                                                                           |

| LTVDA         | I/OD<br>CMOS | LCD/TV Data: Data pin for 2-wire interface.                                                                                                                                                                                                                                                                                                                             |

## 2.7. Power Signals

| Signal Name | Туре  | Description                                                                         |

|-------------|-------|-------------------------------------------------------------------------------------|

| V_1.8       | Power | Core Power (1.8V)                                                                   |

| V_3.3       | Power | I/O Buffer Power (3.3V)                                                             |

| VSUS_3.3    | Power | System Memory Buffer Power (Separate 3.3V power plane for power down modes)         |

| VCCDA       | Power | Display Power Signal (Connect to an isolated 1.8V plane with VCCDACA1 and VCCDACA2) |

| VCCDACA1    | Power | Display Power Signal (Connect to an isolated 1.8V plane with VCCDA and VCCDACA2)    |

| VCCHA       | Power | Isolated 1.8V Power                                                                 |

| VCCBA       | Power | Isolated 1.8V Power                                                                 |

| VCCDACA2    | Power | Display Power Signal (Connect to an isolated 1.8V plane with VCCDA and VCCDACA1)    |

| VSSDA       | Power | Display Ground Signal                                                               |

| VSSDACA     | Power | Display Ground Signal                                                               |

| VSS         | Power | Core Ground                                                                         |

## 2.8. Clock Signals

| Signal Name | Туре      | Description                                                                                                                                           |  |

|-------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| HCLK        | I<br>CMOS | Host Clock Input: Clock used on the host interface. Externally generated 66/100/133 MHz clock.                                                        |  |

| SCLK        | I<br>CMOS | System Memory Clock: Clock used on the output buffers of system memory. Externally generated 100 MHz clock.                                           |  |

| LTCLK       | O<br>CMOS | <b>Transmit Clock:</b> LTCLK is an internally generated local memory clock used to clock the input buffers of the SDRAM devices of the display cache. |  |

| LOCLK       | O<br>CMOS | Output Clock: LOCLK is an internally generated clock used to drive LRCLK.                                                                             |  |

| LRCLK       | I<br>CMOS | <b>Receive Clock:</b> LRCLK is a display cache clock used to clock the input buffers of the GMCH.                                                     |  |

| DCLKREF     | I<br>CMOS | <b>Display Interface Clock:</b> DCLKREF is a 48 MHz clock generated by an external clock synthesizer to the GMCH.                                     |  |

| HLCLK       | I<br>CMOS | <b>Hub Interface Clock:</b> 66 MHz hub interface clock generated by an external clock synthesizer.                                                    |  |

## 2.9. Miscellaneous Interface Signals

| Signal Name | Туре     | Description                                                     |

|-------------|----------|-----------------------------------------------------------------|

| GTLREFA     | I<br>Ref | AGTL Reference Voltage: Reference signal to the Host Interface. |

| GTLREFB     | l<br>Ref | AGTL Reference Voltage: Reference signal to the Host Interface. |

| RESET#      | I        | Global Reset: Driven by the ICH/ICH0 when PCIRST# is active.    |

## 2.10. Power-Up/Reset Strap Options

Table 1 list power-up options that are loaded into the 82810E GMCH during cold reset.

**Table 1. Power Up Options**

| Signal  | Description                                                                                                                                                                                                  |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LMD[31] | XOR Chain Test Select: LMD[31] is set to 0 for normal operation. It must be set to 1 to enter XOR tree mode during reset. This signal must remain 1 during the entire XOR tree test.                         |

| LMD[30] | ALL Z select: If LMD[30] is set to 1, it will tri-state all signals during reset. For normal operation, LMD[30] should be set to 0.                                                                          |

| LMD[29] | <b>Host Frequency Select:</b> If LMD[13] is 0 and LMD[29] is set to 0 during reset, the host bus frequency is 66 MHz. If LMD[13] is 0 and LMD[29] is set to 1, the host bus frequency is 100 MHz.            |

| LMD[28] | In-Order Queue Depth Status: The value on LMD[28] sampled at the rising edge of CPURST# reflects if the IOQD is set to 1 or 4. If LMD[28] is set to 0, the IOQD is 4. If LMD[28] is set to 1, the IOQD is 1. |

| LMD[13] | Host Frequency Select: If LMD[13] is a 0, LMD[29] determines host bus frequency. If LMD[13] is a 1, host bus frequency is 133 MHz.                                                                           |

**Table 2. Host Frequency Strappings**

| LMD[13] | LMD[29] | Host Bus Frequency |

|---------|---------|--------------------|

| 0       | 0       | 66 MHz             |

| 0       | 1       | 100 MHz            |

| 1       | Х       | 133 MHz            |

## 3. Configuration Registers

This section describes the following register sets:

- PCI Configuration Registers . The GMCH contains PCI configuration registers for Device 0 (Hosthub interface Bridge/DRAM Controller) and Device 1 (GMCH internal graphics device).

- Display Cache Interface Registers. This register set is used for configuration of the Display Cache (DC) interface. The registers are located in memory space. The memory space addresses listed are offsets from the base memory address programmed into the MMADR register (Device 1, PCI configuration offset 14h).

- Display Cache Detect and Diagnostic Registers. This register set can be used for DC memory detection and testing. These registers are accessed via either I/O space or memory space. The memory space addresses listed are offsets from the base memory address programmed into the MMADR register (Device 1, PCI configuration offset 14h).

Note that the GMCH also contains an extensive set of registers and instructions for controlling its graphics operations. Intel graphics drivers provide the software interface at this architectural level. The register/instruction interface is transparent at the Application Programmers Interface (API) level and thus, beyond the scope of this document.

### 3.1. Register Nomenclature and Access Attributes

| ľ | Registe                           | r Nomenciature and Access Attributes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | RO                                | Read Only. If a register is read only, writes to this register have no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   | R/W                               | Read/Write. A register with this attribute can be read and written                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   | R/WC                              | Read/Write Clear. A register bit with this attribute can be read and written. However, a write of a 1 clears (sets to 0) the corresponding bit and a write of a 0 has no effect.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | R/WO                              | Read/Write Once. A register bit with this attribute can be written to only once after power up. After the first write, the bit becomes read only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   | Reserved<br>Bits                  | Some of the GMCH registers described in this section contain reserved bits. These bits are labeled "Reserved" or "Intel Reserved". Software must deal correctly with fields that are reserved. On reads, software must use appropriate masks to extract the defined bits and not rely on reserved bits being any particular value. On writes, software must ensure that the values of reserved bit positions are preserved. That is, the values of reserved bit positions must first be read, merged with the new values for other bit positions and then written back. Note the software does not need to perform read, merge, write operation for the configuration address register. |

|   | Reserved<br>Registers             | In addition to reserved bits within a register, the GMCH contains address locations in the configuration space of the Host-hub interface Bridge/DRAM Controller and the internal graphics device entities that are marked either "Reserved" or Intel Reserved". When a "Reserved" register location is read, a random value can be returned. ("Reserved" registers can be 8-, 16-, or 32-bit in size). Registers that are marked as "Reserved" must not be modified by system software. Writes to "Reserved" registers may cause system failure.                                                                                                                                        |

|   | Default<br>Value<br>Upon<br>Reset | Upon a Full Reset, the GMCH sets all of its internal configuration registers to predetermined <b>default</b> states. Some register values at reset are determined by external strapping options. The default state represents the minimum functionality feature set required to successfully bring up the system. Hence, it does not represent the optimal system configuration. It is the responsibility of the                                                                                                                                                                                                                                                                        |

system initialization software (usually BIOS) to properly determine the DRAM configurations, operating parameters and optional system features that are applicable, and to program the GMCH

Datasheet 25

registers accordingly.

### 3.2. PCI Configuration Space Access

The GMCH and the ICH are physically connected via the hub interface. From a configuration standpoint, the hub interface connecting the GMCH and the ICH is **logically PCI bus #0**. All devices internal to the GMCH and ICH appear to be on PCI bus #0. The system primary PCI expansion bus is physically attached to the ICH and, from a configuration standpoint, appears as a hierarchical PCI bus behind a PCI-to-PCI bridge. The primary PCI expansion bus connected to the ICH has a programmable PCI Bus number.

**Note:** Even though the primary PCI bus is referred to as PCI0 in this document it is not PCI bus #0 from a configuration standpoint.

The GMCH contains two PCI devices within a single physical component. The configuration registers for both Device 0 and 1 are mapped as devices residing on PCI bus #0.

- Device 0: Host-hub interface Bridge/DRAM Controller. Logically this appears as a PCI device residing on PCI bus #0. Physically Device 0 contains the PCI registers, DRAM registers, and other GMCH specific registers.

- Device 1: GMCH internal graphics device. These registers contain the PCI registers for the GMCH internal graphics device.

Note that a physical PCI bus #0 does not exist. The hub interface and the internal devices in the GMCH and ICH logically constitute PCI Bus #0 to configuration software.

#### 3.2.1. PCI Bus Configuration Mechanism

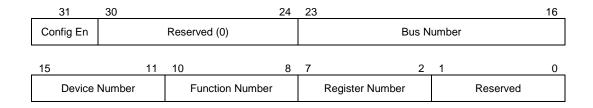

The PCI Bus defines a slot based "configuration space" that allows each device to contain up to 8 functions with each function containing up to 256 8-bit configuration registers. The PCI specification defines two bus cycles to access the PCI configuration space: Configuration Read and Configuration Write. Memory and I/O spaces are supported directly by the processor. Configuration space is supported by a mapping mechanism implemented within the GMCH. The PCI specification defines two mechanisms to access configuration space, Mechanism #1 and Mechanism #2.

#### The GMCH supports only Mechanism #1

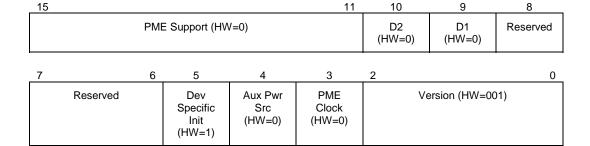

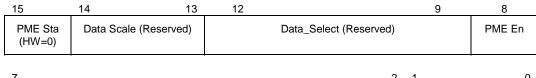

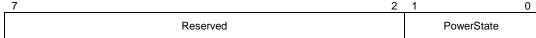

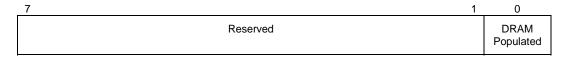

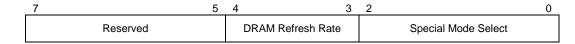

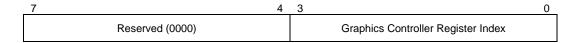

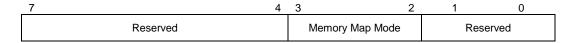

The configuration access mechanism makes use of the CONFIG\_ADDRESS Register and CONFIG\_DATA Register. To reference a configuration register a DWord I/O write cycle is used to place a value into CONFIG\_ADDRESS that specifies the PCI bus, the device on that bus, the function within the device, and a specific configuration register of the device function being accessed. CONFIG\_ADDRESS[31] must be 1 to enable a configuration cycle. CONFIG\_DATA then becomes a window into the four bytes of configuration space specified by the contents of CONFIG\_ADDRESS. Any read or write to CONFIG\_DATA will result in the GMCH translating the CONFIG\_ADDRESS into the appropriate configuration cycle.